1.本实用新型涉及电源控制领域,尤其是涉及一种输出电压,受输入高低电平左右和具有输出时序要求的双控制电路。

背景技术:

2.随着电子技术日新月异的发展,产品供电结构变得越来越复杂,在这种形势下,业界对使用的电源也提出了各种各样的要求。例如:在电源供应上,经常会遇到电源各路输出受电平和时序双控制要求,即电源各路输出除受输入高低电平影响外,还要求电源中的某一路输出延迟另外一路输出,优化产品性能的同时可降低其功耗,所以针对现有的电源电路已经不能够满足上述需求。

技术实现要素:

3.为了解决上述问题,本实用新型提供了一种电平和时序双控制电路。

4.为了实现上述实用新型目的,采用的技术方案是:

5.一种电平和时序双控制电路,包括第一电阻、第二电阻、第三电阻、第四电阻、第一光耦、第二光耦、第三光耦、第四光耦、第一电容、第二电容、第一二极管、第二二极管、555定时器、两个ttl电平端口ttl 、ttl-、两个辅助源端口辅助 12v aux、辅助 12vg aux,两个电压输出端口 5v、 5vg,两个dc-dc转换器使能端口n9_rc、n12_rc,一个电源输入端口 28vg;

6.ttl 串联第一电阻后与第一光耦的a端相连,第一光耦的b端与第二光耦的a端相连,第二光耦的b端与ttl-相连,第一光耦的c端与第一二极管的a端和第二二极管的a端相连,第一二极管的b端与第四光耦的c端和n9_rc相连,第二二极管的b端与n12_rc相连,第一光耦的d端与第四光耦的d端和电源输入端口 28vg相连;

7.第二光耦的c端与电压输出端口 5vg相连,电压输出端口 5v串联第二电阻后与第三光耦的a端相连,第三光耦的b端与第二光耦的d端相连,第三光耦的c端与辅助 12v aux相连,第三光耦的d端与555定时器的d端、h端、第二电容的a端相连,555定时器的b端、f端与第二电容的b端、第三电阻的a端相连,555定时器的e端与第一电容的a端相连,555定时器的a端与第一电容的b端、第四光耦的b端、第三电阻的b端、辅助 12vg aux相连,555定时器的c端串联第四电阻后与第四光耦的a端相连。

8.第一光耦和第三光耦是常开型光耦;第二光耦和第四光耦是常闭型光耦。

9.通过采用上述技术方案,本实用新型电路具有以下优越性:

10.本实用新型所述的一种电平和时序双控制电路,第一光耦控制两个dc-dc转换器使能端口n9_rc、n12_rc,实现ttl电平控制各路输出电压,同时利用555定时器的延时功能满足上电时序要求,可保证电源各路输出按预定的电平和时序正常工作,达到优化产品性能、减小产品浪涌电流和安全可靠工作的目的,本电路具有结构简单、成本低廉、高可靠性等优点。

附图说明

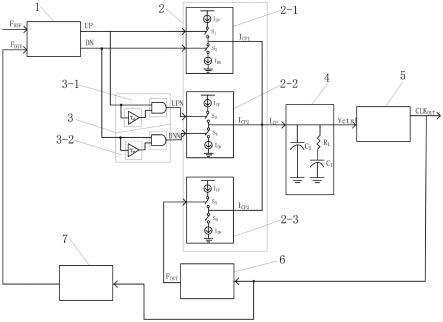

11.图1是本实用新型的电路原理图。

具体实施方式

12.下面结合附图和实例对本实用新型的技术方案进一步详细说明。

13.结合附图1所示的一种电平和时序双控制电路,ttl 串联第一电阻1后与第一光耦2的a端相连,第一光耦2的b端与第二光耦3的a端相连,第二光耦3的b端与ttl-相连,第一光耦2的c端与第一二极管4的a端和第二二极管5的a端相连,第一二极管4的b端与第四光耦13的c端和n9_rc相连,第二二极管5的b端与n12_rc相连,第一光耦2的d端与第四光耦13的d端和电源输入端口 28vg相连;

14.第二光耦3的c端与电压输出端口 5vg相连,电压输出端口 5v串联第二电阻6后与第三光耦7的a端相连,第三光耦7的b端与第二光耦3的d端相连,第三光耦7的c端与辅助 12v aux相连,第三光耦7的d端与555定时器8的d端、h端、第二电容10的a端相连,555定时器8的b端、f端与第二电容10的b端、第三电阻11的a端相连,555定时器8的e端与第一电容9的a端相连,555定时器8的a端与第一电容9的b端、第四光耦13的b端、第三电阻11的b端、辅助 12vg aux相连,555定时器8的c端串联第四电阻12后与第四光耦13的a端相连。

15.电平端口ttl 、ttl-的含义是:ttl 是电平控制的正极;ttl-是电平控制的负极。

16.辅助源端口辅助 12v aux、辅助 12vg aux的含义是:辅助 12v aux是外部辅助源的正极;辅助 12vg aux是外部辅助源的负极。

17.电压输出端口 5v、 5vg的含义是: 5v是输出电压的正极; 5vg是输出电压的负极。

18.dc-dc转换器使能端口n9_rc、n12_rc的含义是:n9_rc是第一个dc-dc转换器n9的使能控制端;n12_rc是第二个dc-dc转换器n12的使能控制端。

19.电源输入端口 28vg的含义是: 28vg是电源输入电压的负极。

20.第一光耦2、第二光耦3、第三光耦7、第四光耦13的a端、b端、c端、d端的含义是:a端是光耦输入的正端,b端是光耦输入的负端,c端是光耦输出的一端,d端是光耦输出的另一端,从附图1中可以看出,第一光耦2和第三光耦7只要是常开的光耦都可以,第二光耦3和第四光耦13只要是常闭的光耦都可以。

21.555定时器8的a端、b端、c端、d端、e端、f端、g端、h端、的含义是:a端是集成电路的供电负极,d端、h端是集成电路的供电正极,b端、f端、e端式是集成电路的控制端,c端是集成电路的输出端。

22.如图1所示,当电平端口ttl 、ttl-输入为高电平时,第一光耦2的a端和b端、c端和d端导通,两个dc-dc转换器的使能端口n9_rc和n12_rc均为低电平,即dc-dc转换器n9、n12使能端拉低,此时dc-dc转换器n9、n12两路无输出电压,第二光耦3的a端和b端导通、c端和d端不导通,第三光耦7的a端和b端不导通、c端和d端不导通,即555定时器8的d端、a端无供电电压,时序电路不起作用,第一电阻1在回路中起限流作用,具体阻值可以根据第一光耦2的输入电流参数来选择,第一二极管4、第二二极管5在电路中起隔离作用,任何二极管均可;

23.当电平端口ttl 、ttl-输入为低电平时,第一光耦2的a端和b端不导通、c端和d端处于断开状态,此时第二dc-dc转换器使能端口n12_rc处于悬空状态,第二光耦3的a端和b

端不导通、c端和d端导通,第三光耦7的a端和b端导通、c端和d端导通,即555定时器8的d端、a端接通供电电压 12v aux,555定时器8延时电路起作用,由于555定时器8的延时时间未到,555定时器8的c端输出低电平,第四光耦13的a端和b端不导通、c端和d端导通,故第一dc-dc转换器使能端口n9_rc处于拉低状态,当延时时间到达后,555定时器8的c端输出高电平,第四光耦13的a端和b端导通、c端和d端处于断开状态,第一dc-dc转换器使能端口n9_rc处于悬空状态,此时第一dc-dc转换器n9产生输出电压。

24.电平输入端口ttl 、ttl-同时控制dc-dc转换器使能端和555定时器8的供电情况,从而通过555定时器8延时电路使第一dc-dc转换器n9的输出电压延迟第二dc-dc转换器n12的输出电压,完成输出电压受电平和时序双控制电路,第二电阻6、第四电阻12在回路中起限流作用,第一电容9在回路中起滤波作用、第二电容10和第三电阻11在回路中决定延时时间的长短。

25.本实用新型电路适用于输出具有电平和时序双控制要求的电源使用,各路输出电压除受电平高低控制外,还对各路输出电压的上电时序有要求,可保证电源各路输出按预定的电平和时序正常工作,达到优化产品性能、减小产品浪涌电流和安全可靠工作的目的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。