闪存控制器、闪存模块以及电子装置1.本技术是申请日为2019年07月17日、申请号为201910647336.x、发明创造名称为“闪存控制器、闪存模块以及电子装置”的中国发明申请的分案申请。

技术领域:

:2.本发明关于闪存的存取控制,尤指一种闪存模块、闪存控制器以及电子装置的用来进行存取管理的方法。

背景技术:

::3.近年来由于存储器的技术不断地发展,各种可携式或非可携式记忆装置(例如:分别符合sd/mmc、cf、ms、xd及ufs标准的记忆卡;又例如:固态硬盘(solidstatedrive,ssd);又例如:分别符合ufs及emmc规格的嵌入式(embedded)记忆装置)被广泛地实施于诸多应用中。因此,这些记忆装置中的存储器的存取控制遂成为相当热门的议题。4.以常用的nand型闪存而言,其主要可包括单阶细胞(singlelevelcell,slc)与多阶细胞(multiplelevelcell,mlc)两大类的闪存。单阶细胞闪存中的每个被当作记忆细胞(memorycell)的晶体管只有两种电荷值,分别用来表示逻辑值0与逻辑值1。另外,多阶细胞闪存中的每个被当作记忆细胞的晶体管的存储能力则被充分利用,是采用较高的电压来驱动,以通过不同级别的电压在一个晶体管中记录至少两位的信息(诸如00、01、11、10)。理论上,多阶细胞闪存的记录密度可以达到单阶细胞闪存的记录密度的至少两倍,这对于曾经在发展过程中遇到瓶颈的nand型闪存的相关产业而言,是非常好的消息。5.相较于单阶细胞闪存,由于多阶细胞闪存的价格较便宜,并且在有限的空间里可提供较大的容量,故多阶细胞闪存很快地成为市面上的记忆装置竞相采用的主流。然而,多阶细胞闪存的不稳定性所导致的问题也一一浮现。为了确保在记忆装置中对闪存的存取控制能符合相关规范,闪存的控制器通常备有某些管理机制以妥善地管理数据的存取。6.依据现有技术,具备上列管理机制的记忆装置仍有不足之处。例如,当三阶细胞(triplelevelcell,tlc)被应用于记忆装置时,会有位错误率增加等问题。虽然针对来自三阶细胞闪存的读取数据的传统感测方案已被提出来尝试解决这些问题,但在具有四阶细胞(quadruplelevelcell,qlc)闪存的记忆装置上并不管用。尤其,传统感测方案对于在四阶细胞闪存中的每记忆细胞的高阶存储电位(high-levelpermemorycell)并不好。因此,需要一种新颖的方法以及相关架构,以在没有副作用或较不会带来副作用的强况下加强整体效能。技术实现要素:7.本发明的一目的在于公开一种用来进行一记忆装置的存取管理的方法,即使在一高密度存储排列下依然能有效率地取得足够的信息供解码运作的用以解决上述问题。8.依据本发明一实施例,揭示了一种电子装置,其中所述电子装置包括一闪存模块以及一闪存控制器。所述闪存模块包括至少一闪存芯片,每一闪存芯片包括多个区块(block),且每一区块包括多个页面,而所述闪存控制器是用来存取所述闪存模块。在所述电子装置的运作中,当所述闪存控制器发送一读取指令至所述闪存模块以请求至少一页面上的数据,所述闪存模块使用多个读取电压来读取所述至少一页面的每一记忆细胞以取得每一记忆细胞的多位信息,以及所述闪存模块将所述至少一页面的每一记忆细胞的所述多位信息传送至所述闪存控制器。9.依据本发明另一实施例,揭示了一种闪存控制器,其中所述闪存控制器耦接至一闪存模块,所述闪存模块包括至少一闪存芯片,每一闪存芯片包括多个区块,每一区块包括多个页面。所述闪存控制器包括一存储器以及一微处理器,其中所述存储器系用来存储一程序代码,以及所述微处理器是用来执行所述程序代码以通过一控制逻辑电路来存取所述闪存模块。在所述闪存控制器的运作中,在所述微处理器发送一读取指令至所述闪存模块以请求至少一页面上的数据以后,所述控制逻辑电路自所述闪存模块接收所述至少一页面的每一记忆细胞的多位信息,以及所述控制逻辑电路对所述至少一页面的每一记忆细胞的所述多位信息进行去随机化(de-randomize)以及解码。10.依据本发明另一实施例,揭示了一种闪存模块,其中所述闪存模块包括至少一闪存芯片,所述至少一闪存芯片中的每一闪存芯片包括至少一存储器数组、多个感测放大器以及一周边(peripheral)电路,所述至少一存储器数组包括多个区块,每一区块包括多个页面,且所述多个感测放大器是用来自所述至少一存储器数组中的多个记忆细胞读取数据。在所述闪存模块的运作中,当所述至少一闪存芯片自一闪存控制器接收到一读取指令时,所述多个感测放大器使用多个读取电压来读取所述至少一页面的每一记忆细胞以取得每一记忆细胞的多位信息,以及所述闪存模块通过所述周边电路将所述至少一页面的每一记忆细胞的所述多位信息传送至所述闪存控制器。附图说明11.图1为依据本发明一实施例的一电子装置的示意图。12.图2为依据本发明一实施例的一三维nand型闪存的示意图。13.图3为依据本发明一实施例绘示的图2所示的三维nand型闪存的某些局部结构。14.图4为依据本发明一实施例绘示的图2所示的三维nand型闪存的多个记忆细胞中的一个记忆细胞的某些实施细节。15.图5为依据本发明一实施例的四阶细胞区块的一记忆细胞的多个状态(编程状态)的示意图。16.图6为依据本发明一实施例的一闪存芯片的示意图。17.图7为依据本发明一第一实施例的一感测放大器的示意图。18.图8为依据本发明一实施例的图7所示的感测放大器的某些信号的时序图。19.图9为依据本发明一实施例的一计数器以及一映射电路的示意图。20.图10为依据本发明一实施例的状态s0~s15以及对应的最高有效位与多个最低有效位的示意图。21.图11为依据本发明一实施例的传送读取指令以及最高有效位/最低有效位的时序图。22.图12为依据本发明一第二实施例的一感测放大器的示意图。23.图13为依据本发明一实施例的图12所示的感测放大器的某些信号的时序图。24.其中,附图标记说明如下:25.10ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ电子装置26.50ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ主装置27.52ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ处理器28.54ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ电源供应电路29.100ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ记忆装置30.110ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ存储器控制器31.112ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ微处理器32.112cꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ程序代码33.112mꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ只读存储器34.114ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ控制逻辑电路35.132ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ编码器36.134ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ解码器37.136ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ随机化器38.138ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ去随机化器39.116ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ随机存取存储器40.118ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ传输接口电路41.120ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ闪存模块42.122-1,122-2,…,122-nꢀꢀꢀꢀꢀꢀꢀꢀꢀ闪存芯片43.m(1,1,1),m(2,1,1),…,m(nx,44.1,1),45.m(1,2,1),…,m(nx,2,1),…,46.m(1,ny,1),…,m(nx,ny,1),47.m(1,1,2),m(2,1,2),…,m(nx,1,2),48.m(1,2,2),…,m(nx,2,2),…,49.m(1,ny,2),…,m(nx,ny,2),…,50.m(1,1,nz),…,m(nx,1,nz),51.m(1,2,nz),…,m(nx,2,nz),…,52.m(1,ny,nz),…,m(nx,ny,nz),53.m(nx,ny,nz)ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ记忆细胞54.mbls(1,1),…,mbls(nx,1),55.mbls(1,2),…,mbls(nx,2),…,56.mbls(1,ny),…,mbls(nx,ny)上方选择电路57.msls(1,1),…,msls(nx,1),58.msls(1,2),…,msls(nx,2),…,59.msls(1,ny),…,msls(nx,ny)下方选择电路60.bl(1),…,bl(nx)ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ位线61.wl(1,1),wl(2,1),…,wl(ny,1),62.wl(1,2),wl(2,2),…,wl(ny,2),…,63.wl(1,nz),wl(2,nz),…,字线64.wl(ny,nz)65.bls(1),bls(2),…,bls(ny)ꢀꢀꢀꢀꢀ上方选择线66.sls(1),sls(2),…,sls(ny)ꢀꢀꢀꢀꢀ下方选择线67.sl(1),sl(2),…,sl(ny)ꢀꢀꢀꢀꢀꢀꢀ源极线68.ps2d(1),ps2d(2),…,ps2d(ny)电路模块69.s(1,1),…,s(nx,1),70.s(1,2),…,s(nx,2),…,71.s(1,ny),…,s(nx,ny)ꢀꢀꢀꢀꢀꢀꢀꢀꢀ次要电路模块72.mchꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ棒段73.mdꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ棒段的上侧74.msꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ棒段的下侧75.mfgꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ第一管状局部结构76.mcgꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ第二管状局部结构77.vr1,vr2,vr3,vr4,vr5,78.vr6,vr7,vr8,vr9,vr10,79.vr11,vr12,vr13,vr14,vr15ꢀꢀꢀꢀ读取电压80.s0,s1,s2,s3,s4,s5,s6,s7,81.s8,s9,s10,s11,s12,s13,s14,状态82.s1583.600ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ闪存芯片84.610,620ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ存储器数组85.612,614,622,624ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ感测放大器86.632,634ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ周边电路87.700,1200ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ感测放大器88.710,1210ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ运算放大器89.712,1212ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ电压源90.714ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ控制电路91.716ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ计数器92.910ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ映射电路93.1214ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ数字模拟转换器94.voutꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ输出信号95.vsen,vpre,vblꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ电压96.vrꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ读取电压97.cntꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ计数值98.cblꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ寄生电容99.sw1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ开关100.i_cellꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ电流101.t0,t1,t2ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ时间102.cnt_en、dac_enꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ致能信号具体实施方式103.图1为依据本发明一实施例的电子装置10的示意图,其中电子装置10可包括一主装置50以及一记忆装置100。主装置50可包括至少一处理器(例如一或多个处理器),可统称为处理器52,且可另包括耦接至处理器52的一电源供应电路54。处理器52可用来控制主装置50的运作,而电源供应电路54可用来提供电源给处理器52以及记忆装置100,并且输出一或多个驱动电压给记忆装置100。记忆装置100可用来提供存储空间给主装置50,并且自主装置50取得所述一或多个驱动电压以作为记忆装置100的电源。主机50的例子可包括(但不限于):多功能移动电话(multifunctionalmobilephone)、平板计算机(tablet)以及个人计算机(personalcomputer)诸如桌面计算机与膝上型计算机。记忆装置100的例子可包括(但不限于):固态硬盘(solidstatedrive,ssd)以及各种类型的嵌入式(embedded)记忆装置诸如符合快捷外设互联(peripheralcomponentinterconnectexpress,pcie)标准的嵌入式记忆装置等等。依据本实施例,记忆装置100可包括一闪存控制器110,且可另包括一闪存模块120,其中闪存控制器110是用来控制记忆装置100的运作以及存取闪存模块120,而闪存模块120是用来存储信息。闪存模块120可包括至少一闪存芯片诸如多个闪存芯片122-1、122-2、…及122-n,其中“n”可表示大于一的正整数。104.如图1所示,存储器控制器110可包括一处理电路诸如一微处理器112、一存储单元诸如一只读存储器(readonlymemory,rom)112m、一控制逻辑电路114、一随机存取存储器(randomaccessmemory,ram)116以及一传输接口电路118,其中这些组件可通过一总线彼此耦接。随机存取存储器116是以一静态随机存取存储器(staticram,sram)来实施,但本发明不限于此。随机存取存储器116可用来提供内部存储空间给闪存控制器110,例如,随机存取存储器116可用来作为一缓冲存储器以缓冲数据。另外,本实施例的只读存储器112m是用来存储一程序代码112c,而微处理器112则用来执行程序代码112c以控制对闪存模块120的存取。请注意,在某些例子中,程序代码112c可存储在随机存取存储器116或任何形式的存储器内。此外,控制逻辑电路114可用来控制闪存模块120,且可包括一编码器132、一解码器134、一随机化器(randomizer)136、一去随机化器(de-randomizer)138以及其它电路。传输接口电路118可符合一特定通信标准(诸如串行高级技术附件(serialadvancedtechnologyattachment,sata)标准、外设组件互联(peripheralcomponentinterconnect,pci)标准、快捷外设互联标准、通用快闪存储(universalflashstorage,ufs)标准等等),且可依据所述特定通信标准进行通信,例如为记忆装置100,和主装置50进行通信,其中主装置50可包括符合所述特定通信标准的对应的传输接口电路,来为主装置50,和记忆装置100进行通信。105.在本实施例中,主装置50可传送主装置指令(hostcommand)与对应的逻辑地址至闪存控制器110来存取记忆装置100。闪存控制器110接收主装置指令与逻辑地址,并将主装置指令转译成存储器操作指令(可简称为操作指令),再以操作指令控制闪存模块120读取、写入(write)/编程(program)闪存模块120当中某些实体地址的记忆单位(例如数据页面),其中实体地址对应于逻辑地址。当存储器控制器110对闪存芯片122-1、122-2、…及122-n中的任一闪存芯片122-n进行一抹除(erase)运作时(符号“n”可表示区间[1,n]中的任一整数),闪存芯片122-n的多个区块(block)中的至少一个区块会被抹除,其中所述多个区块中的每一区块可包括多个页面(例如数据页面),且一存取运作(例如读取或写入)可对一或多个页面进行。[0106]图2为依据本发明一实施例的一三维(three-dimensional,3d)nand型闪存的示意图。例如,上述闪存芯片122-1、122-2、…及122-n中的至少一者中的任一存储器组件可基于图2所示的三维nand型闪存来实施,但本发明不限于此。[0107]依据本实施例,所述三维nand型闪存可包括以一三维架构排列的多个记忆细胞,诸如分别被排列于垂直z轴的nz层并且对齐分别对应于x轴、y轴及z轴的三个方向的(nx*ny*nz)个记忆细胞{{m(1,1,1),…,m(nx,1,1)},{m(1,2,1),…,m(nx,2,1)},…,{m(1,ny,1),…,m(nx,ny,1)}}、{{m(1,1,2),…,m(nx,1,2)},{m(1,2,2),…,m(nx,2,2)},…,{m(1,ny,2),…,m(nx,ny,2)}}、…、以及{{m(1,1,nz),…,m(nx,1,nz)},{m(1,2,nz),…,m(nx,2,nz)},…,{m(1,ny,nz),…,m(nx,ny,nz)}},且可另包括用于选择控制的多个选择器电路,诸如被排列于所述nz层上面的一上方层(upperlayer)的(nx*ny)个上方选择器电路{mbls(1,1),…,mbls(nx,1)}、{mbls(1,2),…,mbls(nx,2)}、…及{mbls(1,ny),…,mbls(nx,ny)}、以及被排列于所述nz层下面的一下方层(lowerlayer)的(nx*ny)个下方选择器电路{msls(1,1),…,msls(nx,1)}、{msls(1,2),…,msls(nx,2)}、…及{msls(1,ny),…,msls(nx,ny)}。另外,所述三维nand型闪存可包括用于存取控制的多个位线(bitline)以及多个字线(wordline),诸如被排列于所述上方层上面的一顶部层(toplayer)的nx个位线bl(1)、…及bl(nx)、以及分别被排列于所述nz层的(ny*nz)个字线{wl(1,1),wl(2,1),…,wl(ny,1)}、{wl(1,2),wl(2,2),…,wl(ny,2)}、…及{wl(1,nz),wl(2,nz),…,wl(ny,nz)}。此外,所述三维nand型闪存可包括用于选择控制的多个选择线,诸如被排列于所述上方层的ny个上方选择线bls(1)、bls(2)、…及bls(ny)、以及被排列于所述下方层的ny个下方选择线sls(1)、sls(2)、…及sls(ny),且可另包括用于提供多个参考位准的多个源极线,诸如被排列于所述下方层下面的一底部层(bottomlayer)的ny个源极线sl(1)、sl(2)、…及sl(ny)。[0108]如图2所示,所述三维nand型闪存可被区分成沿着y轴分布的ny个电路模块ps2d(1)、ps2d(2)、…及ps2d(ny)。为便于理解,电路模块ps2d(1)、ps2d(2)、…及ps2d(ny)可具有与一平面nand闪存(其记忆细胞被排列于一单一层)类似的某些电气特征,因此可分别被视为多个虚拟二维(pseudo-2d)电路模块,但本发明不限于此。另外,电路模块ps2d(1)、ps2d(2)、…及ps2d(ny)中的任一电路模块ps2d(ny)可包括nx个次要(secondary)电路模块s(1,ny)、…及s(nx,ny),其中“ny”可表示区间[1,ny]中的任一整数。例如,电路模块ps2d(1)可包括nx个次要电路模块s(1,1)、…及s(nx,1),电路模块ps2d(2)可包括nx个次要电路模块s(1,2)、…及s(nx,2),…,以及电路模块ps2d(ny)可包括nx个次要电路模块s(1,ny)、…及s(nx,ny)。在电路模块ps2d(ny)中,次要电路模块s(1,ny)、…及s(nx,ny)中的任一次要电路模块s(nx,ny)可包括nz个记忆细胞m(nx,ny,1)、m(nx,ny,2)、…及m(nx,ny,nz),且可包括对应于记忆细胞m(nx,ny,1)、m(nx,ny,2)、…及m(nx,ny,nz)的一组选择器电路,诸如上方选择器电路mbls(nx,ny)以及下方选择器电路msls(nx,ny),其中“nx”可表示区间[1,nx]中的任一整数。上方选择器电路mbls(nx,ny)、下方选择器电路msls(nx,ny)以及记忆细胞m(nx,ny,1)、m(nx,ny,2)、…及m(nx,ny,nz)可由晶体管来实施。例如,上方选择器电路以及下方选择器电路msls(nx,ny)可由不具有任何浮动闸(floatinggate)的普通晶体管来实施,而记忆细胞m(nx,ny,1)、m(nx,ny,2)、…及m(nx,ny,nz)中的任一记忆细胞m(nx,ny,nz)可由一浮动闸晶体管来实施,其中“nz”可表示区间[1,nz]中的任一整数,但本发明不限于此。此外,在电路模块ps2d(ny)中的上方选择器电路mbls(1,ny)、…及mbls(nx,ny)可依据对应的选择线bls(ny)上的选择信号来进行选择,而在电路模块ps2d(ny)中的下方选择器电路msls(1,ny)、…及msls(nx,ny)可依据对应的选择线sls(ny)上的选择信号来进行选择。[0109]图3为依据本发明一实施例绘示的图2所示的三维nand型闪存的某些局部结构。所述三维nand型闪存可设计成具有多个棒状(rod-shaped)局部结构诸如图3所示的棒状局部结构,而所述多个棒状局部结构可分别被安排来穿过次要电路模块{s(1,1),…,s(nx,1)}、{s(1,2),…,s(nx,2)}、…及{s(1,ny),…,s(nx,ny)}。为便于理解,所述多个棒状局部结构可分别被视为图2所示的架构中的次要电路模块{s(1,1),…,s(nx,1)}、{s(1,2),…,s(nx,2)}、…及{s(1,ny),…,s(nx,ny)}的相关晶体管的通道,诸如用于实施上方选择器电路mbls(nx,ny)以及下方选择器电路msls(nx,ny)的普通晶体管的通道以及用于实施记忆细胞m(nx,ny,nz)的浮动闸晶体管的通道。依据某些实施例,所述多个棒状局部结构的数量可等于次要电路模块{s(1,1),…,s(nx,1)}、{s(1,2),…,s(nx,2)}、…及{s(1,ny),…,s(nx,ny)}的总数(nx*ny),但本发明不限于此。例如,所述多个记忆细胞的排列可予以变化,而多个棒状局部结构的数量可相对应地改变。[0110]另外,所述三维nand型闪存可被设计成具有多个管状(pipe-shaped)局部结构,且所述多个管状局部结构可被安排来环绕(encircle)所述多个棒状局部结构以形成次要电路模块{s(1,1),…,s(nx,1)}、{s(1,2),…,s(nx,2)}、…及{s(1,ny),…,s(nx,ny)}的各个组件,尤其是形成图2所示的架构中所述多个记忆细胞的各个控制闸与各个浮动闸以及所述多个选择器电路的各个闸。记忆细胞{{m(1,1,1),m(2,1,1),…},{m(1,1,2),m(2,1,2),…},…}以及字线{wl(1,1),wl(1,2),…}绘示于图3中,且图3所示的管状局部结构可指出有某些额外局部结构围绕所述多个棒状局部结构的每一者,其中针对这些额外局部结构的细节会在后续的实施例中进一步说明。[0111]图4为依据本发明一实施例绘示的图2所示的三维nand型闪存的所述多个记忆细胞中的一个记忆细胞的某些实施细节。如图4所示,记忆细胞m(nx,ny,nz)可包括所述多个棒状局部结构中的一者的一部分,诸如对应于次要电路模块s(nx,ny)的棒状局部结构中的一棒段(rodsegment)mch,且可另包括具有相同对称轴的某些管状局部结构。例如,棒段mch的上侧md与下侧ms可用来当作用于实施记忆细胞m(nx,ny,nx)的浮动闸晶体管的漏极与源极,且这些管状局部结构中的一第一管状局部结构mfg以及一第二管状局部结构mcg可用来作为这个浮动闸晶体管的浮动闸以及控制闸。这些管状局部结构中的其它管状局部结构,诸如棒段mch与所述第一管状局部结构mfg之间的管状局部结构以及所述第一管状局部结构mfg与所述第二管状局部结构mcg之间的管状局部结构,可由一或多个绝缘材料来实施。[0112]依据某些实施例,图2所示的架构中的所述多个选择器电路中的任一选择器电路可通过修改图4所示的架构来实施。例如,棒段mch的上侧md与下侧ms可用来作为用于实施这个选择器电路的普通晶体管的漏极与源极,而这些管状局部结构中的第二管状局部结构mcg可用来作为这个普通晶体管的栅极,其中第一管状局部结构mfg应从所述一或多个绝缘材料移除。因此,棒段mch与第二管状局部结构mcg之间只会有一个管状局部结构,但本发明不限于此。[0113]在闪存模块120中,当闪存芯片122-1~122-n的任一者的区块充当一单阶细胞区块,所述区块中的多个实体页面的每一者对应至一个逻辑页面,即所述页面的多个记忆细胞的每一者被组态成仅存储一个位,其中一个实体页面可包括由一字线控制的全部晶体管(例如,对应于字线wl(1,nz)的记忆细胞m(1,1,nz)~m(nx,1,nz)形成一实体页面)。当闪存芯片122-1~122-n的任一者的区块充当一多阶细胞区块,所述区块中的多个实体页面的每一者对应至两个逻辑页面,即所述页面的多个记忆细胞的每一者被组态成存储两个位。当闪存芯片122-1~122-n的任一者的区块充当一三阶细胞区块,所述区块中的多个实体页面的每一者对应至三个逻辑页面,即所述页面的多个记忆细胞的每一者被组态成存储三个位。当闪存芯片122-1~122-n的任一者的区块充当一四阶细胞区块,所述区块中的多个实体页面的每一者对应至四个逻辑页面,即所述页面的多个记忆细胞的每一者被组态成存储四个位。[0114]图5为依据本发明一实施例的所述四阶细胞区块的一记忆细胞的多个状态(编程状态)的示意图。如图5所示,每一记忆细胞可具有十六个状态,且每一状态代表四个位(分别命名为顶端位、上方位、中间位以及下方位)的不同组合。在图5所示的实施例中,当所述记忆细胞被编程为具有状态s0,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,1,1,1);当所述记忆细胞被编程为具有状态s1,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,1,1,0);当所述记忆细胞被编程为具有状态s2,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,0,1,0);当所述记忆细胞被编程为具有状态s3,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,0,0,0);当所述记忆细胞被编程为具有状态s4,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,0,0,1);当所述记忆细胞被编程为具有状态s5,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,0,0,1);当所述记忆细胞被编程为具有状态s6,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,0,0,0);当所述记忆细胞被编程为具有状态s7,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,0,1,0);当所述记忆细胞被编程为具有状态s8,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,1,1,0);当所述记忆细胞被编程为具有状态s9,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,1,0,0);当所述记忆细胞被编程为具有状态s10,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,1,0,0);当所述记忆细胞被编程为具有状态s11,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,1,0,1);当所述记忆细胞被编程为具有状态s12,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,1,0,1);当所述记忆细胞被编程为具有状态s13,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,1,1,1);当所述记忆细胞被编程为具有状态s14,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,0,1,1);以及当所述记忆细胞被编程为具有状态s15,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,0,1,1)。[0115]在现有技术中,当所述顶端位需被闪存控制器110读取时,闪存控制器110能控制闪存模块120施加四个读取电压vr5、vr10、vr12及vr15来读取所述记忆细胞。若所述记忆细胞在被施加读取电压vr5时是导通的,所述顶端位被判定为“1”;若所述记忆细胞在被施加读取电压vr5时是不导通的且所述记忆细胞在被施加读取电压vr10时是导通的,所述顶端位被判定为“0”;若所述记忆细胞在被施加读取电压vr10时是不导通的且所述记忆细胞在被施加读取电压vr12时是导通的,所述顶端位被判定为“1”;若所述记忆细胞在被施加读取电压vr12时是不导通的且所述记忆细胞在被施加读取电压vr15时是导通的,所述顶端位被判定为“0”;以及若所述记忆细胞在被施加读取电压vr15时是不导通的,所述顶端位被判定为“1”。当所述上方位需被闪存控制器110读取时,闪存控制器110能控制闪存模块120施加三个读取电压vr2、vr8及vr14来读取所述记忆细胞。若所述记忆细胞在被施加读取电压vr2时是导通的,所述上方位被判定为“1”;若所述记忆细胞在被施加读取电压vr2时是不导通的且所述记忆细胞在被施加读取电压vr8时是导通的,所述上方位被判定为“0”;若所述记忆细胞在被施加读取电压vr8时是不导通的且所述记忆细胞在被施加读取电压vr14时是导通的,所述上方位被判定为“1”;若所述记忆细胞在被施加读取电压vr14时是不导通的,所述上方位被判定为“0”。当所述中间位需被闪存控制器110读取时,闪存控制器110能控制闪存模块120施加四个读取电压vr3、vr7、vr9及vr13来读取所述记忆细胞。若所述记忆细胞在被施加读取电压vr3时是导通的,所述中间位被判定为“1”;若所述记忆细胞在被施加读取电压vr3时是不导通的且所述记忆细胞在被施加读取电压vr7时是导通的,所述中间位被判定为“0”;若所述记忆细胞在被施加读取电压vr7时是不导通的且所述记忆细胞在被施加读取电压vr9时是导通的,所述中间位被判定为“1”;若所述记忆细胞在被施加读取电压vr9时是不导通的且所述记忆细胞在被施加读取电压vr13时是导通的,所述中间位被判定为“0”;以及若所述记忆细胞在被施加读取电压vr13时是不导通的,所述中间位被判定为“1”。当所述下方位需被闪存控制器110读取时,闪存控制器110能控制闪存模块120施加四个读取电压vr1、vr4、vr6及vr11来读取所述记忆细胞。若所述记忆细胞在被施加读取电压vr1时是导通的,所述下方位被判定为“1”;若所述记忆细胞在被施加读取电压vr1时是不导通的且所述记忆细胞在被施加读取电压vr4时是导通的,所述下方位被判定为“0”;若所述记忆细胞在被施加读取电压vr4时是不导通的且所述记忆细胞在被施加读取电压vr6时是导通的,所述下方位被判定为“1”;若所述记忆细胞在被施加读取电压vr6时是不导通的且所述记忆细胞在被施加读取电压vr11时是导通的,所述下方位被判定为“0”;以及若所述记忆细胞在被施加读取电压vr11时是不导通的,所述下方位被判定为“1”。[0116]需注意的是,图5所示的格雷码(graycode)只是为了说明的目的,并非对本发明的限制。任意合适的格雷码都能用于记忆装置100中,且用于判定顶端位、上方位、中间位以及下方位的读取电压可据以改变。[0117]通过使用读取电压vr1~vr15的部分而自所述记忆细胞读取的位可被视为一符号位(signbit),而自多个记忆细胞(例如四千(4k)个记忆细胞)取得的符号位由去随机化器138进行处理并且由解码器134进行错误更正运作以产生解码后数据。然而,由于多阶细胞区块中的记忆细胞的状态区间很小,所以这些状态会因为在闪存模块120中发生的读取干扰、编程干扰或数据保留问题而具有严重的变异,而错误更正运作可能失败。为了解决这个问题,现有技术另施加了额外的读取电压来读取所述记忆细胞以取得多个软位(softbit),以增加错误更正运作的成功率。例如,若解码器134无法解码自所述多个记忆细胞取得的多个符号位,闪存控制器110可控制闪存模块120使用额外的读取电压来重新读取所述多个记忆细胞以取得一第一组软位,且解码器134使用一低密度奇偶校验码(low-densityparity-checkcode,ldpc)方法来以所述第一组软位解码所述多个符号位。例如,若闪存控制器110试图读取所述区块的顶端页面(即所述多个记忆细胞的顶端位),闪存控制器110可控制闪存模块120使用额外读取电压(vr5-δ)、(vr10-δ)、(vr12-δ)以及(vr15-δ)来取得所述第一组软位。若解码器134仍然无法解码,闪存控制器110可控制闪存模块120使用额外读取电压(vr5 δ)、(vr10 δ)、(vr12 δ)以及(vr15 δ)来重新读取所述多个记忆细胞以取得一第二组软位,而解码器134可使用所述低密度奇偶校验码方法来以所述第一组软位以及所述第二组软位等等来解码所述多个符号位。[0118]鉴于上述情况,若闪存控制器110需要自闪存模块120中的四阶细胞区块读取数据,闪存控制器110可读取所述多个记忆细胞并且对数据进行多次的解码来取得软位以成功地解码所述数据。每次闪存控制器110读取所述多个记忆细胞都需要传送一读取指令至闪存模块120,且闪存模块120需要一读取忙碌时间来读取符号位或软位。因此,现有技术中的用于高密度存储(诸如搭配三维nand型闪存技术的四阶细胞区块)的读取机制效率并不好。[0119]为了解决上述问题,本发明的实施例公开了一种读取机制以及解码方法来有效率地存取闪存模块120。[0120]图6为依据本发明一实施例的闪存芯片600的示意图,其中闪存芯片600可以是图1所示的闪存芯片122-1~122-n中的任一者。如图6所示,闪存芯片600包括两个存储器数组610及620、感测放大器612、614、622及624、以及周边电路632及634,其中存储器数组610及620包括图2所示的记忆细胞,感测放大器612、614、622及624是用来自存储器数组610及620读取数据,以及周边电路632及634包括垫片(pad)、相关控制电路以及其它接口电路。[0121]图7为依据本发明一第一实施例的感测放大器700的示意图。在图7中,感测放大器700包括一运算放大器710、一电压源712、一控制电路714、一计数器716以及一开关sw1。在本实施例中,感测放大器700是用来读取图1所示的对应于位线bl(1)与字线wl(1,nz)的记忆细胞m(1,1,nz)。当记忆细胞m(1,1,nz)将被读取时,控制电路714是用来产生读取电压vr至图1所示的记忆细胞m(1,1,nz),而上方选择器电路mbls(1,1)以及其它记忆细胞m(1,1,1)~m(1,1,(nz-1))被控制为导通。[0122]一并参考图7以及图8,图8为依据本发明一实施例的感测放大器700的某些信号的时序图。在感测放大器700的运作中,读取电压vr一开始等于零(即记忆细胞m(1,1,nz)是被停用(disable)的),开关sw1被控制以将位线bl(1)连接至电压源712,而电压源712开始对寄生(parasitic)电容cbl充电以使得在寄生电容cbl的一端子上的电压vbl于时间t0等于电压源712所提供的电压vpre。接着,于时间t1,开关sw1被控制以将位线bl(1)连接至运算放大器710的负端子,控制电路714开始产生充当读取电压vr的一斜坡信号至字线wl(1,nz)以控制记忆细胞m(1,1,nz),而控制电路714产生一致能信号cnt_en以使得计数器716开始工作并且在输出信号vout变为高时提供递增的计数值cnt。例如,假设记忆细胞m(1,1,nz)存储有对应于状态s8(其临界电压约为3v)的数据,当读取电压vr开始由0v升高至3v,由于读取电压vr不够高而无法启用(enable)记忆细胞m(1,1,nz),电压vbl维持在电压vpre,而由于电压vbl/vpre大于运算放大器710的正端子上的参考电压vsen,运算放大器710所产生的输出信号vout等于“0”。当读取电压vr于时间t2大于记忆细胞m(1,1,nz)的临界电压,记忆细胞m(1,1,nz)被启用以产生一电流i_cell来对寄生电容cbl放电,而电压vbl会降低。当电压vbl降低而变的低于参考电压vsen,输出信号vout变为“1”以触发计数器716输出当下的计数值cnt。在图8所示的实施例中,若记忆细胞m(1,1,nz)存储有对应于状态s8的数据,计数值cnt约为“28”。[0123]在图7以及图8所示的实施例中,由于读取电压vr的斜率、放电时间以及电路延迟为已知,计数器716输出的计数值cnt可确切地表示出记忆细胞m(1,1,nz)的临界电压。另外,若计数器716为具有较大的分辨率的计数器诸如八位计数器(即计数器716所使用的频率具有较高的频率),计数值cnt能表示记忆细胞m(1,1,nz)的符号位以及软位。因此,相较于现有技术使用多次读取运作来取得符号位以及软位,本发明的实施例能以一单一读取指令得到符号位以及软位,且读取效率可大幅地改善。另外,由于计数器716输出的计数值cnt能表示记忆细胞m(1,1,nz)的临界电压,即记忆细胞m(1,1,nz)的状态能被取得,因此,计数值cnt所载有的信息远多于现有技术所取得的符号位(即现有技术中的符号位无法确切地指出记忆细胞m(1,1,nz)具有哪一个状态)。详细来说,若记忆细胞m(1,1,nz)的顶端位将被读取,现有技术会使用读取电压vr5、vr10、vr12及vr15来读取记忆细胞m(1,1,nz),而闪存模块仅发送所述顶端位至闪存控制器。例如,若现有技术的闪存模块将所述顶端位“1”(即符号位)输出至闪存控制器,闪存控制器仅知道记忆细胞m(1,1,nz)具有状态s0~s4、s10~s11及s15中的其中一个,但闪存控制器无法确切地知道记忆细胞m(1,1,nz)具有哪一个状态。[0124]需注意的是,虽然图8展示了使用所述斜坡信号来充当读取电压vr,但本发明不限于此。在其它实施例中,控制电路714能将分别具有不同电压位准的读取电压vr施加于记忆细胞m(1,1,nz)(即分别具有不同电压位准的读取电压vr可分别被视为多个读取电压),读取电压vr的每一电压位准均对应至一计数值cnt,读取电压vr可具有任意其它合适的设计。在一实施例中,读取电压vr的电压位准的数量(或读取电压的数量)等于或大于记忆细胞m(1,1,nz)的状态的数量。[0125]在一实施例中,感测放大器700另包括图9所示的映射电路910。映射电路910是用来将所述计数值转换为指出记忆细胞m(1,1,nz)的临界电压或状态的八位信息,其中四个位为最高有效位(mostsignificantbit,msb),而其它四个位为最低有效位(leastsignificantbit,lsb)。例如,计数值“1”映射至八位信息(0,0,0,0,0,0,0,0),计数值“2”映射至八位信息(0,0,0,0,0,0,0,1)、计数值“3”映射至八位信息(0,0,0,0,0,0,1,0)、…、计数值“255”映射至八位信息(1,1,1,1,1,1,1,0)、而计数值“256”映射至八位信息(1,1,1,1,1,1,1,1)。图10为依据本发明一实施例的状态s0~s15以及对应的多个最高有效位与多个最低有效位的示意图。在图10所示的实施例中,所述多个最高有效位是用来指出记忆细胞m(1,1,nz)的状态,即最高有效位(0,0,0,0)表示状态s0、最高有效位(0,0,0,1)表示状态s1、最高有效位(0,0,1,0)表示状态s2、…、最高有效位(1,1,1,0)表示状态s14、及最高有效位(1,1,1,1)表示状态s15。另外,所述多个最高有效位所定义的范围另被分成由所述多个最低有效位表示的十六个子范围,且所述多个最低有效位能充当上述软位。[0126]在一实施例中,闪存模块120能在仅接收到一个读取指令的情形下便传送最高有效位以及最低有效位至闪存控制器110,以响应所述读取指令。参考图11,若闪存控制器110欲读取一页面(例如一逻辑页面)中的数据,闪存控制器110传送一读取指令至闪存模块120,并且闪存模块120使用上述机制来读取所述页面的记忆细胞以产生最高有效位以及最低有效位给每一记忆细胞。假设所述页面包括多个组块(chunk)(例如六十四个组块)且每一组块为一编码/解码单元,闪存模块120能将一第一组块中的每一记忆细胞的最高有效位、一第二组块中的每一记忆细胞的最高有效位、…、及一最后组块中的每一记忆细胞的最高有效位依序地传送至闪存控制器110以供后续去随机化(de-randomize)运作以及解码运作。在所述页面的全部记忆细胞的最高有效位都被传送至闪存控制器110后,闪存模块120开始将所述第一组块中的每一记忆细胞的最低有效位、所述第二组块中的每一记忆细胞的最低有效位、…、及所述最后组块中的每一记忆细胞的最低有效位依序地传送至闪存控制器110以供后续去随机化(de-randomize)运作以及解码运作。[0127]在上述实施例中,若闪存控制器110的解码器134仅使用所述页面的多个记忆细胞的最高有效位就能成功地解码数据,所述多个记忆细胞的最低有效位可不用于解码运作,或者闪存控制器110能通知闪存模块120停止传送最低有效位。[0128]在图9所示的实施例中,映射电路910是设置于闪存模块120中,且闪存模块120传送映射电路910输出的信息至闪存控制器110。在本发明的另一实施例中,映射电路910能被设置于闪存控制器110的控制逻辑电路114中,且闪存模块120传送计数值cnt至闪存控制器110。[0129]图12为依据本发明一第二实施例的感测放大器1200的示意图。在第12途中,感测放大器1200包括一运算放大器1210、一电压源1212、一数字模拟转换器1214以及一开关sw1。在本实施例中,感测放大器1200是用来读取图1所示的对应于位线bl(1)与字线wl(1,nz)的记忆细胞m(1,1,nz)。当记忆细胞m(1,1,nz)将被读取时,模拟数字转换器1214是用来产生读取电压vr至图1所示的记忆细胞m(1,1,nz),而其它记忆细胞m(1,1,1)~m(1,1,(nz-1))被控制为导通。[0130]一并参考图12以及图13,图13为依据本发明一实施例的感测放大器1200的某些信号的时序图。在感测放大器1200的运作中,数字模拟转换器1214一开始并未工作且读取电压vr一开始等于零(即记忆细胞m(1,1,nz)是被停用的),开关sw1被控制以将位线bl(1)连接至电压源1212,而电压源1212开始对寄生电容cbl充电以使得在寄生电容cbl的一端子上的电压vbl于时间t0等于电压源1212所提供的电压vpre。接着,于时间t1,开关sw1被控制以将位线bl(1)连接至运算放大器1210的负端子,数字模拟转换器1214根据一致能信号dac_en以开始产生充当读取电压vr的一斜坡信号至字线wl(1,nz)以控制记忆细胞m(1,1,nz)。例如,假设记忆细胞m(1,1,nz)存储有对应于状态s8(其临界电压约为3v)的数据,当读取电压vr开始由0v升高至3v,由于读取电压vr不够高而无法启用(enable)记忆细胞m(1,1,nz),电压vbl维持在电压vpre,而由于电压vbl/vpre大于运算放大器1210的正端子上的参考电压vsen,运算放大器1210所产生的输出信号vout等于“0”。当读取电压vr于时间t2大于记忆细胞m(1,1,nz)的临界电压,记忆细胞m(1,1,nz)被启用以产生一电流i_cell来对寄生电容cbl放电,而电压vbl会降低。当电压vbl降低而变的低于参考电压vsen,输出信号vout变为“1”以触发数字模拟转换器1214输出对应于当下读取电压vr的数字值。[0131]需注意的是,虽然图13展示了使用所述斜坡信号来充当读取电压vr,但本发明不限于此。在其它实施例中,数字模拟转换器1214能将分别具有不同电压位准的读取电压vr施加于记忆细胞m(1,1,nz)(即分别具有不同电压位准的读取电压vr可分别被视为多个读取电压),读取电压vr可具有任意其它合适的设计。在一实施例中,读取电压vr的电压位准的数量(或读取电压的数量)等于或大于记忆细胞m(1,1,nz)的状态的数量。[0132]在图12与图13所示的实施例中,数字模拟转换器1214输出的数字值能表示记忆细胞m(1,1,nz)的临界电压(即对应于数字模拟转换器1214输出的数字值的模拟电压非常接近记忆细胞m(1,1,nz)的临界电压),所以所述数字值能有效地被用于后续的解码运作。另外,假设数字模拟转换器1214是八位数字模拟转换器,所述数字值可具有图10所示的四个最高有效位以及四个最低有效位,而闪存模块120能以一读取指令直接将所述数字值(即多个最高有效位以及多个最低有效位)传送至闪存控制器110。传送所述读取指令以及所述多个最高有效位/最低有效位的时序图可参考图11。另外,因为电路延迟以及放电时间,数字模拟转换器1214输出的数字值可被略微地调整以使得调整后的数字值更接近记忆细胞m(1,1,nz)的临界电压。[0133]上述实施例是以四阶细胞区块为例,然而上述读取机制亦能应用于三阶细胞区块、多阶细胞区块以及单阶细胞区块。熟习此技艺者应能了解如何使用上述步骤来读取三阶细胞区块、多阶细胞区块以及单阶细胞区块中的记忆细胞,其它细节在此不赘述。[0134]总结来说,在本发明的闪存控制器以及闪存模块中,所述闪存模块能因应一个读取指令将每一记忆细胞的多位信息输出至所述闪存控制器,且每一记忆细胞的多位信息可指出所述记忆细胞的临界电压或状态。因此,读取效率能被大幅地改善。[0135]以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。当前第1页12当前第1页12

技术领域:

:2.本发明关于闪存的存取控制,尤指一种闪存模块、闪存控制器以及电子装置的用来进行存取管理的方法。

背景技术:

::3.近年来由于存储器的技术不断地发展,各种可携式或非可携式记忆装置(例如:分别符合sd/mmc、cf、ms、xd及ufs标准的记忆卡;又例如:固态硬盘(solidstatedrive,ssd);又例如:分别符合ufs及emmc规格的嵌入式(embedded)记忆装置)被广泛地实施于诸多应用中。因此,这些记忆装置中的存储器的存取控制遂成为相当热门的议题。4.以常用的nand型闪存而言,其主要可包括单阶细胞(singlelevelcell,slc)与多阶细胞(multiplelevelcell,mlc)两大类的闪存。单阶细胞闪存中的每个被当作记忆细胞(memorycell)的晶体管只有两种电荷值,分别用来表示逻辑值0与逻辑值1。另外,多阶细胞闪存中的每个被当作记忆细胞的晶体管的存储能力则被充分利用,是采用较高的电压来驱动,以通过不同级别的电压在一个晶体管中记录至少两位的信息(诸如00、01、11、10)。理论上,多阶细胞闪存的记录密度可以达到单阶细胞闪存的记录密度的至少两倍,这对于曾经在发展过程中遇到瓶颈的nand型闪存的相关产业而言,是非常好的消息。5.相较于单阶细胞闪存,由于多阶细胞闪存的价格较便宜,并且在有限的空间里可提供较大的容量,故多阶细胞闪存很快地成为市面上的记忆装置竞相采用的主流。然而,多阶细胞闪存的不稳定性所导致的问题也一一浮现。为了确保在记忆装置中对闪存的存取控制能符合相关规范,闪存的控制器通常备有某些管理机制以妥善地管理数据的存取。6.依据现有技术,具备上列管理机制的记忆装置仍有不足之处。例如,当三阶细胞(triplelevelcell,tlc)被应用于记忆装置时,会有位错误率增加等问题。虽然针对来自三阶细胞闪存的读取数据的传统感测方案已被提出来尝试解决这些问题,但在具有四阶细胞(quadruplelevelcell,qlc)闪存的记忆装置上并不管用。尤其,传统感测方案对于在四阶细胞闪存中的每记忆细胞的高阶存储电位(high-levelpermemorycell)并不好。因此,需要一种新颖的方法以及相关架构,以在没有副作用或较不会带来副作用的强况下加强整体效能。技术实现要素:7.本发明的一目的在于公开一种用来进行一记忆装置的存取管理的方法,即使在一高密度存储排列下依然能有效率地取得足够的信息供解码运作的用以解决上述问题。8.依据本发明一实施例,揭示了一种电子装置,其中所述电子装置包括一闪存模块以及一闪存控制器。所述闪存模块包括至少一闪存芯片,每一闪存芯片包括多个区块(block),且每一区块包括多个页面,而所述闪存控制器是用来存取所述闪存模块。在所述电子装置的运作中,当所述闪存控制器发送一读取指令至所述闪存模块以请求至少一页面上的数据,所述闪存模块使用多个读取电压来读取所述至少一页面的每一记忆细胞以取得每一记忆细胞的多位信息,以及所述闪存模块将所述至少一页面的每一记忆细胞的所述多位信息传送至所述闪存控制器。9.依据本发明另一实施例,揭示了一种闪存控制器,其中所述闪存控制器耦接至一闪存模块,所述闪存模块包括至少一闪存芯片,每一闪存芯片包括多个区块,每一区块包括多个页面。所述闪存控制器包括一存储器以及一微处理器,其中所述存储器系用来存储一程序代码,以及所述微处理器是用来执行所述程序代码以通过一控制逻辑电路来存取所述闪存模块。在所述闪存控制器的运作中,在所述微处理器发送一读取指令至所述闪存模块以请求至少一页面上的数据以后,所述控制逻辑电路自所述闪存模块接收所述至少一页面的每一记忆细胞的多位信息,以及所述控制逻辑电路对所述至少一页面的每一记忆细胞的所述多位信息进行去随机化(de-randomize)以及解码。10.依据本发明另一实施例,揭示了一种闪存模块,其中所述闪存模块包括至少一闪存芯片,所述至少一闪存芯片中的每一闪存芯片包括至少一存储器数组、多个感测放大器以及一周边(peripheral)电路,所述至少一存储器数组包括多个区块,每一区块包括多个页面,且所述多个感测放大器是用来自所述至少一存储器数组中的多个记忆细胞读取数据。在所述闪存模块的运作中,当所述至少一闪存芯片自一闪存控制器接收到一读取指令时,所述多个感测放大器使用多个读取电压来读取所述至少一页面的每一记忆细胞以取得每一记忆细胞的多位信息,以及所述闪存模块通过所述周边电路将所述至少一页面的每一记忆细胞的所述多位信息传送至所述闪存控制器。附图说明11.图1为依据本发明一实施例的一电子装置的示意图。12.图2为依据本发明一实施例的一三维nand型闪存的示意图。13.图3为依据本发明一实施例绘示的图2所示的三维nand型闪存的某些局部结构。14.图4为依据本发明一实施例绘示的图2所示的三维nand型闪存的多个记忆细胞中的一个记忆细胞的某些实施细节。15.图5为依据本发明一实施例的四阶细胞区块的一记忆细胞的多个状态(编程状态)的示意图。16.图6为依据本发明一实施例的一闪存芯片的示意图。17.图7为依据本发明一第一实施例的一感测放大器的示意图。18.图8为依据本发明一实施例的图7所示的感测放大器的某些信号的时序图。19.图9为依据本发明一实施例的一计数器以及一映射电路的示意图。20.图10为依据本发明一实施例的状态s0~s15以及对应的最高有效位与多个最低有效位的示意图。21.图11为依据本发明一实施例的传送读取指令以及最高有效位/最低有效位的时序图。22.图12为依据本发明一第二实施例的一感测放大器的示意图。23.图13为依据本发明一实施例的图12所示的感测放大器的某些信号的时序图。24.其中,附图标记说明如下:25.10ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ电子装置26.50ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ主装置27.52ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ处理器28.54ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ电源供应电路29.100ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ记忆装置30.110ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ存储器控制器31.112ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ微处理器32.112cꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ程序代码33.112mꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ只读存储器34.114ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ控制逻辑电路35.132ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ编码器36.134ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ解码器37.136ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ随机化器38.138ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ去随机化器39.116ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ随机存取存储器40.118ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ传输接口电路41.120ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ闪存模块42.122-1,122-2,…,122-nꢀꢀꢀꢀꢀꢀꢀꢀꢀ闪存芯片43.m(1,1,1),m(2,1,1),…,m(nx,44.1,1),45.m(1,2,1),…,m(nx,2,1),…,46.m(1,ny,1),…,m(nx,ny,1),47.m(1,1,2),m(2,1,2),…,m(nx,1,2),48.m(1,2,2),…,m(nx,2,2),…,49.m(1,ny,2),…,m(nx,ny,2),…,50.m(1,1,nz),…,m(nx,1,nz),51.m(1,2,nz),…,m(nx,2,nz),…,52.m(1,ny,nz),…,m(nx,ny,nz),53.m(nx,ny,nz)ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ记忆细胞54.mbls(1,1),…,mbls(nx,1),55.mbls(1,2),…,mbls(nx,2),…,56.mbls(1,ny),…,mbls(nx,ny)上方选择电路57.msls(1,1),…,msls(nx,1),58.msls(1,2),…,msls(nx,2),…,59.msls(1,ny),…,msls(nx,ny)下方选择电路60.bl(1),…,bl(nx)ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ位线61.wl(1,1),wl(2,1),…,wl(ny,1),62.wl(1,2),wl(2,2),…,wl(ny,2),…,63.wl(1,nz),wl(2,nz),…,字线64.wl(ny,nz)65.bls(1),bls(2),…,bls(ny)ꢀꢀꢀꢀꢀ上方选择线66.sls(1),sls(2),…,sls(ny)ꢀꢀꢀꢀꢀ下方选择线67.sl(1),sl(2),…,sl(ny)ꢀꢀꢀꢀꢀꢀꢀ源极线68.ps2d(1),ps2d(2),…,ps2d(ny)电路模块69.s(1,1),…,s(nx,1),70.s(1,2),…,s(nx,2),…,71.s(1,ny),…,s(nx,ny)ꢀꢀꢀꢀꢀꢀꢀꢀꢀ次要电路模块72.mchꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ棒段73.mdꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ棒段的上侧74.msꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ棒段的下侧75.mfgꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ第一管状局部结构76.mcgꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ第二管状局部结构77.vr1,vr2,vr3,vr4,vr5,78.vr6,vr7,vr8,vr9,vr10,79.vr11,vr12,vr13,vr14,vr15ꢀꢀꢀꢀ读取电压80.s0,s1,s2,s3,s4,s5,s6,s7,81.s8,s9,s10,s11,s12,s13,s14,状态82.s1583.600ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ闪存芯片84.610,620ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ存储器数组85.612,614,622,624ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ感测放大器86.632,634ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ周边电路87.700,1200ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ感测放大器88.710,1210ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ运算放大器89.712,1212ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ电压源90.714ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ控制电路91.716ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ计数器92.910ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ映射电路93.1214ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ数字模拟转换器94.voutꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ输出信号95.vsen,vpre,vblꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ电压96.vrꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ读取电压97.cntꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ计数值98.cblꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ寄生电容99.sw1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ开关100.i_cellꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ电流101.t0,t1,t2ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ时间102.cnt_en、dac_enꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ致能信号具体实施方式103.图1为依据本发明一实施例的电子装置10的示意图,其中电子装置10可包括一主装置50以及一记忆装置100。主装置50可包括至少一处理器(例如一或多个处理器),可统称为处理器52,且可另包括耦接至处理器52的一电源供应电路54。处理器52可用来控制主装置50的运作,而电源供应电路54可用来提供电源给处理器52以及记忆装置100,并且输出一或多个驱动电压给记忆装置100。记忆装置100可用来提供存储空间给主装置50,并且自主装置50取得所述一或多个驱动电压以作为记忆装置100的电源。主机50的例子可包括(但不限于):多功能移动电话(multifunctionalmobilephone)、平板计算机(tablet)以及个人计算机(personalcomputer)诸如桌面计算机与膝上型计算机。记忆装置100的例子可包括(但不限于):固态硬盘(solidstatedrive,ssd)以及各种类型的嵌入式(embedded)记忆装置诸如符合快捷外设互联(peripheralcomponentinterconnectexpress,pcie)标准的嵌入式记忆装置等等。依据本实施例,记忆装置100可包括一闪存控制器110,且可另包括一闪存模块120,其中闪存控制器110是用来控制记忆装置100的运作以及存取闪存模块120,而闪存模块120是用来存储信息。闪存模块120可包括至少一闪存芯片诸如多个闪存芯片122-1、122-2、…及122-n,其中“n”可表示大于一的正整数。104.如图1所示,存储器控制器110可包括一处理电路诸如一微处理器112、一存储单元诸如一只读存储器(readonlymemory,rom)112m、一控制逻辑电路114、一随机存取存储器(randomaccessmemory,ram)116以及一传输接口电路118,其中这些组件可通过一总线彼此耦接。随机存取存储器116是以一静态随机存取存储器(staticram,sram)来实施,但本发明不限于此。随机存取存储器116可用来提供内部存储空间给闪存控制器110,例如,随机存取存储器116可用来作为一缓冲存储器以缓冲数据。另外,本实施例的只读存储器112m是用来存储一程序代码112c,而微处理器112则用来执行程序代码112c以控制对闪存模块120的存取。请注意,在某些例子中,程序代码112c可存储在随机存取存储器116或任何形式的存储器内。此外,控制逻辑电路114可用来控制闪存模块120,且可包括一编码器132、一解码器134、一随机化器(randomizer)136、一去随机化器(de-randomizer)138以及其它电路。传输接口电路118可符合一特定通信标准(诸如串行高级技术附件(serialadvancedtechnologyattachment,sata)标准、外设组件互联(peripheralcomponentinterconnect,pci)标准、快捷外设互联标准、通用快闪存储(universalflashstorage,ufs)标准等等),且可依据所述特定通信标准进行通信,例如为记忆装置100,和主装置50进行通信,其中主装置50可包括符合所述特定通信标准的对应的传输接口电路,来为主装置50,和记忆装置100进行通信。105.在本实施例中,主装置50可传送主装置指令(hostcommand)与对应的逻辑地址至闪存控制器110来存取记忆装置100。闪存控制器110接收主装置指令与逻辑地址,并将主装置指令转译成存储器操作指令(可简称为操作指令),再以操作指令控制闪存模块120读取、写入(write)/编程(program)闪存模块120当中某些实体地址的记忆单位(例如数据页面),其中实体地址对应于逻辑地址。当存储器控制器110对闪存芯片122-1、122-2、…及122-n中的任一闪存芯片122-n进行一抹除(erase)运作时(符号“n”可表示区间[1,n]中的任一整数),闪存芯片122-n的多个区块(block)中的至少一个区块会被抹除,其中所述多个区块中的每一区块可包括多个页面(例如数据页面),且一存取运作(例如读取或写入)可对一或多个页面进行。[0106]图2为依据本发明一实施例的一三维(three-dimensional,3d)nand型闪存的示意图。例如,上述闪存芯片122-1、122-2、…及122-n中的至少一者中的任一存储器组件可基于图2所示的三维nand型闪存来实施,但本发明不限于此。[0107]依据本实施例,所述三维nand型闪存可包括以一三维架构排列的多个记忆细胞,诸如分别被排列于垂直z轴的nz层并且对齐分别对应于x轴、y轴及z轴的三个方向的(nx*ny*nz)个记忆细胞{{m(1,1,1),…,m(nx,1,1)},{m(1,2,1),…,m(nx,2,1)},…,{m(1,ny,1),…,m(nx,ny,1)}}、{{m(1,1,2),…,m(nx,1,2)},{m(1,2,2),…,m(nx,2,2)},…,{m(1,ny,2),…,m(nx,ny,2)}}、…、以及{{m(1,1,nz),…,m(nx,1,nz)},{m(1,2,nz),…,m(nx,2,nz)},…,{m(1,ny,nz),…,m(nx,ny,nz)}},且可另包括用于选择控制的多个选择器电路,诸如被排列于所述nz层上面的一上方层(upperlayer)的(nx*ny)个上方选择器电路{mbls(1,1),…,mbls(nx,1)}、{mbls(1,2),…,mbls(nx,2)}、…及{mbls(1,ny),…,mbls(nx,ny)}、以及被排列于所述nz层下面的一下方层(lowerlayer)的(nx*ny)个下方选择器电路{msls(1,1),…,msls(nx,1)}、{msls(1,2),…,msls(nx,2)}、…及{msls(1,ny),…,msls(nx,ny)}。另外,所述三维nand型闪存可包括用于存取控制的多个位线(bitline)以及多个字线(wordline),诸如被排列于所述上方层上面的一顶部层(toplayer)的nx个位线bl(1)、…及bl(nx)、以及分别被排列于所述nz层的(ny*nz)个字线{wl(1,1),wl(2,1),…,wl(ny,1)}、{wl(1,2),wl(2,2),…,wl(ny,2)}、…及{wl(1,nz),wl(2,nz),…,wl(ny,nz)}。此外,所述三维nand型闪存可包括用于选择控制的多个选择线,诸如被排列于所述上方层的ny个上方选择线bls(1)、bls(2)、…及bls(ny)、以及被排列于所述下方层的ny个下方选择线sls(1)、sls(2)、…及sls(ny),且可另包括用于提供多个参考位准的多个源极线,诸如被排列于所述下方层下面的一底部层(bottomlayer)的ny个源极线sl(1)、sl(2)、…及sl(ny)。[0108]如图2所示,所述三维nand型闪存可被区分成沿着y轴分布的ny个电路模块ps2d(1)、ps2d(2)、…及ps2d(ny)。为便于理解,电路模块ps2d(1)、ps2d(2)、…及ps2d(ny)可具有与一平面nand闪存(其记忆细胞被排列于一单一层)类似的某些电气特征,因此可分别被视为多个虚拟二维(pseudo-2d)电路模块,但本发明不限于此。另外,电路模块ps2d(1)、ps2d(2)、…及ps2d(ny)中的任一电路模块ps2d(ny)可包括nx个次要(secondary)电路模块s(1,ny)、…及s(nx,ny),其中“ny”可表示区间[1,ny]中的任一整数。例如,电路模块ps2d(1)可包括nx个次要电路模块s(1,1)、…及s(nx,1),电路模块ps2d(2)可包括nx个次要电路模块s(1,2)、…及s(nx,2),…,以及电路模块ps2d(ny)可包括nx个次要电路模块s(1,ny)、…及s(nx,ny)。在电路模块ps2d(ny)中,次要电路模块s(1,ny)、…及s(nx,ny)中的任一次要电路模块s(nx,ny)可包括nz个记忆细胞m(nx,ny,1)、m(nx,ny,2)、…及m(nx,ny,nz),且可包括对应于记忆细胞m(nx,ny,1)、m(nx,ny,2)、…及m(nx,ny,nz)的一组选择器电路,诸如上方选择器电路mbls(nx,ny)以及下方选择器电路msls(nx,ny),其中“nx”可表示区间[1,nx]中的任一整数。上方选择器电路mbls(nx,ny)、下方选择器电路msls(nx,ny)以及记忆细胞m(nx,ny,1)、m(nx,ny,2)、…及m(nx,ny,nz)可由晶体管来实施。例如,上方选择器电路以及下方选择器电路msls(nx,ny)可由不具有任何浮动闸(floatinggate)的普通晶体管来实施,而记忆细胞m(nx,ny,1)、m(nx,ny,2)、…及m(nx,ny,nz)中的任一记忆细胞m(nx,ny,nz)可由一浮动闸晶体管来实施,其中“nz”可表示区间[1,nz]中的任一整数,但本发明不限于此。此外,在电路模块ps2d(ny)中的上方选择器电路mbls(1,ny)、…及mbls(nx,ny)可依据对应的选择线bls(ny)上的选择信号来进行选择,而在电路模块ps2d(ny)中的下方选择器电路msls(1,ny)、…及msls(nx,ny)可依据对应的选择线sls(ny)上的选择信号来进行选择。[0109]图3为依据本发明一实施例绘示的图2所示的三维nand型闪存的某些局部结构。所述三维nand型闪存可设计成具有多个棒状(rod-shaped)局部结构诸如图3所示的棒状局部结构,而所述多个棒状局部结构可分别被安排来穿过次要电路模块{s(1,1),…,s(nx,1)}、{s(1,2),…,s(nx,2)}、…及{s(1,ny),…,s(nx,ny)}。为便于理解,所述多个棒状局部结构可分别被视为图2所示的架构中的次要电路模块{s(1,1),…,s(nx,1)}、{s(1,2),…,s(nx,2)}、…及{s(1,ny),…,s(nx,ny)}的相关晶体管的通道,诸如用于实施上方选择器电路mbls(nx,ny)以及下方选择器电路msls(nx,ny)的普通晶体管的通道以及用于实施记忆细胞m(nx,ny,nz)的浮动闸晶体管的通道。依据某些实施例,所述多个棒状局部结构的数量可等于次要电路模块{s(1,1),…,s(nx,1)}、{s(1,2),…,s(nx,2)}、…及{s(1,ny),…,s(nx,ny)}的总数(nx*ny),但本发明不限于此。例如,所述多个记忆细胞的排列可予以变化,而多个棒状局部结构的数量可相对应地改变。[0110]另外,所述三维nand型闪存可被设计成具有多个管状(pipe-shaped)局部结构,且所述多个管状局部结构可被安排来环绕(encircle)所述多个棒状局部结构以形成次要电路模块{s(1,1),…,s(nx,1)}、{s(1,2),…,s(nx,2)}、…及{s(1,ny),…,s(nx,ny)}的各个组件,尤其是形成图2所示的架构中所述多个记忆细胞的各个控制闸与各个浮动闸以及所述多个选择器电路的各个闸。记忆细胞{{m(1,1,1),m(2,1,1),…},{m(1,1,2),m(2,1,2),…},…}以及字线{wl(1,1),wl(1,2),…}绘示于图3中,且图3所示的管状局部结构可指出有某些额外局部结构围绕所述多个棒状局部结构的每一者,其中针对这些额外局部结构的细节会在后续的实施例中进一步说明。[0111]图4为依据本发明一实施例绘示的图2所示的三维nand型闪存的所述多个记忆细胞中的一个记忆细胞的某些实施细节。如图4所示,记忆细胞m(nx,ny,nz)可包括所述多个棒状局部结构中的一者的一部分,诸如对应于次要电路模块s(nx,ny)的棒状局部结构中的一棒段(rodsegment)mch,且可另包括具有相同对称轴的某些管状局部结构。例如,棒段mch的上侧md与下侧ms可用来当作用于实施记忆细胞m(nx,ny,nx)的浮动闸晶体管的漏极与源极,且这些管状局部结构中的一第一管状局部结构mfg以及一第二管状局部结构mcg可用来作为这个浮动闸晶体管的浮动闸以及控制闸。这些管状局部结构中的其它管状局部结构,诸如棒段mch与所述第一管状局部结构mfg之间的管状局部结构以及所述第一管状局部结构mfg与所述第二管状局部结构mcg之间的管状局部结构,可由一或多个绝缘材料来实施。[0112]依据某些实施例,图2所示的架构中的所述多个选择器电路中的任一选择器电路可通过修改图4所示的架构来实施。例如,棒段mch的上侧md与下侧ms可用来作为用于实施这个选择器电路的普通晶体管的漏极与源极,而这些管状局部结构中的第二管状局部结构mcg可用来作为这个普通晶体管的栅极,其中第一管状局部结构mfg应从所述一或多个绝缘材料移除。因此,棒段mch与第二管状局部结构mcg之间只会有一个管状局部结构,但本发明不限于此。[0113]在闪存模块120中,当闪存芯片122-1~122-n的任一者的区块充当一单阶细胞区块,所述区块中的多个实体页面的每一者对应至一个逻辑页面,即所述页面的多个记忆细胞的每一者被组态成仅存储一个位,其中一个实体页面可包括由一字线控制的全部晶体管(例如,对应于字线wl(1,nz)的记忆细胞m(1,1,nz)~m(nx,1,nz)形成一实体页面)。当闪存芯片122-1~122-n的任一者的区块充当一多阶细胞区块,所述区块中的多个实体页面的每一者对应至两个逻辑页面,即所述页面的多个记忆细胞的每一者被组态成存储两个位。当闪存芯片122-1~122-n的任一者的区块充当一三阶细胞区块,所述区块中的多个实体页面的每一者对应至三个逻辑页面,即所述页面的多个记忆细胞的每一者被组态成存储三个位。当闪存芯片122-1~122-n的任一者的区块充当一四阶细胞区块,所述区块中的多个实体页面的每一者对应至四个逻辑页面,即所述页面的多个记忆细胞的每一者被组态成存储四个位。[0114]图5为依据本发明一实施例的所述四阶细胞区块的一记忆细胞的多个状态(编程状态)的示意图。如图5所示,每一记忆细胞可具有十六个状态,且每一状态代表四个位(分别命名为顶端位、上方位、中间位以及下方位)的不同组合。在图5所示的实施例中,当所述记忆细胞被编程为具有状态s0,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,1,1,1);当所述记忆细胞被编程为具有状态s1,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,1,1,0);当所述记忆细胞被编程为具有状态s2,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,0,1,0);当所述记忆细胞被编程为具有状态s3,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,0,0,0);当所述记忆细胞被编程为具有状态s4,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,0,0,1);当所述记忆细胞被编程为具有状态s5,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,0,0,1);当所述记忆细胞被编程为具有状态s6,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,0,0,0);当所述记忆细胞被编程为具有状态s7,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,0,1,0);当所述记忆细胞被编程为具有状态s8,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,1,1,0);当所述记忆细胞被编程为具有状态s9,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,1,0,0);当所述记忆细胞被编程为具有状态s10,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,1,0,0);当所述记忆细胞被编程为具有状态s11,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,1,0,1);当所述记忆细胞被编程为具有状态s12,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,1,0,1);当所述记忆细胞被编程为具有状态s13,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,1,1,1);当所述记忆细胞被编程为具有状态s14,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(0,0,1,1);以及当所述记忆细胞被编程为具有状态s15,存储于所述记忆细胞的顶端位、上方位、中间位以及下方位为(1,0,1,1)。[0115]在现有技术中,当所述顶端位需被闪存控制器110读取时,闪存控制器110能控制闪存模块120施加四个读取电压vr5、vr10、vr12及vr15来读取所述记忆细胞。若所述记忆细胞在被施加读取电压vr5时是导通的,所述顶端位被判定为“1”;若所述记忆细胞在被施加读取电压vr5时是不导通的且所述记忆细胞在被施加读取电压vr10时是导通的,所述顶端位被判定为“0”;若所述记忆细胞在被施加读取电压vr10时是不导通的且所述记忆细胞在被施加读取电压vr12时是导通的,所述顶端位被判定为“1”;若所述记忆细胞在被施加读取电压vr12时是不导通的且所述记忆细胞在被施加读取电压vr15时是导通的,所述顶端位被判定为“0”;以及若所述记忆细胞在被施加读取电压vr15时是不导通的,所述顶端位被判定为“1”。当所述上方位需被闪存控制器110读取时,闪存控制器110能控制闪存模块120施加三个读取电压vr2、vr8及vr14来读取所述记忆细胞。若所述记忆细胞在被施加读取电压vr2时是导通的,所述上方位被判定为“1”;若所述记忆细胞在被施加读取电压vr2时是不导通的且所述记忆细胞在被施加读取电压vr8时是导通的,所述上方位被判定为“0”;若所述记忆细胞在被施加读取电压vr8时是不导通的且所述记忆细胞在被施加读取电压vr14时是导通的,所述上方位被判定为“1”;若所述记忆细胞在被施加读取电压vr14时是不导通的,所述上方位被判定为“0”。当所述中间位需被闪存控制器110读取时,闪存控制器110能控制闪存模块120施加四个读取电压vr3、vr7、vr9及vr13来读取所述记忆细胞。若所述记忆细胞在被施加读取电压vr3时是导通的,所述中间位被判定为“1”;若所述记忆细胞在被施加读取电压vr3时是不导通的且所述记忆细胞在被施加读取电压vr7时是导通的,所述中间位被判定为“0”;若所述记忆细胞在被施加读取电压vr7时是不导通的且所述记忆细胞在被施加读取电压vr9时是导通的,所述中间位被判定为“1”;若所述记忆细胞在被施加读取电压vr9时是不导通的且所述记忆细胞在被施加读取电压vr13时是导通的,所述中间位被判定为“0”;以及若所述记忆细胞在被施加读取电压vr13时是不导通的,所述中间位被判定为“1”。当所述下方位需被闪存控制器110读取时,闪存控制器110能控制闪存模块120施加四个读取电压vr1、vr4、vr6及vr11来读取所述记忆细胞。若所述记忆细胞在被施加读取电压vr1时是导通的,所述下方位被判定为“1”;若所述记忆细胞在被施加读取电压vr1时是不导通的且所述记忆细胞在被施加读取电压vr4时是导通的,所述下方位被判定为“0”;若所述记忆细胞在被施加读取电压vr4时是不导通的且所述记忆细胞在被施加读取电压vr6时是导通的,所述下方位被判定为“1”;若所述记忆细胞在被施加读取电压vr6时是不导通的且所述记忆细胞在被施加读取电压vr11时是导通的,所述下方位被判定为“0”;以及若所述记忆细胞在被施加读取电压vr11时是不导通的,所述下方位被判定为“1”。[0116]需注意的是,图5所示的格雷码(graycode)只是为了说明的目的,并非对本发明的限制。任意合适的格雷码都能用于记忆装置100中,且用于判定顶端位、上方位、中间位以及下方位的读取电压可据以改变。[0117]通过使用读取电压vr1~vr15的部分而自所述记忆细胞读取的位可被视为一符号位(signbit),而自多个记忆细胞(例如四千(4k)个记忆细胞)取得的符号位由去随机化器138进行处理并且由解码器134进行错误更正运作以产生解码后数据。然而,由于多阶细胞区块中的记忆细胞的状态区间很小,所以这些状态会因为在闪存模块120中发生的读取干扰、编程干扰或数据保留问题而具有严重的变异,而错误更正运作可能失败。为了解决这个问题,现有技术另施加了额外的读取电压来读取所述记忆细胞以取得多个软位(softbit),以增加错误更正运作的成功率。例如,若解码器134无法解码自所述多个记忆细胞取得的多个符号位,闪存控制器110可控制闪存模块120使用额外的读取电压来重新读取所述多个记忆细胞以取得一第一组软位,且解码器134使用一低密度奇偶校验码(low-densityparity-checkcode,ldpc)方法来以所述第一组软位解码所述多个符号位。例如,若闪存控制器110试图读取所述区块的顶端页面(即所述多个记忆细胞的顶端位),闪存控制器110可控制闪存模块120使用额外读取电压(vr5-δ)、(vr10-δ)、(vr12-δ)以及(vr15-δ)来取得所述第一组软位。若解码器134仍然无法解码,闪存控制器110可控制闪存模块120使用额外读取电压(vr5 δ)、(vr10 δ)、(vr12 δ)以及(vr15 δ)来重新读取所述多个记忆细胞以取得一第二组软位,而解码器134可使用所述低密度奇偶校验码方法来以所述第一组软位以及所述第二组软位等等来解码所述多个符号位。[0118]鉴于上述情况,若闪存控制器110需要自闪存模块120中的四阶细胞区块读取数据,闪存控制器110可读取所述多个记忆细胞并且对数据进行多次的解码来取得软位以成功地解码所述数据。每次闪存控制器110读取所述多个记忆细胞都需要传送一读取指令至闪存模块120,且闪存模块120需要一读取忙碌时间来读取符号位或软位。因此,现有技术中的用于高密度存储(诸如搭配三维nand型闪存技术的四阶细胞区块)的读取机制效率并不好。[0119]为了解决上述问题,本发明的实施例公开了一种读取机制以及解码方法来有效率地存取闪存模块120。[0120]图6为依据本发明一实施例的闪存芯片600的示意图,其中闪存芯片600可以是图1所示的闪存芯片122-1~122-n中的任一者。如图6所示,闪存芯片600包括两个存储器数组610及620、感测放大器612、614、622及624、以及周边电路632及634,其中存储器数组610及620包括图2所示的记忆细胞,感测放大器612、614、622及624是用来自存储器数组610及620读取数据,以及周边电路632及634包括垫片(pad)、相关控制电路以及其它接口电路。[0121]图7为依据本发明一第一实施例的感测放大器700的示意图。在图7中,感测放大器700包括一运算放大器710、一电压源712、一控制电路714、一计数器716以及一开关sw1。在本实施例中,感测放大器700是用来读取图1所示的对应于位线bl(1)与字线wl(1,nz)的记忆细胞m(1,1,nz)。当记忆细胞m(1,1,nz)将被读取时,控制电路714是用来产生读取电压vr至图1所示的记忆细胞m(1,1,nz),而上方选择器电路mbls(1,1)以及其它记忆细胞m(1,1,1)~m(1,1,(nz-1))被控制为导通。[0122]一并参考图7以及图8,图8为依据本发明一实施例的感测放大器700的某些信号的时序图。在感测放大器700的运作中,读取电压vr一开始等于零(即记忆细胞m(1,1,nz)是被停用(disable)的),开关sw1被控制以将位线bl(1)连接至电压源712,而电压源712开始对寄生(parasitic)电容cbl充电以使得在寄生电容cbl的一端子上的电压vbl于时间t0等于电压源712所提供的电压vpre。接着,于时间t1,开关sw1被控制以将位线bl(1)连接至运算放大器710的负端子,控制电路714开始产生充当读取电压vr的一斜坡信号至字线wl(1,nz)以控制记忆细胞m(1,1,nz),而控制电路714产生一致能信号cnt_en以使得计数器716开始工作并且在输出信号vout变为高时提供递增的计数值cnt。例如,假设记忆细胞m(1,1,nz)存储有对应于状态s8(其临界电压约为3v)的数据,当读取电压vr开始由0v升高至3v,由于读取电压vr不够高而无法启用(enable)记忆细胞m(1,1,nz),电压vbl维持在电压vpre,而由于电压vbl/vpre大于运算放大器710的正端子上的参考电压vsen,运算放大器710所产生的输出信号vout等于“0”。当读取电压vr于时间t2大于记忆细胞m(1,1,nz)的临界电压,记忆细胞m(1,1,nz)被启用以产生一电流i_cell来对寄生电容cbl放电,而电压vbl会降低。当电压vbl降低而变的低于参考电压vsen,输出信号vout变为“1”以触发计数器716输出当下的计数值cnt。在图8所示的实施例中,若记忆细胞m(1,1,nz)存储有对应于状态s8的数据,计数值cnt约为“28”。[0123]在图7以及图8所示的实施例中,由于读取电压vr的斜率、放电时间以及电路延迟为已知,计数器716输出的计数值cnt可确切地表示出记忆细胞m(1,1,nz)的临界电压。另外,若计数器716为具有较大的分辨率的计数器诸如八位计数器(即计数器716所使用的频率具有较高的频率),计数值cnt能表示记忆细胞m(1,1,nz)的符号位以及软位。因此,相较于现有技术使用多次读取运作来取得符号位以及软位,本发明的实施例能以一单一读取指令得到符号位以及软位,且读取效率可大幅地改善。另外,由于计数器716输出的计数值cnt能表示记忆细胞m(1,1,nz)的临界电压,即记忆细胞m(1,1,nz)的状态能被取得,因此,计数值cnt所载有的信息远多于现有技术所取得的符号位(即现有技术中的符号位无法确切地指出记忆细胞m(1,1,nz)具有哪一个状态)。详细来说,若记忆细胞m(1,1,nz)的顶端位将被读取,现有技术会使用读取电压vr5、vr10、vr12及vr15来读取记忆细胞m(1,1,nz),而闪存模块仅发送所述顶端位至闪存控制器。例如,若现有技术的闪存模块将所述顶端位“1”(即符号位)输出至闪存控制器,闪存控制器仅知道记忆细胞m(1,1,nz)具有状态s0~s4、s10~s11及s15中的其中一个,但闪存控制器无法确切地知道记忆细胞m(1,1,nz)具有哪一个状态。[0124]需注意的是,虽然图8展示了使用所述斜坡信号来充当读取电压vr,但本发明不限于此。在其它实施例中,控制电路714能将分别具有不同电压位准的读取电压vr施加于记忆细胞m(1,1,nz)(即分别具有不同电压位准的读取电压vr可分别被视为多个读取电压),读取电压vr的每一电压位准均对应至一计数值cnt,读取电压vr可具有任意其它合适的设计。在一实施例中,读取电压vr的电压位准的数量(或读取电压的数量)等于或大于记忆细胞m(1,1,nz)的状态的数量。[0125]在一实施例中,感测放大器700另包括图9所示的映射电路910。映射电路910是用来将所述计数值转换为指出记忆细胞m(1,1,nz)的临界电压或状态的八位信息,其中四个位为最高有效位(mostsignificantbit,msb),而其它四个位为最低有效位(leastsignificantbit,lsb)。例如,计数值“1”映射至八位信息(0,0,0,0,0,0,0,0),计数值“2”映射至八位信息(0,0,0,0,0,0,0,1)、计数值“3”映射至八位信息(0,0,0,0,0,0,1,0)、…、计数值“255”映射至八位信息(1,1,1,1,1,1,1,0)、而计数值“256”映射至八位信息(1,1,1,1,1,1,1,1)。图10为依据本发明一实施例的状态s0~s15以及对应的多个最高有效位与多个最低有效位的示意图。在图10所示的实施例中,所述多个最高有效位是用来指出记忆细胞m(1,1,nz)的状态,即最高有效位(0,0,0,0)表示状态s0、最高有效位(0,0,0,1)表示状态s1、最高有效位(0,0,1,0)表示状态s2、…、最高有效位(1,1,1,0)表示状态s14、及最高有效位(1,1,1,1)表示状态s15。另外,所述多个最高有效位所定义的范围另被分成由所述多个最低有效位表示的十六个子范围,且所述多个最低有效位能充当上述软位。[0126]在一实施例中,闪存模块120能在仅接收到一个读取指令的情形下便传送最高有效位以及最低有效位至闪存控制器110,以响应所述读取指令。参考图11,若闪存控制器110欲读取一页面(例如一逻辑页面)中的数据,闪存控制器110传送一读取指令至闪存模块120,并且闪存模块120使用上述机制来读取所述页面的记忆细胞以产生最高有效位以及最低有效位给每一记忆细胞。假设所述页面包括多个组块(chunk)(例如六十四个组块)且每一组块为一编码/解码单元,闪存模块120能将一第一组块中的每一记忆细胞的最高有效位、一第二组块中的每一记忆细胞的最高有效位、…、及一最后组块中的每一记忆细胞的最高有效位依序地传送至闪存控制器110以供后续去随机化(de-randomize)运作以及解码运作。在所述页面的全部记忆细胞的最高有效位都被传送至闪存控制器110后,闪存模块120开始将所述第一组块中的每一记忆细胞的最低有效位、所述第二组块中的每一记忆细胞的最低有效位、…、及所述最后组块中的每一记忆细胞的最低有效位依序地传送至闪存控制器110以供后续去随机化(de-randomize)运作以及解码运作。[0127]在上述实施例中,若闪存控制器110的解码器134仅使用所述页面的多个记忆细胞的最高有效位就能成功地解码数据,所述多个记忆细胞的最低有效位可不用于解码运作,或者闪存控制器110能通知闪存模块120停止传送最低有效位。[0128]在图9所示的实施例中,映射电路910是设置于闪存模块120中,且闪存模块120传送映射电路910输出的信息至闪存控制器110。在本发明的另一实施例中,映射电路910能被设置于闪存控制器110的控制逻辑电路114中,且闪存模块120传送计数值cnt至闪存控制器110。[0129]图12为依据本发明一第二实施例的感测放大器1200的示意图。在第12途中,感测放大器1200包括一运算放大器1210、一电压源1212、一数字模拟转换器1214以及一开关sw1。在本实施例中,感测放大器1200是用来读取图1所示的对应于位线bl(1)与字线wl(1,nz)的记忆细胞m(1,1,nz)。当记忆细胞m(1,1,nz)将被读取时,模拟数字转换器1214是用来产生读取电压vr至图1所示的记忆细胞m(1,1,nz),而其它记忆细胞m(1,1,1)~m(1,1,(nz-1))被控制为导通。[0130]一并参考图12以及图13,图13为依据本发明一实施例的感测放大器1200的某些信号的时序图。在感测放大器1200的运作中,数字模拟转换器1214一开始并未工作且读取电压vr一开始等于零(即记忆细胞m(1,1,nz)是被停用的),开关sw1被控制以将位线bl(1)连接至电压源1212,而电压源1212开始对寄生电容cbl充电以使得在寄生电容cbl的一端子上的电压vbl于时间t0等于电压源1212所提供的电压vpre。接着,于时间t1,开关sw1被控制以将位线bl(1)连接至运算放大器1210的负端子,数字模拟转换器1214根据一致能信号dac_en以开始产生充当读取电压vr的一斜坡信号至字线wl(1,nz)以控制记忆细胞m(1,1,nz)。例如,假设记忆细胞m(1,1,nz)存储有对应于状态s8(其临界电压约为3v)的数据,当读取电压vr开始由0v升高至3v,由于读取电压vr不够高而无法启用(enable)记忆细胞m(1,1,nz),电压vbl维持在电压vpre,而由于电压vbl/vpre大于运算放大器1210的正端子上的参考电压vsen,运算放大器1210所产生的输出信号vout等于“0”。当读取电压vr于时间t2大于记忆细胞m(1,1,nz)的临界电压,记忆细胞m(1,1,nz)被启用以产生一电流i_cell来对寄生电容cbl放电,而电压vbl会降低。当电压vbl降低而变的低于参考电压vsen,输出信号vout变为“1”以触发数字模拟转换器1214输出对应于当下读取电压vr的数字值。[0131]需注意的是,虽然图13展示了使用所述斜坡信号来充当读取电压vr,但本发明不限于此。在其它实施例中,数字模拟转换器1214能将分别具有不同电压位准的读取电压vr施加于记忆细胞m(1,1,nz)(即分别具有不同电压位准的读取电压vr可分别被视为多个读取电压),读取电压vr可具有任意其它合适的设计。在一实施例中,读取电压vr的电压位准的数量(或读取电压的数量)等于或大于记忆细胞m(1,1,nz)的状态的数量。[0132]在图12与图13所示的实施例中,数字模拟转换器1214输出的数字值能表示记忆细胞m(1,1,nz)的临界电压(即对应于数字模拟转换器1214输出的数字值的模拟电压非常接近记忆细胞m(1,1,nz)的临界电压),所以所述数字值能有效地被用于后续的解码运作。另外,假设数字模拟转换器1214是八位数字模拟转换器,所述数字值可具有图10所示的四个最高有效位以及四个最低有效位,而闪存模块120能以一读取指令直接将所述数字值(即多个最高有效位以及多个最低有效位)传送至闪存控制器110。传送所述读取指令以及所述多个最高有效位/最低有效位的时序图可参考图11。另外,因为电路延迟以及放电时间,数字模拟转换器1214输出的数字值可被略微地调整以使得调整后的数字值更接近记忆细胞m(1,1,nz)的临界电压。[0133]上述实施例是以四阶细胞区块为例,然而上述读取机制亦能应用于三阶细胞区块、多阶细胞区块以及单阶细胞区块。熟习此技艺者应能了解如何使用上述步骤来读取三阶细胞区块、多阶细胞区块以及单阶细胞区块中的记忆细胞,其它细节在此不赘述。[0134]总结来说,在本发明的闪存控制器以及闪存模块中,所述闪存模块能因应一个读取指令将每一记忆细胞的多位信息输出至所述闪存控制器,且每一记忆细胞的多位信息可指出所述记忆细胞的临界电压或状态。因此,读取效率能被大幅地改善。[0135]以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。当前第1页12当前第1页12

再多了解一些

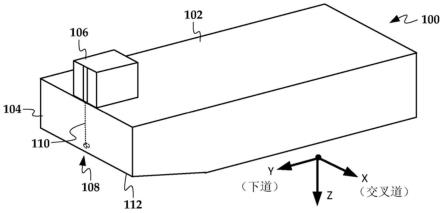

本文用于企业家、创业者技术爱好者查询,结果仅供参考。