1.本发明涉及放大电路。

背景技术:

2.以往,公开了一种放大电路,包含:第1晶体管电路,包含并联连接的多个晶体管;第2晶体管电路,与第1晶体管电路共源共栅(cascode)连接;和多个电容器,与上述多个晶体管各自的栅极连接(例如专利文献1)。由此,通过对包含于第1晶体管电路的并联连接的多个晶体管选择性地供给偏置,从而能够使第1晶体管电路的有效晶体管尺寸变化来调整增益。

3.在先技术文献

4.专利文献

5.专利文献1:国际公开第2019/031553号

6.例如,在上述专利文献1公开的放大电路中,在多个晶体管的并联连接的连接点与输入端子之间,作为输入匹配电路而配置了电感器的情况下,只要增大与该电感器连接的多个电容器的电容,就能够抑制nf(noise figure,噪声系数)值的劣化。然而,若将多个电容器的电容一样地增大,则有导致电路的大型化的担忧。

技术实现要素:

7.发明要解决的课题

8.因此,本发明的目的在于,提供一种容易兼顾nf值的劣化的抑制和电路的大型化的抑制的放大电路。

9.用于解决课题的手段

10.本发明的一个方式涉及的放大电路具备:输入端子;输出端子;放大器,设置在输入端子与输出端子之间,具有并联连接的第1晶体管以及第2晶体管、第1电容器和第2电容器;和电感器,第1晶体管具有与输入端子连接的第1控制端子、与接地连接的第1端子以及与输出端子连接的第2端子,第2晶体管具有与输入端子连接的第2控制端子、与接地连接的第3端子以及与输出端子连接的第4端子,电感器设置在输入端子与第1晶体管以及第2晶体管的并联连接的输入端子侧的连接点之间,第1电容器配置在将上述连接点和第1控制端子连结的路径上,第2电容器配置在将上述连接点和第2控制端子连结的路径上,第1电容器的电容和第2电容器的电容不同。

11.发明效果

12.根据本发明,能够实现容易兼顾nf值的劣化的抑制和电路的大型化的抑制的放大电路。

附图说明

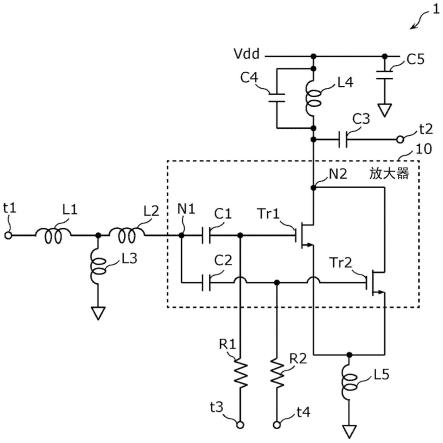

13.图1是示出实施方式1涉及的放大电路的一例的电路结构图。

14.图2是示出实施方式2涉及的放大电路的一例的电路结构图。

15.图3是示出实施方式3涉及的放大电路的一例的电路结构图。

16.图4是示出实施方式4涉及的放大电路的一例的电路结构图。

17.附图标记说明

18.1、1a、1b、1c:放大电路;

19.10、10a、10b、10c:放大器;

20.c1、c2、c3、c4、c5、c6、c7:电容器;

21.l1、l2、l3、l4、l5、l6:电感器;

22.n1、n2:连接点;

23.r1、r2、r3、r4:电阻;

24.t1:输入端子;

25.t2:输出端子;

26.t3、t4、t5、t6:偏置端子;

27.sw1、sw2:开关;

28.tr1、tr2、tr3、tr4:晶体管;

29.vdd 电源。

具体实施方式

30.(以至于得到本发明的一个方式的经过)

31.首先,对以至于得到本发明的一个方式的经过进行说明。

32.为了实现低nf值的放大电路,优选提高作为放大电路的匹配电路而使用的电感器的q值。然而,在将电感器制作为不超过所限制的尺寸的情况下,若要获得大的电感,则q值会下降从而nf值会劣化。只要放宽尺寸的限制就能够提高电感器的q值,但放大电路会大型化、高成本化。

33.因此,通过增大作为放大电路的匹配电路而使用的电容器的电容,从而能够减小电感器的电感。即,能够提高电感器的q值从而抑制nf值的劣化。然而,电容大的电容器的尺寸大,放大电路仍然会大型化、高成本化。特别是,如上述专利文献1公开的放大电路那样具备多个晶体管和与多个晶体管连接的多个电容器的放大电路的情况下,若将多个电容器的电容一样地增大,则放大电路会进一步大型化。

34.因此,以下,对容易兼顾nf值的劣化的抑制和电路的大型化的抑制的放大电路进行说明。

35.以下,利用附图对本发明的实施方式详细进行说明。另外,以下说明的实施方式均示出总括性的或者具体的例子。以下的实施方式中示出的数值、形状、材料、构成要素、构成要素的配置以及连接方式等是一例,主旨并不是对本发明进行限定。关于以下的实施方式中的构成要素之中未记载于独立权利要求的构成要素,作为任意的构成要素进行说明。此外,附图所示的构成要素的大小或者大小之比未必严谨。此外,在各图中,对于实质上相同的结构标注相同的附图标记,有时省略或简化重复的说明。此外,在以下的实施方式中,所谓“连接”,不仅包含直接连接的情况,还包含经由其他元件(例如,电容器或者电感器等)电连接的情况。此外,所谓元件配置在路径上,意味着该元件插入于该路径。

36.(实施方式1)

37.利用图1对实施方式1进行说明。

38.[电路结构]

[0039]

图1是示出实施方式1涉及的放大电路1的一例的电路结构图。

[0040]

放大电路1是对所输入的高频信号进行放大并输出的电路。放大电路1既可以是lna(low noise amplifier,低噪声放大器),也可以是pa(power amplifier,功率放大器)。放大电路1具备输入端子t1、输出端子t2和偏置端子t3以及t4。输入端子t1是输入高频信号的端子,输出端子t2是输出被放大后的高频信号的端子。偏置端子t3以及t4是输入偏置的端子。

[0041]

放大电路1具备放大器10、电感器l1、l2、l3、l4以及l5、电容器c3、c4以及c5和电阻r1以及r2。

[0042]

放大器10设置在输入端子t1与输出端子t2之间。放大器10具有并联连接的晶体管tr1以及tr2、电容器c1和电容器c2。晶体管tr1是第1晶体管的一例,晶体管tr2是第2晶体管的一例,电容器c1是第1电容器的一例,电容器c2是第2电容器的一例。

[0043]

晶体管tr1配置在将输入端子t1和输出端子t2连结的路径上。晶体管tr1例如形成于半导体基板。晶体管tr1具有与输入端子t1连接的第1控制端子、与接地连接的第1端子以及与输出端子t2连接的第2端子。第1控制端子是栅极或者基极,第1端子是源极或者发射极,第2端子是漏极或者集电极。例如,晶体管tr1是mosfet(metal oxide semiconductor field effect transistor,金属氧化物半导体场效应晶体管),在该情况下,第1控制端子成为栅极,第1端子成为源极,第2端子成为漏极。

[0044]

晶体管tr1的栅极经由电感器l1以及l2和电容器c1而与输入端子t1连接,并经由电阻r1而与偏置端子t3连接。晶体管tr1的源极经由电感器l5而与接地连接。晶体管tr1的漏极经由电容器c3而与输出端子t2连接,并经由电感器l4以及电容器c4而与电源vdd连接。

[0045]

晶体管tr2配置在将输入端子t1和输出端子t2连结的路径上。晶体管tr2例如形成于半导体基板。晶体管tr2具有与输入端子t1连接的第2控制端子、与接地连接的第3端子以及与输出端子t2连接的第4端子。第2控制端子是栅极或者基极,第3端子是源极或者发射极,第4端子是漏极或者集电极。例如,晶体管tr2是mosfet,在该情况下,第2控制端子成为栅极,第3端子成为源极,第4端子成为漏极。

[0046]

晶体管tr2的栅极经由电感器l1以及l2和电容器c2而与输入端子t1连接,并经由电阻r2而与偏置端子t4连接。晶体管tr2的源极经由电感器l5而与接地连接。晶体管tr2的漏极经由电容器c3而与输出端子t2连接,并经由电感器l4以及电容器c4而与电源vdd连接。

[0047]

晶体管tr1的栅极和晶体管tr2的栅极连接,晶体管tr1的漏极和晶体管tr2的漏极连接,由此晶体管tr1和晶体管tr2并联连接。

[0048]

例如,晶体管tr1的尺寸大于晶体管tr2的尺寸。具体地,晶体管tr1的栅极的wl比(栅极宽度与栅极长度之比)大于晶体管tr2的栅极的wl比。关于尺寸大的晶体管tr1,增益相对较大,适合对相对较小的高频信号进行放大,要求低nf值的情况较多。关于尺寸小的晶体管tr2,增益相对较小,适合对相对较大的高频信号进行放大,不要求低nf值的情况较多。另外,在晶体管tr1以及tr2为双极晶体管的情况下,晶体管tr1以及tr2的尺寸也可以通过各自的基极的wl比(基极宽度与基极长度之比)来进行比较。

[0049]

电感器l1、l2以及l3是设置在输入端子t1与晶体管tr1以及tr2的并联连接的输入端子t1侧的连接点n1之间的电感器的一例。连接点n1是晶体管tr1的栅极和晶体管tr2的栅极的连接点。设置在输入端子t1与连接点n1之间的电感器既可以是配置在将输入端子t1和连接点n1连结的路径上的电感器,也可以是连接在该路径上的节点与接地之间的电感器。

[0050]

电感器l1配置在将输入端子t1和连接点n1连结的路径上。电感器l1构成用于晶体管tr1以及tr2的输入阻抗的匹配的输入匹配电路。电感器l1也可以呈线圈状或者螺旋状形成在形成了晶体管tr1以及tr2的半导体基板。

[0051]

电感器l2在将输入端子t1和连接点n1连结的路径上与电感器l1串联连接。电感器l2构成用于晶体管tr1以及tr2的输入阻抗的匹配的输入匹配电路。电感器l2也可以呈线圈状或者螺旋状形成在形成了晶体管tr1以及tr2的半导体基板。

[0052]

电感器l3连接在将输入端子t1和连接点n1连结的路径上的节点(具体地为将电感器l1和电感器l2连结的路径上的节点)与接地之间。电感器l3构成用于晶体管tr1以及tr2的输入阻抗的匹配的输入匹配电路。电感器l3也可以呈线圈状或者螺旋状形成在形成了晶体管tr1以及tr2的半导体基板。

[0053]

电容器c1配置在将连接点n1和晶体管tr1的栅极连结的路径上。电容器c1构成用于晶体管tr1的输入阻抗的匹配的输入匹配电路。此外,电容器c1作为阻止输入到偏置端子t3的偏置向输入端子t1泄漏的dc截止用的电容器而发挥功能。电容器c1也可以形成在形成了晶体管tr1以及tr2的半导体基板。

[0054]

电容器c2配置在将连接点n1和晶体管tr2的栅极连结的路径上。电容器c2构成用于晶体管tr2的输入阻抗的匹配的输入匹配电路。此外,电容器c2作为阻止输入到偏置端子t4的偏置向输入端子t1泄漏的dc截止用的电容器而发挥功能。电容器c2也可以形成在形成了晶体管tr1以及tr2的半导体基板。

[0055]

电容器c1的电容和电容器c2的电容不同。例如,电容相互不同的电容器c1以及c2中,电极的形状或者大小不同。所谓电容不同,例如,意味着一个电容器的电容相对于另一个电容器的电容相差5%以上。换言之,在一个电容器的电容和另一个电容器的电容之差小于5%的情况下,也可以视为各电容器的电容相同。例如,与尺寸大的晶体管tr1连接的电容器c1的电容大于与尺寸小的晶体管tr2连接的电容器c2的电容。

[0056]

此外,布线由于具有电感成分,因此能够用于对将连接点n1和电容器c1连接的布线以及将连接点n1和电容器c2连接的布线进行阻抗匹配。此时,例如,将连接点n1和电容器c1连接的布线的布线长度也可以比将连接点n1和电容器c2连接的布线的布线长度短。也就是说,将连接点n1和电容器c1连接的布线的电感成分也可以小于将连接点n1和电容器c2连接的布线的电感成分。

[0057]

电容器c3配置在将晶体管tr1以及晶体管tr2的并联连接的输出端子t2侧的连接点n2和输出端子t2连结的路径上。连接点n2是晶体管tr1的漏极和晶体管tr2的漏极的连接点。电容器c3构成用于晶体管tr1以及tr2的输出阻抗的匹配的输出匹配电路。此外,电容器c3还作为阻止来自电源vdd的直流电流向输出端子t2泄漏的dc截止用的电容器而发挥功能。

[0058]

电容器c4配置在将连接点n2和电源vdd连结的路径上。电容器c4构成用于晶体管tr1以及tr2的输出阻抗的匹配的输出匹配电路。

[0059]

电感器l4在将连接点n2和电源vdd连结的路径上与电容器c4并联连接。电感器l4构成用于晶体管tr1以及tr2的输出阻抗的匹配的输出匹配电路。此外,电感器l4还作为与电源vdd连接的扼流电感器而发挥功能。

[0060]

电容器c5连接在电源vdd与接地之间。电容器c5作为旁路电容器而发挥功能,但也有时构成用于晶体管tr1以及tr2的输出阻抗的匹配的输出匹配电路。

[0061]

电感器l5连接在晶体管tr1的源极以及晶体管tr2的源极与接地之间。电感器l5是用于改善晶体管tr1以及tr2的线性度的源极退化电感器。

[0062]

在晶体管tr1的栅极以及晶体管tr2的栅极分别连接用于供给偏置的偏置电阻。

[0063]

电阻r1是配置在将晶体管tr1的栅极和偏置端子t3连结的路径上的偏置电阻。

[0064]

电阻r2是配置在将晶体管tr2的栅极和偏置端子t4连结的路径上的偏置电阻。

[0065]

在放大器10中,也可以从晶体管tr1以及tr2之中切换用于放大的晶体管。例如,既可以是晶体管tr1用于放大并且晶体管tr2不用于放大,也可以是晶体管tr2用于放大并且晶体管tr1不用于放大。或者,还可以是晶体管tr1以及tr2这两者都用于放大。

[0066]

例如,作为从晶体管tr1以及tr2之中切换用于放大的晶体管的方法,有利用偏置控制的方法。

[0067]

通过不向晶体管的栅极供给偏置,从而能够使得该晶体管不驱动。例如,通过使得向晶体管tr1的栅极供给偏置而不向晶体管tr2的栅极供给偏置,从而能够利用晶体管tr1对高频信号进行放大。例如,通过使得向晶体管tr2的栅极供给偏置而不向晶体管tr1的栅极供给偏置,从而能够利用晶体管tr2对高频信号进行放大。例如,通过向晶体管tr1以及tr2的栅极供给偏置,从而能够利用晶体管tr1以及tr2这两者对高频信号进行放大。另外,在进行利用了晶体管tr1以及tr2这两者的放大时,向晶体管tr1的栅极供给的偏置和向晶体管tr2的栅极供给的偏置也可以不同。

[0068]

另外,既可以在进行利用了晶体管tr1的放大时,向晶体管tr2供给比向晶体管tr1供给的偏置小的微小偏置,也可以在进行利用了晶体管tr2的放大时,向晶体管tr1供给比向晶体管tr2供给的偏置小的微小偏置。

[0069]

此外,例如,作为从晶体管tr1以及tr2之中切换用于放大的晶体管的方法,还有利用开关控制的方法,但关于此将在后面叙述。

[0070]

此外,晶体管tr1也可以为双极晶体管。在该情况下,第1控制端子成为基极,第1端子成为发射极,第2端子成为集电极。此外,晶体管tr2也可以为双极晶体管。在该情况下,第2控制端子成为基极,第3端子成为发射极,第4端子成为集电极。在上述的说明以及以下的说明中,也可以将采用栅极的地方替换为基极,也可以将采用源极的地方替换为发射极,也可以将采用漏极的地方替换为集电极。

[0071]

[效果等]

[0072]

放大电路1具备:输入端子t1;输出端子t2;放大器10,设置在输入端子t1与输出端子t2之间,具有并联连接的晶体管tr1以及tr2、电容器c1和电容器c2;和电感器l1、l2或者l3。晶体管tr1具有与输入端子t1连接的栅极、与接地连接的源极以及与输出端子t2连接的漏极,晶体管tr2具有与输入端子t1连接的栅极、与接地连接的源极以及与输出端子t2连接的漏极。电感器l1、l2或者l3设置在输入端子t1与晶体管tr1以及tr2的并联连接的输入端子t1侧的连接点n1之间。电容器c1配置在将连接点n1和晶体管tr1的栅极连结的路径上,电

容器c2配置在将连接点n1和晶体管tr2的栅极连结的路径上,电容器c1的电容和电容器c2的电容不同。

[0073]

由此,减小了电容器c1以及c2之中的任意一个电容器的电容,因此与将电容器c1以及c2的电容一样地增大时相比,能够抑制电路的大型化。此外,增大了电容器c1以及c2之中的任意一个电容器的电容,因此能够抑制nf值的劣化。

[0074]

像这样,通过使电容器c1的电容和电容器c2的电容不同,从而能够实现容易兼顾nf值的劣化的抑制和电路的大型化的抑制的放大电路1。

[0075]

例如,晶体管tr1的尺寸也可以大于晶体管tr2的尺寸,电容器c1的电容也可以大于电容器c2的电容。

[0076]

关于尺寸大的晶体管tr1,增益相对较大,适合对相对较小的高频信号进行放大,要求低nf值的情况较多。因此,通过增大与晶体管tr1连接的电容器c1的电容,从而能够实现低nf值。另一方面,关于尺寸小的晶体管tr2,增益相对较小,适合对相对较大的高频信号进行放大,不要求低nf值的情况较多。因此,能够减小与晶体管tr2连接的电容器c2的电容。由此,能够有效地进行nf值的劣化的抑制和电路的大型化的抑制。

[0077]

例如,将连接点n1和电容器c1连接的布线的布线长度也可以比将连接点n1和电容器c2连接的布线的布线长度短。

[0078]

由此,与将电容器c2的电容减小的量相应地,通过增长将连接点n1和电容器c2连接的布线的布线长度,从而能够弥补用于晶体管tr2的输入阻抗的匹配所不足的电感成分。

[0079]

例如,在放大器10中,也可以从晶体管tr1以及tr2之中切换用于放大的晶体管。

[0080]

由此,能够根据状况,从晶体管tr1以及tr2之中将最适合的晶体管用于放大。

[0081]

例如,在对相对较小的高频信号进行放大时,尺寸大的晶体管tr1用于放大,要求低nf值的情况较多。由于与晶体管tr1连接的电容器c1的电容大,因此对电感器l1、l2或者l3要求的电感变小,能够增大能以所限制的尺寸实现的q值。因此,能够在保持用于对相对较小的高频信号进行放大所需的一定以上的增益的同时利用电容大的电容器c1来实现低nf值。

[0082]

例如,在对相对较大的高频信号进行放大时,尺寸小的低消耗电流的晶体管tr2用于放大,在该情况下,不要求低nf值的情况较多。由于不要求低nf值,因此与晶体管tr2连接的电容器c2的电容也可以较小,能够实现低消耗电流以及电路的小型化。

[0083]

像这样,在大增益用的晶体管tr1用于放大的情况下,与晶体管tr1连接的电容器c1的电容大,因此能够降低nf值,在小增益用的晶体管tr2用于放大的情况下,与晶体管tr2连接的电容器c2的电容小,因此能够将电路小型化。因此,能够实现无论大增益还是小增益都能应对并且容易兼顾nf值的劣化的抑制和电路的大型化的抑制的放大电路1。

[0084]

另外,也可以将晶体管tr1以及tr2这两者、还有包含晶体管tr1以及tr2的多个晶体管用于放大,通过从多个晶体管中任意地组合用于放大的晶体管,从而能够设计成为任意的增益、nf值以及消耗电流的放大电路。此时,通过使与各晶体管连接的电容器的电容不同,从而能够提高设计的自由度。具体地,在使各晶体管单独进行动作时或者使各晶体管同时进行动作时,能够调整各电容器的电容使得分别成为最佳的输入阻抗。

[0085]

例如,在晶体管tr1的栅极以及晶体管tr2的栅极也可以分别连接用于供给偏置的电阻r1以及r2。

[0086]

由用于供给偏置的电阻r1以及r2和电容器c1以及c2来决定电路的启动时间或者开关控制的切换时间等时间常数。在本发明中,由于减小了电容器c1以及c2之中的任意一个电容器的电容,因此与将电容器c1以及c2的电容一样地增大时相比,能够减小时间常数,能够缩短电路的启动时间或者开关控制的切换时间等。

[0087]

例如,晶体管tr1以及晶体管tr2和电容器c1以及c2也可以形成于半导体基板。

[0088]

由此,通过将电容器c1以及c2形成于半导体基板,从而能够减小电容器c1以及c2的尺寸,进而能够将放大电路1小型化。

[0089]

例如,电感器l1、l2或者l3也可以呈线圈状形成于半导体基板。

[0090]

形成于半导体基板的线圈状的电感器在形成为与外置地形成的情况相同的电感(具体地为相同的卷绕数)的情况下,为了在所限制的尺寸下增多卷绕数,线宽度容易变小从而q值容易变小。但是,在本发明中,能够减小原本需要的电感,因此可以不太增加卷绕数,即使将电感器形成于半导体基板也不易成为问题。换言之,在本发明中,能够增加将电感器形成于半导体基板这样的选项。因此,在电感器l1、l2或者l3呈线圈状形成于半导体基板的情况下,能够有用地应用本发明。

[0091]

(实施方式2)

[0092]

接着,利用图2对实施方式2进行说明。

[0093]

[电路结构]

[0094]

图2是示出实施方式2涉及的放大电路1a的一例的电路结构图。

[0095]

实施方式2涉及的放大电路1a与实施方式1涉及的放大电路1的不同点在于,取代放大器10而具备放大器10a。其他方面与实施方式1中的相同,因此省略说明。此外,关于放大器10a,也在还具备开关sw1以及sw2这一点上与实施方式1涉及的放大器10不同,其他方面与实施方式1中的相同,因此省略说明。

[0096]

开关sw1与晶体管tr1的源极连接,开关sw2与晶体管tr2的源极连接。

[0097]

例如,作为从晶体管tr1以及tr2之中切换用于放大的晶体管的方法,有利用开关控制的方法。

[0098]

开关sw1是配置在将晶体管tr1的源极和接地连结的路径上的串联开关,开关sw2是配置在将晶体管tr2的源极和接地连结的路径上的串联开关。例如,通过将开关sw1设为导通状态,并将开关sw2设为非导通状态,从而能够利用晶体管tr1对高频信号进行放大。例如,通过将开关sw1设为非导通状态,并将开关sw2设为导通状态,从而能够利用晶体管tr2对高频信号进行放大。例如,通过将开关sw1以及sw2设为导通状态,从而能够利用晶体管tr1以及tr2这两者对高频信号进行放大。

[0099]

像这样,也可以通过开关的控制而从晶体管tr1以及tr2之中切换用于放大的晶体管。另外,作为从晶体管tr1以及tr2之中切换用于放大的晶体管的方法,也可以使用利用偏置控制的方法以及利用开关控制的方法这两者。例如,在晶体管tr1用于放大的情况下,也可以向晶体管tr1的栅极供给偏置,并且,开关sw1被设为导通状态。

[0100]

(实施方式3)

[0101]

接着,利用图3对实施方式3进行说明。

[0102]

[电路结构]

[0103]

图3是示出实施方式3涉及的放大电路1b的一例的电路结构图。

[0104]

实施方式3涉及的放大电路1b与实施方式1涉及的放大电路1的不同点在于,取代放大器10而具备放大器10b,且还具备偏置端子t5、电阻r3以及电容器c6。其他方面与实施方式1中的相同,因此省略说明。此外,关于放大器10b,也在还具备晶体管tr3这一点上与实施方式1涉及的放大器10不同,其他方面与实施方式1中的相同,因此省略说明。

[0105]

偏置端子t5是输入偏置的端子。

[0106]

晶体管tr3是与晶体管tr1以及晶体管tr2共源共栅连接的第3晶体管的一例。例如,晶体管tr3配置在将连接点n2和输出端子t2连结的路径上,晶体管tr1、tr2以及tr3构成共源共栅放大器。例如,晶体管tr3是mosfet。晶体管tr1以及tr2各自的漏极经由晶体管tr3而与输出端子t2连接。

[0107]

晶体管tr3的栅极经由电阻r3而与偏置端子t5连接,并经由电容器c6而与接地连接。晶体管tr3的源极与晶体管tr1的漏极以及晶体管tr2的漏极连接。晶体管tr3的漏极经由电容器c3而与输出端子t2连接,并经由电感器l4以及电容器c4而与电源vdd连接。

[0108]

电容器c6是连接在将晶体管tr3的栅极和偏置端子t5连结的路径上的节点与接地之间的旁路电容器。

[0109]

电阻r3是配置在将晶体管tr3的栅极和偏置端子t5连结的路径上的偏置电阻。

[0110]

另外,晶体管tr3也可以配置在将晶体管tr1的漏极和连接点n2连结的路径上,晶体管tr1以及tr3也可以构成共源共栅放大器。此外,晶体管tr3也可以配置在将晶体管tr2的漏极和连接点n2连结的路径上,晶体管tr2以及tr3也可以构成共源共栅放大器。

[0111]

另外,晶体管tr3也可以为双极晶体管,在上述的说明以及以下的说明中能够将晶体管tr3的栅极、源极以及漏极替换为基极、发射极以及集电极。

[0112]

[效果等]

[0113]

例如,放大器10b也可以还具备与晶体管tr1以及tr2共源共栅连接的晶体管tr3。

[0114]

由此,能够实现可得到更大的增益的放大电路1b。

[0115]

(实施方式4)

[0116]

接着,利用图4对实施方式4进行说明。

[0117]

[电路结构]

[0118]

图4是示出实施方式4涉及的放大电路1c的一例的电路结构图。

[0119]

实施方式4涉及的放大电路1c与实施方式3涉及的放大电路1b的不同点在于,取代放大器10b而具备放大器10c,取代电感器l1、l2以及l3而具备电感器l6,且还具备偏置端子t6以及电阻r4。其他方面与实施方式3中的相同,因此省略说明。此外,关于放大器10c,也在还具备晶体管tr4以及电容器c7这一点上与实施方式3涉及的放大器10b不同,其他方面与实施方式3中的相同,因此省略说明。

[0120]

偏置端子t6是输入偏置的端子。

[0121]

晶体管tr4配置在将输入端子t1和输出端子t2连结的路径上。例如,晶体管tr4是mosfet。

[0122]

晶体管tr4的栅极经由电感器l6以及电容器c7而与输入端子t1连接,并经由电阻r4而与偏置端子t6连接。另外,在实施方式4中,晶体管tr1的栅极经由电感器l6以及电容器c1而与输入端子t1连接,晶体管tr2的栅极经由电感器l6以及电容器c2而与输入端子t1连接。晶体管tr4的源极经由电感器l5而与接地连接。晶体管tr4的漏极经由晶体管tr3以及电

容器c3而与输出端子t2连接,并经由晶体管tr3、电感器l4以及电容器c4而与电源vdd连接。

[0123]

晶体管tr1的栅极、晶体管tr2的栅极和晶体管tr4的栅极连接,晶体管tr1的漏极、晶体管tr2的漏极和晶体管tr4的漏极连接,由此晶体管tr1、晶体管tr2和晶体管tr4并联连接。

[0124]

电感器l6是设置在输入端子t1与晶体管tr1、tr2以及tr4的并联连接的输入端子t1侧的连接点n1之间的电感器的一例。电感器l6配置在将输入端子t1和连接点n1连结的路径上。电感器l6构成用于晶体管tr1、tr2以及tr4的输入阻抗的匹配的输入匹配电路。像这样,也可以在输入端子t1与连接点n1之间设置一个电感器l6。

[0125]

电容器c7配置在将连接点n1和晶体管tr4的栅极连结的路径上。电容器c7构成用于晶体管tr4的输入阻抗的匹配的输入匹配电路。此外,电容器c7作为阻止输入到偏置端子t6的偏置向输入端子t1泄漏的dc截止用的电容器而发挥功能。

[0126]

电容器c1的电容、电容器c2的电容和电容器c7的电容不同。

[0127]

电阻r4是配置在将晶体管tr4的栅极和偏置端子t6连结的路径上的偏置电阻。

[0128]

另外,晶体管tr4也可以为双极晶体管,在上述的说明以及以下的说明中能够将晶体管tr4的栅极、源极以及漏极替换为基极、发射极以及集电极。

[0129]

也可以如实施方式4涉及的放大电路1c那样具备并联连接的3个以上的晶体管,即使在该情况下,也与实施方式1等相同地,通过使与各晶体管连接的电容器的电容不同,从而能够实现容易兼顾nf值的劣化的抑制和电路的大型化的抑制的放大电路。

[0130]

(其他实施方式)

[0131]

以上,列举实施方式对本发明涉及的放大电路进行了说明,但本发明不限定于上述实施方式。组合上述实施方式中的任意的构成要素而实现的其他的实施方式、在不脱离本发明的主旨的范围内对上述实施方式实施本领域技术人员想到的各种变形而得到的变形例、内置了本发明涉及的放大电路的各种设备也包含于本发明。

[0132]

例如,在上述实施方式中,对晶体管tr1的尺寸大于晶体管tr2的尺寸且电容器c1的电容大于电容器c2的电容的例子进行了说明,但不限于此。例如,在晶体管tr1的尺寸大于晶体管tr2的尺寸的情况下,电容器c1的电容也可以小于电容器c2的电容。

[0133]

例如,在上述实施方式中,对将连接点n1和电容器c1连接的布线的布线长度比将连接点n1和电容器c2连接的布线的布线长度短的例子进行了说明,但不限于此。例如,将连接点n1和电容器c1连接的布线的布线长度也可以比将连接点n1和电容器c2连接的布线的布线长度长,还可以为相同长度。

[0134]

例如,在上述实施方式中,对从晶体管tr1以及tr2之中切换用于放大的晶体管的例子进行了说明,但也可以不切换用于放大的晶体管。

[0135]

例如,在上述实施方式中,对晶体管tr1以及tr2和电容器c1以及c2形成于半导体基板的例子进行了说明,但晶体管tr1以及tr2和电容器c1以及c2也可以不形成于半导体基板。

[0136]

例如,在上述实施方式中,对电感器l1、l2或者l3呈线圈状形成于半导体基板的例子进行了说明,但电感器l1、l2或者l3也可以不呈线圈状形成于半导体基板。

[0137]

产业上的可利用性

[0138]

本发明作为对高频信号进行放大的放大电路,能够广泛利用于便携式电话等通信

设备。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。