1.本发明关于一种控制装置,特别是关于一种用于减少器件的使用接脚的控制装置与显示装置。

背景技术:

2.一般来说,部分的显示装置需要通过序列周边接口(serial peripheral interface,spi),来设定显示装置的内部暂存器,以调整显示装置的显示特性(例如解析度等)。然而,显示装置的控制器会使用3个接脚分别提供spi控制信号、spi时钟信号、spi数据信号,以便显示装置可以对应地设定及调整显示特性。由于对显示装置的显示特性进行设定会占用到显示装置的控制器的3个接脚,会使控制器的使用功能受到局限,而降低使用上的便利性。

3.因此,如何有效地减少控制器的使用接脚的数量是当前重要的课题。

技术实现要素:

4.本发明提供一种控制装置与显示装置,借以有效地减少器件的使用接脚的数量,以便有空出来的接脚进行功能扩充,并可维持正常显示功能,以增加使用上的便利性。

5.本发明提供一种控制装置,适用于显示装置。控制装置包括控制模块。控制模块具有第一接脚、第二接脚、第三接脚与第四接脚。控制模块的第一接脚提供控制信号。控制模块的第二接脚提供时钟信号。控制模块的第三接脚提供数据信号,且数据信号包括显示数据与配置设定数据。控制模块的第四接脚提供垂直同步信号。在垂直同步信号的使能期间,控制模块提供第一准位的控制信号、时钟信号与包括配置设定数据的数据信号给显示装置,使显示模块依据控制信号、时钟信号与配置设定数据进行配置设定。在垂直同步信号的禁能期间,控制模块提供第二准位的控制信号、时钟信号与包括显示数据的数据信号给显示装置,使显示模块依据控制信号、时钟信号与显示数据进行正常显示。

6.本发明提供一种显示装置,包括控制模块与显示模块。控制模块具有第一接脚、第二接脚、第三接脚与第四接脚,控制模块的第一接脚提供控制信号,控制模块的第二接脚提供时钟信号,控制模块的第三接脚提供数据信号,且数据信号包括显示数据与配置设定数据。显示模块具有第一接脚、第二接脚、第三接脚、第四接脚、第五接脚与第六接脚。显示模块的该第一接脚耦接控制模块的第一接脚。显示模块的第二接脚与第三接脚耦接控制模块的第二接脚。显示模块的第四接脚与第五接脚耦接控制模块的第三接脚。显示模块的第六接脚耦接控制模块的第四接脚。在垂直同步信号的使能期间,控制模块提供第一准位的控制信号、时钟信号与包括配置设定数据的数据信号给显示模块,使显示模块依据控制信号、时钟信号与配置设定数据进行配置设定。在垂直同步信号的禁能期间,控制模块提供第二准位的控制信号、时钟信号与包括显示数据的数据信号给显示模块,使显示模块依据控制信号、时钟信号与显示数据进行正常显示。

7.本发明所述的控制装置与显示装置,通过控制模块的第一接脚提供控制信号,控

制模块的第二接脚提供时钟信号,控制模块的第三接脚提供数据信号,且数据信号包括显示数据与配置设定数据,且在垂直同步信号的使能期间,控制模块提供第一准位的控制信号、时钟信号与包括配置设定数据的数据信号给显示模块(显示装置),使显示模块依据控制信号、时钟信号与配置设定数据进行配置设定,以及在垂直同步信号的禁能期间,控制模块提供第二准位的控制信号、时钟信号与包括显示数据的数据信号给显示模块(显示装置),使显示模块(显示装置)依据控制信号、时钟信号与显示数据进行正常显示。另外,显示模块的第二接脚与第三接脚可以共用控制模块的第二接脚以及显示模块的第四接脚与第五接脚可以共用控制模块的第三接脚。如此一来,可以有效地减少控制模块的使用接脚的数量,使控制模块可以有空出来的接脚对控制模块的功能进行扩充,并可维持显示模块的正常显示功能,以增加使用上的便利性。

附图说明

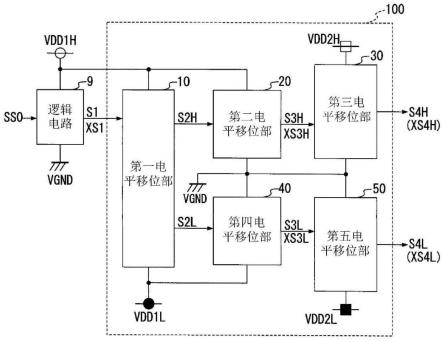

8.图1为依据本发明的一实施例的显示装置的示意图。

9.图2为依据本发明的一实施例的垂直同步信号与水平同步信号的波形图。

10.图3为图2的水平同步信号的一部分、控制信号、时钟信号、数据信号、数据显示指示信号的波形图。

11.图4为图2的水平同步信号的另一部分、控制信号、时钟信号、数据信号、数据显示指示信号的波形图。附图说明

[0012][0013]

100:显示装置

[0014]

110:控制模块

[0015]

111,131:第一接脚

[0016]

112,132:第二接脚

[0017]

113,133:第三接脚

[0018]

114,134:第四接脚

[0019]

115,135:第五接脚

[0020]

116,136:第六接脚

[0021]

130:显示模块

[0022]

137:第七接脚

[0023]

138:第八接脚

[0024]

cs:控制信号

[0025]

clk:时钟信号

[0026]

dat:数据信号

[0027]

vsync:垂直同步信号

[0028]

hsync:水平同步信号

[0029]

de:数据显示指示信号

[0030]

tf:画面期间

[0031]

te:使能期间

[0032]

td:禁能期间

[0033]

th1,th2:水平同步期间

[0034]

d:显示数据

[0035]

inv:无效数据

[0036]

csd:配置设定数据

具体实施方式

[0037]

在以下所列举的各实施例中,将以相同的标号代表相同或相似的器件或组件。

[0038]

图1为依据本发明的一实施例的显示装置的示意图。请参考图1,显示装置100可以包括控制模块110与显示模块130。在本实施例中,控制模块110例如为微控制器(micro control unit,mcu)、微处理器(micro processor)或中央处理器(central processing unit,cpu),显示模块130例如为液晶显示器(liquid crystal display,lcd)。

[0039]

控制模块110可以至少具有第一接脚111、第二接脚112、第三接脚113、第四接脚114、第五接脚115与第六接脚116。

[0040]

控制模块110的第一接脚111(例如为序列周边接口(spi)的控制信号接脚)提供控制信号cs。控制模块110的第二接脚112(例如为显示器接口的时钟信号接脚)提供时钟信号clk,控制模块110的第三接脚113(例如为显示器接口的数据信号接脚)提供数据信号dat。另外,数据信号dat包括显示数据与配置设定数据。控制模块110的第四接脚114(例如为显示器接口的垂直同步信号接脚)提供垂直同步信号vsync。控制模块110的第五接脚115(例如为显示器接口的水平同步信号接脚)提供水平同步信号hsync。控制模块110的第六接脚116(例如为显示器接口的数据显示指示信号接脚)提供数据显示指示信号de。

[0041]

显示模块130可以至少具有第一接脚131、第二接脚132、第三接脚133、第四接脚134、第五接脚135、第六接脚136、第七接脚137与第八接脚138。

[0042]

显示模块130的第一接脚131(例如为spi的控制信号接脚)耦接控制模块110的第一接脚111,接收控制信号cs。显示模块130的第二接脚132(例如为spi的时钟信号接脚)与第三接脚133(例如为显示器接口的时钟信号接脚)耦接控制模块110的第二接脚112,接收时钟信号clk。显示模块130的第四接脚134(例如为spi的数据信号接脚)与第五接脚135(例如为显示器接口的时钟信号接脚)耦接控制模块110的第三接脚113,接收数据信号dat。

[0043]

显示模块130的第六接脚136(例如为显示器接口的垂直同步信号接脚)耦接控制模块110的第四接脚114,接收垂直同步信号vsync。显示模块130的第七接脚137(例如为显示器接口的水平同步信号接脚)耦接控制模块110的第五接脚115,接收水平同步信号hsync。显示模块130第八接脚138(例如为显示器接口的数据显示指示信号接脚)耦接控制模块110的第六接脚116,接收数据显示指示信号de。

[0044]

在垂直同步信号vsync的使能期间,控制模块110提供第一准位的控制信号cs、时钟信号clk与包括配置设定数据的数据信号dat给显示模块130,使显示模块130可以依据控制信号cs、时钟信号clk与配置设定数据进行配置设定。在本实施例中,在垂直同步信号vsync的使能期间,控制信号cs可以作为spi控制信号,时钟信号clk可以作为spi时钟信号,数据信号dat可以作为spi数据信号。另外,本实施例的垂直同步信号vsync例如为负缘触发,亦即在垂直同步信号vsync的使能期间,垂直同步信号vsync为低逻辑准位,但本发明实

施例不限于此。在其他实施例中,垂直同步信号vsync也可以为正缘触发,亦即在垂直同步信号vsync的使能期间,垂直同步信号vsync为高逻辑准位。

[0045]

举例来说,控制模块110的第一接脚111可以提供第一准位(例如低逻辑准位)的控制信号cs,控制模块110的第二接脚112可以提供时钟信号clk、控制模块110的第三接脚113可以提供包括配置设定数据的数据信号dat给显示模块130。

[0046]

此时,显示模块130的第一接脚131接收提供第一准位(例如低逻辑准位)的控制信号cs,显示模块130的第二接脚132接收时钟信号clk,显示模块130的第四接脚134接收包括配置设定数据的数据信号dat。接着,显示模块130可以依据第一准位(例如低逻辑准位)的控制信号cs、时钟信号clk与数据信号dat的配置设定数据进行配置设定。

[0047]

在本实施例中,配置设定数据包括显示模块130的解析度、图像格式等初始设定,但本发明实施例不限于此。举例来说,显示模块130可以利用数据信号dat的配置设定数据,对显示模块130的内部暂存器(internal register)进行配置设定,使得显示模块130可以依据所设定的解析度、图像格式,显示对应的显示画面。

[0048]

另一方面,在垂直同步信号vsync的使能期间,控制模块110的第六接脚116可以提供例如低逻辑准位的数据显示指示信号de(例如数据显示指示信号de的禁能期间)。此时,显示模块130的第三接脚133接收时钟信号clk、显示模块130的第五接脚135接收包括配置设定数据的数据信号dat,显示模块130的第八接脚138接收低逻辑准位的数据显示指示信号de。由于数据显示指示信号de为低逻辑准位,表示数据显示指示信号de的禁能期间,因此显示模块130会忽略显示模块130的第三接脚133所接收的时钟信号clk与显示模块130的第五接脚135所接收的包括配置设定数据的数据信号dat,亦即显示模块130不会对包括配置设定数据的数据信号dat进行显示。

[0049]

在垂直同步信号vsync的禁能期间,控制模块110提供第二准位的控制信号cs、时钟信号clk与包括显示数据的数据信号dat给显示模块130,使显示模块130依据控制信号cs、时钟信号clk与显示数据进行正常显示。在本实施例中,在垂直同步信号vsync的禁能期间,时钟信号clk可以作为显示器接口的时钟信号,数据信号dat可以作为显示器接口的数据信号。另外,在垂直同步信号vsync的禁能期间,垂直同步信号vsync例如为高逻辑准位。

[0050]

举例来说,控制模块110的第一接脚111可以提供第二准位(例如高逻辑准位)的控制信号cs,控制模块110的第二接脚112可以提供时钟信号clk,控制模块110的第三接脚113可以提供包括显示数据的数据信号dat。

[0051]

此时,显示模块130的第一接脚131接收提供第二准位的控制信号cs,显示模块130的第二接脚132接收时钟信号clk、显示模块130的第四接脚134接收包括显示数据的数据信号dat。由于控制信号cs为高逻辑准位,因此显示模块130会忽略显示模块130的第二接脚132所接收的时钟信号clk与显示模块130的第四接脚134所接收的包括显示数据的数据信号dat,亦即显示模块130不会对内部暂存器进行配置设定。

[0052]

另一方面,在显示模块130的垂直同步信号vsync的禁能期间,控制模块110的第六接脚116可以提供例如高逻辑准位的数据显示指示信号de(例如数据显示指示信号de的使能期间)。此时,显示模块130的第三接脚133接收时钟信号clk,显示模块130的第五接脚135接收包括显示数据的数据信号dat,显示模块130的第八接脚138接收高逻辑准位的数据显示指示信号de。接着,显示模块130可以依据高逻辑准位的数据显示指示信号de、时钟信号

clk与包括显示数据的数据信号dat进行正常显示,亦即显示模块130可以在数据显示指示信号de的使能期间,通过时钟信号clk来显示包括显示数据的数据信号dat。

[0053]

在本实施例中,每个垂直同步信号vsync的使能期间会包括数条扫描线(scanning line),且这些扫描线可以分别对应水平同步信号hsync的一个水平同步期间,亦即垂直同步信号vsync的使能期间可以包括水平同步信号hsync的多个水平同步期间。另外,每条扫描线会依据显示模块130的解析度而具有对应数量的时钟信号clk的时钟脉波,亦即水平同步期间的每一者包括时钟信号clk的多个时钟脉波。此外,每条扫描线所具有的时钟信号clk的时钟脉波的数量会依据显示模块的130不同解析度而不同。

[0054]

举例来说,假设显示模块130的解析度为640x480,则每条扫描线至少有640个时钟脉波,亦即水平同步期间的每一者包括时钟信号clk的640个时钟脉波。若垂直同步信号vsync的使能期间有10条扫描线,则垂直同步信号vsync的使能期间会有时钟信号clk的6,400(640*10)个时钟脉波,而此6,400个时钟脉波就可以作为spi时钟信号使用。如此一来,显示模块130就可以在6,400个时钟脉波的期间,利用数据信号dat的配置设定数据对显示模块130的内部暂存器的配置设定。

[0055]

另外,若垂直同步信号vsync的使能期间有2条扫描线,则垂直同步信号vsync的使能期间会有时钟信号clk的1,280(640*2)个时钟脉波,而此1,280个时钟脉波可以作为spi时钟信号使用。其余则类推。上述显示模块130的解析度为640x480仅为本发明的一种实施范例,但本发明实施例不限于此。使用者可视其需求调整垂直同步信号vsync的使能期间所包括的扫描线的数量,亦即垂直同步信号vsync的使能期间所包括的水平同步信号hsync的水平同步期间的数量。

[0056]

另外,控制信号cs的第一准位与控制信号的cs的第二准位可以为互补。举例来说,当控制信号cs的第一准位为低逻辑准位时,控制信号的cs的第二准位为高逻辑准位,如前述实施例的例子。但本发明实施例不限于此。在一些实施例中,当控制信号cs的第一准位为高逻辑准位时,控制信号的cs的第二准位为低逻辑准位。

[0057]

借由上述实施例的说明,可知本实施例的显示模块130的第二接脚132(例如spi的时钟信号接脚)与第三接脚133(例如显示接口的时钟信号接脚)可以共用控制模块110的第二接脚112(例如显示器接口的时钟接脚)以及显示模块130的第四接脚(例如spi的数据信号接脚)134与第五接脚135(例如显示器接口的数据信号接脚可以共用控制模块110的第三接脚113(例如显示器接口的数据信号接脚),并通过控制模块110在垂直同步信号vsync的使能期间与禁能期间,分别提供对应的控制信号、时钟信号与数据信号给显示模块130,使得显示模块130可以进行配置设定或正常显示。如此一来,可以有效地减少控制模块110的使用接脚的数量,亦即减少控制模块110产生spi时钟信号与spi数据信号的接脚,以达成使用在显示装置100上的简化串列周边接口(simplified serial peripheral interface)的效果。另外,由于控制模块110的使用接脚的数量减少,使控制模块110可以有空出来的接脚对控制模块110的功能进行扩充,并可维持显示模块130的正常显示功能,以增加使用上的便利性。

[0058]

在图1中,控制模块110的第三接脚113与显示模块130的第五接脚115绘示为1个。但实际上,显示装置100可以具有多条数据信号线,亦即控制模块110与显示器模块130可以具有多个数据信号接脚,其中控制模块110的第三接脚113与显示模块130的第五接脚135为

上述数据信号接脚的其中一个。另外,不同的显示装置100会具有不同数量的数据信号线。

[0059]

举例来说,当显示装置100有8条数据信号线时,控制模块110与显示器模块130可以具有8个数据信号接脚,其中控制模块110的第三接脚113与显示模块130的第五接脚135可以上述8个数据信号接脚的其中一个。当显示装置100有16条数据信号线时,控制模块110与显示器模块130可以具有16个数据信号接脚,其中控制模块110的第三接脚113与显示模块130的第五接脚135可以上述16个数据信号接脚的其中一个。当显示装置100有24条数据信号线时,控制模块110与显示器模块130可以具有24个数据信号接脚,其中控制模块110的第三接脚113与显示模块130的第五接脚135可以上述24个数据信号接脚的其中一个。其余则类推。

[0060]

图2为依据本发明的一实施例的垂直同步信号与水平同步信号的波形图。图3为图2的水平同步信号的一部分、控制信号、时钟信号、数据信号、数据显示指示信号的波形图。图4为图2的水平同步信号的另一部分、控制信号、时钟信号、数据信号、数据显示指示信号的波形图。

[0061]

在图2~图4中,标号“vsync”表示垂直同步信号,标号“hsync”表示水平同步信号,标号“tf”表示显示模块130的一个画面(frame)期间,标号“te”表示垂直同步信号vsync的使能期间,标号“td”表示垂直同步信号vsync的禁能期间,标号“th1”、“th2”分别表示水平同步信号hsync的水平同步期间(例如包括水平同步信号hsync的使能期间(例如低逻辑准位)与禁能期间(例如高逻辑准位)),标号“clk”表示时钟信号,标号“de”表示数据显示指示信号,标号“dat”表示数据信号,标号“d”表示显示数据,标号“inv”表示无效数据,标号“csd”表示配置设定数据,标号“cs”表示控制信号。

[0062]

请同时参考图1~图4。如图2所示,在显示模块130的一个画面期间tf,在垂直同步信号vsync的使能期间te,垂直同步信号vsync为低逻辑准位,并且垂直同步信号vsync的使能期间te包括2条扫描线,亦即垂直同步信号vsync的使能期间te包括2个水平同步信号hsync的水平同步期间th1,且这2个水平同步信号hsync的水平同步期间th1的每一者可以包括时钟信号clk的多个时钟脉波。此时,如图3所示,控制模块110提供低逻辑准位的控制信号cs、时钟信号clk、包括配置设定数据csd的数据信号dat与低逻辑准位的数据显示信号de给显示模块130。

[0063]

接着,显示模块130可以依据低逻辑位准的控制信号cs、时钟信号clk与配置设定数据csd进行配置设定。另一方面,显示模块130可以依据低逻辑准位的数据显示指示信号de(例如数据显示指示信号de的禁能期间),忽略显示模块130的第三接脚133所接收的时钟信号clk与显示模块130的第五接脚135所接收的包括配置设定数据csd的dat,亦即显示模块130不会对包括配置设定数据csd的数据信号dat进行显示。

[0064]

接着,如图2所示,在垂直同步信号vsync的禁能期间td,垂直同步信号vsync为高逻辑准位,并且垂直同步信号vsync的禁能期间td可以包括多个水平同步信号hsync的水平同步期间th2,且这些水平同步期间th2的每一者可以包括时钟信号clk的多个时钟脉波。此时,如图4所示,控制模块110可以提供高逻辑准位的控制信号cs、时钟信号clk、包括显示数据d的数据信号dat、高逻辑位准的数据显示指示信号de给显示模块130。

[0065]

接着,显示模块130可以依据高逻辑准位的控制信号cs,忽略显示模块130的第二接脚132所接收的时钟信号clk与显示模块130的第四接脚134所接收的包括显示数据d的数

据信号dat,亦即显示模块130不会对内部暂存器进行配置设定。

[0066]

另一方面,显示模块130可以依据高逻辑准位的数据显示指示信号de(例如数据显示指示信号de的使能期间)、时钟信号clk与包括显示数据d的数据信号dat进行正常显示,亦即显示模块130可以在数据显示指示信号de的使能期间,通过时钟信号clk来显示包括显示数据d的数据信号dat。

[0067]

在图2中,绘示出垂直同步信号vsync的使能期间te包括2条扫描线,亦即使能期间te包括水平同步信号hsync的2个水平同步期间th1,但本发明实施例不限于此。使用者可视其需求调整垂直同步信号vsync的使能期间te包括3条或3条以上的扫描线,亦即使能期te可以包括水平同步信号hsync的3个或3个以上的水平同步期间th1,都可以达成相同的效果。

[0068]

综上所述,本发明所述的控制装置与显示装置,通过控制模块的第一接脚提供控制信号,控制模块的第二接脚提供时钟信号,控制模块的第三接脚提供数据信号,且数据信号包括显示数据与配置设定数据,且在垂直同步信号的使能期间,控制模块提供第一准位的控制信号、时钟信号与包括配置设定数据的数据信号给显示模块(显示装置),使显示模块依据控制信号、时钟信号与配置设定数据进行配置设定,以及在垂直同步信号的禁能期间,控制模块提供第二准位的控制信号、时钟信号与包括显示数据的数据信号给显示模块(显示装置),使显示模块(显示装置)依据控制信号、时钟信号与显示数据进行正常显示。另外,显示模块的第二接脚与第三接脚可以共用控制模块的第二接脚以及显示模块的第四接脚与第五接脚可以共用控制模块的第三接脚。如此一来,可以有效地减少控制模块的使用接脚的数量,使控制模块可以有空出来的接脚对控制模块的功能进行扩充,并可维持显示模块的正常显示功能,以增加使用上的便利性。

[0069]

本发明虽以实施例所述如上,然其并非用以限定本发明的范围,任何本领域技术人员,在不脱离本发明的精神和范围内,当可做些许的更动与修改,因此本发明的保护范围当视前附的权利要求范围所界定者为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。