嵌入式sonos闪存ono层的制造方法

技术领域

1.本发明涉及半导体技术领域,特别是涉及一种嵌入式sonos闪存ono层的制造方法。

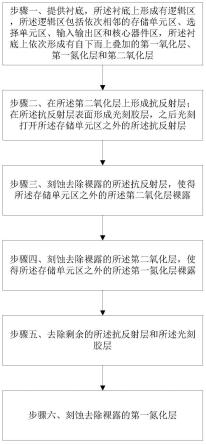

背景技术:

2.嵌入式闪存(embedded flash,e-flash)是把闪存嵌入到cmos(complementary metal-oxide-semiconductor transistor)上,形成soc(system on a chip)。嵌入式sonos(silicon-oxide-nitride-oxide-silicon)闪存是基于现有逻辑平台将sonos flash嵌入到逻辑平台。sonos flash采用的是选择管(select-gate)和存储管(cell-gate)结构。

3.其中ono(oxide-nitride-oxide)工艺是sonos flash的核心工艺之一。ono(氧化层-氮化层-氧化层)工艺不仅包含存储管区ono层的制备,还包括逻辑区(包含io、device)的栅极氧化层的制备。现有工艺流程如图1所示:在完成ono层生长后。通过光刻工艺将逻辑区打开,仅在存储管区保留完整的ono层。利用干法刻蚀将barc和顶层氧化层去除。再除去存储管区的pr(光刻胶)和brac(抗反射涂层)。最后利用湿法刻蚀去除逻辑区中ono层的氮化层。最终ono层在逻辑区仅保留底层氧化层,逻辑器件的栅极氧化层在该底层氧化层的基础上制备。

4.在现有技术中,有三个原因会导致栅极氧化层在刻蚀中受损。首先,干法刻蚀工艺选择比较低,在刻蚀ono层顶层氧化层时,也会刻蚀部分甚至全部氮化层,这削弱了氮化层对底层氧化层的保护作用,最终导致底层氧化层(栅极氧化层)的损伤。其次,ono层中氧化层和氮化层之间界限不明确,这种过渡态会放大干法刻蚀较低选择比对栅极氧化层的不利影响。此外,由于在aa/sti(有源区/浅沟槽隔离)交界处ono层较厚,为了保证此处ono层的顶层氧化层被全部刻蚀完,需要过刻蚀(oe,over etch),而该区域的过刻蚀又会加剧其他区域中氮化层的刻蚀,进而影响其他区域氮化层对栅极氧化层的保护作用,导致栅极氧化层的可靠性衰退。

技术实现要素:

5.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种嵌入式sonos闪存ono层的制造方法,用于解决现有技术中干法刻蚀工艺选择比较低,在刻蚀ono层顶层氧化层时,也会刻蚀部分甚至全部氮化层,这削弱了氮化层对底层氧化层的保护作用,最终导致底层氧化层(栅极氧化层)的损伤,ono层中氧化层和氮化层之间界限不明确,这种过渡态会放大干法刻蚀较低选择比对栅极氧化层的不利影响,为了保证此处ono层的顶层氧化层被全部刻蚀完,需要过刻蚀(oe,over etch),而该区域的过刻蚀又会加剧其他区域中氮化层的刻蚀,进而影响其他区域氮化层对栅极氧化层的保护作用,导致栅极氧化层的可靠性衰退的问题。

6.为实现上述目的及其他相关目的,本发明提供一种嵌入式sonos闪存ono层的制造方法,包括:

7.步骤一、提供衬底,所述衬底上形成有逻辑区,所述逻辑区包括依次相邻的存储单元区、选择单元区、输入输出区和核心器件区,所述衬底上依次形成有自下而上叠加的第一氧化层、第一氮化层和第二氧化层;

8.步骤二、在所述第二氧化层上形成抗反射层以及在所述抗反射层表面的光刻胶层,之后光刻打开所述光刻胶层,使得所述存储单元区之外的所述抗反射层裸露;

9.步骤三、刻蚀去除裸露的所述抗反射层,使得所述存储单元区之外的第二氧化层裸露;

10.步骤四、刻蚀去除裸露的所述第二氧化层,使得所述存储单元区之外的所述第一氮化层裸露;

11.步骤五、去除剩余的所述抗反射层和所述光刻胶层;

12.步骤六、刻蚀去除裸露的第一氮化层。

13.优选地,步骤一中的所述衬底为硅衬底。

14.优选地,步骤一中的所述第一氧化层和第二氧化层的材料均为二氧化硅。

15.优选地,步骤一中的所述第一氮化层的材料为氮化硅。

16.优选地,步骤三中的所述刻蚀的方法为干法刻蚀。

17.优选地,步骤四中所述刻蚀的方法为湿法刻蚀。

18.优选地,步骤五中利用灰化和湿法清洗去除剩余的所述抗反射层和所述光刻胶层。

19.优选地,步骤六中的所述刻蚀为湿法刻蚀。

20.如上所述,本发明的嵌入式sonos闪存ono层的制造方法,具有以下有益效果:

21.本发明的方法首先使用干法刻蚀仅刻蚀掉抗反射层,然后使用湿法刻蚀来刻蚀顶层氧化层,利用湿法刻蚀的选择比高特性,解决干法刻蚀损伤氮化层的问题,进而栅极氧化层的可靠性,最终提高ono工艺的可靠性。

附图说明

22.图1显示为本发明的工艺流程示意图;

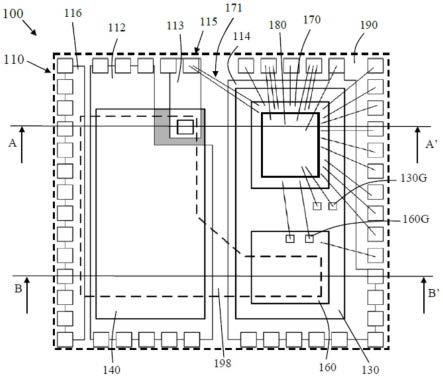

23.图2显示为本发明的衬底示意图;

24.图3显示为本发明的光刻示意图;

25.图4显示为本发明的去除部分抗反射层示意图;

26.图5显示为本发明的刻蚀部分第二氧化层示意图;

27.图6显示为本发明的去除光刻胶以及抗反射层示意图;

28.图7显示为本发明的去除部分第一氮化层示意图。

具体实施方式

29.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

30.请参阅图1,本发明提供一种嵌入式sonos闪存ono层的制造方法,包括:

31.步骤一,请参阅图2,提供衬底10,衬底10上形成有逻辑区,逻辑区包括依次相邻的存储单元区、选择单元区、输入输出区和核心器件区,衬底10上依次形成有自下而上叠加的第一氧化层11、第一氮化层12和第二氧化层13,第一氧化层11、第一氮化层12和第二氧化层13组成了ono层;

32.在一种可选的实施方式中,步骤一中的衬底10优选为硅衬底10,应当理解的是,衬底10也可采用蓝宝石衬底10、有机物衬底10等。

33.在一种可选的实施方式中,步骤一中的第一氧化层11和第二氧化层13的材料均为二氧化硅。

34.在一种可选的实施方式中,步骤一中的第一氮化层12的材料为氮化硅。

35.步骤二,请参阅图3,在第二氧化层13上形成抗反射层14以及在抗反射层14表面的光刻胶层15,之后光刻打开光刻胶层15,再通过显影、竖膜、烘焙等流程后,使得存储单元区之外的抗反射层14裸露;

36.步骤三,请参阅图4,刻蚀去除裸露的抗反射层14,使得存储单元区之外的第二氧化层13裸露;

37.在一种可选的实施方式中,步骤三中的刻蚀的方法为干法刻蚀,现有技术干法刻蚀工艺选择比较低,在刻蚀ono层顶层氧化层时,也会刻蚀部分甚至全部氮化层,这削弱了氮化层对底层氧化层的保护作用,最终导致底层氧化层(栅极氧化层)的损伤。

38.步骤四,请参阅图5,刻蚀去除裸露的第二氧化层13,使得存储单元区之外的第一氮化层12裸露;

39.在一种可选的实施方式中,步骤四中刻蚀的方法为湿法刻蚀,通过湿法刻蚀的高选择比,能够减少对氮化层的损伤。

40.步骤五,请参阅图6,去除剩余的抗反射层14和光刻胶层15;

41.在一种可选的实施方式中,步骤五中利用灰化和湿法清洗去除剩余的抗反射层14和光刻胶层15。

42.步骤六,请参阅图7,刻蚀去除裸露的第一氮化层12。

43.在一种可选的实施方式中,步骤六中的刻蚀为湿法刻蚀,利用湿法刻蚀的选择比高特性,解决干法刻蚀损伤氮化层的问题。

44.需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

45.综上所述,本发明的方法首先使用干法刻蚀仅刻蚀掉抗反射层,然后使用湿法刻蚀来刻蚀顶层氧化层,利用湿法刻蚀的选择比高特性,解决干法刻蚀损伤氮化层的问题,进而栅极氧化层的可靠性,最终提高ono工艺的可靠性。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

46.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。