1.本发明实施例涉及静电放电电路及其操作方法。

背景技术:

2.电子器件(例如芯片或集成电路)可在其上累积静电电荷。如果经累积静电电荷未被恰当地放电,那么电子器件可能损坏或甚至破坏。可透过静电放电(esd)保护以使经累积静电电荷放电。

技术实现要素:

3.本发明的实施例涉及一种电路,其包括:第一晶体管,其包含漏极、源极、栅极及本体,所述第一晶体管的所述漏极经连接到第一端子,所述第一晶体管的所述源极经连接以接收第一电压,且所述第一晶体管的所述栅极及所述本体经连接以接收低于所述第一电压的第二电压,及第二晶体管,其包含漏极、源极、栅极及本体,所述第二晶体管的所述源极、所述栅极及所述本体经连接以接收所述第二电压,且所述第二晶体管的所述漏极经连接到所述第一端子,其中响应于所述第一端子达到触发电压,所述第一晶体管经配置以接通。

4.本发明的实施例涉及一种半导体器件,其包括:第一导电类型的衬底;第二导电类型的第一掺杂区;所述第二导电类型的第一掺杂条带;所述第二导电类型的第二掺杂条带;所述第二导电类型的第三掺杂条带,其中所述第一掺杂条带在所述第一掺杂区与所述第三掺杂条带之间;及所述第二导电类型的第四掺杂条带,其中所述第二掺杂条带在所述第一掺杂区与所述第四掺杂条带之间,其中所述第一及第四掺杂条带经配置以接收第一电压,所述第二及第三掺杂条带经配置以接收低于所述第一电压的第二电压,所述第一掺杂区经配置为上拉突返晶体管的漏极及下拉突返晶体管的漏极,且所述第一掺杂区宽于所述第一、第二、第三及第四条带。

5.本发明的实施例涉及一种操作电路的方法,其包括:响应于第一端子达到第一触发电压,接通连接在所述第一端子与第一电压之间的第一晶体管;响应于所述第一端子达到第二触发电压,接通连接在所述第一端子与第二电压之间的第二晶体管,其中所述第二触发电压大于所述第一电压,其中所述第一晶体管包含漏极延伸式n型金属氧化物半导体场效晶体管(n-mosfet),且所述第二晶体管包含漏极延伸式n-mosfet。

附图说明

6.当结合附图阅读时从下列实施方式最佳地理解本公开的方面。应注意,根据行业中的标准实践,各种构件不按比例绘制。实际上,为清晰论述,各种构件的尺寸可任意增大或减小。

7.图1是根据本公开的一些实施例的esd电路的示意图。

8.图2展示根据本公开的一些实施例的电流-电压曲线。

9.图3描绘根据本公开的一些实施例的静电放电路径。

10.图4是根据本公开的一些实施例的esd结构的平面视图。

11.图5描绘根据本公开的一些实施例的静电放电路径。

12.图6是根据本公开的一些实施例的esd电路的示意图。

13.图7是根据本公开的一些实施例的功率箝制模块的示意图。

14.图8描绘根据本公开的一些实施例的静电放电路径。

15.图9是根据本公开的一些实施例的用于操作esd电路的方法的流程图。

16.除非另有指示,否则不同图中的对应数字及符号通常指对应部件。所述图经绘制以清楚地说明各项实施例的相关方面且未必按比例绘制。

具体实施方式

17.以下揭露提供用于实施所提供的主题的不同构件的许多不同实施例或实例。下文描述组件及布置的特定实例以简化本公开。当然,这些仅为实例且非旨在限制。举例来说,在以下描述中的第一构件形成在第二构件上方或上可包含其中所述第一构件及所述第二构件经形成为直接接触的实施例,且还可包含其中额外构件可形成在所述第一构件与所述第二构件之间,使得所述第一构件及所述第二构件可不直接接触的实施例。另外,本公开可在各个实例中重复元件符号及/或字母。此重复出于简化及清楚的目的且本身不指示所论述的各项实施例及/或配置之间的关系。

18.此外,为便于描述,例如“在

…

下面”、“在

…

下方”、“下”、“在

…

上方”、“上”及类似者的空间相对术语可在本文中用于描述一个元件或构件与另一(些)元件或构件的关系,如图中说明。空间相对术语旨在涵盖除在图中描绘的定向以外的使用或操作中的装置的不同定向。设备可以其它方式定向(旋转90度或按其它定向)且因此可同样解释本文中使用的空间相对描述词。

19.实施例的性质及用途经详细地论述如下。然而,应明白,本公开提供可在各种各样的特定脉络中体现的许多适用发明构思。所论述的特定实施例仅仅阐释用以体现及使用本公开的特定方式,而不限制其范围。

20.与集成电路一起使用的静电放电(esd)保护结构可提供用以将电流从端子旁通到接地或从端子旁通到电力供应轨,借此归因于esd事件的电流绕开敏感内部电路系统的路径。在短持续时间静电放电事件期间观察到在正及负量值两者方面远远超过正常操作电压的电压。esd保护结构防止基于esd事件的电流危害集成电路中的敏感组件。在没有esd保护的情况下,耦合到电源端子的器件可能发生故障。

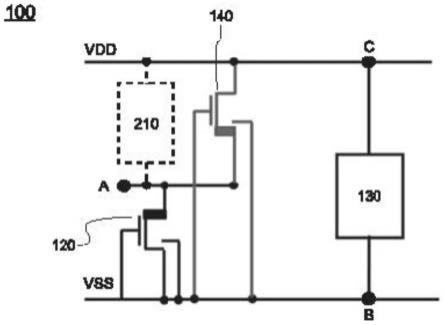

21.图1是根据本公开的一些实施例的电路100的示意图。电路100可包含晶体管120及140,及功率箝制模块130。组件210可经连接到电路100。组件210可受保护免于esd事件。

22.可在电路100中提供两个电力轨。上部电力轨可供应电压vdd。下部电力轨可供应电压vss。电压vdd可超过电压vss。在一些实施例中,电压vdd可为正电力供应器。在一些实施例中,电压vss可经接地。电路100的元件可经连接在电压vdd的电力轨与电压vss的电力轨之间。

23.根据电路100,可保护组件210免于esd事件。组件210可被称为受害(victim)组件。组件210可经连接到电压vdd的电力轨以接收电压vdd。组件210可经连接到端子a。组件210可经连接在电压vdd的电力轨与端子a之间。端子a可为输入、输入/输出或输出垫。在一些实

施例中,端子a可被称为垫端子。在实例应用中,垫端子可为形成在半导体衬底上的集成电路的输入、输出或输入/输出端子。在一些实施例中,组件210可为或可包含可遭受esd事件的任何电路、模块或系统。

24.esd事件通常发生在输入、输入/输出或输出垫与另一端子vss或vdd之间。esd应力模式可针对从垫到vss的正电压被分类为ps模式冲击,针对从垫到vdd的正电压被分类为pd模式冲击,针对从垫到vss的负电压被分类为ns模式冲击,或针对从垫到vdd的负电压被分类为nd模式冲击。

25.晶体管120可经连接到电压vss的电力轨以接收电压vss。晶体管120可经连接到端子a。晶体管120可经连接在电压vss的电力轨与端子a之间。晶体管120可为n型晶体管。晶体管120的漏极可经连接到端子a。晶体管120的源极、本体(或主体)与栅极可经连接到电压vss的电力轨。晶体管120的源极、本体(或主体)与栅极可经连接以接收电压vss。

26.晶体管140可经连接到电压vdd的电力轨以接收电压vdd。晶体管140可经连接到端子a。晶体管140可经连接在电压vdd的电力轨与端子a之间。晶体管140可为n型晶体管。晶体管140的漏极可经连接到端子a。晶体管140的源极可经连接到电压vdd的电力轨。晶体管140的源极可经连接以接收电压vdd。晶体管140的本体(或主体)与栅极可经连接到电压vss的电力轨。晶体管140的本体(或主体)与栅极可经连接以接收电压vss。

27.晶体管120及140可为n型晶体管。晶体管120及140可为n型场效晶体管(fet)。晶体管120及140可为n型金属氧化物半导体场效晶体管(mosfet)。晶体管120及140可为漏极延伸式n型mosfet。

28.晶体管120及140的栅极可经连接到接地,且当组件210在正常模式下操作时,晶体管120及140可不被接通。因为晶体管120及140可为漏极延伸式晶体管,所以当高电压尖峰经施加到晶体管120或140时,被施加高电压尖峰的晶体管120或140可作为双极结晶体管(bjt)接通。晶体管120及140可展现被称为“突返”的特性。突返特性可指当高电压尖峰经施加到晶体管时晶体管可被接通。

29.在一些实施例中,功率箝制模块130可用作二极管(例如,功率箝制主体二极管)。功率箝制主体二极管可具有正向阈值电压。如果节点b与c之间的电压差超过正向阈值电压,那么功率箝制主体二极管可导通,且电流可从节点b流动到节点c。如果节点b与c之间的电压差小于正向阈值电压,那么功率箝制主体二极管的导通可暂停。

30.如图1中所展示,在esd事件中,静电电荷可通过晶体管120及140与功率箝制电路130放电。根据电路100,esd的触发电压可极大地降低。

31.图2展示根据本公开的一些实施例的电流-电压曲线。图2中所展示的电流-电压可根据端子a处的测量来绘制。在图2中,x轴可表示晶体管120或140的漏极与源极之间的电压,且y轴可表示流动通过晶体管120或140的电流。

32.如图2中所展示,如果晶体管120或晶体管140的漏极与源极之间的电压低于电压vt1(其可为晶体管120或140的阈值电压或触发电压),那么晶体管120或晶体管140可被关断,且无电流流动通过晶体管120或晶体管140。当经施加电压(例如,漏极与源极之间的电压)高于电压vt1时,晶体管120及140可被接通。

33.电压vt2可为组件210的击穿电压。如果端子a处的电压高于电压vt2,那么组件210可能会损坏。如果堆叠在组件210中的元件(例如,晶体管)的数目增加,那么电压vt2可增

加。

34.如果esd电路的触发电压过于接近组件210的击穿电压(例如,电压vt2),那么当静电电荷迅速地累积在待受保护电路(例如,组件210)的端子(例如,端子a)处时,可能无法及时触发esd电路。这可能损坏所述电路。

35.为了增强esd电路的稳健性,尤其是在pd模式冲击下,esd电路的触发电压可能降低。在本公开的一些实施例中,esd电路(例如,晶体管120、140;没有组件210的电路100)具有相对低的触发电压(例如,电压vt1)。因此,即使端子a处的电压归因于迅速累积的静电电荷而过快增加,仍可及时触发esd电路(例如,晶体管120、140;没有组件210的电路100),且可保护组件210免于损坏。

36.从图2中所展示的电流-电压曲线,电压可响应于电压达到触发电压vt1而降低。在电压达到电压vt1之前,电流非常小。响应于电压达到电压vt1,电流增加。

37.图3描绘根据本公开的一些实施例的静电放电路径310、320及330。图3描绘根据电路100的静电放电路径310、320及330。响应于端子a处的电压达到给定触发电压(例如,电压vt1),静电电荷可通过所述路径310、320及330的一或多者放电。

38.在路径310中,静电电荷可从端子a、晶体管140的漏极、晶体管140的源极及电压vdd的电力轨放电。在路径320中,静电电荷可从端子a、晶体管120的漏极、晶体管120的源极、电压vss的电力轨及功率箝制模块130的端(即,节点b)放电。在路径330中,静电电荷可从电压vss(即,节点b)的电力轨、功率箝制模块130及电压vdd的电力轨(即,节点c)放电。

39.路径310的触发电压可小于或不大于路径320及330的触发电压。路径310可在路径320及330之前接通。路径310、320及330可同时接通。由于路径310,电路100的总触发电压可极大地降低。因此电路100的稳健性可极大地增强。

40.可在pd模式冲击下将路径320及330组合成一个放电路径。静电电荷可通过两个路径(例如,路径310与路径320及330的组合)放电。因此电路100的稳健性可极大地增强。

41.图4是根据本公开的一些实施例的esd结构的平面视图。图4可为半导体400的平面视图。区401可为氧化物界定区。区401可为第一导电类型的衬底。区401可为p型衬底。区402可为第一类型阱中的第一类型植入区,例如,p阱中的p 植入区。

42.区410可经形成在区401内。区410可为第二导电类型的掺杂区域,例如n型掺杂区域。条带(或区域)411、412、413及414可经形成在区401内。条带(或区域)411、412、413及414可为第二导电类型的掺杂条带(或掺杂区域),例如n型掺杂条带。

43.条带421、422、423、424及431可由多晶硅或金属制成。条带421、422、423及424可经形成在区401上。条带431可经形成在区402内的区上。

44.区410可为上拉突返器件(例如,晶体管140)及下拉突返器件(例如,晶体管120)的漏极。区410可由上拉突返器件及下拉突返器件的漏极共享。区410可宽于条带411、412、413或414。因此,可控制本公开的电路(例如,电路100)的面积、泄漏及电容增量。因此,本公开的电路(例如,电路100)的面积可从突返器件的约1.3倍减小到约2倍。

45.条带411及414可为上拉突返器件的源极。条带412及413可为下拉突返器件的源极。条带421、422、423及424可为上拉突返器件及下拉突返器件的栅极。

46.半导体400可与电路100对应。区410可经连接到垫端子(例如,端子a)。条带411及414可经连接以接收电压vdd。条带412及413可经连接以接收电压vss。根据电路100的实施

例,条带421、422、423及424可经连接以接收电压vss。条带431可经连接以接收电压vss。

47.图5描绘根据本公开的一些实施例的静电放电路径501、502、503及504。图5描绘根据半导体400的静电放电路径501、502、503及504。

48.在路径501中,区410及条带411可被导通。在路径502中,区410及条带414可被导通。在路径503中,区410及条带413可被导通。在路径504中,区410及条带412可被导通。

49.在一些实施例中,响应于达到从垫端子(即,连接到区410的垫端子)到电压vdd的给定正电压(例如,电压vt1)(即,pd模式冲击),静电电荷可通过路径501及502放电。在一些实施例中,响应于达到从垫端子(即,连接到区410的垫端子)到电压vss的给定正电压(即,ps模式冲击),静电电荷可通过路径503及504放电。

50.上拉突返器件可具有两个寄生npn通道,其中的一者可包含区410及条带411且另一者可包含区410及条带414。上拉突返器件的两个寄生npn通道可为平行的且具有不同基底宽度。

51.下拉突返器件可具有两个寄生npn通道,其中的一者可包含区410及条带412且另一者可包含区410及条带413。上拉突返器件的两个寄生npn通道可为平行的且具有不同基底宽度。

52.根据本公开的实施例,半导体400可花费更少时间来接通npn通道且在esd事件期间提供npn通道的更长接通持续时间。

53.图6是根据本公开的一些实施例的电路600的示意图。电路600可包含晶体管120、140、610,功率箝制模块130及端子a。组件210可经连接到电路600。组件210可受保护免于esd事件。

54.可在电路600中提供两个电力轨。上部电力轨可供应电压vdd。下部电力轨可供应电压vss。电压vdd可超过电压vss。在一些实施例中,电压vdd可为正电力供应器。在一些实施例中,电压vss可经接地。电路600的元件可经连接在电压vdd的电力轨与电压vss的电力轨之间。

55.关于图1的电路100,电路600可进一步包含晶体管610及节点d。晶体管610可经连接到电压vdd的电力轨以接收电压vdd。晶体管610可经连接到电压vss的电力轨以接收电压vss。晶体管610可经连接在电压vdd的电力轨与电压vss的电力轨之间。晶体管610可为n型晶体管。晶体管610的漏极及本体(或主体)可经连接到电压vss的电力轨。晶体管610的漏极及本体(或主体)可经连接以接收电压vss。晶体管610的源极可经连接到电压vdd的电力轨。晶体管610的源极可经连接以接收电压vdd。晶体管610的栅极可在节点d处连接到功率箝制模块130。晶体管610的栅极可经连接到功率箝制模块130的r-c反相器节点。晶体管610可在电路600的esd事件期间接通。晶体管610可用来在电路600的esd事件期间使静电电荷放电。

56.晶体管610可为n型mosfet。晶体管610可为嵌入式n型mosfet。在一些实施例中,晶体管610可为嵌入式nmos,且晶体管120及140可为漏极延伸式n型mosfet。

57.图7是根据本公开的一些实施例的功率箝制模块130的示意图。功率箝制模块130可包含晶体管131、132、133、电阻器134、电容器135及节点d。图7中的节点d可与图6中的节点d对应。

58.晶体管131及133可为n型晶体管。晶体管131及133可为n型mosfet。晶体管131的栅极可经连接到晶体管131的本体。晶体管133的栅极可经连接到晶体管133的本体。晶体管

131可为大场效晶体管(fet)。晶体管131的通道宽度可超过1000μm。晶体管131可为io(输入/输出)单元中的局部大fet。局部大fet可在nd模式冲击期间降低电压降。

59.晶体管132可为p型晶体管。晶体管132可为p型mosfet。晶体管132的栅极可经连接到晶体管132的本体。

60.晶体管131可为n型晶体管。晶体管131的漏极可经连接到电压vdd的电力轨。晶体管131的源极可经连接到电压vss的电力轨。晶体管131的栅极可经连接到节点d。

61.晶体管132可为p型晶体管。晶体管132的源极可经连接到电压vdd的电力轨。晶体管132的漏极可经连接到节点d。晶体管132的栅极可经连接到晶体管133的栅极、电阻器134及电容器135。

62.晶体管133可为n型晶体管。晶体管133的漏极可经连接到节点d。晶体管133的源极可经连接到电压vss的电力轨。晶体管133的栅极可经连接到晶体管132的栅极、电阻器134及电容器135。晶体管131的栅极、晶体管132的漏极及晶体管133的漏极可在节点d处彼此连接。

63.电阻器134的一端可经连接到电压vdd的电力轨。电阻器134的另一端可经连接到电容器135、晶体管132的栅极及晶体管133的栅极。电容器135的一端可经连接到电压vss的电力轨。电容器135的另一端可经连接到电阻器134、晶体管132的栅极及晶体管133的栅极。

64.esd箝制器件(例如,功率箝制模块130)的接通持续时间可主要由rc时间常数控制。rc时间常数可足够大(约几百ns)以在esd事件期间保持esd箝制器件“开”。然而,延伸式rc时间常数可能需要电阻器及电容器的更大布局面积。

65.再次参考图4,半导体400可与电路600对应。区410可经连接到垫端子(例如,端子a)。条带411及414可经连接以接收电压vdd。条带412及413可经连接以接收电压vss。根据电路600的实施例,条带421及422可经连接以接收电压vss。根据电路600的实施例,条带423及424可经连接以接收功率箝制模块130的r-c反相器节点(例如,在图6及7的节点d处)。条带431可经连接以接收电压vss。根据电路600的实施例,嵌入式nmo可经放置在条带411与413之间及条带412与414之间。根据电路600的实施例,条带423及424可为嵌入式nmos的栅极。

66.根据本公开的实施例,半导体(例如,半导体400)可具有更短周期来接通npn通道且在esd事件期间可具有npn通道的更长接通持续时间。本公开可能不需要电阻器及电容器的更大布局面积来获得更长接通持续时间。

67.图8描绘根据本公开的一些实施例的静电放电路径810、820、830、840。图8描绘根据电路600的静电放电路径810、820、830、840。响应于端子a处的电压达到给定触发电压(例如,电压vt1),静电电荷可通过所述路径810、820、830、840的一或多者放电。

68.在路径810中,静电电荷可从端子a、晶体管140的漏极、晶体管140的源极及电压vdd的电力轨放电。在路径820中,静电电荷可从端子a、晶体管120的漏极、晶体管120的源极、电压vss的电力轨及晶体管610的漏极放电。在路径830中,静电电荷可从晶体管610的漏极、晶体管610的源极及电压vdd的电力轨放电。在路径840中,静电电荷可从电压vss(即,节点b)的电力轨、功率箝制模块130及电压vdd(即,节点c)的电力轨放电。

69.路径810的触发电压可小于或不大于路径820、830及840的触发电压。路径810可在路径820、830及840之前接通。路径810、820、830及840可同时接通。由于路径810,电路600的总触发电压可极大地降低。因此,电路600的稳健性可极大地增强。

70.在pd模式冲击期间,路径830及840上的静电电荷可从路径820上的静电电荷划分。静电电荷可通过三个路径(例如,路径810、路径820及830的组合,及路径820及840的组合)。因此,电路600的稳健性可极大地增强。

71.图9是根据本公开的一些实施例的用于操作esd电路的方法的流程图。图9可为根据本公开的一些实施例的用于操作电路100或600的方法900的流程图。

72.在操作901中,确定电路100(或600)的端子a是否达到第一触发电压(例如,电压vt1)。如果电路100(或600)的端子a未达到第一触发电压,那么可重复操作901。如果电路100(或600)的端子a达到第一触发电压,那么可执行操作902。

73.在操作902中,响应于电路100(或600)的端子a达到第一触发电压,连接在端子a与电压vdd的电力轨之间的晶体管140将接通。响应于电路100(或600)的端子a达到第一触发电压,晶体管140可作为bjt接通。

74.在操作902之后,可执行操作903。在操作903中,确定电路100(或600)的端子a是否达到第二触发电压(例如,大于电压vt1的电压,或不小于电压vt1的电压)。如果电路100(或600)的端子a未达到第一触发电压,那么可执行操作901。如果电路100(或600)的端子a达到第二触发电压,那么可执行操作904。

75.在操作904中,响应于电路100(或600)的端子a达到第二触发电压,连接在端子a与电压vss的电力轨之间的晶体管120可接通。响应于电路100(或600)的端子a达到第二触发电压,晶体管120可作为bjt接通。

76.在一些实施例中,方法900可不包含操作903。当方法900不包含操作903时,可在操作902之后执行操作904。当方法900不包含操作903时,晶体管120可在晶体管104接通之后接通。在操作904中,晶体管120可作为bjt接通。

77.在方法900的一些实施例中,响应于电路100(或600)的端子a达到第一触发电压,晶体管140可接通,且接着晶体管120可接通。

78.在一些实施例中,方法900可进一步包含接通功率钳位模块130的操作。在其它实施例中,方法900可进一步包含功率箝制模块130响应于电路100(或600)的端子a达到第二触发电压而接通的操作。方法900可进一步包含功率钳位模块130响应于晶体管140接通而接通的操作。

79.在进一步实施例中,方法900可进一步包含电流响应于电路100(或600)的端子a达到第二触发电压而流动通过功率箝制模块130的操作。方法900可进一步包含电流响应于晶体管140接通而流动通过功率箝制模块130的操作。

80.在一些实施例中,方法900可进一步包含晶体管610接通的操作。在其它实施例中,方法900可进一步包含晶体管610响应于电路100(或600)的端子a达到第二触发电压而接通的操作。方法900可进一步包含晶体管610响应于功率钳位模块130接通而接通的操作。方法900可进一步包含晶体管610响应于晶体管120接通而接通的操作。

81.在进一步实施例中,方法900可进一步包含电流响应于电路600的端子a达到第二触发电压而流动通过晶体管610的操作。方法900可进一步包含电流响应于功率箝制模块130接通而流动通过晶体管610的操作。方法900可进一步包含电流响应于晶体管120接通而流动通过晶体管610的操作。

82.在一些实施例中,本公开提供一种电路。所述电路可包含第一晶体管及第二晶体

管。所述第一晶体管可包含漏极、源极、栅极及本体。所述第一晶体管的所述漏极可经连接到第一端子。所述第一晶体管的所述源极可经连接以接收第一电压。所述第一晶体管的所述栅极及所述本体可经连接以接收第二电压。所述第二晶体管可包含漏极、源极、栅极及本体。所述第二晶体管的所述源极、所述栅极及所述本体可经连接以接收所述第二电压。所述第二晶体管的所述漏极可经连接到所述第一端子。响应于所述第一端子达到触发电压,所述第一晶体管可经配置以接通。

83.在一些实施例中,本公开提供一种半导体器件。所述半导体器件可包含:第一导电类型的衬底;第二导电类型的第一掺杂区;所述第二导电类型的第一掺杂条带;所述第二导电类型的第二掺杂条带;所述第二导电类型的第三掺杂条带;及所述第二导电类型的第四掺杂条带。所述第一及第四掺杂条带可经配置以接收第一电压。所述第一掺杂条带在所述第一掺杂区与所述第三掺杂条带之间。所述第二掺杂条带在所述第一掺杂区与所述第四掺杂条带之间。所述第二及第三掺杂条带可经配置以接收低于所述第一电压的第二电压。所述第一掺杂区可经配置为上拉突返晶体管的漏极及下拉突返晶体管的漏极。所述第一掺杂区可宽于所述第一、第二、第三及第四条带。

84.在一些实施例中,本公开提供一种操作电路的方法。所述方法可包含:响应于第一端子达到第一触发电压,接通连接在所述第一端子与第一电压之间的第一晶体管;及响应于所述第一端子达到第二触发电压,接通连接在所述第一端子与第二电压之间的第二晶体管。所述第二触发电压可大于所述第一电压。所述第一晶体管可包含漏极延伸式n型金属氧化物半导体场效晶体管(n-mosfet)。所述第二晶体管可包含漏极延伸式n-mosfet。

85.本技术案的范围并非旨在限于说明书中所描述的过程、机器、制造与物质组合物、构件、方法及步骤的特定实施例。如所属领域的一般技术人员将从本公开的揭露内容容易理解,可根据本公开利用执行与本文中所描述的对应实施例基本上相同功能或实现基本上相同结果的过程、机器、制造、物质组合物、构件、方法或步骤。据此,所附权利要求书旨在将这些过程、机器、制造、物质组合物、构件、方法或步骤/操作包含在其范围内。另外,每一权利要求构成单独实施例,且各个权利要求及实施例的组合在本公开的范围内。

86.符号说明

87.100:电路

88.120:晶体管

89.130:功率箝制模块

90.131:晶体管

91.132:晶体管

92.133:晶体管

93.134:电阻器

94.135:电容器

95.140:晶体管

96.210:组件

97.310:静电放电路径

98.320:静电放电路径

99.330:静电放电路径

100.400:半导体

101.401:区

102.402:区

103.410:区

104.411:条带(或区域)

105.412:条带(或区域)

106.413:条带(或区域)

107.414:条带(或区域)

108.421:条带

109.422:条带

110.423:条带

111.424:条带

112.431:条带

113.501:静电放电路径

114.502:静电放电路径

115.503:静电放电路径

116.504:静电放电路径

117.600:电路

118.610:晶体管

119.810:静电放电路径

120.820:静电放电路径

121.830:静电放电路径

122.840:静电放电路径

123.900:方法

124.901:操作

125.902:操作

126.903:操作

127.904:操作

128.a:端子

129.b:节点

130.c:节点

131.d:节点

132.vdd:电压

133.vss:电压

134.vt1:电压

135.vt2:电压。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。