1.本公开涉及输入缓冲器,且更具体地说,涉及共栅极输入缓冲器。

背景技术:

2.某些读取/写入存储器装置,例如动态随机存取存储器(dram),包含具有存储信息的存储器单元的阵列。举例来说,某些dram装置,例如同步动态ram(sdram)装置,可具有多个存储器组,所述多个存储器组具有包含在存储器阵列中的许多可寻址存储器元件或单元。在使用中,作为sdram装置的存储器装置可在较高速度(例如,6千兆位每秒(gbps)的速度(例如,6gbps、7gbps、8gbps)或大于6gbps的速度)下接收数据输入信号,且基于数据输入信号将数据存储于存储器单元中。输入缓冲器,例如共栅极输入缓冲器,可用于接收高速数据且存储所接收的数据以用于进一步处理,例如,用于转换成二进制位数据或其它非二进制数据。通过经由输入缓冲器技术处理信号,输入缓冲器可提供与外部装置的更高效通信。可有用的是改进并入有共栅极输入缓冲器技术的系统和方法。

3.本公开的实施例可针对于上文所阐述的问题中的一或多个。

技术实现要素:

4.在一个方面中,本技术提供一种存储器装置,其包括:共栅极输入缓冲器电路,其包括:输入节点,其经配置以接收表示待存储于所述存储器装置中的数据的信号;电压参考节点,其经配置以接收表示电压参考的参考信号;放大电路,其电耦合到所述输入节点且电耦合到所述电压参考节点,并且经配置以放大所述信号以提供经放大信号;均衡电路,其电耦合到所述放大电路,并且经配置以处理所述经放大信号以提供经滤波信号;和输出电路,其电耦合到所述均衡电路,且经配置以基于所述经滤波信号提供至少一个输出信号,其中所述输出信号包括差分输出信号,且其中所述共栅极输入缓冲器电路不包含共模反馈(cmfb)环路。

5.在另一方面中,本技术提供一种共栅极输入缓冲器电路,其包括:输入节点,其经配置以接收表示数据的信号;电压参考节点,其经配置以接收表示电压参考的参考信号;放大电路,其电耦合到所述输入节点且电耦合到所述电压参考节点,并且经配置以放大所述信号以提供经放大信号;均衡电路,其电耦合到所述放大电路,并且经配置以处理所述经放大信号以提供经滤波信号;和输出电路,其电耦合到所述均衡电路,并且经配置以基于所述经滤波信号提供至少一个输出信号,其中所述输出信号包括差分输出信号,且其中所述输出电路包括经配置以基于所述经滤波信号的低摆幅电压而增大所述至少一个输出信号的输出信号电流的第一开关装置。

6.在又一方面中,本技术提供一种存储器装置,其包括:共栅极输入缓冲器电路,其包括:输入节点,其经配置以接收表示待存储于所述存储器装置中的数据的信号;电压参考节点,其经配置以接收表示电压参考的参考信号;放大电路,其电耦合到所述输入节点且电耦合到所述电压参考节点,并且经配置以放大所述信号以提供经放大信号;均衡电路,其电

耦合到所述放大电路,并且配置以处理所述经放大信号以提供经滤波信号;和输出电路,其电耦合到所述均衡电路,并且经配置以基于所述经滤波信号提供至少一个输出信号,其中所述输出信号包括差分输出信号,且其中所述输出电路包括经配置以基于所述经滤波信号的高摆幅电压而减小所述至少一个输出信号的输出信号电流的第一开关装置。

附图说明

7.在阅读以下详细描述并且参考图式之后可更好地理解本公开的各个方面,在图式中:

8.图1是根据实施例的说明可包含一或多个共栅极输入缓冲器的存储器装置的组织的框图;

9.图2为根据实施例的可在图1的存储器装置中使用的通信系统的框图;

10.图3为根据实施例的伪差分共栅极输入缓冲器的电路图;且

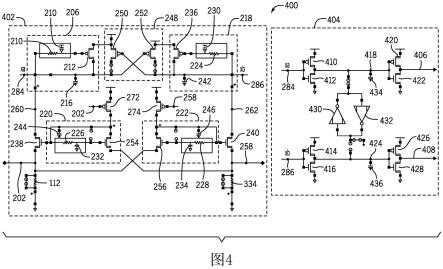

11.图4为根据实施例的并不包含共模反馈(cmfb)环路的伪差分共栅极输入缓冲器的电路图。

具体实施方式

12.下文将描述一个或多个具体实施例。为了提供这些实施例的简要描述,不会在本说明书中描述实际实施方案的所有特征。应了解,在任何此类实际实施方案的发展中,如同在任何工程或设计项目中,必须制定众多的实施方案特定决策以实现研发者的特定目标,例如与系统相关和企业相关约束的一致性,这可能从一个实施方案到另一实施方案有所变化。此外,应了解,此类开发工作可能是复杂且耗时的,然而对于受益于本公开的一般技术人员来说,这些都是设计、构造和制造中的常规任务。

13.许多电气装置可包含耦合到处理电路的随机存取存储器(ram)装置,且存储器装置可提供用于数据处理的存储。ram装置的实例包含动态ram(dram)装置和同步dram(sdram)装置,其可以电子方式存储各个位。所存储位可经组织成可寻址存储器元件(例如,字),其可存储在存储器组中。为了接收和发射位,ram装置可以包含某些数据通信电路以及适用于保存并从存储器组检索位的通信线路。在某些dram及sdram装置中,输入缓冲器可用于存储可在高速(例如超过6gbps的速度)下发射的数据。

14.在某些实施例中,本文中所描述的输入缓冲器可安置于接地参考信令(grs)接收器中,所述接收器可包含于例如某些存储器装置中且适合于接收经由通信信道从grs发射器发射的数据。在grs系统中,接地可为唯一的信号返回网络,其可通过从返环路径去除电力输送网络(pdn)而实现通信链路的两端处的高质量端接。也就是说,接地可用作唯一的信号参考电压,所发射电压可与信号参考电压进行比较以导出例如逻辑1或逻辑0数据。在某些实施例中,输入缓冲器或接收器可为将单端信号转换成差分输出的伪差分共栅极输入缓冲器,如下文进一步描述。在某些实施例中,伪差分共栅极输入缓冲器可包含共模反馈(cmfb)结构或环路,而在其它实施例中,可去除cmfb结构或环路。因此,可改进在较高速率(例如,超过6gbps)下的信号处理。

15.现在转而参考各图,图1是说明存储器装置10的某些特性的简化框图。具体来说,图1的框图是说明存储器装置10的某些功能性的功能框图。根据一个实施例,存储器装置10

可为第五代双数据速率同步动态随机存取存储器(ddr5 sdram)装置。与先前各代ddr sdram相比,如本文进一步描述的ddr5 sdram的各种特征允许减少的功率消耗、更多的带宽,及更多的存储容量。

16.存储器装置10可包含数个存储器组12。举例来说,存储器组12可以是ddr5 sdram存储器组。存储器组12可设置在布置于双列直插式存储器模块(dimm)上的一或多个芯片(例如,sdram芯片)上。应了解,每个dimm可包含多个sdram存储器芯片(例如,x8或x16存储器芯片)。每一sdram存储器芯片可包含一或多个存储器组12。存储器装置10表示具有数个存储器组12的单个存储器芯片(例如,sdram芯片)的部分。对于ddr5,存储器组12可进一步经布置以形成组群。举例来说,对于8千兆字节(gb)ddr5 sdram,存储器芯片可包含布置成8个组群的16个存储器组12,每一组群包含2个存储器组。对于16gb ddr5 sdram,存储器芯片可例如包含布置成8个组群的32个存储器组12,每一组群包含4个存储器组。取决于整个系统的应用和设计,可利用存储器装置10上的存储器组12的各种其它配置、组织和大小。

17.存储器装置10可包含命令接口14和输入/输出(i/o)接口16。命令接口14经配置以提供来自外部装置(未示出)的多个信号(例如,信号15),所述外部装置例如处理器或控制器。处理器或控制器可将各种信号15提供到存储器装置10以促进待写入到存储器装置10或从存储器装置10读取的数据的发射和接收。

18.如将了解,命令接口14可包含数个电路,例如时钟输入电路18和命令地址输入电路20,例如以确保对信号15的恰当处置。命令接口14可从外部装置接收一或多个时钟信号。一般来说,双数据速率(ddr)存储器利用系统时钟信号的差分对,在本文中被称为真时钟信号(clk_t)及互补时钟信号(clk_c)。ddr的正时钟边缘指代上升真时钟信号clk_t与下降互补时钟信号clk_c交叉的点,而负时钟边缘指示下降真时钟信号clk_t的转变及互补时钟信号clk_c的上升。命令(例如,读取命令、写入命令(wrcmd)等)通常在时钟信号的正边缘上输入,且数据在正时钟边缘和负时钟边缘两者上发射或接收。

19.时钟输入电路18接收真时钟信号(clk_t)和互补时钟信号(clk_c)且产生内部时钟信号clk。内部时钟信号clk供应给内部时钟产生器,例如延迟锁定环路(dll)电路30。dll电路30基于所接收的内部时钟信号clk产生相控内部时钟信号lclk。相控内部时钟信号lclk供应到例如i/o接口16,并用作用于确定读取数据的输出定时的定时信号。

20.内部时钟信号clk也可以提供到存储器装置10内的各种其它组件,且可用以产生各种额外内部时钟信号。举例来说,内部时钟信号clk可提供到命令解码器32。命令解码器32可从命令总线34接收命令信号且可对命令信号进行解码以提供各种内部命令。举例来说,命令解码器32可经由总线36向dll电路30提供命令信号,以协调相控内部时钟信号lclk的产生。相控内部时钟信号lclk可用以例如通过io接口16对数据进行计时。

21.此外,命令解码器32可以对例如读取命令、写入命令、模式寄存器集命令、激活命令等命令进行解码,并且经由总线路径40提供对与所述命令相对应的特定存储器组12的存取。如将了解,存储器装置10可包含各种其它解码器,例如行解码器和列解码器,以促进对存储器组12的存取。在一个实施例中,每一存储器组12包含组控制块22,所述组控制块22提供必需的解码(例如,行解码器和列解码器)以及其它特征,例如时序控制和数据控制,以促进来往于存储器组12的命令的执行。

22.存储器装置10基于从例如处理器的外部装置接收的命令/地址信号而执行例如读

取命令和写入命令的操作。在一个实施例中,命令/地址总线可以是用于容纳命令/地址信号(ca《13:0》)的14位总线。使用时钟信号(clk_t和clk_c)将命令/地址信号计时到命令接口14。命令接口14可包含命令地址输入电路20,其经配置以通过例如命令解码器32接收和发射命令以提供对存储器组12的存取。另外,命令接口14可以接收片选信号(cs_n)。cs_n信号使得存储器装置10能够处理传入ca《13:0》总线上的命令。对存储器装置10内的特定组12的存取通过命令在ca《13:0》总线上编码。

23.另外,命令接口14可经配置以接收数个其它命令信号。举例来说,可以提供裸片终端上的命令/地址(ca_odt)信号以促进存储器装置10内的恰当阻抗匹配。举例来说,在加电期间可使用重置命令(reset_n)来重置命令接口14、状态寄存器、状态机等等。命令接口14也可接收命令/地址反相(cai)信号,可提供所述命令/地址反相信号以例如取决于特定存储器装置10的命令/地址路由而使命令/地址总线上的命令/地址信号ca《13:0》的状态反相。还可提供镜像(mir)信号以促进镜像功能。基于特定应用中的多个存储器装置的配置,mir信号可用于多路复用信号,使得其可调换以用于实现信号到存储器装置10的某一路由。还可提供用于促进存储器装置10的测试的各种信号,例如测试启用(ten)信号。举例来说,ten信号可用于将存储器装置10置于测试模式以用于连接性测试。

24.命令接口14还可用于针对可检测到的某些错误将警报信号(alert_n)提供到系统处理器或控制器。举例来说,可在检测到循环冗余校验(crc)错误的情况下从存储器装置10发射警报信号(alert_n)。也可以产生其它警报信号。此外,用于从存储器装置10发射警报信号(alert_n)的总线和引脚可在某些操作期间用作输入引脚,所述操作例如如上文所描述的使用ten信号执行的连接性测试模式。

25.通过经由io接口16发射和接收数据信号44,可以利用上文所论述的命令和时钟信号,将用于读取和写入命令的数据发送到存储器装置10和从存储器装置10发送数据。更确切地说,数据可经由包含多个双向数据总线的数据路径46发送到存储器组12或从存储器组12检索数据。通常被称作dq信号的数据io信号通常在一或多个双向数据总线中发射和接收。对于例如ddr5 sdram存储器装置等某些存储器装置,io信号可划分成上部和下部字节。举例来说,对于x16存储器装置,可以将io信号划分成对应于例如数据信号的上部和下部字节的上部和下部io信号(例如,dq《15:8》和dq《7:0》)。用于读取和写入的数据(例如,io信号)可经寻址到存储器组12中的某一存储器(例如,存储器单元)。

26.本文中所描述的技术实现可处理经由i/o接口16传达的输入信号(例如,dq《15:8》和dq《7:0》)的通信系统50。通信系统50可包含可使用vss终端(在lpddr5的情况下)的接收器系统(例如,接地参考信令(grs)接收器系统)或使用vddq终端(在ddr5的情况下)的接收器系统,其又可包含一或多个共栅极(cg)输入缓冲器,例如伪差分共栅极输入缓冲器,适合于放大经由通信信道接收的传入信号以供进一步变换成逻辑数据(例如,逻辑高和逻辑低数据),如下文进一步描述。cg输入缓冲器可包含改进的共源极结构,所述共源极结构可使用如下文进一步描述的输入和电压参考(vref)组合来维护更稳定的电流,因此改进过程、电压、温度(pvt)条件且减少工作循环偏移,这又可改进较高速度下的操作。

27.阻抗(zq)校准信号还可通过io接口16提供到存储器装置10。zq校准信号可提供到参考引脚且用于通过跨过程、电压和温度(pvt)值的改变调整存储器装置10的上拉和下拉电阻器来调谐输出驱动器和odt值。因为pvt特性可影响zq电阻器值,所以zq校准信号可提

供到zq参考引脚以用于调整电阻以将输入阻抗校准到已知值。如将了解,精密电阻器通常耦合在存储器装置10上的zq引脚与存储器装置10外部的gnd/vss之间。在vss终端的情况下,zq可连接到vddq电力。此电阻器充当用于调整内部odt和io引脚的驱动强度的参考。

28.此外,可通过io接口16将环回信号(loopback)提供到存储器装置10。环回信号可在测试或调试阶段期间用于将存储器装置10设置在其中信号通过同一引脚环回到存储器装置10的模式下。举例来说,环回信号可用于设置存储器装置10以测试存储器装置10的数据输出(dq)。环回可包含数据和选通两者或可能仅包含数据引脚。这通常意图用于监测在io接口16处由存储器装置10捕获的数据。如将了解,还可将各种其它组件并入到存储器系统10中,例如电源电路(用于接收外部vdd和vss信号)、模式寄存器(用于定义可编程操作和配置的各种模式)、温度传感器(用于感测存储器装置10的温度)等。

29.说明通信系统50的实施例将是有益的。因此,图2描绘具有经由通信信道104通信地耦合到接收器102的发射器100的通信系统50的实施例。应理解,所描绘的实施例仅为简化实例,可用于说明,且其它通信系统50可包含更多或更少组件和/或连接。在某些实施例中,通信系统50可为可例如用于存储器装置10与处理器、现场可编程门阵列(fpga)、图形处理单元(gpu)、专用芯片等之间的接口的封装上片上芯片通信系统。在其它实施例中,通信系统50可为芯片上通信系统,例如芯片上串行链路系统,其适合于例如在一或多个核心与存储器系统(例如,系统10)之间通信。

30.发射器100可为vss终端的信令发射器或接地参考信令(grs)发射器(例如,使用接地作为参考电压),可接着从其比较发射信号以便导出例如逻辑低和/或逻辑高数据的数据。在某些实施例中,通信信道104可为中介层信道,例如将硅衬底用作到接收器102中的高密度和/或三维(3d)封装中的通信媒体的硅(si)中介层信道。接收器102可为使用vref作为参考电压的伪差分接收器或还使用接地作为参考电压的grs接收器,从所述参考电压与传入信号进行比较以用于将信号转换成逻辑低和/或逻辑高数据或转换成非二进制数据。通信系统50可包含可基于所使用的通信信道104的类型在值上变化的特定发射(tx)和接收(rx)电容负载106、108。还展示输入线路终端电阻器112,所述输入线路终端电阻器112可用于例如在通信信道104中最小化反射或“重像”。

31.当通信系统50包含使用例如伪差分共栅极输入缓冲器等grs技术时,可使用接地环路114,适合于提供用于grs发射器100和grs接收器102两者的单个接地参考。在某些实施例中,接地参考可用于中心或中间电压参考,使得可通过感测高于接地参考的信号而导出波形峰值,且可通过感测低于接地参考的信号而导出波形谷值。应注意,接地环路114可连接到接收器102的任何数目个组件,包含输入线路终端电阻器112。当通信系统50包含ddr5的使用时,ddr5使用vddq终端,而lpddr5使用vss终端。在一个实例中,在vss终端的情况下,vil=vss,vih=200mv,且在vddq终端的情况下,vil=vddq-200mv,vih=vddq)。可因此使用vss终端以及vddq终端。如果需要vddq终端,那么电路可反转vddq/vss且反转nmos和pmos。

32.并且,通信系统50被设计成接收vref信号。当然,如果在不连接vref信号的情况下将其设置为vss,那么可将其用作grs输入缓冲器。如果使用vref,那么不必连接终端电阻器。这是因为vref信号充当参考且很好地维持共模。但如果不连接vref,那么在vss侧上需要终端电阻器。如果不存在vref信号,那么合适的终端电阻器应放置在vss侧上以使得良好

地形成共模。因此,解释两种情况将为良好的。

33.接收器102可以是或可包含输入缓冲器电路(例如,伪差分共栅极输入缓冲器电路)以提供适合于解密经由通信信道104传达的数据的某些功能。举例来说,接收器102可提供用于信号预放大的增益,提供输入波形的电平移位(例如,将输入信号的电压升高和/或降低设定量),和/或提供用于高频(例如,超过6gbs的频率)通信信道104衰减的补偿。本文中所描述的技术包含共栅极输入缓冲器电路,如下文进一步描述,其使得接收器102能够以更有效且稳固的方式更有效地提供前述功能中的一或多者,因此改进过程、电压、温度(pvt)条件且减少工作循环偏移,这又可改进较高速度下的操作。

34.图3为说明可包含于接收器102中的伪差分共栅极输入缓冲器电路200的实施例的示意图。伪差分共栅极输入缓冲器电路200可用于从单端信号转换到差分信号,例如,通过将单个输入信号转换成两个输出信号。输入信号可被放大和/或滤波,例如,以去除符号间干扰(isi)。isi可由高频振幅和相位失真引起,所述高频振幅和相位失真可使接收侧的数据位“拖尾”。本文中所描述的技术包含伪差分共栅极输入缓冲器电路,所述伪差分共栅极输入缓冲器电路包含适合于输入缓冲器电路200中的频率增益和/或频率抑制的ctle系统。举例来说,本文中所描述的输入缓冲器电路200可通过恢复可能归因于通信信道衰减而丢失的频率内容(例如,经由放大)来补偿信号行进穿过通信信道之后的损失,且进一步抑制可能关注噪声(例如,噪声放大)的某些频率。此外,如下文进一步描述,如所描绘的伪差分共栅极输入缓冲器电路200包含适合于辅助维持共模的共模反馈偏置(cmfb)结构或环路。

35.在所描绘的实施例中,可经由输入节点202将例如从控制器(例如,组控件22)传入的输入信号发射到电路200中以将数据存储在相应存储器组12中。待存储的数据可包含可经由通信信道104发射的表示逻辑高和/或逻辑低数据的高频率(例如,6gbps或更高的)信号。在所描绘的实施例中,连续时间线性均衡器(ctle)电路206、218可处理表示二进制数据的传入高频信号(例如,单端信号)。信号可先前已行进穿过系统内部的各种互连件到达其目的地(例如,输入缓冲器200),因此在发射器、连接器、迹线、布线和接收器处诱发的任何电降级可对信号的时序和质量具有影响。举例来说,信号中的波形失真可由例如短线和通孔的阻抗失配、频率相依性衰减和信号迹线之间的电磁耦合(例如,串扰)引起。此外,移动穿过信道的高速信号可经受高频损伤,例如反射、电介质损耗和归因于皮肤效应的损耗。这些损伤可降低信号的质量,使得接收器系统(例如,输入缓冲器电路200)正确地解译信号数据更成问题。

36.因此,传入信号可被放大和/或滤波。在所描绘的实施例中,ctle有源电感器电路206可处理信号以增加高频增益和/或扩展带宽(例如,直流电(dc)增益减小且dc信号增益减小)。也就是说,ctle有源电路206可包含表现为电感器的组件,其中电阻元件208(例如,电阻器)耦合到用于驱动开关装置212(例如,晶体管)的电容性元件210(例如,电容器)。ctle有源电感器电路206还可包含耦合到开关装置212的漏极的电容性元件216。

37.展示三个其它ctl和/或有源电感器电路218、220和222,具有相应电阻性元件224、226、228、电容性元件230、232、234和开关装置236、254、256。还展示分别包含于ctl和/或有源电感器电路218、220和222中的电容性元件242、244、246(例如,负载电容器)。包含交叉耦合的p型金属氧化物半导体(pmos)电路248,例如,其可引入正反馈以增加信号增益,例如高过渡信号增益。在所描绘的实施例中,交叉耦合的pmos电路248包含彼此交叉耦合(例如,经

由栅极耦合)的两个开关装置250、252。开关装置250可包含连接到ctle有源电感器电路206的源极和漏极,而开关装置252可包含连接到ctle有源电感器电路218的源极和漏极。开关装置250、252可因此用于将正反馈引入到电路206和218中以增加有源电感器质量因子。应注意,vss可指代接地电位电压,且vperi可指代电源电位与接地电位vss之间的电位差。

38.开关装置238和240描绘于共栅极(例如,栅极连接到偏置,而源极充当输入且漏极充当输出)中,且分别在共源极配置(栅极连接到输入,而源极连接到地面且漏极充当输出)中。对于接地参考信令,vref信号连接到vss,且112和334的vss终端电阻器用于控制输出信号的共模。另一方面,当使用vref信号时,不需要连接334电阻器。vref信号将为输入的vih/vil的中间电平。

39.开关装置238可经由节点202放大输入信号,而开关装置240可通过节点258放大vref。例如,归因于开关装置238与240之间的不对称信号放大路径,在节点260(例如,von节点)处的信号摆幅可小于在节点262(例如,vop节点)处的信号摆幅。因此,伪差分共栅极输入缓冲器电路200可包含共模反馈(cmfb)环路,其可辅助将xa和xb的共模维持为中心。也就是说,cmfb环路可比较第1级输出266和第2级输出268的共模电压(例如,纵向电压或电压的半和),且调节输入偏置分支(例如,经由开关装置272、244的栅极),使得第1级输出xa、xb居中(例如,通过将输出信号与例如逆变器阈值vdd/2的阈值匹配)。还展示电阻器334(rbot电阻器),其可经调谐以提供所要的输入参考偏移。

40.cmfb环路可包含cmfb放大电路270,其可例如经由节点276将信号传送到开关装置272、274。cmfb电路270可用于保持xa和xb节点的共模恒定。由于za、zb信号为执行全摆幅的反相器的输出信号,因此其以vperi/vss摆动。za/zb的中心电平zm具有vperi/2的偏置且充当参考。当xa、xb信号的共模上升时,ym也上升,且cmfb电压通过270比较器下降。当cmfb电压下降时,电流通过272、274pmos增加,并且na3和nb3电压上升。最终,xa和xb信号被降到恒定电平,并且共模通过反馈保持恒定。也就是说,cmfb放大电路270可耦合到电路204的输入分支(例如,节点202分支)开关装置272和电压参考分支开关装置274(例如,vref节点258分支)的栅极,且接着产生可经由zm节点278和ym节点280使用以提供用于输出电路282的输出266、268的共模反馈偏置的zm和ym信号。cmfb环路的“环路”部分可指代电路204到电路282之间的连接(例如,经由节点284、286),接着为电路282与电路270之间的连接(例如,经由节点278、280),且接着从电路270返回到电路204(例如,经由节点276)。

41.输出电路282经由xa节点284和xb节点286连接到电路204,且更确切地说,连接到ctle有源电感器电路206和ctle有源电感器电路218。经由xa节点284和xb节点286传入到输出电路282的信号可因此被放大和滤波,以及具有经由例如电阻器288、290、292、294减小的输出信号的摆幅电压。更确切地说,输出电路282包含耦合到电阻器288、292的开关装置296、298,耦合到电阻器290、294的开关装置300、302,耦合到电阻器292的开关装置304、306,以及耦合到电阻器294的开关装置308、310,以提供xa和xb信号的共模处理。某些电容元件(例如,电容器)312、314、316和318还可用于输出电路282中,适合于存储电荷和/或滤波信号。

42.如上文所提及,cmfb放大电路270可使用反馈来提供共模反馈偏置。在所说明的实施例中,开关装置322、324经由正反馈环路耦合(例如,漏极耦合),而开关装置326、328经由负反馈环路耦合(例如,源极耦合)。开关装置322、328经由源极和漏极彼此耦合,而开关装

置324、326也经由源极和漏极彼此耦合。cmfb放大电路270还可包含可经由其相应栅极彼此耦合的开关装置330、332。开关装置330、332的栅极可耦合到开关装置322、328的源极和漏极。开关装置330的源极可耦合到开关装置322、324的漏极,而开关装置332的漏极可耦合到开关装置326、328的源极。cmfb放大电路270可比较zm和ym节点的共模信号,且当ym为低时(例如,表示当xa、xb信号为低时),cmfb偏置经比较且升高,且因此降低na3和nb3节点信号(例如,使得xa、xb信号升高以进行补偿)。举例来说,以此方式,cmfb放大电路270可处理信号以调节输出266、268。

43.作为伪差分共栅极输入缓冲器电路204的高电平概述,差分输入信号放大可经由开关装置206、218提供,从而产生差分信号xa、xb。用于信号xa、xb的ctle处理可经由有源感应电路(例如,电路206、218)提供,所述有源感应电路可经由交叉耦合的pmos电路248耦合。交叉耦合的pmos电路248可提供xa和xb的增益增加,以及相应输出信号266、268。交叉耦合电路220、222可提供放大开关装置238、240的偏置(例如,选择所要电流)。cmfb放大电路270可辅助偏置放大开关装置272、274且提供输出信号到阈值(例如,vdd/2)的较好匹配。

44.在一些情况下,可能不需要cmfb环路(例如,cmfb放大电路270和/或连接到cmfb放大电路270的某些组件)。举例来说,例如大工作循环变化、大电流变化等一些“角点”条件可导致不按需要的电路pvt条件。因此,本文中所描述的技术包含去除了cmfb环路的伪差分共栅极输入缓冲器电路的实施例,如图4中所示。

45.图4为说明可不包含cmfb环路的伪差分共栅极输入缓冲器电路400的实施例的示意图。因为所说明的实施例包含与图3中所展示的组件相同的组件中的一些,所以使用相同元件编号对所述组件进行编号。如在图3的伪差分共栅极输入缓冲器电路200中,输入节点202可接收传入信号,因此将数据存储在存储器组12中。开关装置238可放大用于第一分支(例如,节点260分支)的输入信号,而开关装置240可放大用于电路402的第二分支(例如,节点262分支)的信号。用于信号xa、xb的ctle处理可经由有源感应电路(例如,电路206、218)提供,所述有源感应电路可经由交叉耦合的pmos电路248耦合。交叉耦合的pmos电路248可提供xa和xb的增益增加。交叉耦合电路220、222可提供放大开关装置238、240的偏置(例如,选择所要电流)。

46.电路402大体上类似于具有某些微小变化的电路204。举例来说,开关装置272、274不再连接到cmfb放大电路270,因为cmfb放大电路270不再存在。实际上,开关装置272的栅极现在可以耦合到输入节点202,并且开关装置274的栅极可以耦合到节点258(例如,vref节点)。另外,当电路402、404在节点286、286处连接而不是以环路方式连接时,电路204的“环路”部分不再存在。

47.电路404可为反相器电路且包含输出406和408。电路404(例如,共源极结构)可提供比先前cmfb的偏置电路更高的增益,以通过去除电阻来增加284、286信号的电压摆幅。节点202处的输入信号和节点258处的vref信号的共模可控制电流镜用于更稳定的操作。随着na3节点和nb3节点的偏置减小,开关装置238、240的共栅极的电流对应地减小。因此,不同于先前电路,其消耗稳定电流且以改进的稳定性操作。通过应用共源极结构404,当与图3的电路200的增益相比较时,xa节点284和xb节点286的增益可更高。此外,当与图3的电路200相比较时,可能已进一步改进退出xa时序和退出xb时序之间的时序。

48.在所描绘的实施例中,节点xa 284可耦合到开关装置410和412的栅极,因此控制

开关装置410、412的源极。同样地,节点xb 286可耦合到开关装置414、416的栅极,因此控制开关装置414、416的源极。节点za 418(例如,可用于共模处理的共模节点)展示为连接到开关装置420、422的栅极。节点zb 424(例如,可用于公共节点处理的共模节点)展示为连接到开关装置426、428的栅极。

49.还展示了反相器430、432。反相器430、432可用于将电路404的za节点418分支(例如,第一或顶部分支)耦合到zb节点424分支(例如,第二或下部分支)。还展示了电容性元件434、436。通过提供伪差分共栅极输入缓冲器电路400,本文所描述的技术可舍弃cmfb环路的使用且改进增益、工作循环,且更一般来说,实现存储器装置10的改进pvt特性。在cmfb电路中,282电路为反相器电路,且za、zb节点和266、268节点为全摆幅信号。因此,其是归因于反馈环路而改进共模的xa和xb信号,并且266和268可能不具有影响。并且,保持恒定电流为402电路的作用,且406、408输出信号不相关。cmfb输出信号不在图4的电路400中使用,且in/vref信号通过将in/vref信号连接到pmos(例如,272、274)而具有与cmfb输出信号类似的效果。对于接地参考信令,可不使用vref,且接着将电阻器112和334的vss终端用于控制输出信号的共模。

50.虽然本文描述的实施例可能易有各种修改和替代形式,但特定实施例已经在图中借助于实例展示且将在本文中详细描述。然而,应理解所公开的内容并不意图限于所公开的特定形式。实际上,本公开涵盖属于如由所附权利要求书限定的本公开中所描述的技术和系统的精神和范围内的所有修改、等效物和替代方案。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。