用于三维交叉点存储器的层级选择晶体管

背景技术:

1.三维(3d)交叉点存储器阵列可具有存储器单元的叠层(tier)或层级 (deck)。然而,以这种方式增大存储器单元的总数可能会成比例地增大所 需的解码器晶体管的数量,从而增大解码器晶体管的总的覆盖区。因此, 需要解决方案来增大存储器密度,同时最小化解码器晶体管覆盖区。

附图说明

2.在附图中通过示例而非限制的方式来示出本文描述的材料。为了图示 的简单和清楚起见,图中所示的要素不一定按比例绘制。例如,为了清楚 起见,一些要素的尺寸可能相对于其他要素被夸大。此外,为了讨论的清 楚,各种物理特征可以以他们简化的“理想”形式和几何形状表示,但是仍然 应当理解,实际实施方式可能仅接近所示的理想。例如,可能会绘制平滑 表面和正方形交叉点,而不考虑通过纳米制造技术形成的结构的有限粗糙 度、角圆化和不完美的角度交叉特性。此外,在认为合适的情况下,在图 中重复了参考标签以指示对应的或类似要素。

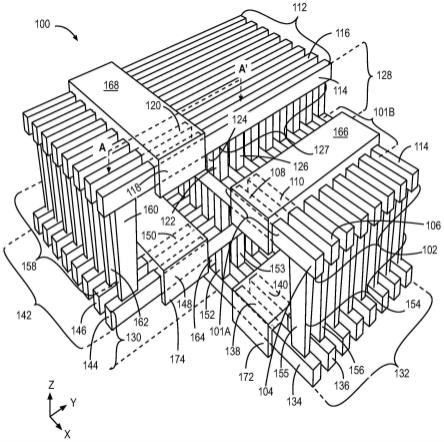

3.图1是根据本公开的实施例的存储器设备结构的等距图示,其中存储 器设备结构包括多个晶体管。

4.图2a是根据本公开的实施例的图1中的存储器设备结构的部分的等距 图示。

5.图2b是穿过图2a中的线结构的截面图示。

6.图2c是穿过与图2a中的线结构正交的线的截面图示。

7.图2d是图2a中的线结构的门控(gated)部分的截面图示。

8.图3a是根据本公开的实施例的图1中的存储器设备结构的部分的等距 图示。

9.图3b是图3a中的线结构的截面图示。

10.图3c是图3a中的线结构的门控部分的截面图示。

11.图4a是根据本公开的实施例的图1中的存储器设备结构的部分的等距 图示。

12.图4b是图4a中的线结构的截面图示。

13.图4c是图4a中的线结构的门控部分的截面图示。

14.图4d是穿过与图4a中的线结构正交的线的截面图示。

15.图5a是穿过图1中的线a-a'的存储器设备的结构的截面图示。

16.图5b是根据本公开的实施例的存储器单元的截面图示。

17.图5c是根据本公开的实施例的非易失性存储器元件的截面图示。

18.图5d是根据本公开的实施例的非易失性存储器元件的截面图示。

19.图5e是根据本公开的实施例的选择器元件的截面图示。

20.图6是制造诸如结合图2a、3a或4a描述的设备结构的设备结构的方 法。

21.图7a是根据本公开的实施例在衬底上方的电介质中图案化的多个互 连的截面图示。

22.图7b是图7a中结构的等距图示。

23.图8a示出了在衬底上方形成多个线段之后的图7a的结构。

24.图8b是图8a中结构的等距图示。

25.图9示出了在多个线段中的每个之间形成电介质以形成块之后的图8b 的结构。

26.图10a示出了在蚀刻块的部分的工艺之后的图9的结构。

27.图10b是图10a中的线结构的截面图示。

28.图11a示出了在多条线结构之上形成薄膜沟道(tf沟道)材料之后的 图10a的结构。

29.图11b是穿过多个线结构的截面图示。

30.图12a是图11b中的结构在去除相邻的线结构的部分之间的沟道材料 的部分的工艺之后的截面图示。

31.图12b是图11b中的结构在从线结构上方去除沟道材料的部分的工艺 之后的截面图示。

32.图13a示出了在形成栅极电介质层1300之后的图11b的结构。

33.图13b是穿过图13a中的多个线结构的截面图示。

34.图14a示出了在形成栅极电极之后的图13a的结构。

35.图14b是图14a中的多个线结构之上的栅极电极的截面图示。

36.图15a示出了图9的结构,其中利用ald沉积工艺来选择性地在线结 构的部分周围沉积tft沟道材料。

37.图15b是图15a中的线结构周围的栅极电极的截面图示。

38.图16a示出了在形成多个开口之后的图9的结构。

39.图16b示出了在多个开口中的每个开口中在电介质702上形成牺牲电 介质之后在电介质1604上形成沟道层1606之后的图16a的结构。

40.图16c示出了在减小沟道的高度的工艺之后的图16d的结构。

41.图16d示出了在形成栅极电介质层之后的图16c的结构。

42.图16e示出了在栅极电介质层上形成栅极电极之后的图16d的结构。

43.图16f示出了在去除栅极电介质层的部分的工艺之后的图16e的结构。

44.图16g示出了在形成与每个沟道相邻的源极结构之后的图16f的结构。

45.图17是系统的等距图示,其中存储器设备结构通过多个逻辑晶体管和 外围部件耦合。

46.图18是计算系统的示例的框图,该计算系统包括与存储器设备阵列耦 合的层级选择晶体管阵列以实现解码器晶体管覆盖区缩放。

47.图19是移动设备的示例的框图,该移动设备包括与存储器设备阵列耦 合的层级选择晶体管阵列以实现解码器晶体管覆盖区缩放。

具体实施方式

48.描述了用于3维(3d)交叉点的层级选择晶体管和制造方法。在以下 描述中,阐述了许多具体细节,诸如结构方案和详细的制造方法,以提供 对本公开的实施例的透彻理解。对于本领域技术人员来说显而易见的是, 可以在没有这些具体细节的情况下实践本公开的实施例。在其他情况下, 不那么详细地描述众所周知的特征(诸如与存储器设备和晶

体管相关联的 操作),以免不必要地混淆本公开的实施例。此外,应当理解,图中所示的 各种实施例是说明性表示并且不一定按比例绘制。

49.在一些情况下,在以下描述中,众所周知的方法和设备以框图形式示 出而不是详细示出,以避免混淆本公开。在整个说明书中对“实施例”或“一 个实施例”或“一些实施例”的引用意指结合实施例描述的特定特征、结构、 功能或特性包括在本公开的至少一个实施例中。因此,在整个说明书的各 个地方出现的短语“在实施例中”或“在一个实施例中”或“一些实施例”不一 定指本公开的相同实施例。此外,特定特征、结构、功能或特性可以在一 个或多个实施例中以任何合适的方式组合。例如,在与两个实施例相关联 的特定特征、结构、功能或特性不相互排斥的任何地方,第一实施例可以 与第二实施例组合。

50.如说明书和所附权利要求书中使用的,单数形式的“一”、“一个”和“该

”ꢀ

也旨在包括复数形式,除非上下文另有明确说明。还应当理解,本文使用 的术语“和/或”指并涵盖一个或多个相关联的所列项目中的任何和所有可能 的组合。

51.术语“耦合”和“连接”及其派生词在本文中可以用于描述部件之间的功 能或结构关系。应当理解,这些术语并非旨在作为彼此的同义词。相反, 在特定实施例中,“连接”可以用于指示两个或更多个元件彼此直接物理、光 学或电接触。“耦合”可以用于指示两个或多个元件直接或间接(在它们之间 有其他居间元件)物理、电或磁接触,和/或两个或多个元件彼此协作或交 互(例如,在因果关系中)。

52.如本文所用,术语“在

……

之上”、“在

……

之下”、“在

……

之间”和

ꢀ“

在

……

上”是指一个部件或材料相对于其他部件或材料的相对位置,其中这 种物理关系是值得注意的。例如,在材料的上下文中,安置在一种材料之 上或之下的另一种或多种材料可以直接接触或者可以具有一种或多种居间 材料。此外,安置在两种材料之间的一种材料可以直接与两层接触或者可 以具有一个或多个居间层。相比而言,在第二材料“上”的第一材料与该第二 材料(单种或多种)直接接触。在部件组件的上下文中进行类似的区分。 如遍及本说明书以及在权利要求中所使用的,由术语“至少一个”或“一个或 多个”连接的项目列表可以意指所列术语的任何组合。

53.这里的术语“相邻的”一般是指一个事物邻近(例如,紧邻或靠近,它们 之间有一个或多个事物)或邻接另一事物(例如,毗连它)的位置。

54.术语“信号”可以指至少一个电流信号、电压信号、磁信号或数据/时钟 信号。“一”、“一个”和“该”的含义包括复数引用。“在

……

中”的含义包括

ꢀ“

在

……

中”和“在

……

上”。

55.根据术语“设备”的使用的上下文,术语“设备”通常可以指装置。例如, 设备可以指层或结构的堆叠体、单个结构或层、具有有源和/或无源元件的 各种结构的连接等。通常,设备是具有沿xyz笛卡尔坐标系的xy方向的平 面和沿z方向的高度的三维结构。设备的平面也可以是包括该设备的装置 的平面。

56.如遍及本说明书以及在权利要求中所使用的,由术语“至少一个”或“一 个或多个”连接的项目列表可意指所列术语的任何组合。

57.除非在他们使用的明确上下文中另有说明,否则术语“基本上相等”、“大 约相等”和“大致相等”意指所描述的两个事物之间仅存在偶然的变化。在本 领域中,这种变化通常不超过预定目标值的 /-10%。

如,第一互连过孔可以用于耦合该对字线,而第二互连过孔可以将最低字 线耦合到解码器晶体管。随着层级的数量的增大,来自每个相继层级的相 应字线可以通过居间互连过孔耦合在一起。对应于最低水平面层级的最低 字线还可以耦合到最低层级下方的单个解码器晶体管。

64.类似地,第一层级的每条位线可以通过互连过孔与直接在下方的第二 层级的对应位线耦合。每对位线通过互连过孔耦合到单个解码器晶体管。 当层级的数量增大时,来自每个相继的层级的相应位线彼此耦合并耦合到 单个解码器晶体管。例如,来自第一层级的第一位线可以与来自直接在第 一位线上方的第二层级的第一位线耦合。因此,存储器阵列中的解码器晶 体管的总数等于任何给定层级上的字线和位线的总数,并且与层级的数量 无关。在操作期间,跨多个层级耦合的所有字线(位线)可以同时被偏置。 然而,因为在每个层级上的存储器单元和互连过孔之间存在居间层级选择 晶体管,所以可以通过偏置适当的层级选择晶体管来选择待编程的单个存 储器单元。

65.当每个层级包括大数量的字线和位线(例如8k)时,导通每个层级选 择晶体管将需要大数量的布线。为了减轻对每个晶体管单独布线的问题, 单个层级的每条字线(位线)上的每个层级选择晶体管的栅极可以电耦合 在一起。单个布线导体可以与单个层级选择晶体管耦合。在操作期间,单 个层级的字线(位线)上的所有层级选择晶体管将处于相同的栅极偏置。 然而,单个层级选择晶体管和单个字线-位线组合可以被偏置以对单个存储 器单元进行编程。

66.在第一层级选择晶体管实施例中,每条字线(位线)包括完全氧化的 线部分(本文中,氧化线部分)以形成电中断,并且沟道材料与氧化线部 分的至少一个侧壁相邻。在一些这样的实施例中,栅极结构与沟道材料相 邻并且在氧化线部分的任一侧上的字线(或位线)的紧邻(immediate)导 电部分可以用作层级选择晶体管的源极或漏极区域。在一些实施例中,沟 道材料完全包覆氧化线部分,并且栅极结构包覆沟道材料。在示例性实施 例中,晶体管是包括非晶或多晶沟道的薄膜晶体管。

67.在第二层级选择晶体管实施例中,每条字线(位线)被分成共线的两 条导电线段,其中沟道材料(也共线)在两条导电线段之间并与两条导电 线线段共线。沟道材料任一侧上的两条导电线段可用作第二层级选择晶体 管实施例的源极或漏极区域。在一些这样的实施例中,栅极结构与沟道材 料的两个或更多个表面相邻。在示例性实施例中,栅极结构在沟道材料的 三个表面上(例如,在顶表面和两个侧壁表面上)并且层级选择晶体管是 fin-fet设备。

68.图1是包括层级选择晶体管(诸如层级选择晶体管101a和101b)的 存储器设备结构100的等距图示。存储器设备结构100包括沿第一方向(例 如,x轴)的第一线结构102(本文中线结构102)。线结构102包括与线结 构106(本文中线106)相邻的线104(本文中线104),其中线104包括沟 道108并且线106包括晶体管沟道110。存储器设备结构100还包括沿着第 二方向(例如,y轴)的第二多个线结构112(本文中线结构112)。如所示, 线结构112沿y轴定向。线结构112包括与线116相邻的线114,其中线114 包括晶体管沟道118并且线116包括晶体管沟道120。

69.存储器设备结构100还包括在线结构102和线结构112之间的每个交 叉点处的存储器单元。每个层级的存储器单元的总数等于线结构102中的 线的数量与线结构112中的

线的数量的乘积。如所示,存储器设备结构100 在单个层级上包括64个存储器单元。例如,存储器设备结构100的示例包 括在线104和线结构114之间的交叉点处的存储器单元122、在线104和线 116之间的交叉点处的存储器单元124、在线106和线结构114之间的交叉 点处的存储器单元126。

70.在实施例中,存储器设备结构100包括多层线结构,诸如线结构102 和112。被存储器单元的阵列(诸如存储器单元阵列127)分开的每对线结 构(诸如线结构102和112)的构成存储器层级。线结构102和112中的线 分别作为多个字线和位线对操作(或反之亦然)。在说明性实施例中,存储 器结构100包括3个层级。第一层级128包括线结构102和112,以及存储 器单元阵列127。

71.在说明性实施例中,存储器设备结构100还包括在层级128下方的第 二层级130。层级130包括平行于线结构112的多个线结构132(本文中线 结构132)。线结构132包括线134和线136,其中线134包括晶体管沟道 138,并且线136包括晶体管沟道140。

72.存储器设备结构100还包括平行于线结构112的多个线结构142(本文 中线结构142)。在图中,线结构142具有沿y轴的纵轴。线结构142包括 与线结构146相邻的线结构144,其中线144包括晶体管沟道148,并且线146包括晶体管沟道150。层级130还包括在线结构132和线结构142之间 的每个交叉点处的存储器单元。如所示,存储器单元152位于线结构134 和144之间的交叉点处,并且存储器单元153位于线结构136和144之间 的交叉点处。线结构132和142中的线分别作为多个字线和位线对操作(或 反之亦然)。

73.在说明性实施例中,存储器设备结构100在每个层级包括8

×

8的正交 线的阵列。取决于实施例,层级128或130可以包括2000条至8000条之 间的线。

74.每个层级选择晶体管,例如晶体管101a,包括与沟道相邻的栅极电极 和在栅极电极和沟道之间的居间栅极电介质层。在说明性实施例中,每个 层级选择晶体管,例如,晶体管101a和101b,的单独栅极电极耦合在一 起。如所示,栅极结构166包括线结构102的每条线中的相邻晶体管沟道 的栅极电极。栅极电介质层隔离线结构102中的每个层级选择晶体管(101a、 101b等)的每个沟道层。在实施例中,区别的层级选择晶体管101a、101b 等的栅极电极之间的耦合有利地使得能够实现栅极电极的同时偏置,为其 他基本电路系统节省了大量的空间。在实施例中,在线结构102包括8000 条线时,所有8000个栅极电极可以通过单个布线导体耦合。

75.存储器设备结构100还包括与多个晶体管沟道相邻的栅极结构168、172 和174。栅极结构168、172和174包括栅极结构166的一个或多个特征, 诸如栅极电极和栅极电介质层。应当理解,每个栅极结构166、168、172 和174可以通过一个或多个偏置电极(图中未示出)独立偏置。

76.存储器设备结构100可以包括不同的层级选择晶体管架构,该架构包 括具有不同fet特性(例如,对于n-fet和p-fet)的不同栅极和沟道结 构。

77.图2a是根据本公开的实施例的层级选择晶体管200的等距图示。为清 楚起见,沟道108的部分被去除。如所示,线结构102中的每个线结构具 有沿纵向长度(例如,x轴)具有变化的材料成分的不同部分。在说明性实 施例中,线结构102中的每条线还在yz平面中具有在沟道108内的区域中 沿x方向变化的截面面积。栅极结构202和沟道108的部分被切除以显示 代表性线(例如线104)和沟道(例如沟道108)的形状。在实施例中,栅 极结构202包

括栅极电介质层和栅极电极。在说明性实施例中,为清楚起 见,未示出栅极电介质层。如所示,栅极结构202与线结构102的每条线 中的每个晶体管沟道相邻。

78.图2b是穿过图2a的结构中的线a-a'的层级选择晶体管200的截面图 示。在说明性实施例中,线104具有线部分104a和包括金属或包括金属的 合金的线部分104b,以及线部分104a和线部分104b之间的线部分104c。 在实施例中,线部分104c包括金属和氧。层级选择晶体管200包括沟道 108和沟道108上的栅极结构202。如所示,栅极结构202包括沟道108上 的栅极电介质层202a和栅极电介质层202a上的栅极电极202b。在说明性 实施例中,线部分104a是源极或漏极区域,并且线部分104b是层级选择 晶体管200的漏极或源极区域。在说明性实施例中,端子互连与线部分104b 耦合,并且存储器单元122在线部分104b上并与线部分104b耦合。仅示 出了一个存储器单元,然而线部分104b足够长以包括如图1中所示的多 个存储器单元。再次参考图2b,整个线部分104b可以被认为是源极或漏 极,因为线部分104a和104b是导电的。

79.线部分104c是绝缘的并且沿x轴具有长度lo。在一些实施例中,lo在10nm和500nm之间。线部分104c的长度确定了层级选择晶体管200的 最大有效栅极长度lg。

80.在说明性实施例中,线104还包括线部分104b和104c之间的线部分 104d。线部分104d可以具有与线部分104b相同或基本上相同的材料成分 (composition)。如所示,线104还包括线部分104a和104c之间的部分 104e。线部分104e具有与线部分104a或104b的材料成分相同或基本上 相同的材料成分。线部分104d和104e可以被认为是沟道108之下的横向 源极或漏极延伸。在一些实施例中,线结构部分104a、104d和104e包括 诸如钨、钽或钛的金属。在其他实施例中,线结构部分104a、104d和104e 包括钨、钽或钛中的至少一种和氮。

81.如所示,线部分104d和104e分别具有长度l1和l2。在一些实施例中, l1以及l2分别在10nm和100nm以及10nm和100nm之间的范围内。l1可以等于或不同于l2。

82.如所示,线104相对于最低表面104f具有沿x方向变化的高度。在说 明性实施例中,与远离沟道108相比,线104的高度在沟道108附近降低。 如所示,线部分104a和104b具有高度h1。在实施例中,h1在15nm和 100nm之间。如所示,部分104c、104d和104e具有小于h1的高度h2。 在实施例中,h2在10nm和95nm之间。在示例性实施例中,h2沿x轴基 本上均匀。

83.在说明性实施例中,沟道108沿x轴横向延伸超过线部分104c,并在 线部分104d和104e之上延伸。沟道108具有厚度tc。在说明性实施例中, 沟道108具有基本上等于线部分104a和线部分104c、104d或104e的相 应高度之间的差的厚度tc。在其他实施例中,tc大于或小于线部分104a 和线部分104c、104d或104e的相应高度之间的差。

84.栅极结构202具有小于沟道108的横向宽度(层级选择晶体管200的 l

effective

)的栅极长度。在实施例中,lg在50nm和600nm之间。在说明性 实施例中,栅极结构202没有在线部分104a和104b之上延伸。

85.在实施例中,取决于晶体管是p-fet还是n-fet晶体管,栅极电极202 包括至少一种p型功函数金属或n型功函数金属。n型材料的示例包括铪、 锆、钛、钽、铝、这些金属的合金和这些金属的碳化物(诸如碳化铪、碳 化锆、碳化钛、碳化钽或碳化铝),并且p型材料的示例包括钌、钯、铂、 钴、镍或导电金属氧化物(例如氧化钌)。

86.在实施例中,栅极电介质层202a包括具有高介电常数的材料或高k 材料。栅极电介质层202a的示例包括氧和一种或多种元素(诸如铪、硅、 钛、钽、镧、铝、锆、钡、锶、钇、铅、

钪、铌或锌)。可以用于栅极电介 质层202a中的高k材料的示例包括但不限于氧化铪、铪硅氧化物、氧化 镧、镧铝氧化物、氧化锆、锆硅氧化物、氧化钽、氧化钛、钡锶钛氧化物、 钡钛氧化物、锶钛氧化物、氧化钇、氧化铝、铅钪钽氧化物和铌酸锌铅(leadzinc niobate)。

87.在一些实施例中,栅极结构202包括一个或多个功函数层(栅极电极 202b),以及该一个或多个功函数层上的填充金属,其中填充金属(图示中 未示出)填充相应的相邻线的栅极电极之间的空间。在一些这样的实施例 中,栅极结构202包括在栅极电极202b上方延伸的附加导电材料的层。

88.图2c是线部分104a或104b的截面图示。在说明性实施例中,线部 分104c(虚线)的轮廓示出了线部分104c和104a、104b的相对宽度。 如所示,线部分104a或104b比线部分104c横向宽(沿y方向)。在一个 实施例中,线部分104a和104b具有宽度wa,线部分104c具有宽度wc, 其中wa大于wc。在实施例中,wa比wc大至少5nm。

89.图2d是穿过图2a中的结构的线c-c'的截面图示。在说明性实施例中, 线部分104c在yz平面中具有矩形截面并且沟道108在线部分104c的至少 3个表面上。如所示,沟道108与表面104g、以及线部分104c的侧壁104h 和104j相邻。这种沟道108可以称为鞍形沟道108。如所示,栅极电介质 层202a和栅极电极202b与侧壁104h和104j以及表面104g共形。在一 些这样的实施例中,层级选择晶体管200被称为鞍型fet。

90.图3a是根据本公开的实施例的层级选择晶体管300的等距图示。如所 示,线结构102中的每条线沿纵向长度(x轴)具有变化的材料成分。在说 明性实施例中,线结构102的每条线还在yz平面中具有在晶体管沟道302 内和远离晶体管沟道302的区域中沿x轴变化的截面面积。晶体管沟道302 和栅极结构304的部分被切除以显示代表性线结构(诸如线104)和晶体管 沟道302的形状。为了清楚起见,图中未示出栅极电介质层。在说明性实 施例中,晶体管沟道302围绕线部分104c、104d(不可见)和104e。在 说明性实施例中,沟道302不对称地围绕线104。在实施例中,栅极结构 304具有栅极结构202的一个或多个特征。如所示,栅极结构302耦合线结 构102的每条线中的每个晶体管沟道。

91.图3b是穿过图3a的结构中的线a-a'的层级选择晶体管300的截面图 示。在说明性实施例中,线104具有上文结合图2b描述的一个或多个特征。

92.在说明性实施例中,晶体管沟道302沿x轴横向延伸超过线部分104c, 并在线部分104d和104e之上延伸。晶体管沟道302具有厚度tc。在说明 性实施例中,晶体管沟道302具有基本上等于线部分104a和线部分104c、 104d或104e的相应高度之间的差的厚度tc。在其它实施例中,tc大于或 小于线部分104a和线部分104c、104d或104e的相应高度之间的差。然 而,如所示,沟道302具有在线部分104a的最低表面104f下方的最低表 面302a。如所示,栅极结构304的栅极电介质层304a和栅极电极304b 也在最低表面104f下方。

93.在实施例中,栅极电介质层304a和栅极电极304b包括分别与栅极电 介质层204a和栅极电极204b的材料相同或基本上相同的材料,如结合图 2b所描述的。在实施例中,晶体管沟道302包括与沟道108的材料相同或 基本上相同的材料。

94.在一些实施例中,栅极结构304包括一个或多个功函数层(栅极电极 304b),以及该一个或多个功函数层上的填充金属,其中填充金属(图示中 未示出)填充相应的相邻线的栅极电极之间的空间。在一些这样的实施例 中,栅极结构304包括在栅极电极304b上方延伸的附加导电材料层。附加 导电材料的层也可以在栅极电极304b的在表面104f之下的

部分下方延伸。

95.图3c是穿过图3a中的结构的线b-b'的截面图示。在说明性实施例中, 线部分104c在yz平面中具有矩形截面并且晶体管沟道302包覆线部分 104c。如所示,栅极电介质层304a包覆线部分104c和沟道302,并且栅 极电极304b包覆栅极电介质层304a。在一些这样的实施例中,层级选择 晶体管300被称为全环绕栅fet。取决于应用,层级选择晶体管300可以 是p-fet或n-fet。

96.在第三实施例中,层级选择晶体管包括鳍式fet架构(非平面晶体管 的示例)。图4a是根据本公开的实施例的层级选择晶体管400的等距图示。 栅极结构402的部分被切除以显示代表性晶体管沟道(诸如晶体管沟道404) 的形状。为了清楚起见,图中未示出栅极电介质层。栅极结构402与线结 构102的每条线相邻。

97.图4b是穿过图4a的结构中的线a-a'的层级选择晶体管400的截面图 示。在说明性实施例中,线104具有第一和第二部分104a和104b。如所 示,线104还包括线部分104a和104b之间的层级选择晶体管沟道404。 在说明性实施例中,线部分104a是源极或漏极区域之一并且线部分104b 是层级选择晶体管400的源极或漏极区域中的另一个。晶体管沟道404具 有长度lo,如所示。在实施例中,lo在50nm和600nm之间

98.如所示,线部分104a和104b具有高度h1。在实施例中,h1在15nm 和100nm之间。晶体管沟道404具有高度h2。如所示,h2大于h1。在实 施例中,h2在10nm和95nm之间。在示例性实施例中,h2沿x轴基本上 均匀。取决于期望的鳍高度,h2可以小于h1。

99.如所示,栅极结构402在截面图示中在沟道404上。取决于制造工艺, 栅极结构402具有小于或等于晶体管沟道404的长度lo的栅极长度lg。当 lg小于lo时,栅极电介质层402a可以与栅极电极402b的侧壁相邻。应 当理解,存储器单元122与层级选择晶体管400的线部分104b耦合并且端 子互连155与层级选择晶体管400的线部分104a耦合。

100.在实施例中,栅极电介质层402a和栅极电极402b包括分别与栅极电 介质层204a和栅极电极204b的材料相同或基本上相同的材料。在实施例 中,晶体管沟道404包括与沟道108的材料相同或基本上相同的材料。

101.在一些实施例中,栅极结构402包括一个或多个功函数层(栅极电极 402b),以及该一个或多个功函数层上的填充金属,其中填充金属(图中未 示出)填充相应的相邻线的栅极电极之间的空间。在一些这样的实施例中, 栅极结构402包括在栅极电极402b上方延伸的附加导电材料的层。

102.图4c是穿过图4a中的结构的线b-b'的截面图示。在说明性实施例中, 晶体管沟道404在yz平面上具有矩形截面。如所示,晶体管沟道404在yz 平面中具有矩形截面。在说明性实施例中,栅极电介质层402a在晶体管沟 道404的顶表面404a上以及侧壁表面404b和404c上。栅极电极402b在 与表面404a、404b和404c相邻的栅极电介质层402a上。在一些这样的 实施例中,层级选择晶体管300被称为鳍式fet(非平面晶体管的示例)。 取决于应用,层级选择晶体管400可以是p-fet或n-fet。

103.图4d是穿过图4a中的结构的线b-b'的截面图示。在说明性实施例中, 晶体管沟道404的轮廓(虚线)示出了线104和沟道404的相对宽度。如 所示,线部分104a和104b比晶体管沟道404在横向上更宽(沿y方向)。 如所示,线部分104a和104b具有宽度wa,并且线部分104c具有宽度 wc。在说明性实施例中,wa大于wc。在实施例中,wa比wc大至少5nm。

104.再次参考图1,存储器设备结构100还包括一组端子互连,其耦合沿相 同方向对准的跨两个或更多个层级的线。在说明性实施例中,每个端子互 连组154和158包括多个端子互连。在说明性实施例中,端子互连组154 中的每个端子互连耦合在线结构102中的单条线和线结构132中的对应的 垂直对准的线之间。例如,线104和134通过端子互连155耦合,线106 和136通过端子互连156耦合。在操作期间,任何单个端子互连,诸如端 子互连155,可以同时将两个不同层级上的两条线104和134偏置到相同电 位。然而,通过对层级选择晶体管101a施加偏压,可以相对于存储器单元 152(在存储器单元122下方)优选地对诸如存储器单元122的单个存储器 单元进行编程。

105.在说明性实施例中,每个晶体管沟道在端子互连和存储器单元之间。 例如,沟道108在横向上在存储器单元122和端子互连155之间,并且晶 体管沟道138在横向上在存储器单元152和端子互连155之间。类似地, 晶体管沟道110在横向上在存储器单元124和端子互连156之间,并且晶 体管沟道140在横向上在存储器单元153和端子互连156之间。

106.也如所示,端子互连组158中的每个端子互连耦合在层级128的线结 构112中的单条线与层级130的线结构142内的对应的垂直对准的线之间。 在说明性实施例中,线114和144通过端子互连160耦合,并且线116和 146通过端子互连162耦合。在操作期间,端子互连160可以同时将两个不 同层级上的两条线114和144偏置到相同电位。

107.在说明性实施例中,晶体管沟道118在横向上在存储器单元122和端 子互连160之间,并且晶体管沟道120在横向上在存储器单元124和端子 互连162之间。类似地,晶体管沟道148在横向上在存储器单元152和端 子互连160之间,并且晶体管沟道150在横向上在存储器单元164和端子 互连162之间。

108.在实施例中,线结构102、112、132和142中的每个线结构中的线包 括诸如钨、钽或钛的金属或包括钨、钽或钛中的至少一种和氮的合金。

109.在实施例中,晶体管沟道110、118、120、138、140、148和150均包 括适合用于薄膜晶体管的多晶或非晶材料。

110.在一些实施例中,沟道110、118、120、138、140、148和150等包括 n型半导体材料。n型半导体材料的示例包括in、ga、zn、mg、al、sn、 hf、o、w中的两种或更多种,诸如in2o3、ga2o3、zno、ingazno、inzno、 ingao、gazno、inalo、insno、inmgo、inwo、gaznmgo、gaznsno、 gaalzno、gaalsno、hfzno、hfinzno、hfalgazno或inmgzno。

111.在实施例中,n型沟道可以掺杂有ti、w、cu、mn、mg、fe、hf、 al、ni、co或ru。在实施例中,掺杂剂浓度在10

16

个原子/cm3和10

20

个 原子/cm3之间,并且其中沟道包括在1nm到80nm之间的厚度。

112.在其他实施例中,沟道110、118、120、138、140、148和150等包括 p型材料。p型半导体材料的示例包括nbo、nio、coo、sno、cu2o、agalo、 cualo3、alscoc、sr3bpo3、la2sio4se、lacuse、rb2sn2o3、la2o2s2、 k2sn2o3、na2feose2、znrh2o4或cuo

x

,其中x是1或2。

113.在实施例中,互连155、156、160、162中的每个互连包括铜、钨、钽、 钛、铪、锆、铝、银、锡、铅、钌、钼、钴及他们的合金,或包括铜、钨、 钽、钛、铪、锆、铝、银、钛、锡或铅中的一种或多种和氮的合金。在一 些实施例中,互连155、156、160、162中的每个互连包括金属碳化物,诸 如碳化铪、碳化锆、碳化钛、碳化钽或碳化铝。

114.在说明性实施例中,存储器设备结构100还包括对应于层级128和层 级130之间的

附加层级的附加存储器单元。

115.图5a是穿过图1中的结构的线a-a'的截面图示并且示出了层级500 内的附加存储器单元的布置。层级500包括线结构102和142,以及存储器 单元阵列502。在截面图示中示出了两个存储器单元,诸如线104和线144 之间的存储器单元504,以及线106和线144之间的存储器单元506。线结 构102和142中的每个线结构中的相应的线之间的交叉处的其他存储器单 元在截面图示中不可见。

116.在实施例中,对应于每个层级的相关联的晶体管都可以是p-fet或 n-fet。在一些实施例中,在存储器设备结构100中实现了p-fet或n-fet 两者的情况下,n-fet和p-fet晶体管在交替的线结构上。例如,对应于 沟道104和106的层级选择晶体管可以是p-fet或n-fet,对应于沟道118 和120的层级选择晶体管可以是n-fet或p-fet,对应于沟道148和150 的层级选择晶体管可以是p-fet或n-fet,并且对应于沟道138和140的 层级选择晶体管可以是n-fet或p-fet。

117.应当理解的是,在一些实施例中,给定的层级内的所有存储器单元具 有相同的结构,即,非易失性存储器元件在选择器设备上,或反之亦然。

118.在实施例中,存储器单元122具有如图5b中所示的结构,其中选择器 元件508在非易失性存储器元件510上方。在其他实施例中,选择器元件 508在非易失性存储器元件510下方。非易失性存储器元件510可以包括相 变存储器、电阻式随机存取存储器(r-ram)、双向阈值开关(ots)存储 器或导电桥ram。

119.同样如所示,存储器单元122、124、504以及106、152和153中的每 个存储器单元都具有高度h

mc

。在实施例中,h

mc

取决于相应选择器元件 508和非易失性存储器元件510中的每个的厚度和结构。

120.图5c示出了示例非易失性存储器元件502的截面视图,该非易失性存 储器元件502包括电阻式随机存取存储器(rram)设备,该设备包括氧 空位开关。在所示实施例中,rram材料堆叠体包括底部电极512、底部 电极512之上的开关层514、开关层514之上的氧交换层516和氧交换层 516上的顶部电极518。

121.在实施例中,底部电极512包括非晶层。在实施例中,底部电极512 是形貌上平滑的电极。在实施例中,底部电极512包括诸如w、ta、tan 或tin的材料。在实施例中,底部电极512由与ta层交错的ru层组成。 在实施例中,底部电极512具有在20nm和50nm之间的厚度。在实施例中, 顶部电极518包括诸如w、ta、tan或tin的材料。在实施例中,顶部电 极518具有在120和70nm之间的厚度。在实施例中,底部电极512和顶部 电极518是相同的金属,诸如ta或tin。

122.开关层514可以是金属氧化物,例如,包括氧和一种或多种金属的原 子,诸如但不限于hf、zr、ti、ta或w。在钛或铪或具有氧化态 4的钽的 情况下,开关层514具有化学成分mo

x

,其中o是氧并且x是或基本上接 近2。在具有氧化态 5的钽的情况下,开关层514具有化学成分m2o

x

,其 中o是氧并且x是或基本上接近5。在实施例中,开关层514具有在1nm 和5nm之间的厚度。

123.氧交换层516用作氧空位的源或用作用于o

2-的收集器(sink)。在实施 例中,氧交换层516由金属组成,金属诸如是但不限于铪、钽或钛。在实 施例中,氧交换层516具有在5nm和20nm之间的厚度。在实施例中,氧 交换层516的厚度至少是开关层514的厚度的两倍。

在另一个实施例中, 氧交换层516的厚度至少是开关层514的厚度的两倍。在实施例中,rram 设备的单独层的组合总厚度在60nm和100nm之间,并且宽度在10nm和 50nm之间。

124.虽然图5c中示出了氧空位开关设备,但rram设备可包括其他示例, 诸如相变设备。

125.图5d是其中rram设备包括相变层的存储器元件的结构的截面图示。 在说明性实施例中,非易失性存储器元件510包括电极层512和518以及 电极层512和518之间的绝缘体层517。

126.在一些这样的实施例中,绝缘体层517表现出电荷载流子隧穿行为。 在一些这样的实施例中,绝缘体层517包括氧和金属,诸如但不限于铝、 铪、钽和钛。在另外的实施例中,绝缘体层517还掺杂有一种或多种金属 的原子,诸如是但不限于铜、银或金。在一些这样的实施例中,绝缘体层 517被以诸如铜、银或金的一种或多种金属的原子掺杂至2%-10%(原子) 之间的浓度。在实施例中,绝缘体层517具有在2nm至5nm之间的厚度。

127.在另一个实施例中,绝缘体层517包括阈值开关材料,诸如相变材料。

128.在一些示例中,绝缘体层517可以包括呈现至少两种不同电状态的相变材 料,该两种不同电状态的特征在于两种不同的电阻、导电状态和电阻状态。

129.在一些示例中,相变材料呈现至少两种不同的材料状态,对应于两种不同 电阻状态的非晶态和结晶态。在实施例中,处于完全结晶相的相变材料是 导电的,而当相变材料处于非晶态时,相变材料是电阻的。然而,通过在 给定体积的相变材料中调节结晶相和非晶相的相对程度,可以调节相变材 料的电阻。在实施例中,可以通过例如在电极512和518之间施加电压偏 置以引起焦耳加热来以具体方式加热和冷却相变材料而设定相变材料的电 阻状态。

130.在实施例中,相变材料包括ge和te。在实施例中,相变材料还包括 sb。在实施例中,相变材料包括ge、te和sb的三元合金,诸如ge2sb2te5。 在实施例中,相变材料包括二元合金、三元合金或四元合金,这些合金包 括vi族周期表中的至少一种元素,诸如te、se或s。在实施例中,相变材 料包括二元合金、三元合金或四元合金,这些合金包括te、se或s中的至 少一种,其中所述合金还包括来自v族周期表的一种元素,诸如sb。在实 施例中,相变材料包括诸如银、铟、镓、氮、硅或锗的掺杂剂。在实施例 中,掺杂剂浓度在相变材料的总成分的5%和20%之间。在实施例中,绝 缘体层517具有在2nm和15nm之间的厚度(沿例如x轴测量的)。

131.图5e是根据本公开的实施例的选择器元件508的结构的截面图示。如 所示,选择器设备包括金属-绝缘体-金属(mim)堆叠体。选择器元件510 的mim堆叠体包括选择器电极520、选择器电极520和选择器电极524之 间的绝缘体层522。

132.在实施例中,绝缘体层522包括双向阈值开关材料。在实施例中,绝 缘体包括ge、as和se的合金,诸如geasse、gese或asse。在实施例中, 合金ge、as和se可以包括掺杂剂,例如掺杂as的gese、掺杂ge的asse 或掺杂in、te或sb的geasse。在实施例中,绝缘体层522具有取决于材 料的厚度,其中厚度在5nm和20nm之间。电极520和524可以包括与电 极512和518的材料相同或基本上相同的材料。

133.在另一个实施例中,绝缘体层522包括可以经历绝缘体到金属的可逆 转变的材料。在实施例中,转变由热过程或由电过程触发。在一些这样的 实施例中,绝缘体层522包

括氧和一种或多种金属的原子,金属诸如是但 不限于铌、钒和钽。在一些具体示例中,绝缘体层522包括钒(iv)氧化 物vo2和钒(v)氧化物v2o5和铌(v)氧化物nb2o5。在一具体示例中, 绝缘体层522包括铌(v)氧化物nb2o5并且可能呈现丝状导电。在实施例 中,绝缘体层522是非晶的。在实施例中,可以经历绝缘体到金属转变的 绝缘体层522具有在5nm和20nm之间的厚度。

134.在将发生绝缘体到金属转变的一些实施例中,绝缘体层522还包括诸 如银、铜或金的掺杂剂。在实施例中,掺杂剂浓度在绝缘体层522的总成 分的0.1-10%之间。0.1-10%之间的掺杂剂浓度可以促进丝状导电。

135.在实施例中,选择器电极520和524包括诸如tin和tan的导电材料 或诸如ta、w或pt的金属。在实施例中,选择器电极520和524具有在 5nm和20nm之间的厚度。电极520和524可以具有相同的厚度或可以不具 有相同的厚度。

136.图6是根据本公开的实施例的制造图2a-2d和3a-3c的层级选择晶体 管200或304的方法600。方法600在操作610处开始,在衬底上方的电介 质中形成多个过孔。方法600在操作620处继续,在过孔中的单独过孔上 方形成多条线。方法600在操作630处继续,进行氧化多条线中的线中的 单独线的部分以在线中的单独线内形成远离过孔的氧化区域的工艺。方法600在操作640处继续,在线中的每条线的氧化区域上形成晶体管沟道材料。 方法600在操作650处结束,在多条线中的单独线中的每条线的沟道材料 上形成栅极结构。

137.图7a是根据本公开的实施例的在衬底704之上的电介质702中形成的 端子互连阵列700的截面图示。在实施例中,通过掩模和蚀刻工艺将多个 过孔图案化到电介质702中。在形成多个过孔之后,将衬垫层以及随后的 填充金属沉积到多个过孔中并且执行平坦化工艺以形成端子互连155、156、 706和708。在实施例中,电介质702包括硅以及氧、氮或碳中的一种或多 种,并且图案化工艺包括等离子体蚀刻。在实施例中,端子互连706和708 包括与端子互连155和156的材料相同的材料。

138.图7b是在衬底704之上的电介质702中形成的端子互连阵列700的等 距图示。在实施例中,端子互连阵列700中的每个端子互连具有基本上为 矩形的平面视图剖面。在其他实施例中,平面视图剖面可以是圆形的或椭 圆形的。

139.图8a示出了在衬底704上方形成多个线段800之后的图7a的结构。 在实施例中,多条线段800中的每条线段801包括导电线802、硬掩模804、 电介质806和电介质806上的硬掩模808。

140.在实施例中,多条线段801的材料层堆叠体沉积在电介质702上和端 子互连700上。在实施例中,形成材料层堆叠体包括在导电层上沉积第一 硬掩模材料的层,在硬掩模材料的层上沉积电介质层并在电介质层上沉积 第二硬掩模材料的层。抗蚀剂掩模可以形成在第二硬掩模材料的层上并且 材料层堆叠体被图案化。在实施例中,图案化工艺包括等离子体蚀刻工艺。 材料层堆叠体中的单独层被图案化以形成多条线段800。第二硬掩模材料的 层被图案化以形成硬掩模808,电介质层被图案化以形成电介质806,第一 硬掩模材料的层被图案化以形成硬掩模804,并且导电层被图案化以形成导 电线802。如所示,在图案化工艺期间也使电介质702的部分凹陷。应当理 解,在图案化工艺期间没有暴露端子互连700。在说明性实施例中,示出了 四个线段801。四个线段801的形成在每个线段801之间产生开口809。线 段800中的线的数量等于存储器阵列中的字线或位线的数量。

141.在实施例中,硬掩模804和808包括氧、氮或碳中的一种或多种和硅。 在实施例中,电介质806包括氧、氮或碳中的一种或多种和硅。在示例性 实施例中,电介质806包括氧或碳中的一种或多种和硅。在实施例中,导 电线802包括线104的材料。

142.图8b是图8a中结构的等距图示。

143.图9示出了在每个开口809中形成电介质810以形成块900之后的图 8b的结构。在实施例中,电介质810被沉积在开口809中。沉积工艺可以 包括pecvd(等离子体增强化学气相沉积)、物理气相沉积(pvd)、化学 气相沉积(cvd)工艺。在实施例中,电介质包括硅和氮和/或碳。在实施 例中,电介质810被平坦化。在实施例中,使用化学机械抛光(cmp)工 艺来平坦化电介质810,电介质810形成与硬掩模808的最上表面808a基 本上共面的最上表面810a。

144.图10a示出了在蚀刻块900的部分的工艺之后的图9的结构。在实施 例中,利用等离子体蚀刻工艺来蚀刻电介质810和每个线段801的部分以 形成块900的区段1000a和区段1000b。区段1000a和1000b之间的区域 1002暴露线结构802。

145.在实施例中,等离子体蚀刻工艺蚀刻硬掩模808、电介质806和硬掩模 804,并暴露与导电线802相邻的电介质702的最上表面。利用随后的蚀刻 工艺使导电线802的上部部分和侧面部分凹陷。在实施例中,利用湿法化 学和等离子体蚀刻工艺的组合来形成横向和垂直凹槽。

146.在蚀刻工艺之后,对暴露的区域1002进行部分掩模并且执行氧化工艺。 在实施例中,牺牲掩模包括不被等离子体氧化或湿化学工艺侵蚀的材料。 掩模的轮廓由虚线1004限定。掩模在区域1002的部分之上产生开口。在 实施例中,利用等离子体氧化或湿化学工艺来氧化区域1002中的导电线802 的部分。氧化工艺在导电的线部分802b和802c之间形成氧化线部分802a。 在氧化工艺之后,去除牺牲掩模。线部分802a的长度(沿x轴)取决于要 形成的晶体管的期望的栅极长度。在实施例中,当导电线802包括诸如w、 ta、ti或ru的纯金属或诸如wn、tin或tin的金属的合金时,线部分802a 被充分氧化成不导电的。

147.图10b是沿图10a中的结构的线a-a'截取的截面图示。示出了线部分 802a的截面。导电线802的未蚀刻部分的截面(由虚线表示)被叠加以示 出导电线802和线部分802a之间的相对尺寸。如所示,线部分802a具有 在横向上从宽度wa减小到蚀刻工艺之后的较小的宽度wc的宽度。宽度 wc对应于导电线802的未蚀刻部分的宽度。线部分802a的高度从h1减小 到h2。高度的减小可以在5nm和20nm之间。

148.图11a示出了在每条导电线802的在区域1002中的线部分802a、802b 和802c之上形成薄膜沟道材料(本文中沟道材料)1100之后的图10a的 结构。在实施例中,在图10a的结构上形成了掩模(图中未示出)。可以利 用pvd、pevcd或cvd沉积工艺来沉积沟道材料1100。在实施例中,沟 道材料1100包括与沟道108的材料相同或基本上相同的材料。在实施例中, 沟道材料1100沉积在被掩模暴露的线部分802a、802b和802c的所有表 面上。沟道材料1100也沉积在电介质702的暴露的表面上。在实施例中, 将沟道材料1100沉积到在5nm和20nm之间的厚度。

149.图11b是沿图11a中的结构的线a-a'(穿过线部分802a的切片)截 取的截面图示。在说明性实施例中,沟道材料1100共形地沉积在线部分 802a的侧壁和上表面上。

150.图12a是在去除在电介质702上方且与线部分802a相邻的沟道材料 1100的部分的

工艺之后的图11b中的结构的截面图示。在实施例中,在沟 道材料1100的在线部分802a上方的部分之上图案化掩模1200(在虚线 1200内)。在实施例中,利用等离子体蚀刻工艺来蚀刻和去除沟道材料1100 的未被掩模1200覆盖的暴露的部分。等离子体蚀刻工艺形成与每个线部分 802a相邻(并且在进入图的平面上在部分802b和802c上)的沟道1202。 应当理解,隔离与每条导电线802相关联的每个沟道的工艺使的每条导电 线802能够选择性地对存储器设备结构中的存储器单元进行编程。

151.在一些实施例中,也从每个线部分802a的顶表面去除沟道材料1100, 如图12b中所示。上面结合图12a描述的用于掩模和蚀刻的工艺可以用于 在每个线部分802a的顶表面上方形成开口。如所示,等离子体蚀刻工艺形 成与线部分802a的侧壁相邻的沟道1202。

152.图13a示出了在形成栅极电介质层1300之后的图11b的结构。在实施 例中,栅极电介质层1300包括与栅极电介质层202a的材料相同或基本上 相同的材料。在实施例中,通过原子层沉积(ald)或pvd工艺将栅极电 介质层1300毯式沉积在图11b的结构上。在实施例中,栅极电介质层共形 地沉积在沟道1202(图示中隐藏)上、电介质702上、线部分802b和802c (图示中隐藏)上以及每个线段801的在区段1002中暴露的侧壁上。栅极 电介质层1300也沉积在区段1000a和区段1000b上,如所示。

153.图13b是沿图13a中的结构的线a-a'截取的截面图示。如所示,栅极 电介质层1300共形地沉积在沟道1202周围。

154.图14a示出了在形成栅极电极1400之后的图13a的结构。在实施例 中,将栅极电极1400的材料毯式沉积在栅极电介质层1300上。

155.在实施例中,对栅极电极1400的材料进行平坦化。平坦化工艺可以包 括例如化学机械抛光(cmp)工艺。在说明性实施例中,cmp工艺去除区 域1000a和1000b中的栅极电极1400和栅极电介质层1300的材料,并在 区域1002中形成栅极电极1400。在实施例中,形成栅极电极1400的工艺 完成了形成薄膜晶体管1402的工艺,薄膜晶体管1402具有结合图2a-2d 讨论的一种或多种特性。平坦化工艺对硬掩模808具有足够的选择性。如 所示,cmp工艺不从每个线段801上方去除硬掩模808。硬掩模808还用 作制造工艺期间的抛光停止部。

156.图14b是沿图14a中的结构的线a-a'截取的截面图示。在说明性实施 例中,栅极电极1400连续地延伸跨越包覆每个线部分802a的每个沟道1202。 应当理解,如果需要,在操作期间,栅极电极1400可以激活每个线部分802a 上方的每个沟道1202。

157.再次参考图14a,在实施例中,在随后的操作中,在从每个导电线802 上方去除硬掩模808、电介质806和硬掩模804之后,可以在每个线结构上 方沉积用于制造存储器单元的材料。在一些实施例中,可以将电介质毯式 沉积在图14a的结构上,并且可以形成过孔开口以制造rram设备。

158.在其他示例中,可以通过对结合图7a-14b描述的工艺流程的修改来制 造晶体管306。在一个实施例中,图15a示出了图9的结构,其中利用ald 沉积工艺在线部分802a(图中隐藏)以及线结构部分802b和802c的未被 掩模覆盖的部分周围选择性地沉积薄膜晶体管沟道材料(沟道材料)1500。 在一些这样的实施例中,沉积工艺利用可以顺利地在氧化的金属材料上成 核的前体。

159.图15b是沿线a-a'截取的图15a中的结构的截面图。如所示,将tft 沟道材料1500沉积为完全包覆线部分802a以形成分立沟道1500。形成栅 极电极的方法与结合图10a-14b

描述的一种或多种工艺操作基本上相同。

160.在其他示例中,可以通过对结合图7a-14b描述的工艺流程的修改来制 造晶体管,例如结合图4a描述的晶体管400。图16a示出了在区域1002 中形成多个开口1600之后的图9的结构。在说明性实施例中,通过完全蚀 刻出线段801来形成多个开口1600。

161.图16b示出了,在多个开口1600中的每个开口中,在每个开口中在电 介质702上形成牺牲电介质1604之后在电介质1604上形成沟道层1606之 后的图16a的结构。为清楚起见,示出了区域1002的部分1602。在实施 例中,通过ald工艺沉积电介质。在实施例中,沟道层1606沉积或生长 在沟道层1606上。在实施例中,沟道层1606包括与沟道层404的材料相 同或基本上相同的材料。在实施例中,电介质1604包括与电介质702的材 料相同或基本上相同的材料。在实施例中,可控制开口1600的横向厚度(沿 y轴)和电介质1604的沉积厚度以获得沟道层1606的期望的横向厚度(y 轴)。

162.图16c示出了在减小沟道层1606的高度的工艺之后的图16d的结构。 在实施例中,通过等离子体蚀刻工艺、湿化学蚀刻工艺或其组合使电介质 1604和沟道层1606凹陷。如所示,使电介质1604和沟道层1606相对于沟 道层1606的最上表面1606a凹陷厚度t1。可以在使电介质凹陷之前使沟 道层1606垂直凹陷以防止沟道层1606的横向厚度减小。可以使沟道层1606 凹陷到要形成的鳍结构的期望的高度hf。如所示,沟道层1606的顶表面 1606b基本上是平面的。在一些实施例中,存在沟道层1606的顶部边缘部 分的圆化。

163.可以在对区域1602的部分1602a和区域1000a进行掩模之后执行选 择性地使电介质1604和沟道层1606凹陷的工艺。在说明性实施例中,在 使电介质1604和沟道层1606凹陷之后去除区域1602中的电介质810的暴 露的部分。

164.在实施例中,在在下一操作形成栅极结构之前去除电介质1604a的暴 露的侧壁。

165.图16d示出了在去除电介质1604b(在图16c示出的)的暴露的侧壁 之后形成栅极电介质层1610之后的图16c的结构。栅极电介质层1610包 括与栅极电介质层202a的材料相同或基本上相同的材料。在说明性实施例 中,栅极电介质层共形地沉积在沟道层1606周围、电介质702上并与沟道 1606之下的电介质1604的部分相邻。栅极电介质层1610也沉积在硬掩模 808(图中隐藏)和电介质810的上表面上、沟道层1606a的最上表面上和 相邻的电介质1604上。在实施例中,栅极电介质层1610通过ald工艺沉 积至1nm和10nm之间的厚度。

166.图16e示出了在栅极电介质层1610上形成栅极电极1612之后的图16d 的结构。在实施例中,形成栅极电极1612的工艺与用于形成栅极电极1400 的工艺相同或基本上相同。在实施例中,在栅极电介质层1610上毯式沉积 栅极电极1612的材料并执行平坦化。在说明性实施例中,平坦化工艺隔离 栅极电极1612但不去除栅极电介质层1610。

167.图16f示出了在去除栅极电介质层1610的部分的工艺之后的图16e的 结构。在实施例中,从电介质层810、硬掩模808上方、从区域1602a中 的电介质层1604和沟道层1606的部分上方去除栅极电介质层。在说明性 实施例中,在去除区域1602a中的栅极电介质层1610之后蚀刻并去除区域 1602a中的电介质1604和沟道层1606。开口1614形成在与区域1602b相 邻的区域1602a中。

168.图16g示出了在形成与区域1602b中的每个沟道1606相邻的源极结构 1616之后的图16f的结构。在实施例中,源极结构1616包括诸如线802 的材料的材料以防止在线802和

1812经由与处理器1810集成的前端电路耦合到处理器1810。在一个示例 中,一个或多个传感器1812经由系统1800的另一部件耦合到处理器1810。

175.在一个示例中,系统1800包括音频子系统1820,其代表与向计算设备 提供音频功能相关联的硬件(例如,音频硬件和音频电路)和软件(例如, 驱动程序、编解码器)部件。音频功能可以包括扬声器或头戴式受话器输 出,以及麦克风输入。用于此类功能的设备可集成到系统1800中,或连接 到系统1800。在一个示例中,用户通过提供由处理器1810接收和处理的音 频命令来与系统1800交互。

176.显示子系统1830代表提供用于呈现给用户的视觉显示的硬件(例如, 显示设备)和软件部件(例如,驱动程序)。在一个示例中,显示器包括用 于用户与计算设备交互的触觉部件或触摸屏元件。显示子系统1830包括显 示接口1832,其包括用于向用户提供显示的特定屏幕或硬件设备。在一个 示例中,显示接口1832包括与处理器1810(诸如图形处理器)分离的逻辑 设备以执行与显示相关的至少一些处理。在一个示例中,显示子系统1830 包括向用户提供输出和输入的触摸屏设备。在一个示例中,显示子系统1830 包括向用户提供输出的高清(hd)或超高清(uhd)显示器。在一个示例 中,显示子系统包括或驱动触摸屏显示器。在一个示例中,显示子系统1830 基于存储在存储器中的数据或基于由处理器1810运行的操作或两者来生成 显示信息。

177.i/o控制器1840代表与和用户交互相关的硬件设备和软件部件。i/o控 制器1840可以操作以管理作为音频子系统1820或显示子系统1830或两者 的部分的硬件。此外,i/o控制器1840示出了用于连接到系统1800的附加 设备的连接点,用户可以通过该附加设备与系统交互。例如,可以附接到 系统1800的设备可以包括麦克风设备、扬声器或立体声系统、视频系统或 其他显示设备、键盘或小键盘设备、或与具体应用一起使用的其他i/o设备 (诸如读卡器或其他设备)。

178.如上所述,i/o控制器1840可以与音频子系统1820或显示子系统1830 或两者交互。例如,通过麦克风或其他音频设备的输入可以为系统1800的 一个或多个应用或功能提供输入或命令。另外,可以提供音频输出来代替 显示输出,或除了显示输出之外,提供音频输出。在另一示例中,如果显 示子系统包括触摸屏,则显示设备还充当输入设备,其可以至少部分地由 i/o控制器1840管理。系统1800上还可以存在附加按钮或开关以提供由i/o 控制器1840管理的i/o功能。

179.在一个示例中,i/o控制器1840管理诸如加速度计、相机、光传感器 或其他环境传感器、陀螺仪、全球定位系统(gps)或可以包括在系统1800 中的其他硬件的设备、或传感器1812。输入可以是直接用户交互的部分, 也可以为系统提供环境输入以影响其操作(诸如过滤噪声、调整显示以进 行亮度检测、为相机应用闪光或其他特征)。

180.在一个示例中,系统1800包括管理电池电力使用、电池的充电以及与 省电操作相关的特征的电力管理部1850。电力管理部1850管理来自电源 1852的电力,电源1852向系统1800的部件提供电力。在一个示例中,电 源1852包括ac到dc(交流到直流)适配器以插入壁式插座中。这种ac 电力可以是可再生能量(例如,太阳能、基于运动的电力)。在一个示例中, 电源1852仅包括dc电力,其可以由dc电源提供,dc电源是诸如外部 ac到dc转换器。在一个示例中,电源1852包括通过靠近充电场而进行 充电的无线充电硬件。在一个示例中,电源1852可以包括内部电池或燃料 电池源。

181.存储器子系统1860包括用于在系统1800中存储信息的单个或多个存 储器设备1862。存储器子系统1860可以包括非易失性(到存储器设备的电 力中断时状态不改变)或易失性(到存储器设备的电力中断时状态不确定) 存储器设备、或组合。存储器子系统1860可以存储应用数据、用户数据、 音乐、照片、文档或其他数据,以及与系统1800的应用和功能的运行相关 的系统数据(无论是长期的还是临时的)。在一个示例中,存储器子系统1860 包括存储器控制器1864(其也可以被认为是系统1800的控制的部分,并且 可能潜在地被认为是处理器1810的部分)。存储器控制器1864包括调度器 以生成和发出命令以控制对存储器设备1862的访问。

182.连接性1870包括硬件设备(例如,无线或有线连接器和通信硬件,或 有线和无线硬件的组合)和软件部件(例如,驱动程序、协议栈)以使得 系统1800能够与外部设备通信。外部设备可以是独立的设备(诸如其他计 算设备、无线接入点或基站),以及外围设备(诸如耳机、打印机或其他设 备)。在一个示例中,系统1800与外部设备交换数据以存储在存储器中或 显示在显示设备上。交换的数据可以包括要存储在存储器中的数据,或者 已经存储在存储器中的数据,以读取、写入或编辑数据。

183.连接性1870可以包括多种不同类型的连接性。概括地说,系统1800 被示为具有蜂窝连接性1872和无线连接性1874。蜂窝连接性1872通常是 指由无线运营商提供的蜂窝网络连接性,诸如通过gsm(全球移动通信系 统)或变体或派生、cdma(码分多址)或变体或派生、tdm(时分复用) 或变体或派生、lte(长期演进——也称为“4g”)或其他蜂窝服务标准提供 的。无线连接性1874是指非蜂窝的无线连接性,并且可以包括个域网(诸 如蓝牙)、局域网(诸如wifi)或广域网(诸如wimax),或其他无线通信, 或组合。无线通信是指通过经非固态介质的调制电磁辐射的使用来传输数 据。有线通信通过固态通信介质进行。

184.外围连接1880包括硬件接口和连接器,以及进行外围连接的软件部件 (例如,驱动程序、协议栈)。应当理解,系统1800既可以是至其他计算 设备的外围设备(“至”1882),也可以具有连接到它的外围设备(“从”1884)。 系统1800通常具有“对接(docking)”连接器以连接到其他计算设备以用于 诸如管理(例如,下载、上传、改变、同步)系统1800上的内容的目的。 另外,对接连接器可以允许系统1800连接到允许系统1800控制内容输出 到例如视听或其他系统的某些外围设备。

185.除了专有对接连接器或其他专有连接硬件之外,系统1800还可以通过 通用或基于标准的连接器进行外围连接1880。常见类型可包括通用串行总 线(usb)连接器(其可包括多种不同硬件接口中的任何硬件接口)、包括 迷你显示端口(mini displayport,mdp)的显示端口(displayport)、高清 多媒体接口(hdmi)或其他类型。

186.图19是计算系统的示例的框图,该计算系统包括存储器设备结构内的 层级选择晶体管以使得能够实现解码器晶体管覆盖区缩放。系统1900代表 根据本文任何示例的计算设备,并且可以是膝上型计算机、台式计算机、 平板计算机、服务器、游戏或娱乐控制系统、嵌入式计算设备或其他电子 设备。

187.系统1900包括在存储器1930中的存储器设备结构,诸如例如图1的 存储器设备结构100。在一个示例中,层级选择晶体管1990代表根据本文 提供的任何示例的层级选择晶体管。层级选择晶体管1990使得存储器1930 能够提供对存储器设备结构内的目标单元的选择。与传统解码器晶体管相 比,所描述的层级选择晶体管的使用使得能够以更低的能量

使用进行选择。

188.系统1900包括处理器1910,处理器1910可包括任何类型的微处理器、 中央处理单元(cpu)、图形处理单元(gpu)、处理核、或其他处理硬件、 或组合,以为系统1900提供指令的处理或运行。处理器1910控制系统1900 的整体操作,并且可以是或包括一个或多个可编程通用或专用微处理器、 数字信号处理器(dsp)、可编程控制器、专用集成电路(asic)、可编程 逻辑设备(pld),或这些设备的组合。

189.在一个示例中,系统1900包括耦合到处理器1910的接口1912,接口 1912可以代表用于需要更高带宽连接的系统部件的更高速度接口或高吞吐 量接口,系统部件是诸如存储器子系统1920或图形接口部件1940。接口 1912代表接口电路,它可以是独立的部件或集成到处理器管芯上。接口1912 可以作为电路集成到处理器管芯上或作为部件集成在片上系统上。在存在 图形接口1940的情况下,图形接口1940与图形部件进行接口连接以向系 统1900的用户提供视觉显示。图形接口1940可以是独立部件或集成到处 理器管芯上或片上系统上。在一个示例中,图形接口1940可以驱动向用户 提供输出的高清(hd)显示器。在一个示例中,显示器可以包括触摸屏显 示器。在一个示例中,图形接口1940基于存储在存储器1930中的数据或 基于处理器1910运行的操作或两者来生成显示。

190.存储器子系统1920代表系统1900的主存储器并且为要由处理器1910 运行的代码或要在运行例程中使用的数据值提供存储。存储器子系统1920 可以包括一个或多个存储器设备1930,诸如只读存储器(rom)、闪存、 一种或多种随机存取存储器(ram)(诸如dram)或其他存储器设备, 或者这些设备的组合。在一些实施例中,存储器子系统1920包括持久存储 器(pmem),持久存储器(pmem)可以提供比传统dram更高的ram 容量。pmem可以在持久模式下操作,即利用与叠层架构中的选择器集成 的非易失性设备(例如,rram、pcm、cbram等),来存储数据而无需 向存储器子系统920施加电力用于非易失性数据存储。在其他实施例中, 存储器子系统1920包括驻留在nand封装中以用于快速存储的固态驱动器 (ssd)。

191.存储器1930对操作系统(os)1932进行存储和托管等以提供用于系 统1900中的指令的运行的软件平台。另外,应用1934可以从存储器1930 在os 1932的软件平台上运行。应用1934代表程序,该程序具有他们自己 的操作逻辑来运行一项或多项功能的运行。进程1936代表向os 1932或一 个或多个应用1934或组合提供辅助功能的代理或例程。os 1932、应用1934 和进程1936提供软件逻辑来提供用于系统1900的功能。在一个示例中, 存储器子系统1920包括存储器控制器1922,其是用于生成和向存储器1930 发出命令的存储器控制器。应当理解,存储器控制器1922可以是处理器1910 的物理部分或接口1912的物理部分。例如,存储器控制器1922可以是集 成存储器控制器,集成到具有处理器1910的电路上,诸如集成到处理器管 芯或片上系统上。

192.尽管未具体示出,但应理解,系统1900可以包括一个或多个总线或设 备之间的总线系统,诸如存储器总线、图形总线、接口总线等。总线或其 他信号线可以将部件通信或电耦合在一起,或通信且电耦合该部件。总线 可以包括物理通信线路、点对点连接、桥接器、适配器、控制器或其他电 路系统或组合。总线可以包括例如以下之一或多个:系统总线、外围部件 互连(pci)总线、超传输(hypertransport)或行业标准架构(isa)总线、 小型计算机系统接口(scsi)总线、通用串行总线(usb),或其他总线, 或组合。

193.在一个示例中,系统1900包括接口1914,其可以耦合到接口1912。 接口1914可以

是比接口1912速度低的接口。在一个示例中,接口1914代 表可以包括独立部件和集成电路系统的接口电路。在一个示例中,多个用 户接口部件或外围部件或两者耦合到接口1914。网络接口1950为系统1900 提供通过一个或多个网络与远程设备(例如,服务器或其他计算设备)通 信的能力。网络接口1950可以包括以太网适配器、无线互连部件、蜂窝网 络互连部件、usb(通用串行总线)或其他基于有线或无线标准的接口或 专有接口。网络接口1950可以与远程设备交换数据,这可以包括发送存储 在存储器中的数据或接收要存储在存储器中的数据。

194.在一个示例中,系统1900包括一个或多个输入/输出(i/o)接口1960。 i/o接口1960可以包括一个或多个接口部件,用户通过该一个或多个接口 部件与系统1900交互(例如,音频、字母数字、触觉/触摸或其他接口连接)。 外围接口1970可以包括上面未具体提到的任何硬件接口。外围设备通常是 指从属地连接到系统1900的设备。从属连接是系统1900提供软件平台或 硬件平台或两者所在的连接,操作在该软件平台或硬件平台上运行并且用 户与该软件平台或硬件平台交互。

195.在一个示例中,系统1900包括以非易失性方式存储数据的存储子系统 1980。在一个示例中,在某些系统实施方式中,存储子系统1980的至少某 些部件可以与存储器子系统1920的部件重叠。存储子系统1980包括一个 或多个存储设备1984,其可以是或包括用于以非易失性方式存储大量数据 的任何常规介质,诸如一个或多个基于磁性、固态或光学的盘,或组合。 存储设备1984以持久状态保持代码或指令和数据1986(即,即使到系统 1900的电力中断,但仍保留该值)。存储设备1984通常可以被认为是“存储 器”,然而存储器1930通常是向处理器1910提供指令的运行或操作存储器。 而存储设备1984是非易失性的,存储器1930可以包括易失性存储器(即, 如果到系统1900的电力中断,则数据的值或状态是不确定的)。在一个示 例中,存储子系统1980包括与存储设备1984接口连接的控制器1982。在 一个示例中,控制器1982是接口1914或处理器1910的物理部分,或者可 以包括在处理器1910和接口1914二者中的电路或逻辑。

196.电源1902向系统1900的部件提供电力。更具体地,电源1902通常与 系统1902中的一个或多个供电部1904接口连接以向系统1900的部件提供 电力。在一个示例中,供电部1904包括ac到dc(交流到直流)适配器 以插入壁式插座中。这种ac电力可以是可再生能量(例如太阳能)电源 1902。在一个示例中,电源1902包括dc电源,诸如外部ac到dc转换 器。在一个示例中,电源1902或供电部1904包括无线充电硬件,以通过 靠近充电场进行充电。在一个示例中,电源1902可以包括内部电池或燃料 电池电源。

197.因此,本公开的一个或多个实施例总体上涉及用于3d交叉点存储器的 层级选择晶体管和制造方法。

198.在第一示例中,一种存储器设备结构包括第一多个线结构,其中,所 述第一多个线结构中的单独线结构各自包括第一晶体管沟道。所述存储器 设备结构还包括:与所述第一多个线结构基本上正交的第二多个线结构, 其中,所述第二多个线结构中的单独线结构各自包括第二晶体管沟道;以 及在所述第一多个线结构和所述第二多个线结构之间的每个交叉点处的存 储器单元。

199.在第二示例中,对于第一示例中的任何示例,第一层级包括所述第一 多个线结构和所述第二多个线结构。所述存储器设备结构还包括在所述第 一层级上方或下方的第二

层级,其中,所述第二层级包括基本上平行于所 述第一多个线结构的第三多个线结构,其中,所述第三多个线结构中的单 独线结构各自包括第三晶体管沟道。所述存储器设备结构还包括基本上平 行于所述第二多个线结构的第四多个线结构,其中,所述第四多个线结构 中的单独线结构各自包括第四晶体管沟道。存储器单元在所述第三多个线 结构和所述第四多个线结构之间的每个交叉点处。所述设备结构还包括在 所述第一层级和所述第二层级之间的多个端子互连,其中,所述多个端子 互连中的单独端子互连耦合在所述第一层级中的线结构中的单独线结构和 所述第二层级中的线结构中的对应的单独线结构之间,并且其中,所述晶 体管沟道中的单独晶体管沟道在所述端子互连中的单独端子互连和所述存 储器单元之间。

200.在第三示例中,对于第一至第二示例中的任何示例,所述第一多个线 结构、所述第二多个线结构、所述第三多个线结构和所述第四多个线结构 各自包括:钨、钽或钛;或其合金,其中所述合金还包括氮。

201.在第四示例中,对于第一至第三示例中的任何示例,所述第一晶体管 沟道、所述第二晶体管沟道、所述第三晶体管沟道和所述第四晶体管沟道 各自包括多晶或非晶材料。

202.在第五示例中,对于第一至第四示例中的任何示例,其中,所述多晶 或非晶材料包括in2o3、ga2o3、zno、ingazno、inzno、ingao、gazno、 inalo、insno、inmgo、gaznmgo、gaznsno、gaalzno、gaalsno、hfzno、 hfinzno、hfalgazno、inmgzno、nbo、nio、coo、sno、cu2o、agalo、 cualo3、alscoc、sr3bpo3、la2sio4se、lacuse、rb2sn2o3、la2o2s2、 k2sn2o3、na2feose2、znrh2o4或cuo

x

,其中x为1或2。

203.在第六示例中,对于第一至第五示例中的任何示例,所述第一多个线 结构、所述第二多个线结构、所述第三多个线结构和所述第四多个线结构 中的单独线结构包括:第一部分和第二部分,其中,所述第一部分和所述 第二部分中的每者包括金属。第三部分在所述第一部分和所述第二部分之 间,其中,所述第三部分包括所述金属和氧;并且

204.在第七示例中,对于第六示例中的任何示例,所述晶体管沟道包覆所 述第三部分。

205.在第八示例中,对于第一至第七示例中的任何示例,所述晶体管沟道 在所述第一部分或所述第二部分的最上表面上方和最下表面下方延伸。

206.在第九示例中,对于第一至第八示例中的任何示例,所述第一多个线 结构、所述第二多个线结构、所述第三多个线结构和所述第四多个线结构 中的单独线结构包括:各自包括金属的第一部分和第二部分;以及在所述 第一部分和所述第二部分之间的第三部分,其中,所述第三部分包括所述 晶体管沟道的材料。

207.在第十示例中,对于第一至第九示例中的任何示例,所述第三部分具 有大于所述第一部分的高度或所述第二部分的高度的高度。

208.在第十一示例中,对于第一至第十示例中的任何示例,所述第一多个 线结构、所述第二多个线结构、所述第三多个线结构和所述第四多个线结 构中的晶体管沟道中的单独晶体管通过栅极结构电并联耦合。

209.在第十二示例中,对于第一至第十一示例中的任何示例,所述存储器 设备结构还包括在所述第一多个线结构和所述第三多个线结构之间的每个 交叉点处的存储器单元。

210.在第十三示例中,对于第一至第十二示例中的任何示例,所述存储器 单元包括与

选择器元件耦合的非易失性存储器元件。

211.在第十四示例中,一种制造层级选择晶体管的方法包括在衬底上方形 成导电过孔,并且形成在所述过孔上方且与所述过孔耦合的互连线结构, 其中,所述过孔与所述线结构的第一部分耦合。所述方法还包括氧化所述 线结构的第二部分,并且在与所述线结构的所述第二部分相邻的侧壁上沉 积沟道材料。所述方法还包括在所述沟道材料上沉积栅极氧化层,并且在 所述栅极氧化层上形成栅极电极。

212.在第十五示例中,对于第十四示例中的任何示例,在氧化所述线结构 的所述第二部分之前,所述方法包括执行蚀刻工艺以减小所述线结构的横 向和垂直厚度。

213.在第十六示例中,对于第十四到第十五示例中的任何示例,氧化所述 线结构的所述第二部分包括破坏所述线结构的导电性。

214.在第十七示例中,对于第十四至第十六示例中的任何示例,形成所述 沟道包括围绕多个所述互连线结构中的线结构中的单独线结构的所述第二 部分,并且形成所述栅极电极包括围绕所述沟道。

215.在第十八示例中,对于第十四至第十七示例中的任何示例,形成所述 沟道还包括将所述沟道材料沉积在所述线结构的所述第二部分的顶表面上 和侧壁上,并从所述顶表面去除所述沟道材料的部分。

216.在第十九示例中,一种系统包括处理器,以及存储器设备结构,所述 存储器设备结构包括沿第一方向的第一多个线结构,所述第一多个线结构 包括与第二线结构相邻的第一线结构,其中,所述第一线结构包括第一晶 体管沟道,并且所述第二线结构包括第二晶体管沟道。所述存储器设备结 构还包括第二多个线结构,第二多个线结构沿与所述第一方向正交的第二 方向与所述第一多个线结构基本上正交,所述第二多个线结构包括与第四 线结构相邻的第三线结构,其中,所述第三线结构包括第三晶体管沟道, 并且第四线结构包括第四晶体管沟道。所述存储器设备结构还包括:在所 述第一多个线结构和所述第二多个线结构之间的每个交叉点处的存储器单 元;以及多个端子互连,其中,所述多个端子互连中的单独端子互连耦合 在所述线结构中的单独线结构和多个逻辑晶体管中的单独逻辑晶体管之间, 并且其中,所述晶体管沟道中的单独晶体管沟道在所述端子互连中的所述 单独端子互连和所述存储器单元之间。

217.在第二十示例中,对于第十九示例中的任何示例,所述系统还包括与 所述存储器设备结构耦合的存储器控制器。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。