1.本公开一般地芯片设计领域。更具体地,本公开涉及用于芯片设计的内存上电下电管脚重连方法和装置。

背景技术:

2.随着集成电路的发展,对于集成电路的稳定性的要求越来越高。目前,在设计芯片时,设计者只会根据功能和使用需求对芯片内存单元进行上下电连接,而并没有考虑到内存单元的物理分布位置。一个驱动通常会并行为多个内存单元进行上下电,使得在上电或者下电时会瞬间造成电源网络比较大的压降,甚至会损坏芯片中的一些组成单元,例如供电部件。因此如何获得一种能够考虑到内存单元实际的物理分布位置而减少上电下电对电源网络影响的方法成为现有技术中需要解决的问题。

技术实现要素:

3.为了至少部分地解决背景技术中提到的技术问题,本公开的方案提供了一种用于芯片设计的内存上电下电管脚重连方法和装置。

4.在一个方面中,本公开提供一种用于芯片设计的内存上电下电管脚重连方法,所述方法包括:根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组;根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组;根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接。

5.在另一方面中,本公开提供一种用于芯片设计的内存上电下电管脚重连装置,其中,所述装置包括:第一分组模块,其配置成根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组;第二分组模块,其配置成根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组;重连模块,其配置成根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接。

6.在另一方面,本公开提供一种用于芯片设计的内存上电下电管脚重连装置,其中,所述装置包括存储器和处理器,所述存储器中存储有计算机程序,所述处理器执行所述计算机程序时,实现如下步骤:

7.根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组;根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组;根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接。

8.在另一方面中,本公开提供一种计算机可读存储介质,其中,所述存储介质存储有计算机程序,所述计算机程序被执行时,实现如下步骤:

9.根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组;根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组;根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接。

10.利用本公开的用于芯片设计的内存上电下电管脚重连方法和装置,可以根据内存

单元实际的物理分布位置对内存单元的上电下电管脚进行重新连接,从而减少上电下电对电源网络的影响。

附图说明

11.通过参考附图阅读下文的详细描述,本公开示例性实施方式的上述以及其他目的、特征和优点将变得易于理解。在附图中,以示例性而非限制性的方式示出了本公开的若干实施方式,并且相同或对应的标号表示相同或对应的部分其中:

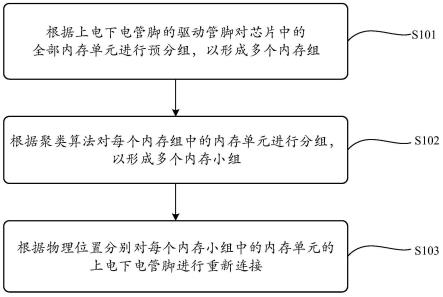

12.图1是示出根据本公开的一个实施例的用于芯片设计的内存上电下电管脚重连方法的流程图;

13.图2是示出根据本公开的另一个实施例的用于芯片设计的内存上电下电管脚重连方法的流程图;

14.图3是示出根据本公开的一个实施例的用于芯片设计的内存上电下电管脚重连装置的示意性框图;

15.图4是示出根据本公开的另一个实施例的用于芯片设计的内存上电下电管脚重连装置的示意性框图。

具体实施方式

16.下面将结合本公开实施例中的附图,对本公开实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本公开一部分实施例,而不是全部的实施例。基于本公开中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本公开保护的范围。

17.本公开的技术方案在整体上提供一种用于芯片设计的内存上电下电管脚重连方法和装置。在设计芯片时,设计者会根据功能和使用需求对芯片内存单元进行上下电连接,一个驱动通常会并行为多个内存单元进行上下电。本公开提供在芯片设计时对内存上电下电管脚进行重连的方法,充分考虑到内存单元的实际物理分布位置,通过对内存单元进行分组并对组内的上电下电管脚进行重连,极大地降低了内存单元的上电下电对电源网络的影响。如此,设计者在芯片设计初期可以不必考虑内存单元上电下电问题,只需按照功能和使用需求进行设计,随后可使用本公开的方法进行重连。因此可以获得既满足功能和设计需求又降低瞬时功耗的上下电连接。

18.下面结合附图来详细描述本公开的具体实施方式。

19.本公开提供一种用于芯片设计的内存上电下电管脚重连方法。参照图1,图1是示出根据本公开的一个实施例的用于芯片设计的内存上电下电管脚重连方法的流程图。如图1中所示,所述方法包括以下步骤s101-s103。步骤s101:根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组。步骤s102:根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组。步骤s103:根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接。

20.在步骤s101中,可以根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组。

21.根据本公开的实施例,芯片中通常具有多个内存单元,而内存单元都具有上电下

电管脚,该上下电管脚用于与驱动单元连接以便对内存单元上电或下电。而在设计芯片时,每个内存单元的上电下电管脚通常都会与驱动管脚连接来获得驱动,因此会出现一个驱动管脚连接多个内存单元的上电下电管脚的情况。从而在多个驱动管脚的情况下,每个驱动管脚会与芯片上的全部内存单元中的一部分内存单元的上电下电内存管脚相连。因此需要对上电下电管脚进行重连,以便降低瞬时压降的影响。

22.为了对上电下电管脚进行重连,可以先根据驱动单元的驱动管脚对芯片中的全部内存单元进行分组。

23.具体地,根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组可以包括:确定所述全部内存单元的上电下电管脚的驱动管脚;将每个驱动管脚所连接的所有内存单元作为一个内存组。

24.在该实施例中,可以先查询芯片中的全部内存单元的上电下电管脚所连接的驱动管脚,即确定芯片中的内存单元用到的驱动单元的驱动管脚。然后可以将连接同一驱动管脚(驱动单元)的所有内存单元分为一组,如此分组后,可获得多个内存组。考虑到在设计芯片时根据功能或设计需求使用同一驱动管脚连接多个内存单元,为了兼顾功能和设计需求,将连接同一驱动管脚的所有内存单元分为一组。

25.在将芯片上的全部内存单元分为多个内存组后,在步骤s102中,可以根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组。在该实施例中,可以对以上划分的内存组再进行更细化的分组。

26.进一步地,所述聚类算法可以包括kmean聚类算法。因此,根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组可以包括:

27.步骤1:获取中心位置;

28.步骤2:根据所述中心位置和对应的所述内存组中的所有内存单元的物理位置,确定与每个中心位置对应的中间小组;

29.步骤3:根据每个中间小组中的所有内存单元的物理位置,更新与每个中间小组对应的中心位置;

30.步骤4:当更新前的中心位置与更新后的中心位置之间的距离小于或等于预设阈值时,将所有所述中间小组作为所述内存小组;当更新前的中心位置与更新后的中心位置之间的距离大于预设阈值时,根据更新后的中心位置重复执行步骤2至步骤4。

31.在该实施例中,通过将kmean聚类算法具体应用到内存单元的分组中,可以根据内存单元的物理分布位置将上述获得的内存组再分为多个内存小组。

32.更具体地,所述步骤1可以包括:根据每个内存组中的内存单元的物理位置,确定中心位置的数量,并针对每个内存组随机选取所述数量的中心位置。

33.在该实施例中,在每个内存组中,内存单元分散分布,可以根据例如芯片设计图中的内存单元的物理位置,例如内存单元的位置坐标来确定内存单元的集中度。举例来说,通过内存单元的位置坐标,可以确定内存单元在设计图中的主要集中区域,然后可以根据内存单元主要集中的区域的数量来确定中心位置的数量。应当注意,由于各个内存组之间的内存单元集中区域的数量可能相同或不同。因此,每个内存组具有各自的中心位置的数量。当然,也可以根据内存单元的集中度,人为对每个内存组预先设定中心位置的数量。

34.针对每个内存组,在确定了中心位置的数量后,可以在每个内存组中随机选取该

数量的内存单元的物理位置(内存单元的物理位置的中心)作为初始的中心位置。当然,还可以在每个上述集中区域中随机选取一个内存单元的物理位置(内存单元的物理位置的中心)作为初始的中心位置。举例来说,在一个内存组中,大部分内存单元都集中在3个区域,则中心位置的数量为3,因此在该内存组中可以任意选取3个内存单元的物理位置作为中心位置,或者也可以在这3个区域中的每个区域中任选一个内存单元的物理位置作为中心位置。

35.所述步骤2可以包括:根据所述内存组中的所有内存单元各自的物理位置,确定距离每个内存单元最近的一个中心位置,并确定对应关系;将与同一中心位置符合对应关系的内存单元划分为一个中间小组。

36.在该实施例中,针对每个内存组,在确定了中心位置之后,可以计算内存组内的每个内存单元的物理位置(内存单元的中心坐标)距离每个中心位置的距离,并确定距离每个内存单元最近的一个中心位置。因此,每个内存单元都可以找到一个离它最近的中心位置,从而可以将每个内存单元视为归属于离它最近的中心位置,即建立对应关系。然后,可以将归属于同一中心位置的内存单元的集合作为一个中间小组。

37.所述步骤3可以包括:将每个中间小组中的所有内存单元的物理位置进行加权平均,获得与每个中间小组各自对应的平均位置;利用与每个中间小组各自对应的所述平均位置来更新对应的中心位置。

38.在该实施例中,在对每个内存组划分完中间小组后,可以计算每个内存组中的每个中间小组中的所有内存单元的中心坐标的加权平均值,即可获得每个中间小组内的内存单元的平均位置。然后,可以利用与每个中间小组对应的平均位置来替换掉与每个中间小组对应的中心位置,因此对于每个中间小组来说,更新了中心位置。

39.在步骤4中,针对每个内存组,如果更新前的中心位置与更新后的中心位置之间的距离小于或等于预设阈值,则可以将所有所述中间小组作为所述内存小组;如果更新前的中心位置与更新后的中心位置之间的距离大于预设阈值时,则可以根据更新后的中心位置重复执行上述步骤2至步骤4。该预设阈值可以根据经验认为设定。

40.在步骤s103中,可以根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接。

41.具体地,所述根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接包括:当所述内存小组包括一个内存单元时,保持所述内存单元的上电下电管脚与对应的驱动管脚连接;当所述内存小组包括至少两个内存单元时,根据所述至少两个内存单元各自上电下电管脚的物理位置,对所述上电下电管脚进行重新连接。

42.在该实施例中,在将每个内存组划分为多个内存小组后,有的内存小组可能只包括一个内存单元。对于这种情况,仍然保持该内存单元的上电下电管脚与对应的驱动管脚的连接。如果内存小组包括多个内存单元时,需要对这些内存单元的上电下电管脚进行重新连接。

43.进一步地,当所述内存小组包括至少两个内存单元时,根据所述至少两个内存单元各自上电下电管脚的物理位置,对所述上电下电管脚进行重新连接包括:在所述内存小组中的所有内存单元的上电下电管脚中,除了与对应的所述驱动管脚距离最近的上电下电管脚保持与所述驱动管脚连接以外,剩余上电下电管脚全部与所述驱动管脚断开连接;保

持连接的上电下电管脚所属内存单元的pudelay管脚(传递上电下电信号的输出管脚)与距离最近的断开连接的上电下电管脚连接;当存在断开连接的上电下电管脚时,最新连接的上电下电管脚所属内存单元的pudelay管脚与距离最近的断开连接的上电下电管脚连接,直到断开连接的上电下电管脚全部连接完毕。

44.在该实施例中,根据以上的内存分组可知,在内存小组中,多个内存单元各自的上电下电管脚连接同一驱动管脚。选择与该驱动管脚距离最近的上电下电管脚保持与驱动管脚连接,剩余的所有上电下电管脚都与该驱动管脚断开连接。然后,利用仍然保持连接的上电下电管脚所属内存单元的pudelay管脚与距离最近的一个上电下电管脚连接。该pudelay管脚是内存单元的用于传递上电下电信号的管脚,即可以将上电下电信号转发给其它内存单元的上电下电管脚。最后,判断该内存小组中是否还存在断开连接的上电下电管脚时,如果存在,则用最新连接的上电下电管脚所属内存单元的pudelay管脚与距离最近的断开连接的上电下电管脚连接,直到断开连接的上电下电管脚全部连接完毕。

45.由此,针对每个内存小组的上电下电管脚通过串联而重连完毕之后,则完成对芯片内存单元的上电下电管脚重连。这种上电下电管脚的串联可以有效避免过大的瞬时压降,从而可以减小上电下电对电源网络的影响。

46.本公开还提供另一种用于芯片设计的内存上电下电管脚重连方法。参照图2,图2是示出根据本公开的另一个实施例的用于芯片设计的内存上电下电管脚重连方法的流程图。如图2所示,所述方法在以上结合图1描述的步骤s101之前还包括以下步骤s201。

47.在该步骤s201中,将所述全部内存单元的上电下电管脚所连接的缓冲器树移除。

48.根据本公开的实施例,上电下电管脚本应连接驱动管脚,但在设计芯片时,出于设计需求,会在内存单元的上电下电管脚上连接缓冲器树,即在上电下电管脚与驱动管脚之间插入缓冲器树,这对本公开的上电下电管脚重连会造成干扰,因此需要先行将插入的这些缓冲器树去除,以便找到上电下电管脚原本应当连接的驱动管脚。

49.本公开还提供一种用于芯片设计的内存上电下电管脚重连装置。该装置用于执行以上结合图1所描述的用于芯片设计的内存上电下电管脚重连方法实施例中的步骤。可选地,该用于芯片设计的内存上电下电管脚重连装置可以应用于eda工具中,例如,该用于芯片设计的内存上电下电管脚重连装置可以集成于eda工具中。

50.参照图3,图3是示出根据本公开的一个实施例的用于芯片设计的内存上电下电管脚重连装置100的示意性框图。该用于芯片设计的内存上电下电管脚重连装置100包括第一分组模块101、第二分组模块102和重连模块103。该第一分组模块101配置为根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组。该第二分组模块102配置为根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组。该重连模块103配置为根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接。

51.根据本公开的实施例,所述第一分组模块101配置为采取如下方式根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组:确定所述全部内存单元的上电下电管脚的驱动管脚;将每个驱动管脚所连接的所有内存单元作为一个内存组。

52.根据本公开的实施例,所述聚类算法包括kmean聚类算法。

53.根据本公开的实施例,所述第二分组模块102配置为根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组:步骤1:获取中心位置;步骤2:根据所述中心位置和对应的所述内存组中的所有内存单元的物理位置,确定与每个中心位置对应的中间小组;步骤3:根据每个中间小组中的所有内存单元的物理位置,更新与每个中间小组对应的中心位置;步骤4:当更新前的中心位置与更新后的中心位置之间的距离小于或等于预设阈值时,将所有所述中间小组作为所述内存小组;当更新前的中心位置与更新后的中心位置之间的距离大于预设阈值时,根据更新后的中心位置重复执行步骤2至步骤4。

54.根据本公开的实施例,所述第二分组模块102配置为采取如下方式执行步骤1:根据每个内存组中的内存单元的物理位置,确定中心位置的数量,并针对每个内存组随机选取固定所述数量的中心位置。

55.根据本公开的实施例,所述第二分组模块102配置为采取如下方式执行所述步骤2:根据所述内存组中的所有内存单元各自的物理位置,确定距离每个内存单元最近的一个中心位置,并确定对应关系;将与同一中心位置符合对应关系的内存单元划分为一个中间小组。

56.根据本公开的实施例,所述第二分组模块102配置为采取如下方式执行所述步骤3:将每个中间小组中的所有内存单元的物理位置进行加权平均,获得与每个中间小组各自对应的平均位置;利用与每个中间小组各自对应的所述平均位置来更新对应的中心位置。

57.根据本公开的实施例,所述重连模块103配置为采取如下方式根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接:当所述内存小组包括一个内存单元时,保持所述内存单元的上电下电管脚与对应的驱动管脚连接;当所述内存小组包括至少两个内存单元时,根据所述至少两个内存单元各自上电下电管脚的物理位置,对所述上电下电管脚进行重新连接。

58.根据本公开的实施例,当所述内存小组包括至少两个内存单元时,所述重连模块103配置为采取如下方式根据所述至少两个内存单元各自上电下电管脚的物理位置,对所述上电下电管脚进行重新连接:在所述内存小组中的所有内存单元的上电下电管脚中,除了与对应的所述驱动管脚距离最近的上电下电管脚保持与所述驱动管脚连接以外,剩余上电下电管脚全部与所述驱动管脚断开连接;保持连接的上电下电管脚所属内存单元的pudelay管脚与距离最近的断开连接的上电下电管脚连接;当存在断开连接的上电下电管脚时,最新连接的上电下电管脚所属内存单元的pudelay管脚与距离最近的断开连接的上电下电管脚连接,直到断开连接的上电下电管脚全部连接完毕。

59.本公开还提供另一种用于芯片设计的内存上电下电管脚重连装置。该装置用于执行以上结合图2所描述的用于芯片设计的内存上电下电管脚重连方法实施例中的步骤。

60.参照图4,图4是示出根据本公开的另一个实施例的用于芯片设计的内存上电下电管脚重连装置200的示意性框图。图4所示的用于芯片设计的内存上电下电管脚重连装置200与图3所示的用于芯片设计的内存上电下电管脚重连装置100的区别仅在于,该装置200还包括预处理模块201。该预处理模块201配置为将所述全部内存单元的上电下电管脚所连接的缓冲器树移除。

61.可以理解的是,关于以上参照图3和图4描述的实施例中的用于芯片设计的内存上电下电管脚重连装置,其中各个模块执行操作的具体方式已经在有关用于芯片设计的内存

上电下电管脚重连方法的实施例中进行了详细描述,此处将不做详细阐述说明。

62.本公开一实施例还提供一种用于芯片设计的内存上电下电管脚重连装置,其中,所述装置包括存储器和处理器,所述存储器中存储有计算机程序,所述处理器执行所述计算机程序时,实现如下步骤:

63.根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组;根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组;根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接。

64.可以理解的是,所述处理器执行所述计算机程序时实现的步骤与上述方法中的各个步骤的实现方式基本一致,具体方式已经在有关用于芯片设计的内存上电下电管脚重连方法的实施例中进行了详细描述,此处将不做详细阐述说明。

65.在另一方面中,本公开提供一种计算机可读存储介质,其中,所述存储介质存储有计算机程序,所述计算机程序被执行时,实现如下步骤:

66.根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组;根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组;根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接。

67.可以理解的是,所述处理器执行所述计算机程序时实现的步骤与上述方法中的各个步骤的实现方式基本一致,具体方式已经在有关用于芯片设计的内存上电下电管脚重连方法的实施例中进行了详细描述,此处将不做详细阐述说明。

68.依据以下条款可更好地理解前述内容:

69.条款a1,一种用于芯片设计的内存上电下电管脚重连方法,其中,所述方法包括:根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组;根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组;根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接。

70.条款a2,根据条款a1所述的用于芯片设计的内存上电下电管脚重连方法,其中,在根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组以形成多个内存组之前,所述方法还包括:将所述全部内存单元的上电下电管脚所连接的缓冲器树移除。

71.条款a3,根据条款a1所述的用于芯片设计的内存上电下电管脚重连方法,其中,所述根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组包括:确定所述全部内存单元的上电下电管脚的驱动管脚;将每个驱动管脚所连接的所有内存单元作为一个内存组。

72.条款a4,根据条款a3所述的用于芯片设计的内存上电下电管脚重连方法,其中,所述聚类算法包括kmean聚类算法。

73.条款a5,根据条款a4所述的用于芯片设计的内存上电下电管脚重连方法,其中,所述根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组包括:步骤1:获取中心位置;步骤2:根据所述中心位置和对应的所述内存组中的所有内存单元的物理位置,确定与每个中心位置对应的中间小组;步骤3:根据每个中间小组中的所有内存单元的物理位置,更新与每个中间小组对应的中心位置;步骤4:当更新前的中心位置与更新后的中心位置之间的距离小于或等于预设阈值时,将所有所述中间小组作为所述内存小组;当更新前的中心位置与更新后的中心位置之间的距离大于预设阈值时,根据更新后的中心位

置重复执行步骤2至步骤4。

74.条款a6,根据条款a5所述的用于芯片设计的内存上电下电管脚重连方法,其中,所述步骤1包括:根据每个内存组中的内存单元的物理位置,确定中心位置的数量,并针对每个内存组随机选取所述数量的中心位置。

75.条款a7,根据条款a6所述的用于芯片设计的内存上电下电管脚重连方法,其中,所述步骤2包括:根据所述内存组中的所有内存单元各自的物理位置,确定距离每个内存单元最近的一个中心位置,并确定对应关系;将与同一中心位置符合对应关系的内存单元划分为一个中间小组。

76.条款a8,根据条款a7所述的用于芯片设计的内存上电下电管脚重连方法,其中,所述步骤3包括:将每个中间小组中的所有内存单元的物理位置进行加权平均,获得与每个中间小组各自对应的平均位置;利用与每个中间小组各自对应的所述平均位置来更新对应的中心位置。

77.条款a9,根据条款a1所述的用于芯片设计的内存上电下电管脚重连方法,其中,所述根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接包括:当所述内存小组包括一个内存单元时,保持所述内存单元的上电下电管脚与对应的驱动管脚连接;当所述内存小组包括至少两个内存单元时,根据所述至少两个内存单元各自上电下电管脚的物理位置,对所述上电下电管脚进行重新连接。

78.条款a10,根据条款a9所述的用于芯片设计的内存上电下电管脚重连方法,其中,所述当所述内存小组包括至少两个内存单元时,根据所述至少两个内存单元各自上电下电管脚的物理位置,对所述上电下电管脚进行重新连接包括:在所述内存小组中的所有内存单元的上电下电管脚中,除了与对应的所述驱动管脚距离最近的上电下电管脚保持与所述驱动管脚连接以外,剩余上电下电管脚全部与所述驱动管脚断开连接;保持连接的上电下电管脚所属内存单元的pudelay管脚与距离最近的断开连接的上电下电管脚连接;当存在断开连接的上电下电管脚时,最新连接的上电下电管脚所属内存单元的pudelay管脚与距离最近的断开连接的上电下电管脚连接,直到断开连接的上电下电管脚全部连接完毕。

79.条款a11,一种用于芯片设计的内存上电下电管脚重连装置,其中,所述装置包括:第一分组模块,其配置成根据上电下电管脚的驱动管脚对芯片中的全部内存单元进行预分组,以形成多个内存组;第二分组模块,其配置成根据聚类算法对每个内存组中的内存单元进行分组,以形成多个内存小组;重连模块,其配置成根据物理位置分别对每个内存小组中的内存单元的上电下电管脚进行重新连接。

80.以上对本公开实施例进行了详细介绍,本文中应用了具体个例对本公开的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本公开的方法及其核心思想;同时,对于本领域的一般技术人员,依据本公开的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本公开的限制。

81.应当理解,本公开的权利要求、说明书及附图中的术语“第一”和“第二”、等是用于区别不同对象,而不是用于描述特定顺序。本公开的说明书和权利要求书中使用的术语“包括”和“包含”指示所描述特征、整体、步骤、操作、元素和/或组件的存在,但并不排除一个或多个其它特征、整体、步骤、操作、元素、组件和/或其集合的存在或添加。

82.还应当理解,在此本公开说明书中所使用的术语仅仅是出于描述特定实施例的目

的,而并不意在限定本公开。如在本公开说明书和权利要求书中所使用的那样,除非上下文清楚地指明其它情况,否则单数形式的“一”、“一个”及“该”意在包括复数形式。还应当进一步理解,在本公开说明书和权利要求书中使用的术语“和/或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

83.以上对本公开实施例进行了详细介绍,本文中应用了具体个例对本公开的原理及实施方式进行了阐述,以上实施例的说明仅用于帮助理解本公开的方法及其核心思想。同时,本领域技术人员依据本公开的思想,基于本公开的具体实施方式及应用范围上做出的改变或变形之处,都属于本公开保护的范围。综上所述,本说明书内容不应理解为对本公开的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。