1.本发明有关于微电子领域的技术,且特别有关于一种执行新增指令的方法及系统。

背景技术:

::2.处理器技术这些年来得到迅速发展。随着处理器功能的增强,后代处理器往往会在前代处理器的基础上增加新的指令。由于前代处理器无法执行后代处理器所支持的新增指令,当前代处理器执行到新增指令时,会产生未知指令异常(#ud),进而造成包含新增指令的进程被操作系统终止。从而导致包含新增指令的应用程序或操作系统无法在前代处理器上执行。3.因此,需要一种执行新增指令的方法及系统,以达到在前代处理器上执行新增指令的目的。技术实现要素:4.以下公开的内容仅为示例性的,且不意指以任何方式加以限制。除了所述说明方面、实施方式和特征之外,通过参照附图和下述具体实施方式,其他方面、实施方式和特征也将显而易见。即,以下公开的内容被提供以介绍概念、重点、益处以及本文所描述新颖且非显而易见的技术优势。所选择,非所有的,实施例将进一步详细描述如下。因此,以下公开的内容并不意旨在所要求保护主题的必要特征,也不意旨在决定所要求保护主题的范围中使用。5.因此,本发明的主要目的在于提供一种执行新增指令的方法及系统,以达到无需更改前代处理核心的硬件架构即可执行新增指令的目的。6.本发明提出一种执行新增指令的方法,包括:接收一指令,当上述接收指令为未知指令时,发出一未知指令异常。响应于上述未知指令异常,通过一转换程序:判断上述接收指令是否为新增指令;当上述接收指令为新增指令时,将上述接收指令转换为至少一个旧指令。以及,在与上述接收指令相同的执行模式下,执行上述至少一个旧指令。7.本发明提出一种执行新增指令的系统,包括:一指令译码单元(decoder),接收一指令,判断上述接收指令是否为未知指令。一指令提交单元,当上述接收指令为未知指令时,上述指令提交单元发出一未知指令异常。响应于上述未知指令异常,上述执行新增指令的系统通过一转换程序:判断上述接收指令是否为新增指令;以及当上述接收指令为新增指令时,将上述接收指令转换为至少一个旧指令。其中,上述执行新增指令的系统在与上述接收指令相同的执行模式下,执行上述至少一个旧指令。8.通过本发明提供的执行新增指令的方法与执行新增指令的系统,在不对处理核心的硬件架构进行修改的情况下,就可以在前代处理器上执行新增指令。附图说明9.图1是显示根据本发明第一实施例所述的执行新增指令的系统的示意图。10.图2是依据本发明第一实施例所述的处理器的结构图。11.图3是显示根据本发明第一实施例所述的执行新增指令的流程图。12.图4是显示根据本发明第一实施例所述的处理接收指令的流程图。13.图5是显示根据本发明第一实施例所述的进入系统管理模式的流程图。14.图6是显示根据本发明第一实施例所述的模拟器的处理流程图。15.图7是显示根据本发明第一实施例所述的转换程序的处理流程图。16.图8是显示根据本发明第一实施例所述的在系统管理模式下处理未知指令的例子。17.图9a~9b是显示根据本发明第一实施例所述的退出系统管理模式的流程图。18.图10是显示根据本发明第二实施例所述的执行新增指令的系统的示意图。19.图11是依据本发明第二实施例所述的处理器的结构图。20.图12是显示根据本发明第二实施例所述的执行新增指令的流程图。21.图13是显示根据本发明第二实施例所述的处理接收指令的流程图。22.图14是显示根据本发明第二实施例所述的在处理未知指令异常的微码中处理接收指令的流程图。23.图15a~15b是显示根据本发明第三实施例所述的执行新增指令的系统的示意图。24.图16是依据本发明第三实施例所述的处理接收指令的流程图。25.图17是显示根据本发明第四实施例所述的执行新增指令的系统的示意图。26.图18是显示根据本发明一实施例所述的执行新增指令的流程图。27.图19是显示根据本发明一实施例所述的执行新增指令的流程图。28.图20是依据本发明一实施例所述的转换新增指令的流程图。29.图21是显示用以实现本发明实施例的示例性操作环境。30.其中,附图中符号的简单说明如下:31.100:执行新增指令的系统;110:处理器;112:中断预处理单元;114:系统管理模式出/入口;1142:系统管理模式入口;1144:系统管理模式出口;120:操作系统;130:应用程序;118:指令;132:未知指令;142:模拟器;145:转换程序;200:处理器;201:指令旁路转换缓冲;202:指令快取;203:分支预测器;230:指令译码单元;204:重命名单元;205:保留站;206:执行单元;207:访存单元;220:微体系结构寄存器;240:重排缓冲区;245:指令提交单元;250:系统管理模式;260:架构寄存器;s305、s310、s315、s320、s325:步骤;s405、s410、s415、s420、s425、s430、s435:步骤;s505、s510、s515、s520、s525、s530:步骤;s605、s610、s615、s620、s625、s630、s635、s640、s645:步骤;s705、s710、s712、s715、s720、s725:步骤;s901、s904、s903、s905、s907、s909、s911、s913、s915、s917、s919、s921、s923、s925、s927、s929、s933:步骤;1000:执行新增指令的系统;1100:处理器;1110:转换程序;s1205、s1210、s1215、s1220、s1225:步骤;s1305、s1310、s1315、s1320、s1325:步骤;s1405、s1410、s1415、s1420、s1425:步骤;1500:执行新增指令的系统;150:内核驱动程序;1600:流程图;s1605、s1610、s1620、s1625:步骤;1700:执行新增指令的系统;190:专用处理核心;s1805、s1810、s1815、s1820、s1825:步骤;s1905、s1910、s1915、s1920、s1925:步骤;s2005、s2010、s2015:步骤;2100:计算装置;2110:总线;2112:内存;2114:处理器;2116:显示元件;2118:i/o端口;2120:i/o元件;2122:电源供应器。具体实施方式32.在下文中将参考附图对本发明的各方面进行更充分的描述。然而,本发明可以具体化成许多不同形式且不应解释为局限于贯穿本发明所呈现的任何特定结构或功能。相反地,提供这些方面将使得本发明周全且完整,并且本发明将给本领域技术人员充分地传达本发明的范围。基于本文所教导的内容,本领域的技术人员应意识到,无论是单独还是结合本发明的任何其它方面实现本文所公开的任何方面,本发明的范围旨在涵盖本文中所公开的任何方面。例如,可以使用本文所提出任意数量的装置或者执行方法来实现。另外,除了本文所提出本发明的多个方面之外,本发明的范围更旨在涵盖使用其它结构、功能或结构和功能来实现的装置或方法。应可理解,其可通过权利要求的一或多个元件具体化本文所公开的任何方面。33.词语“示例性”在本文中用于表示“用作示例、实例或说明”。本发明的任何方面或本文描述为“示例性”的设计不一定被解释为优选于或优于本发明或设计的其他方面。此外,相同的数字在所有若干图示中指示相同的元件,且除非在描述中另有指定,冠词“一”和“上述”包含多个的参考。34.可以理解,当元件被称为被“连接”或“耦接”至另一元件时,该元件可被直接地连接到或耦接至另一元件或者可存在中间元件。相反地,当该元件被称为被“直接连接”或“直接耦接”至到另一元件时,则不存在中间元件。用于描述元件之间的关系的其他词语应以类似方式被解释(例如,“在…之间”与“直接在…之间”、“相邻”与“直接相邻”等方式)。35.为了更好地描述本发明的实施例,下面先对本发明中用到的专用名词进行定义。36.旧指令:被前代处理器原生支持的指令被称为原生指令(nativeinstruction),也被称为已存在指令或旧指令。37.未知指令:不被前代处理器原生支持的指令。38.新增指令:与前代处理器相比,后代处理器所新增支持的指令。新增指令无法被前代处理器所辨识,因此对前代处理器而言属于未知指令。39.新增架构寄存器:与前代处理器相比,后代处理器所新增支持的架构寄存器。新增架构寄存器在前代处理器中并不存在,因此在前代处理器上模拟执行使用新增架构寄存器的新增指令时,需要模拟新增架构寄存器。40.无法辨识指令:未知指令中,除去新增指令之后剩余的那部分指令。即,无法辨识指令是指不被后代处理器原生支持的指令。41.模型特别寄存器:处理器中的一类寄存器,可用于完成一些特定的功能。42.陷阱:陷阱一般由软中断指令(比如int指令)引起。当一条指令引起陷阱异常时,并不表示这条指令本身的执行出现错误。因此,当一条指令出现陷阱异常后,处理器会继续执行这条指令的下一条指令。举例来说,软件开发人员对软件程序码进行调试时,可在程序码中设置断点。在处理器上执行设置了断点的程序码时,执行到断点时,将产生一个陷阱,从而使得程序码在断点处暂停执行。软件开发人员通过处理陷阱的微码处理程序,可以查看程序码执行到断点时处理器中各架构寄存器的值或程序码中各个变量的值。并根据各架构寄存器的值或程序码中各个变量的值,判断执行到断点时程序码是否执行正常。43.本发明所述的处理器可为具备精简指令集运算(reducedinstructionsetcomputing,risc,例如arm/mips/risc-v指令集)、复杂指令集运算(complexinstructionsetcomputing,cisc,例如x86指令集)、或其他指令集类型的处理器;亦或是能同时支持多种不同指令集架构的处理器(例如同时支援x86指令集与arm指令集的处理器)。本发明在处理器所支持的指令集类型上并不做特别限定,但为方便说明,本说明书实施例以支持x86指令集的处理器来描述。此外,本领域技术人员皆知,x86处理器会依据原始程序顺序(in-order)解译宏指令(macroinstruction)成为至少一个微指令(microinstruction)或微指令序列,但微指令的执行方式是以乱序(out-of-order)方式进行以提升执行效率,只是微指令执行完毕后的提交(retire)过程中仍以原始的程序顺序进行。44.本发明具有多种实施方式,下面用4个实施例来描述本发明的4种主要的实施方式。第一实施例为在系统管理模式下模拟执行新增指令的实施方式。第二实施例为在与新增指令相同的执行模式下模拟执行新增指令的实施方式。第三实施例以及第四实施例为通过操作系统模拟执行新增指令的实施方式,其中,第四实施例使用一专用处理核心完成对新增指令的转换操作。下面先描述第一实施例。45.[第一实施例][0046]图1是显示根据发明第一实施例所述的执行新增指令的系统的示意图。如图1所示,执行新增指令的系统100包含处理器110、操作系统120、应用程序130以及模拟器142。操作系统120运行于处理器110之上,用于对处理器110进行管理。应用程序130运行于操作系统120之上,可以通过操作系统120使用处理器110以及其它硬件(未示出,比如硬盘、网卡等等)提供的各种功能。模拟器142运行于处于系统管理模式(systemmanagementmode,smm)下的处理器110之上。操作系统120或应用程序130,无法感知到模拟器142的执行过程。即,模拟器142执行的所有操作,对操作系统120或应用程序130是透明的。[0047]当处理器110执行到应用程序130或操作系统120的一条未知指令时,处理器110会进入系统管理模式,并将上述未知指令发送模拟器142进行处理。如果上述未知指令为新增指令,模拟器142将模拟执行上述新增指令。值得注意的是,应用程序130或操作系统120的源码一般是使用高级语言(比如c语言、c 语言,等等)和/或低级语言(比如汇编语言,等等)编写的。使用编译器(compiler)对源码进行编译后,生成可以被处理器执行的可执行代码。可执行代码由可以被处理器执行的指令组成。在本发明中,应用程序130或操作系统120是指经编译器对应用程序130或操作系统120的源码编译后,生成的可执行代码。下面将以图1中的处理器110处理未知指令132为例,对执行新增指令的系统100的处理过程进行简单的描述。[0048]如图1所示,处理器110包含中断预处理单元112以及系统管理模式出/入口114。系统管理模式出/入口114包含系统管理模式入口1142以及系统管理模式出口1144。图1中带数字编号的实线箭头表示指令信息的传输方向,带数字编号的虚线箭头表示指令模拟执行结果的传输方向。下面描述处理器110处理未知指令132的整个过程。[0049]首先,处理器110接收应用程序130中完成指定功能的指令118(如实线箭头1所示)。接收到指令118之后,处理器110判断指令118是否为未知指令132。若指令118为未知指令132,处理器110发出一未知指令异常(#ud)。响应于上述未知指令异常,中断预处理单元112执行未知指令异常的微码处理程序。在未知指令异常的微码处理程序中,中断预处理单元112设置一模拟标识(emulationflag,ef)并发出一系统管理中断(#smi),同时把未知指令132的指令信息发送给系统管理模式出/入口114(如实线箭头2所示)。对于如何发出未知指令异常以及系统管理中断,为本领域技术人员的通常知识,此处就不赘述了。在一实施例中,处理器110是支持x86指令集的处理器,中断预处理单元112是微码控制单元。在实际操作上,本领域技术人员可以对中断预处理单元112中保存的未知指令异常的微码处理程序进行修改,以添加设置模拟标识、获取未知指令的指令信息,以及发出系统管理中断的功能。由于这些微码会依处理器版本而不同,本领域技术人员可依实际情况撰写对应的微码。[0050]然后,处理器110通过执行系统管理模式入口1142进入系统管理模式,并把未知指令132的指令信息发送给模拟器142(如实线箭头3所示)。在系统管理模式中,模拟器142判断未知指令132是否为新增指令。如果未知指令132为新增指令,模拟器142模拟执行上述新增指令。模拟执行完上述新增指令之后,模拟器142把模拟执行结果发送给系统管理模式出/入口114(如虚线箭头4所示)。然后,处理器110通过系统管理模式出口1144将模拟执行结果发送给应用程序130(如虚线箭头5所示),并退出系统管理模式。到此,处理器110就处理完了未知指令132。在一实施例中,在模拟器142模拟执行上述新增指令的过程中,可以将模拟执行过程中产生的中间运算结果存入系统管理内存(smram)中。[0051]图2是显示根据本发明第一实施例所述的处理器的结构图。如图2所示,位于虚线左边的处理器200为图1所示的处理器110的结构图,位于虚线右边的模拟器142以及转换程序145运行于处于系统管理模式下的处理器200之上。在一实施例中,转换程序145所完成的功能实现于一转换模块中,或者,也可以把转换程序145看作是执行新增指令的系统100中的转换模块。下面结合图1对图2进行说明。[0052]如图2所示,处理器200包含指令旁路转换缓冲(instructiontranslationlookasidebuffer,itlb)201、指令快取(instructioncache)202以及分支预测器(branchpredictor)203。当处理器200执行到应用程序130或是操作系统120的一指令时,处理器200的指令旁路转换缓冲201接收此指令。分支预测器203用于对条件分支进行预测,并将分支预测结果传给指令快取202。指令快取202根据分支预测结果从指令旁路转换缓冲201获取上述接收指令,然后处理器200会对上述接收指令做进一步的处理。[0053]如图2所示,处理器200还包含指令译码单元230。指令译码单元230判断上述接收指令是否为未知指令,然后生成至少一微指令,其中,上述微指令中包含一未知指令标识,用于表示上述接收指令是否为未知指令。当未知指令标识为第一数值时,表示上述接收指令为未知指令。当未知指令标识为第二数值时,表示上述接收指令为旧指令。在一实施例中,第一数值为1,第二数值为0。[0054]处理器200还包含重命名单元204、保留站205、执行单元206、访存单元207、重排缓冲区240、中断预处理单元112以及架构寄存器260。重命名单元204从指令译码单元230接收微指令后,对其进行重命名处理,其中,上述微指令中包含一未知指令标识(ud)。然后,重命名单元204将重命名后的微指令发送给保留站205和重排缓冲区240。保留站205根据上述微指令的类型,将上述微指令发送给执行单元206或访存单元207做进一步处理。重排缓冲区240接收到上述微指令后,将其存入指令条目中。重排缓冲区240中包含多个指令条目,每个指令条目包含一未知指令标识字段,用于保存上述微指令中的未知指令标识。[0055]重排缓冲区240包含指令提交单元245。当上述微指令满足提交(retire)条件时,指令提交单元245会提交上述微指令。提交上述微指令时,如果执行上述微指令时没有产生异常,指令提交单元245会根据上述微指令的执行结果更新架构寄存器260。如果执行上述微指令时产生了异常,指令提交单元245会报告(report)上述异常。响应于上述异常,处理器200会执行上述异常的微码处理程序。[0056]当指令提交单元245提交上述微指令时,如果上述微指令的未知指令标识为第一数值,指令提交单元245会发出一未知指令异常(#ud)。响应于上述未知指令异常,处理器200执行未知指令异常的微码处理程序。在上述未知指令异常的微码处理程序中,处理器200将一值为第一数值的模拟标识存入微体系结构寄存器220中,并发出一系统管理中断(#smi)。响应于上述系统管理中断,处理器200将通过如图1所示的系统管理模式入口1142,根据微体系结构寄存器220中存储的上述模拟标识进入系统管理模式。在系统管理模式下,处理器200通过模拟器142处理上述接收指令。首先,模拟器142判断上述接收指令是否为新增指令。如果上述接收指令为新增指令,模拟器142将模拟执行上述接收指令。在模拟执行上述接收指令的过程中,模拟器142可以将中间运算结果存入系统管理内存(smram)。需要说明的是,当模拟标识为第一数值时,表示需要模拟器142处理上述接收指令;当模拟标识为第二数值时,表示不需要模拟器142处理上述接收指令。[0057]模拟器142处理完上述接收指令后,处理器200通过执行如图1所示的系统管理模式出口1144退出系统管理模式。系统管理模式出口1144将微体系结构寄存器220中存储的模拟标识设置为第二数值,然后退出系统管理模式。当处理器200执行另一指令,并且另一指令为未知指令时,处理器200在执行未知指令异常的微码处理程序时,又会把微体系结构寄存器220中存储的模拟标识设置为第一数值。然后,处理器200按前述的处理过程处理上述另一指令。[0058]图3是显示根据本发明第一实施例所述的执行新增指令的流程图。请同时参照图2与图3,如图3所示,指令译码单元230接收一指令(s305),当上述接收指令为未知指令时,指令提交单元245发出一未知指令异常(s310)。响应于上述未知指令异常,处理器200进入一系统管理模式(s315),并通过一转换程序判断上述接收指令是否为新增指令(s320)。当上述接收指令为新增指令时,处理器200通过执行至少一个旧指令来模拟上述接收指令的执行(s325)。详细说明如下:指令译码单元230先执行步骤s305。[0059]在步骤s305中,指令译码单元230接收一指令。具体而言,指令译码单元230从指令快取202接收上述指令。然后,处理器200执行步骤s310。[0060]在步骤s310中,当上述接收指令为未知指令时,指令提交单元245发出一未知指令异常。具体来说,如前所述,当指令译码单元230判断上述接收指令为未知指令后,将生成一微指令,其中,上述微指令中包含一值为第一数值的未知指令标识。然后,指令译码单元230把上述微指令发送给重命名单元204。重命名单元204对上述微指令进行重命名处理,然后将上述微指令发送给重排缓冲区240。重排缓冲区240将上述微指令存入一指令条目中。当上述微指令满足提交(retire)条件时,指令提交单元245从上述指令条目中读取上述微指令,并对上述微指令进行提交处理。由于上述微指令的未知指令标识为第一数值,指令提交单元245发出一未知指令异常。然后,处理器200执行步骤s315。[0061]在步骤s315中,响应于上述未知指令异常,处理器200进入一系统管理模式(systemmanagementmode,smm)。具体来说,响应于上述未知指令异常,处理器200执行未知指令异常的微码处理程序。在上述未知指令异常的微码处理程序中,处理器200将一值为第一数值的模拟标识(emulationflag,ef)写入微体系结构寄存器220中,并发出一系统管理中断(#smi)。响应于上述系统管理中断,处理器200将通过如图1所示的系统管理模式入口1142,根据上述模拟标识进入系统管理模式。然后执行步骤s320。[0062]在步骤s320中,在上述系统管理模式下,处理器200通过一转换程序判断上述接收指令是否为新增指令。至于转换程序是如何判断上述接收指令是否为新增指令的,后文将结合图7进行详细说明。在一实施例中,上述转换程序可被预先储存于一基本输入输出系统(bios)中。本领域技术人员皆知,执行新增指令的系统100开机启动时,会执行上述基本输入输出系统。上述基本输入输出系统中包含对系统管理模式进行初始化的代码。当执行新增指令的系统100执行到上述对系统管理模式进行初始化的代码时,会将上述转换程序载入系统管理内存中(smram)。然后,处理器200就可以在进入系统管理模式后,直接执行存储于系统管理内存中的上述转换程序了。然后,处理器200执行步骤s325。[0063]在步骤s325中,当上述接收指令为新增指令时,处理器200通过执行至少一个旧指令来模拟上述接收指令的执行。具体来说,当上述接收指令为新增指令时,处理器200会先通过上述转换程序把上述接收指令转换为至少一个旧指令。然后,处理器200执行上述至少一个旧指令。至于更详细的说明,参见后文对图6的步骤s615、s620、s625以及s630的描述。[0064]在一实施例中,上述接收指令为指令集架构指令,上述至少一个旧指令为指令集架构指令。在另一实施例中,上述接收指令为x86指令、arm指令、risc-v指令或mips指令,上述至少一个旧指令为x86指令、arm指令、risc-v指令或mips指令。[0065]图4是显示根据本发明第一实施例所述的处理接收指令的流程图。请同时参照图2与图4,如图4所示,指令译码单元230接收一指令(s405),并判断上述接收指令是否为一未知指令(s410)。当上述接收指令为未知指令时,进入系统管理模式处理上述接收指令。由于步骤s405与图3的步骤s305相同,此处就不赘述了。下面描述步骤s410。[0066]在步骤s410中,指令译码单元230判断上述接收指令是否为一未知指令。具体而言,指令译码单元230对接上述收指令进行译码,以获得上述接收指令的译码信息。在一实施例中,上述译码信息包含前缀(prefix)、转义码(escapecode)、操作码(opcode)、操作数模式(modr/m)以及其它译码信息,等等。然后,指令译码单元230根据上述译码信息判断上述接收指令是否为未知指令。举例来说,可以将处理器200所原生支持的旧指令的操作码存放到一个查找表(lookuptable)中。指令译码单元230可以查看上述接收指令的上述操作码是否存放在上述查找表中,如果存放在上述查找表中,则表示上述接收指令为旧指令;否则,表示上述接收指令为未知指令。在一实施例中,上述查找表存储在指令译码单元230中。[0067]当上述接收指令为旧指令时(步骤s410中的“否”),执行步骤s435。在步骤s435中,处理器200正常处理上述接收指令。至于如何正常处理上述接收指令,例如将上述旧指令转换为与其对应的微指令,并执行上述对应的微指令,为本领域技术人员的通常知识,此处就不赘述了。当上述接收指令为未知指令(步骤s410中的“是”)时,执行步骤s415。[0068]在步骤s415中,处理器200将一模拟标识写入一微体系结构寄存器220中。具体而言,当上述接收指令为未知指令时,指令译码单元230生成一微指令,上述微指令的未知指令标识为第一数值。在一实施例中,上述微指令为空操作微指令(nop)。指令译码单元230将上述微指令发送给重命名单元204。重命名单元204对上述微指令做重命名处理。然后,重命名单元204把上述微指令发送给重排缓冲区240。重排缓冲区240将上述微指令保存在自己的指令条目中。当提交上述微指令时,由于上述微指令的未知指令标识为第一数值,指令提交单元245对发出一未知指令异常。响应于上述未知指令异常,处理器200执行未知指令异常的微码处理程序。在上述未知指令异常的微码处理程序中,处理器200将一模拟标识写入微体系结构寄存器220中。另外,处理器200还将上述接收指令的信息以及上述接收指令的运行环境信息存入微体系结构寄存器220中。然后,在上述未知指令异常的微码处理程序中,处理器200发出一系统管理中断(#smi)。在一实施例中,上述接收指令的信息包括上述接收指令的指令指针。在另一实施例中,上述接收指令的信息包括上述接收指令的指令指针和上述接收指令的机器码。上述运行环境信息包含上述接收指令的运行模式(即处理器200执行到上述接收指令时,处理器200的运行模式)。举例来说,运行模式包含实模式(readmode)、保护模式(protectedmode)、虚拟8086模式(v8086mode)、兼容模式(compatibilitymode)以及长模式(longmode),等等。然后,处理器200执行步骤s420。[0069]在步骤s420中,处理器200进入系统管理模式。具体来说,响应于上述系统管理中断,处理器200通过执行如图1所示的系统管理模式入口1142,进入系统管理模式。至于处理器200进入系统管理模式的细节,后文将结合图5进行详述。然后,处理器200执行步骤s425。[0070]在步骤s425中,处理器200处理上述接收指令。至于处理器200如何处理上述接收指令,后文将结合图6~8进行详细描述。然后,处理器200执行步骤s430。[0071]在步骤s430中,处理器200退出系统管理模式,并结束此流程。具体而言,处理器200通过执行如图1所示的系统管理模式出口1144,退出系统管理模式。至于处理器200如何退出系统管理模式,后文将结合图9a~9b进行详细描述。[0072]图5是显示根据本发明第一实施例所述的进入系统管理模式的流程图。图5为与图1所示的系统管理模式入口1142对应的微码处理程序的处理流程。请参照图2与图5,如图5所示,处理器200禁用中断(s505),判断模拟标识是否为第一数值(s510)。如果步骤s510的判断结果为“是”,则进入系统管理模式。详细说明如下:处理器200先执行步骤s505。[0073]在步骤s505中,处理器200禁用中断。本领域技术人员皆知,在系统管理模式下是禁用中断的,因此本发明中也延续此架构要求而禁用中断。至于如何禁用中断,举例来说,处理器200将if标识清零以禁用可屏蔽中断,将tf标识清零以禁用单步中断,将dr7清零以禁用断点中断。然后,处理器200执行步骤s510。[0074]接着,在步骤s510中,处理器200判断上述模拟标识是否为第一数值。具体而言,处理器200判断微体系结构寄存器220中保存的模拟标识是否为第一数值。如果判断结果为“否”,执行步骤s530,以执行进入系统管理模式的正常处理流程。本领域技术人员都了解系统管理模式的正常处理流程,此处就不赘述了。如果判断结果为“是”,处理器200执行步骤s515。[0075]在步骤s515中,处理器200发出进入系统管理模式通知(assert#smmact),以通知芯片组处理器200进入了系统管理模式。至于如何发出进入系统管理模式通知,为本领域技术人员的通常知识,此处就不赘述了。然后,处理器200执行步骤s520。[0076]在步骤s520中,处理器200将模拟标识、接收指令的信息以及运行环境信息存入系统管理内存中。具体而言,处理器200从微体系结构寄存器220读取模拟标识、接收指令的信息以及运行环境信息,并将读取到的模拟标识、接收指令的信息以及运行环境信息存入系统管理内存中。同时,架构寄存器260中的内容(即处理器200的当前状态)也会被存入系统管理内存中。系统管理内存中存储的信息如下表1所示。[0077]表1[0078][0079]然后,处理器200执行步骤s525中,建立系统管理模式执行环境,并进入系统管理模式。对于如何建立系统管理模式执行环境以及如何进入系统管理模式,为本领域技术人员的通常知识,此处就不赘述了。[0080]值得注意的是,在图5所示的通过图1的系统管理模式入口1142进入系统管理模式的实际操作上,本领域技术人员可在发出系统管理中断(#smi)后,在进入系统管理模式对应的微码中加入一些执行保存模拟标识、上述接收指令的信息和运行环境信息至系统管理内存(smram)的微码,并确保这些数据/信息不会因处理器200切换至系统管理模式而被覆写(overwrite)。再者,因为在已知技术下,处于系统管理模式下的处理器200会去访问系统管理内存(smram),所以本领域技术人员可基于这部分的微码做修改,即可达到访问这些数据/信息的目的。由于这些微码会依处理器版本而不同,本领域技术人员可依据实际状况撰写对应的微码。[0081]然后,处理器200在系统管理模式下处理上述接收指令(如图4所示的步骤s425)。下面结合图6~8详述处理器200如何在系统管理模式下处理上述接收指令。[0082]图6是显示根据本发明第一实施例所述的模拟器的处理流程图。如前所述,处理器200在系统管理模式中通过模拟器142对上述接收指令进行处理。请参照图2和图6,如图6所示,在系统管理模式中,模拟器142建立模拟运行环境(s605),然后判断模拟标识是否为第一数值(s610)。如果步骤s610的判断结果为“是”,模拟器142通过转换程序转换上述接收指令,并生成一转换结果(s615)。然后,模拟器142处理上述转换结果。详细说明如下:首先,模拟器142执行步骤s605。[0083]在步骤s605中,模拟器142建立模拟运行环境。具体而言,模拟器142从系统管理内存读取模拟标识、接收指令的信息、接收指令的运行环境信息以及架构寄存器的信息。后续步骤中,将使用上述读取到的信息模拟执行上述接收指令。然后,模拟器142执行步骤s610。[0084]在步骤s610中,模拟器142判断模拟标识是否为第一数值。具体而言,模拟器142判断在步骤s605中读取到的模拟标识是否为第一数值。如果判断结果为“否”,模拟器142执行步骤s645。在步骤s645中,模拟器142执行系统管理模式的正常处理流程。对于系统管理模式的正常处理流程,为本领域技术人员的通常知识,此处就不再赘述了。如果步骤s610的判断结果为“是”,模拟器142执行步骤s615。[0085]在步骤s615中,模拟器142通过转换程序145转换上述接收指令,并生成一转换结果。转换结果的结构如下面的表2所示,包含结果和内容两个字段。当结果字段为第一数值时,表示转换成功,此时内容字段中包含由上述接收指令转换得到的至少一个旧指令以及上述接收指令的长度;当结果字段为第二数值时,表示转换失败,此时内容字段中包含一异常编号。至于如何通过转换程序145转换上述接收指令,后文将结合图7详述。[0086]表2[0087]结果内容……[0088]在步骤s620中,模拟器142判断上述转换程序是否转换成功。具体而言,模拟器142根据上述转换结果中的结果字段,判断上述转换程序是否转换成功。当转换结果的结果字段为第一数值时,判断结果为“是”,模拟器142执行步骤s625;当转换结果的结果字段为第二数值时,判断结果为“否”,模拟器142根据转换结果生成模拟执行结果,然后执行步骤s630。模拟执行结果的结构如下面的表3所示,包含结果和详情两个字段。当模拟执行结果的结果字段为第一数值时,表示模拟执行成功,详情字段中保存模拟执行后获得的运算结果;当模拟执行结果的结果字段为第二数值时,表示模拟执行失败,详情字段中保存异常编号。当模拟执行结果的结果字段为第二数值时,根据转换结果生成的模拟执行结果如下面的表3-1所示。表3-1中的详情字段中的异常编号,就是转换结果的内容字段中的异常编号。[0089]表3[0090]结果详情……[0091]表3-1[0092]结果详情第二数值异常编号[0093]更进一步说,当步骤s620的判断结果为转换成功时(即步骤s620的判断结果为“是”),模拟器142执行步骤s625。在步骤s625中,模拟器142从上述转换结果中获取至少一个旧指令,并执行上述至少一个旧指令。具体而言,模拟器142从上述转换结果的内容字段获取上述至少一个旧指令以及上述接收指令的长度。然后,模拟器142通过呼叫指令或跳转指令使处理器200执行上述至少一个旧指令。处理器200将上述至少一个旧指令译码为至少一个微指令,并执行上述至少一个微指令,生成一模拟执行结果。如果处理器200执行上述至少一个微指令的过程中发生了运行时异常(runtimeexception),则模拟执行结果的内容字段如下表3-2所示。表3-2中模拟执行结果的结果字段为第二数值,表示模拟执行失败;模拟执行结果的详情字段为异常编号,即运行时异常的编号。如果处理器200执行上述至少一个微指令成功,则模拟执行结果的内容字段如下表3-3所示。表3-3中模拟执行结果的结果为第一数值,表示模拟执行成功;模拟执行结果的详情字段为运算结果。[0094]表3-2[0095]结果详情第二数值异常编号[0096]表3-3[0097]结果详情第一数值运算结果[0098]在一实施例中,当上述接收指令的操作数包含新增架构寄存器时,上述新增架构寄存器利用系统管理内存进行模拟。举例来说,当处理器200的后代处理器中包含一个位宽为1024-bit的新增架构寄存器时,模拟器142可以利用系统管理内存中一连续的1024-bit的存储空间来模拟上述新增架构寄存器。也就是说,当上述接收指令访问上述新增架构寄存器时,模拟器142实际访问的是系统管理内存中的上述连续的1024-bit的存储空间。[0099]当上述新增架构寄存器为上述接收指令的目的操作数(destinationoperand)时,执行完上述至少一个旧指令后,处理器200将上述接收指令的运算结果存入上述系统管理内存中。这样,当处理器200执行另一指令,并且另一指令也为新增指令,且上述新增架构寄存器为上述另一指令的源操作数(sourceoperand)时,处理器200在模拟执行上述另一指令时,直接使用上述系统管理内存中保存的上述运算结果。需要注意的是,上述接收指令和上述另一指令可以是连续的(即相邻的),也可以不是连续的,本发明对此并不做限制。[0100]在系统管理模式下,模拟器142只能访问系统管理内存,而无法以正常的访问内存的方式访问内存(即系统内存,下同)。本发明的一实施例中,提供了一种物理内存直接访问接口,以实现在系统管理模式下访问内存的操作。当上述接收指令包含内存操作数时,可以通过上述物理内存直接访问接口访问上述内存操作数。通过上述物理内存直接访问接口访问内存操作数的步骤如下:[0101]第一步,模拟器142将上述内存操作数的虚拟地址转换为物理地址。具体而言,模拟器142通过上述物理内存直接访问接口,通过访问页表,将上述内存操作数的虚拟地址转换为物理地址。将虚拟地址转换为物理地址的步骤为:一、从系统管理内存中读出架构寄存器cr3中保存的页表基地址;二、根据页表基地址和虚拟地址进行页表查询,模拟页表查询过程后,获取到物理地址。[0102]第二步,模拟器142通过上述物理内存直接访问接口根据上述物理地址读取该内存操作数的数值,其中,该物理地址不在系统管理内存中。具体而言,模拟器142通过上述物理内存直接访问接口,利用一模型特别寄存器(modelspecificregister,msr),根据上述物理地址读取该内存操作数的数值。具体步骤为:[0103]第1步,模拟器142将上述模型特别寄存器的地址写入一第一寄存器(ecx),并将上述物理地址写入一第二寄存器(edx:eax)。[0104]第2步,模拟器142执行写模型特别寄存器指令(wrmsr),以将上述内存操作数的数值存储到上述模型特别寄存器中。具体而言,模拟器142执行完上述写模型特别寄存器指令后,上述物理地址会被写入上述模型特别寄存器中。然后,处理器1100使用上述模型特别寄存器中存储的上述物理地址,通过执行一从物理地址加载微指令(ld_phys),将上述内存操作数的数值从系统内存加载到上述模型特别寄存器中。[0105]第3步,模拟器142执行读模型特别寄存器指令(rdmsr),以从上述模型特别寄存器中读取上述内存操作数的数值,并将读取到的上述内存操作数的数值存储到上述第二寄存器中。[0106]在一实施例中,上述接收指令的下一条指令为上述另一指令。上述至少一个旧指令中的最后一条指令为跳转指令(jump)或呼叫指令(call),处理器1100通过上述跳转指令或上述呼叫指令跳转到上述另一指令。上述另一指令的指令指针为:eip length,其中,eip为上述接收指令的指令指针,length为上述接收指令的长度。[0107]然后,模拟器142执行步骤s630。在步骤s630中,模拟器142将模拟执行结果写入系统管理内存。具体而言,模拟器142将在步骤s625或步骤s620中生成的模拟执行结果写入系统管理内存。由前述可知,模拟执行结果存在两种情况:一种是模拟执行成功,一种是模拟执行失败。系统管理内存中包含一异常向量表,其结构如下表4所示。异常向量表包含异常标识和异常编号2个字段。将模拟执行结果存入系统管理内存时,需要填写系统管理内存中的异常向量表。下面分别描述模拟器142将这两种情况的模拟执行结果存入系统管理内存的过程。[0108]表4[0109]异常标识异常编号……[0110]当模拟执行成功时,模拟器142将系统管理内存中的异常向量表的异常标识字段设置为第一数值(如下面的表4-1所示),并将模拟执行结果的详情字段中存储的运算结果存入系统管理内存中。举例来说,如果上述运算结果为架构寄存器ecx的值变为了10h(即十六进制数字10,下同),则模拟器142需要将10h写入系统管理内存中架构寄存器ecx对应的存储空间。如果运算结果为新增架构寄存器的值变为了20h,则模拟器142需要将20h写入系统管理内存中模拟新增架构寄存器所用的存储空间。模拟器142还将保存在系统管理内存中的上述接收指令的指令指针的值更新为:eip length,以使处理器200的指令指针指向下一条要执行的指令,其中,eip为指令指针更新前的值,length为上述接收指令的长度。系统管理内存中的上述接收指令的指令指针为架构寄存器eip对应的存储空间。退出系统管理模式时,系统管理内存中架构寄存器对应的存储空间中的值会被写入对应的架构寄存器260中,以将新增指令的模拟执行结果发送给应用程序130或操作系统120,后文将对此进行详述。[0111]表4-1[0112]异常标识异常编号第一数值…[0113]当模拟执行失败时,表示模拟执行时出现了异常。模拟器142将系统管理内存中的异常向量表的异常标识字段设置为第二数值(如下面的表4-2所示),并将模拟执行结果的详情字段中存储的异常编号写入异常向量表的异常编号字段。根据异常编号可以判断异常是否为陷阱(trap),当上述异常为陷阱时,模拟器142将保存在系统管理内存中的上述接收指令的指令指针的值更新为:eip length,以将处理器200的指令指针指向下一条要执行的指令集架构指令,其中,eip为上述接收指令的指令指针更新前的值,length为保存在系统管理内存中的上述接收指令的长度。[0114]表4-2[0115]异常标识异常编号第二数值异常编号[0116]然后,模拟器142执行步骤s635。在步骤s635中,模拟器142执行退出系统管理模式指令(resumefromsystemmanagementmode,rsm)。执行退出系统管理模式指令后,处理器200将执行如图1所示的系统管理模式出口1144的微码处理程序,后文将结合图9a~9b对其进行详细说明。[0117]图7是显示根据本发明第一实施例所述的转换程序的处理流程图。图7为如图1所示的转换程序145的处理流程图。请参照图2与图7,如图7所示,转换程序145获得上述接收指令的操作码(s705)。然后,转换程序145根据上述操作码判断上述接收指令是否为新增指令(s710)。当上述接收指令为新增指令时,转换程序145将上述接收指令转换为至少一个旧指令(s720),并生成一转换结果(s725)。详细说明如下:转换程序145先执行步骤s705。[0118]在步骤s705中,转换程序145根据上述接收指令的信息,获得上述接收指令的操作码。需要注意的是,由于此时还没有对上述接收指令进行译码,所以上述接收指令的信息不包含前缀、转义码及操作码等译码信息。根据前文对图4的步骤s415的描述可知,在一实施例中,上述接收指令的信息只包含上述接收指令的指令指针;在另一实施例中,上述接收指令的信息包含上述接收指令的指令指针和上述接收指令的机器码。转换程序145执行图7所示的处理流程时,可分为如下三种情形:[0119]第一种情形:当上述接收指令的信息只包含上述接收指令的指令指针时,转换程序145对上述接收指令进行译码时,根据上述接收指令的指令指针,每次读取并处理1个字节的机器码,直到译码完成;[0120]第二种情形:当上述接收指令的信息只包含上述接收指令的指令指针时,转换程序145先根据上述接收指令的指令指针读取完上述接收指令的机器码,然后再对读取到的机器码进行译码;[0121]第三种情形:当上述接收指令的信息包含上述接收指令的指令指针和上述接收指令的机器码时,转换程序145直接对上述接收指令的信息中的机器码进行译码;[0122]下面先描述在第一种情形下,转换程序145执行图7的处理流程的过程。转换程序145先执行步骤s705。[0123]在步骤s705中,转换程序145获得上述接收指令的操作码(opcode)。具体而言,转换程序145根据上述接收指令的信息获得上述接收指令的操作码。如前所述(图6的步骤s605),上述接收指令的信息是由模拟器142从系统管理内存中读取到的。上述接收指令的信息中只包含上述接收指令的指令指针,转换程序145是根据上述接收指令的指令指针获得上述接收指令的操作码的。详细来说,转换程序145根据上述接收指令的指令指针先从内存(即系统内存,systemmemory)读取上述接收指令的机器码的第1个字节,然后根据读取到的字节(即前1个字节)判断上述接收指令的操作码。如果根据上述机器码的第1个字节不能判断出上述接收指令的操作码,就再读取上述机器码的第2个字节,然后根据读取到的字节(即前2个字节)判断上述接收指令的操作码。依此类推,直到判断出上述接收指令的操作码为止。值得注意的是,如果上述接收指令包含前缀(prefix)和/或转义码(escape),转换程序145会先获取上述接收指令的前缀和/或转义码,然后再获取其操作码。在一实施例中,转换程序145通过如前所述的物理内存直接访问接口,根据上述接收指令的指令指针从内存读取机器码的。获得上述接收指令的操作码之后,转换程序145执行步骤s710。[0124]接着,在步骤s710中,转换程序145判断上述接收指令是否为新增指令。具体而言,转换程序145根据上述接收指令的操作码判断上述接收指令是否为新增指令。举例来说,可以将处理器200所支持的新增指令的操作码存放到一个查找表(lookuptable)中。转换程序145可以查看上述操作码是否存放在上述查找表中,如果存放在上述查找表中,则表示上述接收指令为新增指令,判断结果为“是”;否则,判断结果为“否”。在一实施例中,上述查找表存放在系统管理内存中。在一实施例中,转换程序145同时根据上述接收指令的转义码和操作码判断上述接收指令是否为新增指令。[0125]当上述接收指令不是新增指令(步骤s710判断结果为“否”)时,表示上述接收指令为无法辨识指令,转换程序145执行步骤s725,生成如下表2-1所示的转换结果。如下表2-1所示,转换结果的结果字段值为第二数值,表示转换失败;转换结果的内容字段为未知指令异常的异常编号#ud(值为6)。[0126]表2-1[0127]结果内容第二数值#ud[0128]当上述接收指令为新增指令时(步骤s710的判断结果为“是”),转换程序145执行步骤s712。在步骤s712中,转换程序145判断是否存在译码异常。具体而言,如前所述(图6的步骤s605),模拟程序142从系统管理内存中读取到了处理器200执行上述接收指令当时的运行环境信息,其中,上述运行环境信息包含处理器200的运行模式。转换程序145判断上述接收指令是否可以在上述运行环境下执行。举例来说,当上述运行模式为实模式时,如果上述接收指令不能运行在实模式下,则步骤s712的判断结果就为“是”;如果上述接收指令可以运行在实模式下,则步骤s712的判断结果就为“否”。[0129]在一实施例中,新增指令的操作码及其支持的运行环境被存放到一个查找表中。转换程序145可以根据上述接收指令的操作码,通过上述查找表查到上述接收指令可以在哪些运行环境下运行。在另一实施例中,上述查找表被存放在系统管理内存中。[0130]当转换程序145判断上述接收指令存在译码异常时(步骤s712的判断结果为“是”),执行步骤s725,生成如下表2-2所示的转换结果。如下表2-2所示,转换结果的结果字段值为第二数值,表示转换失败;转换结果的内容字段为未知指令异常的异常编号#ud(值为6)。[0131]表2-2[0132]结果内容第二数值#ud[0133]当转换程序145判断上述接收指令不存在译码异常时(步骤s712的判断结果为“否”),执行步骤s715。在步骤s715中,转换程序145获得上述接收指令的其它译码信息。具体而言,转换程序145继续一个字节一个字节地从内存读取上述接收指令的机器码,边读取边译码,直到译码出上述接收指令的其它译码信息,并计算出上述接收指令的长度,其中,上述其它译码信息包含操作数模式(modr/m)、源操作数和目的操作数,等等。本领域技术人员皆知,只有完成对上述接收指令的译码后,才能计算出上述接收指令的长度。然后,转换程序145执行步骤s720。[0134]在步骤s720中,转换程序145将上述接收指令转换为至少一个旧指令。具体而言,转换程序145可以通过查表的方式,将上述接收指令转换为至少一个旧指令。举例来说,可以先将上述接收指令对应的至少一个旧指令存放在一查找表中。然后,转换程序145根据上述接收指令的操作码,从上述查找表中获取上述至少一个旧指令。在一实施例中,当上述接收指令包含转义码时,转换程序145根据上述接收指令的转义码和操作码,从上述查找表中获取上述至少一个旧指令。在另一实施例中,转换程序145根据上述接收指令的转义码、操作码和操作数模式,从上述查找表中获取上述至少一个旧指令。[0135]值得注意的是,由于从上述查找表中获取到的上述至少一个旧指令中没有包含上述接收指令的源操作数和/或目的操作数等其它译码信息,所以需要将其它译码信息写入上述至少一个旧指令中,以使其可以模拟上述接收指令的执行。举例来说,转换程序145将上述接收指令的源操作数和/或目的操作数的具体值,写入上述至少一个旧指令中对应的位置。然后,处理器200就可以通过执行上述至少一个旧指令来模拟新增指令的执行了。在一实施例中,转换程序145是根据上述接收指令的前缀,将其它译码信息写入上述至少一个旧指令中的。[0136]在一实施例中,上述查找表被存放在基本输入输出系统(bios)中。本领域技术人员皆知,执行新增指令的系统100开机启动时,会执行上述基本输入输出系统。上述基本输入输出系统中包含对系统管理模式进行初始化的代码,当系统100执行到上述对系统管理模式进行初始化的代码时,会将上述查找表载入系统管理内存。然后,转换程序145便能根据上述接收指令的操作码,从上述查找表中获取上述至少一个旧指令。在另一实施例中,上述查找表被存放在私有只读存储器中。所以,在这2个实施例中,转换程序145是通过有硬件支持的查找表将接收指令转换为至少一个旧指令的。[0137]在另一实施例中,转换程序145将上述至少一个旧指令存入一内存或快取(cache)中。当处理器200执行另一指令时,如果上述另一指令为新增指令,则转换程序145判断上述接收指令与上述另一指令是否为同一指令。如果上述接收指令与上述另一指令为同一指令,则转换程序145会直接从上述内存或上述快取中获取上述至少一个旧指令。[0138]然后,转换程序145执行步骤s725,生成如下表2-3所示的转换结果。如下表2-3所示,转换结果的结果字段值为第一数值,表示转换成功;转换结果的内容字段为上述接收指令的长度和上述至少一个旧指令。[0139]表2-3[0140]结果内容第一数值接收指令的长度和至少一个旧指令[0141]下面描述在第二种情形下,转换程序145执行图7的处理流程的过程。在第二种情形下,转换程序145执行步骤s710、s712、s720以及s725的过程与在第一种情形下相同,此处就不赘述了。下面描述步骤s705和s715。[0142]与第一种情形不同的是,在第二种情形下,在步骤s705中,转换程序145先根据上述接收指令的指令指针从内存中读取到完整的上述接收指令的机器码,然后再对读取到的上述机器码进行译码处理,以获得上述接收指令的操作码。并且,在步骤s715中,转换程序145也是对在步骤s705中读取到的机器码进行译码,以获得上述接收指令的其它译码信息。在第二种情形下的其它处理都与第一种情形下相同,此处就不赘述了。[0143]值得注意的是,转换程序145根据上述接收指令的指令指针读取上述机器码时,由于还不知道上述接收指令的长度,所以需要读取足够长的上述机器码。举例来说,如果处理器200所能处理的新增指令中最长的新增指令的长度为15字节,那在步骤s705中,就需要读取至少15字节长的上述机器码。[0144]下面描述在第三种情形下,转换程序145执行图7的处理流程的过程。在第三种情形下,转换程序145执行步骤s710、s712、s715、s720以及s725的过程与在第二种情形下相同,此处就不赘述了。下面描述步骤s705。[0145]与第二种情形不同的是,在第三种情形下,在步骤s705中,转换程序145直接对上述接收指令的信息中的机器码进行译码处理,以获得上述接收指令的操作码。在第三种情形下的其它处理都与第二种情形下相同,此处就不赘述了。[0146]图8是显示根据本发明第一实施例所述的在系统管理模式下处理未知指令的例子。图8是以伪代码(pseudocode)的形式,展示如何实现如图6和图7所示的处理未知指令的处理流程,是模拟器的一个具体实现。[0147]如图8所示,第1-25行为实现模拟器的主函数simulator_start包含的代码。第27-36行为实现译码函数check_decode_excep包含的代码。第38-47行为实现新增指令功能的模拟函数unsupport_x_handle包含的代码,其中包含前文所述的与接收指令对应的至少一个旧指令。下面先描述主函数simulator_start。[0148]在主函数simulator_start中,先执行第3行代码。第3行代码完成图6的步骤s605的功能,处理器200建立模拟运行环境。在第3行代码中,处理器200通过函数setup_simulator_env来建立模拟运行环境。执行完第3行代码后,处理器200就把从系统管理内存读取到的模拟标识、接收指令的信息、接收指令的运行环境信息以及架构寄存器的信息保存到变量env中了。举例来说,在第4行代码中,通过env.emulation_flag访问的是模拟标识的值。第4行代码完成图6的步骤s610的功能,处理器200判断模拟标识是否为第一数值。如果第4行代码的判断结果为模拟标识不是第一数值,则执行第5行代码。第5行代码完成图6的步骤s645的功能,处理器200执行系统管理模式的正常处理流程。在第5行代码中,处理器200通过函数exit_to_normal_smm来执行进入系统管理模式的正常处理流程。如果第4行代码的判断结果为模拟标识是第一数值,则执行第8行代码,定义变量inst_emu,以作为第9行代码中的译码函数check_decode_excep的传出参数(后文将描述)。然后执行第9行代码。[0149]第9-15行代码完成图6的步骤s615的功能,处理器200通过转换程序转换上述接收指令,并生成一译码结果。具体来说,处理器200先执行第9行代码,通过译码函数check_decode_excep获得上述接收指令的操作码等译码信息,其中,上述译码信息被保存在传出参数inst_emu中。然后,处理器200执行第10行代码,判断译码是否成功。在第10行的代码中,处理器200根据译码结果decode_excep判断是否译码成功。如果译码失败,则表示转换失败,处理器200执行第11行的代码。第11行代码完成图6的步骤s630的功能,处理器200将转换失败的模拟执行结果写入系统管理内存。在第11行代码中,处理器200通过函数set_exception将转换失败的模拟执行结果写入系统管理内存。执行完第11行的代码后,执行第12行的代码,跳转到第23行的代码。在第12行代码中,处理器200通过指令goto跳转到标号out所在的位置(即第23行)。然后开始从第23行继续执行。由于第23行只有一个标号out,没有需要执行的代码,处理器200执行第24行的代码。第24行的代码完成图6的步骤s635的功能,处理器200执行退出系统管理模式指令。在第24行代码中,处理器200通过函数execute_rsm执行退出系统管理模式的指令。随后,处理器200将执行如图1所示的系统管理模式出口1144的微码。如果第10行代码的判断结果为译码成功,则执行第15行的代码。第15行代码完成图7的步骤s720的功能,处理器200根据接收指令的信息将上述接收指令转换为至少一个旧指令。如图8所示,在第15行代码中,是通过使用上述接收指令的操作码opcode,从表op_mapping中查找到上述至少一个旧指令的。以指针routine表示上述至少一个旧指令,routine的值为unsupport_x_handle函数的地址。然后,执行第16行的代码。[0150]第16行代码完成图6的步骤s625的功能,处理器200执行至少一个旧指令。执行routine时,处理器200实际执行的是模拟函数unsupport_x_handle(后文将详述)。执行完routine后,返回一值runtime_excep。然后,执行第18~19行的代码。第18~19行代码完成图6的步骤s630的功能,处理器200判断是否存在运行时异常。如果存在运行时异常,处理器200把出现运行时异常的模拟执行结果写入系统管理内存。在第18行代码中,处理器200根据返回值runtime_excep的值判断是否存在运行时异常。如果存在运行时异常,则执行第19行的代码。在第19行代码中,处理器200通过函数set_exception将上述运行时异常的模拟执行结果存入系统管理内存。然后,处理器200执行第20行的代码,通过goto指令跳转到第23行。如前所述,处理器200接下来会执行第24行的代码。第24行代码的功能前面已经描述,此处就不赘述了。[0151]下面描述译码函数check_decode_excep。[0152]在译码函数check_decode_excep中,先执行第29-30行代码,获得上述接收指令的操作码(图7的步骤s705)。在第29行中,处理器200通过函数read_instruction读取上述接收指令的机器码machine_code。此处是根据上述接收指令的指令指针ip从内存读取code_len字节长度的机器码machine_code(即前面讲解图7时所说的第二种情形),code_len的值可以是15。在第30行中,处理器200通过函数decode_opcode对上述机器码machine_code进行译码,得到上述接收指令的操作码opcode。在第31行中,处理器200通过函数is_emulate_op根据上述操作码opcode判断上述接收指令是否为新增指令(图7的步骤s710)。如果上述接收指令不是新增指令,处理器200执行第32行的代码,通过return指令向主函数simulator_start返回译码异常信息。如果上述接收指令是新增指令,处理器200先执行第33行代码,将上述操作码opcode存入传出参数inst_emu中;然后执行第34行的代码,获得上述接收指令的其它译码信息(图7的步骤s715),并将得到的其他译码信息存入传出参数inst_emu中。最后,处理器200执行第35行的代码,通过return指令向主函数simulator_start返回译码成功信息。主函数simulator_start可以通过传出参数inst_emu获得上述接收指令的操作码opcode和其它译码信息operands。[0153]下面描述模拟函数unsupport_x_handle。[0154]在模拟函数unsupport_x_handle中,先执行第40-41行代码。第40-41行代码完成读取操作数的值的操作,读取到的操作数的值存放在数组op中。在第41行中,处理器是通过函数read_op完成读取操作数的操作的。具体来说,read_op函数是从前文所述的env变量中获取操作数的值的。第42行代码完成图6的步骤s625的功能,处理器200执行至少一个旧指令,即处理器200模拟执行上述接收指令。在第42行中,op表示上述接收指令的操作数,operatewithop即表示将上述接收指令的操作数的值写入上述至少一个旧指令,并执行上述至少一个旧指令。然后执行第43行代码。第43行代码完成第6图的步骤s630的功能,处理器200将模拟执行结果(包含产生运行时异常的模拟执行结果和没有产生运行时异常的模拟执行结果)写入系统管理内存。更详细地说,在第43行代码中,处理器200通过函数write_result_to_smram将模拟执行结果存入系统管理内存。第44行代码判断执行第42行时是否产生了运行时异常,如果产生了运行时异常,执行第45行代码,将异常信息发送给主函数;否则,执行第46行代码,将执行正确的信息发送给主函数。在第45、46行代码中,处理器200是通过return指令将异常信息或执行正确的信息发送给主函数simulator_start的。[0155]图9a~9b是显示根据本发明第一实施例所述的退出系统管理模式的流程图。图9a~9b为与图1所示的系统管理模式出口1144对应的微码处理程序的处理流程。请参照图2与图9,如图9a~9b所示,退出系统管理模式时,处理器200判断模拟标识是否为第一数值(s901)。如果判断结果为“是”,处理器200重置模拟标识(s904),判断模拟执行结果是否存在异常(s905)。处理器200根据模拟执行结果是否存在异常以及异常的类型,执行退出系统管理模式的操作。详细说明如下:处理器200先执行步骤s901。[0156]在步骤s901中,处理器200判断模拟标识是否为第一数值。具体而言,处理器200从系统管理内存读取模拟标识(由前述对图5的步骤s520的描述可知,模拟标识被存入了系统管理内存),然后判断读取到的上述模拟标识是否为第一数值。如果上述模拟标识不为第一数值,处理器200执行步骤s903。在步骤s903中,处理器200执行退出系统管理模式的正常处理流程。对于退出系统管理模式的正常处理流程,为本领域技术人员的通常知识,此处就不赘述了。如果上述模拟标识为第一数值,处理器200执行步骤s904。[0157]在步骤s904中,处理器200重置模拟标识。具体而言,处理器200将微体系结构寄存器220和系统管理内存中的模拟标识设置为第二数值。重置模拟标识后,处理器200在后续的执行过程中,当发生正常的系统管理中断时,就会执行系统管理模式的正常处理流程了。然后,处理器200执行步骤s905。[0158]在步骤s905中,处理器200判断模拟执行结果是否存在异常。具体而言,处理器200从系统管理内存读取如前文表4所示的异常向量表。如果异常向量表的异常标识字段的值为第一数值,则表示模拟执行结果存在异常,判断结果为“是”;如果异常向量表的异常标识字段的值为第二数值,则表示模拟执行结果不存在异常,判断结果为“否”。如果判断结果为“否”,处理器200执行步骤s907。[0159]如图9b所示,在步骤s907中,处理器200将系统管理内存中保存的模拟执行结果存入架构寄存器。如前文所述,在图6的步骤s630中,处理器200已经将上述接收指令的模拟执行结果写入了系统管理内存中架构寄存器对应的区域。在本步骤中,处理器200将系统管理内存中架构寄存器对应的区域中的值存入架构寄存器260。这样,就相当于处理器200执行完了上述接收指令。[0160]如果上述接收指令的目的操作数为新增架构寄存器,由于处理器200的架构寄存器260中不包含新增架构寄存器,处理器200不会把系统管理内存中模拟新增架构寄存器的区域中的值存入架构寄存器260。如前所述,当处理器200在模拟执行另一新增指令,并且上述另一新增指令的操作数也为上述新增架构寄存器时,处理器200就可以直接使用保存在系统管理内存中的模拟上述新增架构寄存器的区域中的值,来模拟上述另一新增指令的执行。[0161]然后,处理器200执行步骤s909。在步骤s909中,处理器200启用中断。举例来说,处理器200设置if标识以启用可屏蔽中断,设置tf标识以启用单步中断,设置dr7以启用断点中断。然后,处理器200执行步骤s911。[0162]在步骤s911中,处理器200发出退出系统管理模式通知(deassert#smmact),以通知芯片组处理器200退出了系统管理模式。然后,处理器200执行步骤s913,退出系统管理模式。[0163]如图9a所示,当在步骤s905中,处理器200判断模拟执行结果存在异常时,执行步骤s915。[0164]在步骤s915中,处理器200判断异常类型是否为陷阱(trap)。具体而言,处理器200根据在步骤s905中从系统管理内存中读到的异常向量表中的异常标识及异常编号,判断模拟执行结果中的异常是否为陷阱。举例来说,当异常标识为第一数值,异常编号为3时(表4中内容如下表4-2所示),表示是溢出(overflow)异常。溢出异常的类型为陷阱,所以判断结果为“是”。当异常标识为第一数值,异常编号为0时(表4中内容如下表4-3所示),表示是除法错误异常。除法错误异常为错误(fault),不是陷阱,所以判断结果为“否”。[0165]表4-2[0166]异常标识异常编号第一数值3[0167]表4-3[0168]异常标识异常编号第一数值0[0169]当步骤s915的判断结果为“否”时,处理器200执行步骤s917、s919、s921以及s723。其中,步骤s917、步骤s919和步骤s921分别与步骤s909、步骤s911和步骤s913相同,此处就不赘述了。下面描述步骤s923。[0170]在步骤s923中,处理器200执行异常的微码处理程序。具体来说,处理器200根据系统管理内存中存储的异常向量表中的异常标识,判断是否产生了异常。如果产生了异常,处理器200根据上述异常向量表中存储的异常编号,执行上述异常的微码处理程序。即执行与上述异常编号对应的异常的微码处理程序。举例来说,当系统管理内存中存储的异常向量表中的异常标识为第一数值时,表示模拟执行结果存在异常。如果此时异常向量表中的异常编号为0,表示上述异常为除法错误,处理器200会执行除法错误的微码处理程序。[0171]在步骤s915中,当判断结果为“是”,即模拟执行结果的异常类型为陷阱时,处理器200执行图9b所示的步骤s925、s927、s929以及s933。其中,步骤s925、s927、s929分别于步骤s907、s909、s911相同,此处就不赘述了。下面描述步骤s933。[0172]在步骤s933中,处理器200执行异常的微码处理程序。举例来说,当模拟执行结果存在异常,并且异常为溢出异常时,处理器200执行溢出异常的微码处理程序。在图9a、9b所示的通过系统管理中断出口1144退出系统管理模式的实际操作上,本领域技术人员可在呼叫退出系统管理模式的指令(resumefromsystemmanagementmode,rsm)后,在退出系统管理模式对应的微码中加入一些将模拟执行结果从系统管理内存存入架构寄存器的微码,以将模拟执行结果传给应用程序130或操作系统120。由于这些微码会依处理器版本而不同,本领域技术人可依据实际状况撰写对应的微码。[0173]值得注意的是,在第一实施例中,微体系结构寄存器220是处理器200中本来就存在的寄存器。因此,在本发明的第一实施例中,在不对处理器的硬件结构进行修改的情况下,就可以在前代处理器上执行新增指令。所以,在本发明的第一实施例中,可以通过升级微码的方式,使得已经生产的处理器获得执行新增指令的功能。[0174][第二实施例][0175]图10是显示根据本发明第二实施例所述的执行新增指令的系统1000的示意图。与图1所示的第一实施例不同的是,图10所示的执行新增指令的系统1000中的转换程序145在与新增指令相同的执行模式下,直接运行于处理器之上。另外,由于第二实施例中的转换程序145是运行在与新增指令相同的执行模式下的,所以处理器执行转换程序145时不需要切换运行模式。下面详述第二实施例与第一实施例的不同之处。[0176]如图10所示,当指令118为未知指令132时,处理器110执行处理未知指令异常的微码处理程序。在处理未知指令异常的微码处理程序中,直接调用转换程序145(如图10中的实线箭头2所示)。转换程序145将判断未知指令132是否为新增指令。如果未知指令132为新增指令,转换程序145将其转换为至少一个旧指令,并将上述至少一个旧指令发送给处理未知指令异常的微码处理程序(如图10中的实线箭头6所示)。处理未知指令异常的微码处理程序接收上述至少一个旧指令,并通过呼叫指令(call)或跳转指令(jump)使处理器110执行上述至少一个旧指令。[0177]图11是依据本发明第二实施例所述的处理器的结构图。图11中和图2中相同名称的元件的功能相同,在此不再赘述。[0178]需注意的是,如图11所示,位于虚线左边的处理器1100为图10所示的处理器110的结构图,位于虚线右边的转换程序145运行于处于与新增指令相同的执行模式下的处理器1100之上(即,处理器不需要切换执行模式)。转换程序145可储存于处理器1100的处理核心内的中断预处理单元112中。在另一实施例中,转换程序145可储存于处理器1100的一非核心(uncore)中。因而,处理器1100的所有处理核心可以共享转换程序145。[0179]图12是显示根据本发明第二实施例所述的执行新增指令的流程图。图12所示的处理流程,可由图11的处理器1100执行。如图12所示,处理器1100接收一指令(s1205),当上述接收指令为未知指令时,发出一未知指令异常(s1210)。响应于上述未知指令异常,通过一转换程序判断上述接收指令是否为新增指令(s1215)。当上述接收指令为新增指令时,通过上述转换程序将上述接收指令转换为至少一个旧指令(s1220)。最后,处理器1100在与上述接收指令相同的执行模式下,执行上述至少一个旧指令(s1225)。图12的步骤s1205、s1210与图3的步骤s305、s310相同,此处就不赘述了。图3的步骤s320和s325与图12的步骤s1220和s1225的不同之处是,图3的步骤s320和s325运行在系统管理模式下,而图12的步骤s1220和s1225则是运行在与上述接收指令相同的执行模式下。图3的步骤s320和s325与图12的步骤s1220和s1225完成的功能是相同的,此处也不赘述了。下面只描述步骤s1215。[0180]在步骤s1215中,响应于上述未知指令异常,处理器1100通过一转换程序判断上述接收指令是否为新增指令。具体而言,指令提交单元245发出未知指令异常后,处理器1100执行处理未知指令异常的微码处理程序。在处理未知指令异常的微码处理程序中,处理器1100将上述接收指令的信息和运行环境信息发送给转换程序145。转换程序145根据上述接收指令的信息判断上述接收指令是否为新增指令。至于转换程序145是如何判断上述接收指令是否为新增指令的,已经在第一实施例中做了详细描述,此处就不赘述了。[0181]图13是显示根据本发明第二实施例所述的处理接收指令的流程图。图13的步骤s1305、s1310、s1325与图4的步骤s405、s410、s435相同,此处就不赘述了。下面描述步骤s1320。[0182]在步骤s1320中,图11的处理器1100处理上述接收指令。具体而言,当上述接收指令为未知指令时(步骤s1310的判断结果为“是”),处理器1100执行处理未知指令异常的微码处理程序。在处理未知指令异常的微码处理程序中,处理器1100通过转换程序145处理上述未知指令(后文将结合图14详述)。[0183]图14是显示根据本发明第二实施例所述的在处理未知指令异常的微码处理程序中处理接收指令的流程图。如图14所示,图11的处理器1100获取接收指令的信息(s1405),通过转换程序145转换上述接收指令,并生成转换结果(s1410)。如果转换成功(步骤s1415的判断结果为“是”),处理器1100从上述转换结果中获取至少一个旧指令,并执行上述至少一个旧指令(s1420)。详细说明如下:处理器1100先执行步骤s1405。[0184]在步骤s1405中,在未知指令异常的微码处理程序中获取接收指令的信息。上述接收指令的信息包含上述接收指令的指令指针。值得注意的是,由于此时还没有对上述接收指令进行译码,所以上述接收指令的信息不包含前缀、转义码及操作码等译码信息。执行未知指令异常的微码处理程序时,由于不需要进行模式转换,处理器1100的运行环境不会发生变化。所以,在未知指令异常的微码处理程序中,可以直接获取处理器1100的运行环境信息,这个运行环境信息就是上述接收指令的运行环境信息。然后,执行步骤s1410。[0185]在步骤s1410中,处理器1100通过转换程序145转换上述接收指令,并生成转换结果。至于如何通过转换程序145转换上述接收指令,与第一实施例中的处理过程相同,此处就不赘述了。步骤s1415与图6的步骤s620相同,此处就不赘述了。下面描述步骤s1420和s1425。[0186]当转换程序145转换成功时(步骤s1415中的“是”),处理器1100执行步骤s1420。在步骤s1420中,处理器1100从上述转换结果中获取至少一个旧指令,并执行上述至少一个旧指令。此外,处理器1100还可以从上述转换结果中获取上述接收指令的长度。在一实施例中,上述接收指令的下一条指令为另一指令。上述至少一个旧指令中的最后一条指令为跳转指令(jump)或呼叫指令(call),处理器1100通过上述跳转指令或上述呼叫指令跳转到上述另一指令。上述另一指令的指令指针为:eip length,其中,eip为上述接收指令的指令指针,length为上述接收指令的长度。[0187]当转换程序145转换失败时(步骤s1415中的“否”),处理器1100执行步骤s1425。在步骤s1425中,处理器1100处理异常。具体而言,当转换程序145转换上述接收指令时出现任何异常,都会导致转换失败。在中断预处理单元112的处理未知指令异常的微码处理程序中,可以从转换结果的内容字段中获得一异常编号。然后,处理未知指令异常的微码处理程序发出对应于上述异常编号的异常。响应于上述对应于上述异常编号的异常,处理器1100执行对应的微码处理程序,以处理上述异常。[0188]第二实施例的转换程序的处理流程与第一实施例中图7转换程序的处理流程相同,在此不再赘述。[0189]综上所述,与第一实施例不同的是,在本实施例中,当处理器1100执行到一未知指令时,处理器1100直接在与未知指令相同的执行模式下,执行转换程序145。转换程序145判断上述未知指令是否为新增指令。当上述未知指令为新增指令时,转换程序145将新增指令转换为至少一个旧指令。然后,处理器1100在与上述未知指令相同的执行模式下,执行上述至少一个旧指令。与第一实施例相比,在本实施例中,处理器不需要切换执行模式,因此模拟执行新增指令的效率更高。[0190][第三实施例][0191]图15a~15b是显示根据本发明第三实施例所述的执行新增指令的系统1500的示意图。与图1所示的第一实施例和图10所示的第二实施例不同的是,在第三实施例中,执行新增指令的系统1500中的转换程序145由操作系统120中的内核驱动程序150所运行。而转换程序145可位于内核驱动程序150的内部(如图15a所示)或是外部(如图15b所示)。请参照图11和图15a~15b,当处理器1100判断指令118为未知指令132后,会发出一未知指令异常。响应于上述未知指令异常,处理器1100执行未知指令异常的微码处理程序。在未知指令异常的微码处理程序中,处理器1100会调用内核驱动程序150,同时会把未知指令132的信息和运行环境信息发送给内核驱动程序150。内核驱动程序150通过转换程序145处理上述接收指令。[0192]在一实施例中,在未知指令异常的微码处理程序中,处理器1100通过自行定义的中断服务程序(中断服务程序的开发者,可以通过自行定义的中断向量#ne(non-supportinstructionemulator)调用自行定义的中断处理程序,其中,自行定义的中断向量#ne在中断向量表的保留编号中)去调用内核驱动程序150。值得注意的是,中断服务程序调用内核驱动程序150时必须将未知指令132的信息(包含指令指针等)和运行环境信息传给内核驱动程序150、或是将未知指令132的信息和运行环境信息的储存地址通知内核驱动程序150。再者,内核驱动程序150所使用的中断服务程序(自行定义的中断向量#ne对应的中断服务程序),可以是储存在中断预处理单元112中的微码并由中断预处理单元112调用(中断预处理单元112可用状态机或组合逻辑电路构筑)。在一实施例中,内核驱动程序150通过转换程序145处理未知指令132的方式,可以经由系统调用(systemcall)来呼叫操作系统120执行内核驱动程序150,例如把内核驱动程序150作为一回调函数(callbackfunction),未知指令132的信息和运行环境信息则被当成参数传给内核驱动程序150。如果未知指令132为新增指令,内核驱动程序150通过转换程序145处理完未知指令132后将至少一个旧指令回传处理器1100。此外,抑或是通过内部中断(internalinterrupt)或是陷阱(trap)来调用内核驱动程序150,例如处理器1100的设计者自行定义一中断向量#ne,并藉此进入操作系统的核心(kernel)去呼叫内核驱动程序150,熟习本领域技术人应知这部分的技术细节故不再赘述。在一实施例中,在未知指令异常的微码处理程序中发送未知指令132的信息和运行环境信息的过程为:将未知指令132的信息和运行环境信息压入(push)堆栈(stack)中,然后,内核驱动程序150从堆栈中获取未知指令132的信息和运行环境信息。[0193]在另一实施例中,可将操作系统中处理未知指令异常的中断服务程序修改为直接调用内核驱动程序150,以实现对未知指令132的处理。在修改后的处理未知指令异常的中断服务程序中,可以先读取未知指令132的信息和运行环境信息,并将读取到的未知指令132的信息和运行环境信息传送给内核驱动程序150。在本实施例中,不需要对处理器的硬件和/或微码进行修改,只需修改操作系统中处理未知指令异常的中断服务程序就可以实现如前文所述的对未知指令的处理,因而实现起来相当方便。在实际操作上,本领域技术人员可以对处理未知指令异常的中断服务程序进行修改,以添加读取未知指令132的信息和运行环境信息,以及调用内核驱动程序150的功能。由于处理未知指令异常的中断服务程序会依操作系统和/或处理器版本而不同,本领域技术人员可依实际情况撰写对应的代码。[0194]图16是依据本发明第三实施例所述的处理接收指令的流程图。图16的步骤s1605、s1610、s1625与第二实施例的图13的步骤s1305、s1310、s1325相同,此处就不赘述了。下面描述步骤s1620。[0195]请参照图11、图15a~15b和图16,图16所示的处理流程,可由图11的处理器1100执行。在步骤s1620中,处理器1100处理上述接收指令。具体而言,当上述接收指令为未知指令时,在处理未知指令异常的微码处理程序中,处理器1100是通过操作系统120的内核驱动程序150,调用转换程序145对上述接收指令进行处理的。需要说明的是,相较于本实施例,在上述第二实施例的图13的步骤s1320中,当上述接收指令为未知指令时,在处理未知指令异常的微码处理程序中,处理器1100是直接通过转换程序145对上述接收指令进行处理的。[0196]在一实施例中,转换程序145为上述操作系统120的一驱动程序或应用程序。第三实施例中的其它处理流程均与第二实施例相同,此处就不赘述了。[0197]综上所述,与第二实施例不同的是,在本实施例(第三实施例)中,当处理器1100执行到一未知指令时,处理未知指令异常的微码处理程序执行操作系统120的内核驱动程序150,以接续处理可转换的新增指令。与第二实施例相比,在本实施例中,使用操作系统的内核驱动程序通过转换程序转换新增指令,与更新处理器的硬件和/或处理器中的微码相比,更新内核驱动程序和转换程序更加方便、快捷,从而提高了开发效率。[0198][第四实施例][0199]图17是显示根据本发明第四实施例所述的执行新增指令的系统1700的示意图。与第三实施例相同,在本实施例(第四实施例)中,执行新增指令的系统1700中的转换程序145也由操作系统120中的内核驱动程序150所运行。不同之处是,在本实施例中,转换程序145运行于一专用处理核心190上。内核驱动程序150通过轮询(polling)或门铃(doorbell)机制将未知指令132的信息和运行环境信息发送给转换程序145。转换程序145也需要通过轮询或门铃机制,把转换结果发送给内核驱动程序150。下面将分别描述具体是如何通过轮询或门铃机制在内核驱动程序150和转换程序145之间传输数据的。[0200]下面先描述轮询机制。请参照图11与图17,在一实施例中,处理器1100的设计者可在处理器1100的非核心(uncore)中设置一传输寄存器(未绘示),用于存放未知指令132的信息、运行环境信息、一传输信息标识和一传输结果标识(皆未绘示于图17中),其中,传输信息标识和传输结果标识的默认值都为第二数值。内核驱动程序150将未知指令132的信息和运行环境信息存入上述传输寄存器,并将值为第一数值的传输信息标识存入上述传输寄存器。然后,内核驱动程序150每隔固定的时间(比如每隔100毫秒)就去读取传输寄存器中的传输结果标识,以等待接收转换结果。如果读取到传输结果标识为第一数值,表示转换程序145已经生成了转换结果,内核驱动程序150将从传输寄存器读取转换结果。另外,运行于专用处理核心190上的转换程序145被设置为,当空闲时,每隔固定的时间(比如每隔100毫秒)就去查看传输寄存器中的传输信息标识是否为第一数值。如果传输寄存器中的传输信息标识为第一数值,转换程序145从上述传输寄存器读取未知指令132的信息和运行环境信息,然后将传输寄存器中的传输信息标识设置为第二数值。然后,转换程序145按前文所述的方法对未知指令132进行转换处理,生成转换结果。然后,转换程序145将上述转换结果存入传输寄存器中,并将值为第一数值的传输结果标识存入传输寄存器。如前所述,由于传输结果标识为第一数值,内核驱动程序150会从传输寄存器读取转换结果,并将传输寄存器中的传输结果标识设置为第二数值。至此,内核驱动程序150和转换程序145之间就完成了一次数据传输。在另一实施例中,于多核心处理器架构下,还需要把处理核心的编号存入传输寄存器中或者在传输寄存器中为每个处理核心分配专用的存储空间,以使得运行于每个处理核心上的内核驱动程序150都可以与转换程序145进行数据传输。[0201]下面描述门铃机制。同样参照图11与图17,在一实施例中,处理器1100的设计者可在处理器1100的非核心中设置一传输寄存器(未绘示),用于存放未知指令132的信息和运行环境信息(皆未绘示于图17中)。内核驱动程序150将未知指令132的信息和运行环境信息存入上述传输寄存器之后,通过中断的方式通知运行于专用处理器190上的转换程序145。响应于上述中断,转换程序145从上述传输寄存器读取未知指令132的信息和运行环境信息,并生成转换结果。然后,转换程序145将转换结果存入传输寄存器,并通过中断的方式通知内核驱动程序150。响应于上述中断,内核驱动程序150从传输寄存器读取转换结果。至此,内核驱动程序150和转换程序145之间就完成了一次数据传输。至于如何设置中断,比如分别为内核驱动程序150和转换程序145自行定义中断服务程序、并自行定义各自对应的中断向量号,前文已经做了描述,此处就不赘述了。在另一实施例中,也可以单独为处理器1100和/或专用处理器190添加一硬件中断信号线(pin),内核驱动程序150和/或转换程序145可通过上述硬件中断信号线触发中断,以完成数据传输。[0202]本实施例中的其它处理流程均与第三实施例相同,此处就不赘述了。[0203]在另一实施例中,前述第一实施例、第二实施例以及第四实施例中所描述的转换程序145的功能,可以实现于一硬件电路中。[0204]由上可知,与第三实施例相同,在本实施例中,也是通过操作系统120的内核驱动程序150实现对新增指令的转换的。与第三实施例不同的是,在本实施例中,转换程序145运行于专用处理核心190之上。在本实施例中,由于转换程序145运行于专用处理核心190之上,因而执行速度较快;另外,由于不需要在每个处理核心中都运行一个转换程序145,从而减轻了处理器的其它处理核心的工作负担。[0205]图18是显示根据本发明一实施例所述的执行新增指令的流程图。请同时参照图11、17、18,由上述对第三实施例和本实施例的描述可知,处理器1100接收一指令(s1805),当上述接收指令为未知指令时,处理器1100通过操作系统120执行一转换程序(s1810)。在上述转换程序中,判断上述接收指令是否为新增指令(s1815),以及当上述接收指令为新增指令时,将上述接收指令转换为至少一个旧指令(s1820)。最后,处理器1100执行上述至少一个旧指令(s1825)。图18的步骤s1805、s1815、s1820、s1825已在第一实施例中做了详细描述,此处就不赘述了。下面描述步骤s1810。[0206]在步骤s1810中,当上述接收指令为未知指令时,处理器1100通过操作系统执行一转换程序。具体而言,如前对第三实施例和本实施例的描述可知,当上述接收指令为未知指令时,指令提交单元245会发出一未知指令异常。响应于上述未知指令异常,处理器1100执行未知指令异常的微码处理程序。在未知指令异常的微码处理程序中,调用操作系统的内核驱动程序150。操作系统的内核驱动程序150再调用转换程序145。[0207]图19是显示根据本发明一实施例所述的执行新增指令的流程图。请同时参照图11、17、19,由上述对第一实施例、第二实施例、第三实施例和本实施例的描述可知,处理器1100接收一指令(s1905),当上述接收指令为未知指令时,处理器1100启动一转换程序(s1910)。在上述转换程序中,判断上述接收指令是否为新增指令(s1915),以及当上述接收指令为新增指令时,将上述接收指令转换为至少一个旧指令(s1920)。最后,处理器1100通过执行上述至少一个旧指令,来模拟上述接收指令的执行(s1925)。图19的步骤s1905、s1915、s1920、s1925已在第一实施例中做了详细描述,此处就不赘述了。下面描述步骤s1910。[0208]在步骤s1910中,当上述接收指令为未知指令时,处理器1100启动一转换程序。具体而言,如前对第一实施例、第二实施例、第三实施例和本实施例的描述可知,当上述接收指令为未知指令时,指令提交单元245会发出一未知指令异常。响应于上述未知指令异常,处理器1100执行未知指令异常的微码处理程序。[0209]特别说明的是,在第一实施例中,未知指令异常的微码处理程序发出一系统管理中断(#smi)。响应于上述系统管理中断,处理器1100进入系统管理模式。在系统管理模式中,启动模拟器142,并由模拟器142启动转换程序145。在第二实施例中,未知指令异常的微码处理程序直接启动转换程序145。在第三实施例和本实施例中,未知指令异常的微码处理程序调用操作系统120的内核驱动程序150。然后操作系统120的内核驱动程序150再调用转换程序145。[0210]图20是显示根据本发明一实施例所述的转换新增指令的流程图。请同时参照图11、17、20,由上述对第一实施例、第二实施例、第三实施例和本实施例的描述可知,转换程序145接收一指令,其中上述指令为未知指令(s2005),判断上述接收指令是否为新增指令(s2010)。当上述接收指令为新增指令时,转换程序145将上述接收指令转换为至少一个旧指令(s2015)。在前文中,已经对图20的步骤s2005、s2010以及s2015做了详细描述,此处就不赘述了。[0211]对于本发明已描述的实施例,下文描述了可以实现本发明实施例的示例性操作环境。具体参考图21,图21是显示用以实现本发明实施例的示例性操作环境,一般可被视为计算装置2100。计算装置2100仅为一合适计算环境的一个示例,并不意图暗示对本发明使用或功能范围的任何限制。计算装置2100也不应被解释为具有与所示元件任一或组合相关任何的依赖性或要求。[0212]可在计算机或机器中使用指令来执行本发明,指令可为程序模块的计算机可执行指令,程序模块由计算机或其它机器,例如个人数字助理或其它可携式装置执行。一般而言,程序模块包括例程、程序、物件、元件、数据结构等,程序模块指的是执行特定任务或实现特定抽象数据类型的程序码。本发明可在各种系统配置中实现,包括可携式装置、消费者电子产品、通用计算机、更专业的计算装置等。本发明还可在分散式运算环境中实现,处理由通讯网络所连结的装置。[0213]请参考图21。计算装置2100包括直接或间接耦接以下装置的总线2110、内存2112、一或多个处理器2114、一或多个显示元件2116、输入/输出(i/o)端口2118、输入/输出(i/o)元件2120以及电源供应器2122。总线2110可为一或多个总线的元件(例如,地址总线、数据总线或其组合)。虽然图21的各个方块为简要起见以线示出,实际上,各个元件的分界并不是具体的,例如,可将显示装置的呈现元件视为i/o元件;处理器可具有内存。[0214]计算装置2100一般包括各种计算机可读取介质。计算机可读取介质可以是可被计算装置2100存取的任何可用介质,该介质同时包括易失性和非易失性介质、可移动和不可移动介质。举例但不局限于,计算机可读取介质可包括计算机储存介质和通讯介质。计算机可读取介质同时包括在用于储存像是计算机可读取指令、数据结构、程序模块或其它数据之类信息的任何方法或技术中实现的易失性和非易失性介质、可移动和不可移动介质。计算机储存介质包括但不局限于随机存取内存(randomaccessmemory,ram)、只读内存(read-onlymemory,rom)、电子抹除式可复写只读内存(electrically-erasableprogrammableread-onlymemory,eeprom)、快闪内存或其它内存技术、cd-rom、数字多功能光盘(dvd)或其它光盘储存装置、磁片、磁盘、磁片储存装置或其它磁储存装置,或可用于储存所需的信息并且可被计算装置2100存取的其它任何介质。计算机储存介质本身不包括信号。[0215]通讯介质一般包含计算机可读取指令、数据结构、程序模块或其它采用诸如载波或其他传输机制之类的模块化数据信号形式的数据,并包括任何信息传递介质。术语“模块化数据信号”是指具有一或多个特征集合或以在信号中编码信息之一方式更改的信号。举例但不局限于,通讯介质包括像是有线网络或直接有线连接的有线介质及无线介质,像是声频、射频、红外线以及其它无线介质。上述介质的组合包括在计算机可读取介质的范围内。[0216]内存2112包括以易失性和非易失性内存形式的计算机储存介质。内存可为可移动、不移动或可以为这两种的组合。示例性硬件装置包括固态内存、硬盘驱动器、光盘驱动器等。第一实施例中的系统管理内存位于内存2112中。[0217]计算装置2100包括一或多个处理器2114,其读取来自像是内存2112或i/o元件2120各实体的数据。显示元件2116向使用者或其它装置显示数据指示。示例性显示元件包括显示装置、扬声器、打印元件、振动元件等。[0218]i/o端口2118允许计算装置2100逻辑连接到包括i/o元件2120的其它装置,一些此种装置为内建装置。示例性元件包括麦克风、摇杆、游戏台、盘形卫星信号接收器、扫描器、打印机、无线装置等。i/o元件2120可提供一自然使用者接口(naturaluserinterface,nui),用于处理使用者生成的姿势、声音或其它生理输入。在一些例子中,这些输入可被传送到一合适的网络元件以便进一步处理。自然使用者接口可实现语言识别、触摸与手写笔辨识、面部识别、生物识别、在屏幕上以及邻近屏幕的姿势识别、空中手势、头部及眼部追踪以及与计算装置2100所显示相关联的触摸识别的任意组合。计算装置2100可装备有深度照相机,像是立体照相机系统、红外线照相机系统、rgb照相机系统和这些系统的组合,以侦测与识别姿势。另外,计算装置2100可以装备有侦测运动的加速度计或陀螺仪。加速度计或陀螺仪的输出可被提供给计算装置2100显示以呈现沉浸式增强现实或虚拟实境。[0219]此外,计算装置2100中的处理器2114也可执行内存2112中的程序及指令以呈现上述实施例所述的动作和步骤,或其它在说明书中描述的内容。[0220]在此所公开程序的任何具体顺序或分层的步骤纯为一举例的方式。基于设计上的偏好,必须了解到程序上的任何具体顺序或分层的步骤可在此文件所公开的范围内被重新安排。伴随的方法权利要求以一示例顺序呈现出各种步骤的元件,也因此不应被此所展示的特定顺序或阶层所限制。[0221]权利要求中用以修饰元件的“第一”、“第二”、“第三”等序数词的使用本身未暗示任何优先权、优先次序、各元件之间的先后次序、或方法所执行的步骤的次序,而仅用作标识来区分具有相同名称(具有不同序数词)的不同元件。[0222]通过本发明提供的执行新增指令的方法与执行新增指令的系统,在不对处理核心的硬件架构进行修改的情况下,就可以在前代处理器上执行新增指令。[0223]以上所述仅为本发明较佳实施例,然其并非用以限定本发明的范围,任何熟悉本项技术的人员,在不脱离本发明的精神和范围内,可在此基础上做进一步的改进和变化,因此本发明的保护范围当以本技术的权利要求书所界定的范围为准。当前第1页12当前第1页12

背景技术:

::2.处理器技术这些年来得到迅速发展。随着处理器功能的增强,后代处理器往往会在前代处理器的基础上增加新的指令。由于前代处理器无法执行后代处理器所支持的新增指令,当前代处理器执行到新增指令时,会产生未知指令异常(#ud),进而造成包含新增指令的进程被操作系统终止。从而导致包含新增指令的应用程序或操作系统无法在前代处理器上执行。3.因此,需要一种执行新增指令的方法及系统,以达到在前代处理器上执行新增指令的目的。技术实现要素:4.以下公开的内容仅为示例性的,且不意指以任何方式加以限制。除了所述说明方面、实施方式和特征之外,通过参照附图和下述具体实施方式,其他方面、实施方式和特征也将显而易见。即,以下公开的内容被提供以介绍概念、重点、益处以及本文所描述新颖且非显而易见的技术优势。所选择,非所有的,实施例将进一步详细描述如下。因此,以下公开的内容并不意旨在所要求保护主题的必要特征,也不意旨在决定所要求保护主题的范围中使用。5.因此,本发明的主要目的在于提供一种执行新增指令的方法及系统,以达到无需更改前代处理核心的硬件架构即可执行新增指令的目的。6.本发明提出一种执行新增指令的方法,包括:接收一指令,当上述接收指令为未知指令时,发出一未知指令异常。响应于上述未知指令异常,通过一转换程序:判断上述接收指令是否为新增指令;当上述接收指令为新增指令时,将上述接收指令转换为至少一个旧指令。以及,在与上述接收指令相同的执行模式下,执行上述至少一个旧指令。7.本发明提出一种执行新增指令的系统,包括:一指令译码单元(decoder),接收一指令,判断上述接收指令是否为未知指令。一指令提交单元,当上述接收指令为未知指令时,上述指令提交单元发出一未知指令异常。响应于上述未知指令异常,上述执行新增指令的系统通过一转换程序:判断上述接收指令是否为新增指令;以及当上述接收指令为新增指令时,将上述接收指令转换为至少一个旧指令。其中,上述执行新增指令的系统在与上述接收指令相同的执行模式下,执行上述至少一个旧指令。8.通过本发明提供的执行新增指令的方法与执行新增指令的系统,在不对处理核心的硬件架构进行修改的情况下,就可以在前代处理器上执行新增指令。附图说明9.图1是显示根据本发明第一实施例所述的执行新增指令的系统的示意图。10.图2是依据本发明第一实施例所述的处理器的结构图。11.图3是显示根据本发明第一实施例所述的执行新增指令的流程图。12.图4是显示根据本发明第一实施例所述的处理接收指令的流程图。13.图5是显示根据本发明第一实施例所述的进入系统管理模式的流程图。14.图6是显示根据本发明第一实施例所述的模拟器的处理流程图。15.图7是显示根据本发明第一实施例所述的转换程序的处理流程图。16.图8是显示根据本发明第一实施例所述的在系统管理模式下处理未知指令的例子。17.图9a~9b是显示根据本发明第一实施例所述的退出系统管理模式的流程图。18.图10是显示根据本发明第二实施例所述的执行新增指令的系统的示意图。19.图11是依据本发明第二实施例所述的处理器的结构图。20.图12是显示根据本发明第二实施例所述的执行新增指令的流程图。21.图13是显示根据本发明第二实施例所述的处理接收指令的流程图。22.图14是显示根据本发明第二实施例所述的在处理未知指令异常的微码中处理接收指令的流程图。23.图15a~15b是显示根据本发明第三实施例所述的执行新增指令的系统的示意图。24.图16是依据本发明第三实施例所述的处理接收指令的流程图。25.图17是显示根据本发明第四实施例所述的执行新增指令的系统的示意图。26.图18是显示根据本发明一实施例所述的执行新增指令的流程图。27.图19是显示根据本发明一实施例所述的执行新增指令的流程图。28.图20是依据本发明一实施例所述的转换新增指令的流程图。29.图21是显示用以实现本发明实施例的示例性操作环境。30.其中,附图中符号的简单说明如下:31.100:执行新增指令的系统;110:处理器;112:中断预处理单元;114:系统管理模式出/入口;1142:系统管理模式入口;1144:系统管理模式出口;120:操作系统;130:应用程序;118:指令;132:未知指令;142:模拟器;145:转换程序;200:处理器;201:指令旁路转换缓冲;202:指令快取;203:分支预测器;230:指令译码单元;204:重命名单元;205:保留站;206:执行单元;207:访存单元;220:微体系结构寄存器;240:重排缓冲区;245:指令提交单元;250:系统管理模式;260:架构寄存器;s305、s310、s315、s320、s325:步骤;s405、s410、s415、s420、s425、s430、s435:步骤;s505、s510、s515、s520、s525、s530:步骤;s605、s610、s615、s620、s625、s630、s635、s640、s645:步骤;s705、s710、s712、s715、s720、s725:步骤;s901、s904、s903、s905、s907、s909、s911、s913、s915、s917、s919、s921、s923、s925、s927、s929、s933:步骤;1000:执行新增指令的系统;1100:处理器;1110:转换程序;s1205、s1210、s1215、s1220、s1225:步骤;s1305、s1310、s1315、s1320、s1325:步骤;s1405、s1410、s1415、s1420、s1425:步骤;1500:执行新增指令的系统;150:内核驱动程序;1600:流程图;s1605、s1610、s1620、s1625:步骤;1700:执行新增指令的系统;190:专用处理核心;s1805、s1810、s1815、s1820、s1825:步骤;s1905、s1910、s1915、s1920、s1925:步骤;s2005、s2010、s2015:步骤;2100:计算装置;2110:总线;2112:内存;2114:处理器;2116:显示元件;2118:i/o端口;2120:i/o元件;2122:电源供应器。具体实施方式32.在下文中将参考附图对本发明的各方面进行更充分的描述。然而,本发明可以具体化成许多不同形式且不应解释为局限于贯穿本发明所呈现的任何特定结构或功能。相反地,提供这些方面将使得本发明周全且完整,并且本发明将给本领域技术人员充分地传达本发明的范围。基于本文所教导的内容,本领域的技术人员应意识到,无论是单独还是结合本发明的任何其它方面实现本文所公开的任何方面,本发明的范围旨在涵盖本文中所公开的任何方面。例如,可以使用本文所提出任意数量的装置或者执行方法来实现。另外,除了本文所提出本发明的多个方面之外,本发明的范围更旨在涵盖使用其它结构、功能或结构和功能来实现的装置或方法。应可理解,其可通过权利要求的一或多个元件具体化本文所公开的任何方面。33.词语“示例性”在本文中用于表示“用作示例、实例或说明”。本发明的任何方面或本文描述为“示例性”的设计不一定被解释为优选于或优于本发明或设计的其他方面。此外,相同的数字在所有若干图示中指示相同的元件,且除非在描述中另有指定,冠词“一”和“上述”包含多个的参考。34.可以理解,当元件被称为被“连接”或“耦接”至另一元件时,该元件可被直接地连接到或耦接至另一元件或者可存在中间元件。相反地,当该元件被称为被“直接连接”或“直接耦接”至到另一元件时,则不存在中间元件。用于描述元件之间的关系的其他词语应以类似方式被解释(例如,“在…之间”与“直接在…之间”、“相邻”与“直接相邻”等方式)。35.为了更好地描述本发明的实施例,下面先对本发明中用到的专用名词进行定义。36.旧指令:被前代处理器原生支持的指令被称为原生指令(nativeinstruction),也被称为已存在指令或旧指令。37.未知指令:不被前代处理器原生支持的指令。38.新增指令:与前代处理器相比,后代处理器所新增支持的指令。新增指令无法被前代处理器所辨识,因此对前代处理器而言属于未知指令。39.新增架构寄存器:与前代处理器相比,后代处理器所新增支持的架构寄存器。新增架构寄存器在前代处理器中并不存在,因此在前代处理器上模拟执行使用新增架构寄存器的新增指令时,需要模拟新增架构寄存器。40.无法辨识指令:未知指令中,除去新增指令之后剩余的那部分指令。即,无法辨识指令是指不被后代处理器原生支持的指令。41.模型特别寄存器:处理器中的一类寄存器,可用于完成一些特定的功能。42.陷阱:陷阱一般由软中断指令(比如int指令)引起。当一条指令引起陷阱异常时,并不表示这条指令本身的执行出现错误。因此,当一条指令出现陷阱异常后,处理器会继续执行这条指令的下一条指令。举例来说,软件开发人员对软件程序码进行调试时,可在程序码中设置断点。在处理器上执行设置了断点的程序码时,执行到断点时,将产生一个陷阱,从而使得程序码在断点处暂停执行。软件开发人员通过处理陷阱的微码处理程序,可以查看程序码执行到断点时处理器中各架构寄存器的值或程序码中各个变量的值。并根据各架构寄存器的值或程序码中各个变量的值,判断执行到断点时程序码是否执行正常。43.本发明所述的处理器可为具备精简指令集运算(reducedinstructionsetcomputing,risc,例如arm/mips/risc-v指令集)、复杂指令集运算(complexinstructionsetcomputing,cisc,例如x86指令集)、或其他指令集类型的处理器;亦或是能同时支持多种不同指令集架构的处理器(例如同时支援x86指令集与arm指令集的处理器)。本发明在处理器所支持的指令集类型上并不做特别限定,但为方便说明,本说明书实施例以支持x86指令集的处理器来描述。此外,本领域技术人员皆知,x86处理器会依据原始程序顺序(in-order)解译宏指令(macroinstruction)成为至少一个微指令(microinstruction)或微指令序列,但微指令的执行方式是以乱序(out-of-order)方式进行以提升执行效率,只是微指令执行完毕后的提交(retire)过程中仍以原始的程序顺序进行。44.本发明具有多种实施方式,下面用4个实施例来描述本发明的4种主要的实施方式。第一实施例为在系统管理模式下模拟执行新增指令的实施方式。第二实施例为在与新增指令相同的执行模式下模拟执行新增指令的实施方式。第三实施例以及第四实施例为通过操作系统模拟执行新增指令的实施方式,其中,第四实施例使用一专用处理核心完成对新增指令的转换操作。下面先描述第一实施例。45.[第一实施例][0046]图1是显示根据发明第一实施例所述的执行新增指令的系统的示意图。如图1所示,执行新增指令的系统100包含处理器110、操作系统120、应用程序130以及模拟器142。操作系统120运行于处理器110之上,用于对处理器110进行管理。应用程序130运行于操作系统120之上,可以通过操作系统120使用处理器110以及其它硬件(未示出,比如硬盘、网卡等等)提供的各种功能。模拟器142运行于处于系统管理模式(systemmanagementmode,smm)下的处理器110之上。操作系统120或应用程序130,无法感知到模拟器142的执行过程。即,模拟器142执行的所有操作,对操作系统120或应用程序130是透明的。[0047]当处理器110执行到应用程序130或操作系统120的一条未知指令时,处理器110会进入系统管理模式,并将上述未知指令发送模拟器142进行处理。如果上述未知指令为新增指令,模拟器142将模拟执行上述新增指令。值得注意的是,应用程序130或操作系统120的源码一般是使用高级语言(比如c语言、c 语言,等等)和/或低级语言(比如汇编语言,等等)编写的。使用编译器(compiler)对源码进行编译后,生成可以被处理器执行的可执行代码。可执行代码由可以被处理器执行的指令组成。在本发明中,应用程序130或操作系统120是指经编译器对应用程序130或操作系统120的源码编译后,生成的可执行代码。下面将以图1中的处理器110处理未知指令132为例,对执行新增指令的系统100的处理过程进行简单的描述。[0048]如图1所示,处理器110包含中断预处理单元112以及系统管理模式出/入口114。系统管理模式出/入口114包含系统管理模式入口1142以及系统管理模式出口1144。图1中带数字编号的实线箭头表示指令信息的传输方向,带数字编号的虚线箭头表示指令模拟执行结果的传输方向。下面描述处理器110处理未知指令132的整个过程。[0049]首先,处理器110接收应用程序130中完成指定功能的指令118(如实线箭头1所示)。接收到指令118之后,处理器110判断指令118是否为未知指令132。若指令118为未知指令132,处理器110发出一未知指令异常(#ud)。响应于上述未知指令异常,中断预处理单元112执行未知指令异常的微码处理程序。在未知指令异常的微码处理程序中,中断预处理单元112设置一模拟标识(emulationflag,ef)并发出一系统管理中断(#smi),同时把未知指令132的指令信息发送给系统管理模式出/入口114(如实线箭头2所示)。对于如何发出未知指令异常以及系统管理中断,为本领域技术人员的通常知识,此处就不赘述了。在一实施例中,处理器110是支持x86指令集的处理器,中断预处理单元112是微码控制单元。在实际操作上,本领域技术人员可以对中断预处理单元112中保存的未知指令异常的微码处理程序进行修改,以添加设置模拟标识、获取未知指令的指令信息,以及发出系统管理中断的功能。由于这些微码会依处理器版本而不同,本领域技术人员可依实际情况撰写对应的微码。[0050]然后,处理器110通过执行系统管理模式入口1142进入系统管理模式,并把未知指令132的指令信息发送给模拟器142(如实线箭头3所示)。在系统管理模式中,模拟器142判断未知指令132是否为新增指令。如果未知指令132为新增指令,模拟器142模拟执行上述新增指令。模拟执行完上述新增指令之后,模拟器142把模拟执行结果发送给系统管理模式出/入口114(如虚线箭头4所示)。然后,处理器110通过系统管理模式出口1144将模拟执行结果发送给应用程序130(如虚线箭头5所示),并退出系统管理模式。到此,处理器110就处理完了未知指令132。在一实施例中,在模拟器142模拟执行上述新增指令的过程中,可以将模拟执行过程中产生的中间运算结果存入系统管理内存(smram)中。[0051]图2是显示根据本发明第一实施例所述的处理器的结构图。如图2所示,位于虚线左边的处理器200为图1所示的处理器110的结构图,位于虚线右边的模拟器142以及转换程序145运行于处于系统管理模式下的处理器200之上。在一实施例中,转换程序145所完成的功能实现于一转换模块中,或者,也可以把转换程序145看作是执行新增指令的系统100中的转换模块。下面结合图1对图2进行说明。[0052]如图2所示,处理器200包含指令旁路转换缓冲(instructiontranslationlookasidebuffer,itlb)201、指令快取(instructioncache)202以及分支预测器(branchpredictor)203。当处理器200执行到应用程序130或是操作系统120的一指令时,处理器200的指令旁路转换缓冲201接收此指令。分支预测器203用于对条件分支进行预测,并将分支预测结果传给指令快取202。指令快取202根据分支预测结果从指令旁路转换缓冲201获取上述接收指令,然后处理器200会对上述接收指令做进一步的处理。[0053]如图2所示,处理器200还包含指令译码单元230。指令译码单元230判断上述接收指令是否为未知指令,然后生成至少一微指令,其中,上述微指令中包含一未知指令标识,用于表示上述接收指令是否为未知指令。当未知指令标识为第一数值时,表示上述接收指令为未知指令。当未知指令标识为第二数值时,表示上述接收指令为旧指令。在一实施例中,第一数值为1,第二数值为0。[0054]处理器200还包含重命名单元204、保留站205、执行单元206、访存单元207、重排缓冲区240、中断预处理单元112以及架构寄存器260。重命名单元204从指令译码单元230接收微指令后,对其进行重命名处理,其中,上述微指令中包含一未知指令标识(ud)。然后,重命名单元204将重命名后的微指令发送给保留站205和重排缓冲区240。保留站205根据上述微指令的类型,将上述微指令发送给执行单元206或访存单元207做进一步处理。重排缓冲区240接收到上述微指令后,将其存入指令条目中。重排缓冲区240中包含多个指令条目,每个指令条目包含一未知指令标识字段,用于保存上述微指令中的未知指令标识。[0055]重排缓冲区240包含指令提交单元245。当上述微指令满足提交(retire)条件时,指令提交单元245会提交上述微指令。提交上述微指令时,如果执行上述微指令时没有产生异常,指令提交单元245会根据上述微指令的执行结果更新架构寄存器260。如果执行上述微指令时产生了异常,指令提交单元245会报告(report)上述异常。响应于上述异常,处理器200会执行上述异常的微码处理程序。[0056]当指令提交单元245提交上述微指令时,如果上述微指令的未知指令标识为第一数值,指令提交单元245会发出一未知指令异常(#ud)。响应于上述未知指令异常,处理器200执行未知指令异常的微码处理程序。在上述未知指令异常的微码处理程序中,处理器200将一值为第一数值的模拟标识存入微体系结构寄存器220中,并发出一系统管理中断(#smi)。响应于上述系统管理中断,处理器200将通过如图1所示的系统管理模式入口1142,根据微体系结构寄存器220中存储的上述模拟标识进入系统管理模式。在系统管理模式下,处理器200通过模拟器142处理上述接收指令。首先,模拟器142判断上述接收指令是否为新增指令。如果上述接收指令为新增指令,模拟器142将模拟执行上述接收指令。在模拟执行上述接收指令的过程中,模拟器142可以将中间运算结果存入系统管理内存(smram)。需要说明的是,当模拟标识为第一数值时,表示需要模拟器142处理上述接收指令;当模拟标识为第二数值时,表示不需要模拟器142处理上述接收指令。[0057]模拟器142处理完上述接收指令后,处理器200通过执行如图1所示的系统管理模式出口1144退出系统管理模式。系统管理模式出口1144将微体系结构寄存器220中存储的模拟标识设置为第二数值,然后退出系统管理模式。当处理器200执行另一指令,并且另一指令为未知指令时,处理器200在执行未知指令异常的微码处理程序时,又会把微体系结构寄存器220中存储的模拟标识设置为第一数值。然后,处理器200按前述的处理过程处理上述另一指令。[0058]图3是显示根据本发明第一实施例所述的执行新增指令的流程图。请同时参照图2与图3,如图3所示,指令译码单元230接收一指令(s305),当上述接收指令为未知指令时,指令提交单元245发出一未知指令异常(s310)。响应于上述未知指令异常,处理器200进入一系统管理模式(s315),并通过一转换程序判断上述接收指令是否为新增指令(s320)。当上述接收指令为新增指令时,处理器200通过执行至少一个旧指令来模拟上述接收指令的执行(s325)。详细说明如下:指令译码单元230先执行步骤s305。[0059]在步骤s305中,指令译码单元230接收一指令。具体而言,指令译码单元230从指令快取202接收上述指令。然后,处理器200执行步骤s310。[0060]在步骤s310中,当上述接收指令为未知指令时,指令提交单元245发出一未知指令异常。具体来说,如前所述,当指令译码单元230判断上述接收指令为未知指令后,将生成一微指令,其中,上述微指令中包含一值为第一数值的未知指令标识。然后,指令译码单元230把上述微指令发送给重命名单元204。重命名单元204对上述微指令进行重命名处理,然后将上述微指令发送给重排缓冲区240。重排缓冲区240将上述微指令存入一指令条目中。当上述微指令满足提交(retire)条件时,指令提交单元245从上述指令条目中读取上述微指令,并对上述微指令进行提交处理。由于上述微指令的未知指令标识为第一数值,指令提交单元245发出一未知指令异常。然后,处理器200执行步骤s315。[0061]在步骤s315中,响应于上述未知指令异常,处理器200进入一系统管理模式(systemmanagementmode,smm)。具体来说,响应于上述未知指令异常,处理器200执行未知指令异常的微码处理程序。在上述未知指令异常的微码处理程序中,处理器200将一值为第一数值的模拟标识(emulationflag,ef)写入微体系结构寄存器220中,并发出一系统管理中断(#smi)。响应于上述系统管理中断,处理器200将通过如图1所示的系统管理模式入口1142,根据上述模拟标识进入系统管理模式。然后执行步骤s320。[0062]在步骤s320中,在上述系统管理模式下,处理器200通过一转换程序判断上述接收指令是否为新增指令。至于转换程序是如何判断上述接收指令是否为新增指令的,后文将结合图7进行详细说明。在一实施例中,上述转换程序可被预先储存于一基本输入输出系统(bios)中。本领域技术人员皆知,执行新增指令的系统100开机启动时,会执行上述基本输入输出系统。上述基本输入输出系统中包含对系统管理模式进行初始化的代码。当执行新增指令的系统100执行到上述对系统管理模式进行初始化的代码时,会将上述转换程序载入系统管理内存中(smram)。然后,处理器200就可以在进入系统管理模式后,直接执行存储于系统管理内存中的上述转换程序了。然后,处理器200执行步骤s325。[0063]在步骤s325中,当上述接收指令为新增指令时,处理器200通过执行至少一个旧指令来模拟上述接收指令的执行。具体来说,当上述接收指令为新增指令时,处理器200会先通过上述转换程序把上述接收指令转换为至少一个旧指令。然后,处理器200执行上述至少一个旧指令。至于更详细的说明,参见后文对图6的步骤s615、s620、s625以及s630的描述。[0064]在一实施例中,上述接收指令为指令集架构指令,上述至少一个旧指令为指令集架构指令。在另一实施例中,上述接收指令为x86指令、arm指令、risc-v指令或mips指令,上述至少一个旧指令为x86指令、arm指令、risc-v指令或mips指令。[0065]图4是显示根据本发明第一实施例所述的处理接收指令的流程图。请同时参照图2与图4,如图4所示,指令译码单元230接收一指令(s405),并判断上述接收指令是否为一未知指令(s410)。当上述接收指令为未知指令时,进入系统管理模式处理上述接收指令。由于步骤s405与图3的步骤s305相同,此处就不赘述了。下面描述步骤s410。[0066]在步骤s410中,指令译码单元230判断上述接收指令是否为一未知指令。具体而言,指令译码单元230对接上述收指令进行译码,以获得上述接收指令的译码信息。在一实施例中,上述译码信息包含前缀(prefix)、转义码(escapecode)、操作码(opcode)、操作数模式(modr/m)以及其它译码信息,等等。然后,指令译码单元230根据上述译码信息判断上述接收指令是否为未知指令。举例来说,可以将处理器200所原生支持的旧指令的操作码存放到一个查找表(lookuptable)中。指令译码单元230可以查看上述接收指令的上述操作码是否存放在上述查找表中,如果存放在上述查找表中,则表示上述接收指令为旧指令;否则,表示上述接收指令为未知指令。在一实施例中,上述查找表存储在指令译码单元230中。[0067]当上述接收指令为旧指令时(步骤s410中的“否”),执行步骤s435。在步骤s435中,处理器200正常处理上述接收指令。至于如何正常处理上述接收指令,例如将上述旧指令转换为与其对应的微指令,并执行上述对应的微指令,为本领域技术人员的通常知识,此处就不赘述了。当上述接收指令为未知指令(步骤s410中的“是”)时,执行步骤s415。[0068]在步骤s415中,处理器200将一模拟标识写入一微体系结构寄存器220中。具体而言,当上述接收指令为未知指令时,指令译码单元230生成一微指令,上述微指令的未知指令标识为第一数值。在一实施例中,上述微指令为空操作微指令(nop)。指令译码单元230将上述微指令发送给重命名单元204。重命名单元204对上述微指令做重命名处理。然后,重命名单元204把上述微指令发送给重排缓冲区240。重排缓冲区240将上述微指令保存在自己的指令条目中。当提交上述微指令时,由于上述微指令的未知指令标识为第一数值,指令提交单元245对发出一未知指令异常。响应于上述未知指令异常,处理器200执行未知指令异常的微码处理程序。在上述未知指令异常的微码处理程序中,处理器200将一模拟标识写入微体系结构寄存器220中。另外,处理器200还将上述接收指令的信息以及上述接收指令的运行环境信息存入微体系结构寄存器220中。然后,在上述未知指令异常的微码处理程序中,处理器200发出一系统管理中断(#smi)。在一实施例中,上述接收指令的信息包括上述接收指令的指令指针。在另一实施例中,上述接收指令的信息包括上述接收指令的指令指针和上述接收指令的机器码。上述运行环境信息包含上述接收指令的运行模式(即处理器200执行到上述接收指令时,处理器200的运行模式)。举例来说,运行模式包含实模式(readmode)、保护模式(protectedmode)、虚拟8086模式(v8086mode)、兼容模式(compatibilitymode)以及长模式(longmode),等等。然后,处理器200执行步骤s420。[0069]在步骤s420中,处理器200进入系统管理模式。具体来说,响应于上述系统管理中断,处理器200通过执行如图1所示的系统管理模式入口1142,进入系统管理模式。至于处理器200进入系统管理模式的细节,后文将结合图5进行详述。然后,处理器200执行步骤s425。[0070]在步骤s425中,处理器200处理上述接收指令。至于处理器200如何处理上述接收指令,后文将结合图6~8进行详细描述。然后,处理器200执行步骤s430。[0071]在步骤s430中,处理器200退出系统管理模式,并结束此流程。具体而言,处理器200通过执行如图1所示的系统管理模式出口1144,退出系统管理模式。至于处理器200如何退出系统管理模式,后文将结合图9a~9b进行详细描述。[0072]图5是显示根据本发明第一实施例所述的进入系统管理模式的流程图。图5为与图1所示的系统管理模式入口1142对应的微码处理程序的处理流程。请参照图2与图5,如图5所示,处理器200禁用中断(s505),判断模拟标识是否为第一数值(s510)。如果步骤s510的判断结果为“是”,则进入系统管理模式。详细说明如下:处理器200先执行步骤s505。[0073]在步骤s505中,处理器200禁用中断。本领域技术人员皆知,在系统管理模式下是禁用中断的,因此本发明中也延续此架构要求而禁用中断。至于如何禁用中断,举例来说,处理器200将if标识清零以禁用可屏蔽中断,将tf标识清零以禁用单步中断,将dr7清零以禁用断点中断。然后,处理器200执行步骤s510。[0074]接着,在步骤s510中,处理器200判断上述模拟标识是否为第一数值。具体而言,处理器200判断微体系结构寄存器220中保存的模拟标识是否为第一数值。如果判断结果为“否”,执行步骤s530,以执行进入系统管理模式的正常处理流程。本领域技术人员都了解系统管理模式的正常处理流程,此处就不赘述了。如果判断结果为“是”,处理器200执行步骤s515。[0075]在步骤s515中,处理器200发出进入系统管理模式通知(assert#smmact),以通知芯片组处理器200进入了系统管理模式。至于如何发出进入系统管理模式通知,为本领域技术人员的通常知识,此处就不赘述了。然后,处理器200执行步骤s520。[0076]在步骤s520中,处理器200将模拟标识、接收指令的信息以及运行环境信息存入系统管理内存中。具体而言,处理器200从微体系结构寄存器220读取模拟标识、接收指令的信息以及运行环境信息,并将读取到的模拟标识、接收指令的信息以及运行环境信息存入系统管理内存中。同时,架构寄存器260中的内容(即处理器200的当前状态)也会被存入系统管理内存中。系统管理内存中存储的信息如下表1所示。[0077]表1[0078][0079]然后,处理器200执行步骤s525中,建立系统管理模式执行环境,并进入系统管理模式。对于如何建立系统管理模式执行环境以及如何进入系统管理模式,为本领域技术人员的通常知识,此处就不赘述了。[0080]值得注意的是,在图5所示的通过图1的系统管理模式入口1142进入系统管理模式的实际操作上,本领域技术人员可在发出系统管理中断(#smi)后,在进入系统管理模式对应的微码中加入一些执行保存模拟标识、上述接收指令的信息和运行环境信息至系统管理内存(smram)的微码,并确保这些数据/信息不会因处理器200切换至系统管理模式而被覆写(overwrite)。再者,因为在已知技术下,处于系统管理模式下的处理器200会去访问系统管理内存(smram),所以本领域技术人员可基于这部分的微码做修改,即可达到访问这些数据/信息的目的。由于这些微码会依处理器版本而不同,本领域技术人员可依据实际状况撰写对应的微码。[0081]然后,处理器200在系统管理模式下处理上述接收指令(如图4所示的步骤s425)。下面结合图6~8详述处理器200如何在系统管理模式下处理上述接收指令。[0082]图6是显示根据本发明第一实施例所述的模拟器的处理流程图。如前所述,处理器200在系统管理模式中通过模拟器142对上述接收指令进行处理。请参照图2和图6,如图6所示,在系统管理模式中,模拟器142建立模拟运行环境(s605),然后判断模拟标识是否为第一数值(s610)。如果步骤s610的判断结果为“是”,模拟器142通过转换程序转换上述接收指令,并生成一转换结果(s615)。然后,模拟器142处理上述转换结果。详细说明如下:首先,模拟器142执行步骤s605。[0083]在步骤s605中,模拟器142建立模拟运行环境。具体而言,模拟器142从系统管理内存读取模拟标识、接收指令的信息、接收指令的运行环境信息以及架构寄存器的信息。后续步骤中,将使用上述读取到的信息模拟执行上述接收指令。然后,模拟器142执行步骤s610。[0084]在步骤s610中,模拟器142判断模拟标识是否为第一数值。具体而言,模拟器142判断在步骤s605中读取到的模拟标识是否为第一数值。如果判断结果为“否”,模拟器142执行步骤s645。在步骤s645中,模拟器142执行系统管理模式的正常处理流程。对于系统管理模式的正常处理流程,为本领域技术人员的通常知识,此处就不再赘述了。如果步骤s610的判断结果为“是”,模拟器142执行步骤s615。[0085]在步骤s615中,模拟器142通过转换程序145转换上述接收指令,并生成一转换结果。转换结果的结构如下面的表2所示,包含结果和内容两个字段。当结果字段为第一数值时,表示转换成功,此时内容字段中包含由上述接收指令转换得到的至少一个旧指令以及上述接收指令的长度;当结果字段为第二数值时,表示转换失败,此时内容字段中包含一异常编号。至于如何通过转换程序145转换上述接收指令,后文将结合图7详述。[0086]表2[0087]结果内容……[0088]在步骤s620中,模拟器142判断上述转换程序是否转换成功。具体而言,模拟器142根据上述转换结果中的结果字段,判断上述转换程序是否转换成功。当转换结果的结果字段为第一数值时,判断结果为“是”,模拟器142执行步骤s625;当转换结果的结果字段为第二数值时,判断结果为“否”,模拟器142根据转换结果生成模拟执行结果,然后执行步骤s630。模拟执行结果的结构如下面的表3所示,包含结果和详情两个字段。当模拟执行结果的结果字段为第一数值时,表示模拟执行成功,详情字段中保存模拟执行后获得的运算结果;当模拟执行结果的结果字段为第二数值时,表示模拟执行失败,详情字段中保存异常编号。当模拟执行结果的结果字段为第二数值时,根据转换结果生成的模拟执行结果如下面的表3-1所示。表3-1中的详情字段中的异常编号,就是转换结果的内容字段中的异常编号。[0089]表3[0090]结果详情……[0091]表3-1[0092]结果详情第二数值异常编号[0093]更进一步说,当步骤s620的判断结果为转换成功时(即步骤s620的判断结果为“是”),模拟器142执行步骤s625。在步骤s625中,模拟器142从上述转换结果中获取至少一个旧指令,并执行上述至少一个旧指令。具体而言,模拟器142从上述转换结果的内容字段获取上述至少一个旧指令以及上述接收指令的长度。然后,模拟器142通过呼叫指令或跳转指令使处理器200执行上述至少一个旧指令。处理器200将上述至少一个旧指令译码为至少一个微指令,并执行上述至少一个微指令,生成一模拟执行结果。如果处理器200执行上述至少一个微指令的过程中发生了运行时异常(runtimeexception),则模拟执行结果的内容字段如下表3-2所示。表3-2中模拟执行结果的结果字段为第二数值,表示模拟执行失败;模拟执行结果的详情字段为异常编号,即运行时异常的编号。如果处理器200执行上述至少一个微指令成功,则模拟执行结果的内容字段如下表3-3所示。表3-3中模拟执行结果的结果为第一数值,表示模拟执行成功;模拟执行结果的详情字段为运算结果。[0094]表3-2[0095]结果详情第二数值异常编号[0096]表3-3[0097]结果详情第一数值运算结果[0098]在一实施例中,当上述接收指令的操作数包含新增架构寄存器时,上述新增架构寄存器利用系统管理内存进行模拟。举例来说,当处理器200的后代处理器中包含一个位宽为1024-bit的新增架构寄存器时,模拟器142可以利用系统管理内存中一连续的1024-bit的存储空间来模拟上述新增架构寄存器。也就是说,当上述接收指令访问上述新增架构寄存器时,模拟器142实际访问的是系统管理内存中的上述连续的1024-bit的存储空间。[0099]当上述新增架构寄存器为上述接收指令的目的操作数(destinationoperand)时,执行完上述至少一个旧指令后,处理器200将上述接收指令的运算结果存入上述系统管理内存中。这样,当处理器200执行另一指令,并且另一指令也为新增指令,且上述新增架构寄存器为上述另一指令的源操作数(sourceoperand)时,处理器200在模拟执行上述另一指令时,直接使用上述系统管理内存中保存的上述运算结果。需要注意的是,上述接收指令和上述另一指令可以是连续的(即相邻的),也可以不是连续的,本发明对此并不做限制。[0100]在系统管理模式下,模拟器142只能访问系统管理内存,而无法以正常的访问内存的方式访问内存(即系统内存,下同)。本发明的一实施例中,提供了一种物理内存直接访问接口,以实现在系统管理模式下访问内存的操作。当上述接收指令包含内存操作数时,可以通过上述物理内存直接访问接口访问上述内存操作数。通过上述物理内存直接访问接口访问内存操作数的步骤如下:[0101]第一步,模拟器142将上述内存操作数的虚拟地址转换为物理地址。具体而言,模拟器142通过上述物理内存直接访问接口,通过访问页表,将上述内存操作数的虚拟地址转换为物理地址。将虚拟地址转换为物理地址的步骤为:一、从系统管理内存中读出架构寄存器cr3中保存的页表基地址;二、根据页表基地址和虚拟地址进行页表查询,模拟页表查询过程后,获取到物理地址。[0102]第二步,模拟器142通过上述物理内存直接访问接口根据上述物理地址读取该内存操作数的数值,其中,该物理地址不在系统管理内存中。具体而言,模拟器142通过上述物理内存直接访问接口,利用一模型特别寄存器(modelspecificregister,msr),根据上述物理地址读取该内存操作数的数值。具体步骤为:[0103]第1步,模拟器142将上述模型特别寄存器的地址写入一第一寄存器(ecx),并将上述物理地址写入一第二寄存器(edx:eax)。[0104]第2步,模拟器142执行写模型特别寄存器指令(wrmsr),以将上述内存操作数的数值存储到上述模型特别寄存器中。具体而言,模拟器142执行完上述写模型特别寄存器指令后,上述物理地址会被写入上述模型特别寄存器中。然后,处理器1100使用上述模型特别寄存器中存储的上述物理地址,通过执行一从物理地址加载微指令(ld_phys),将上述内存操作数的数值从系统内存加载到上述模型特别寄存器中。[0105]第3步,模拟器142执行读模型特别寄存器指令(rdmsr),以从上述模型特别寄存器中读取上述内存操作数的数值,并将读取到的上述内存操作数的数值存储到上述第二寄存器中。[0106]在一实施例中,上述接收指令的下一条指令为上述另一指令。上述至少一个旧指令中的最后一条指令为跳转指令(jump)或呼叫指令(call),处理器1100通过上述跳转指令或上述呼叫指令跳转到上述另一指令。上述另一指令的指令指针为:eip length,其中,eip为上述接收指令的指令指针,length为上述接收指令的长度。[0107]然后,模拟器142执行步骤s630。在步骤s630中,模拟器142将模拟执行结果写入系统管理内存。具体而言,模拟器142将在步骤s625或步骤s620中生成的模拟执行结果写入系统管理内存。由前述可知,模拟执行结果存在两种情况:一种是模拟执行成功,一种是模拟执行失败。系统管理内存中包含一异常向量表,其结构如下表4所示。异常向量表包含异常标识和异常编号2个字段。将模拟执行结果存入系统管理内存时,需要填写系统管理内存中的异常向量表。下面分别描述模拟器142将这两种情况的模拟执行结果存入系统管理内存的过程。[0108]表4[0109]异常标识异常编号……[0110]当模拟执行成功时,模拟器142将系统管理内存中的异常向量表的异常标识字段设置为第一数值(如下面的表4-1所示),并将模拟执行结果的详情字段中存储的运算结果存入系统管理内存中。举例来说,如果上述运算结果为架构寄存器ecx的值变为了10h(即十六进制数字10,下同),则模拟器142需要将10h写入系统管理内存中架构寄存器ecx对应的存储空间。如果运算结果为新增架构寄存器的值变为了20h,则模拟器142需要将20h写入系统管理内存中模拟新增架构寄存器所用的存储空间。模拟器142还将保存在系统管理内存中的上述接收指令的指令指针的值更新为:eip length,以使处理器200的指令指针指向下一条要执行的指令,其中,eip为指令指针更新前的值,length为上述接收指令的长度。系统管理内存中的上述接收指令的指令指针为架构寄存器eip对应的存储空间。退出系统管理模式时,系统管理内存中架构寄存器对应的存储空间中的值会被写入对应的架构寄存器260中,以将新增指令的模拟执行结果发送给应用程序130或操作系统120,后文将对此进行详述。[0111]表4-1[0112]异常标识异常编号第一数值…[0113]当模拟执行失败时,表示模拟执行时出现了异常。模拟器142将系统管理内存中的异常向量表的异常标识字段设置为第二数值(如下面的表4-2所示),并将模拟执行结果的详情字段中存储的异常编号写入异常向量表的异常编号字段。根据异常编号可以判断异常是否为陷阱(trap),当上述异常为陷阱时,模拟器142将保存在系统管理内存中的上述接收指令的指令指针的值更新为:eip length,以将处理器200的指令指针指向下一条要执行的指令集架构指令,其中,eip为上述接收指令的指令指针更新前的值,length为保存在系统管理内存中的上述接收指令的长度。[0114]表4-2[0115]异常标识异常编号第二数值异常编号[0116]然后,模拟器142执行步骤s635。在步骤s635中,模拟器142执行退出系统管理模式指令(resumefromsystemmanagementmode,rsm)。执行退出系统管理模式指令后,处理器200将执行如图1所示的系统管理模式出口1144的微码处理程序,后文将结合图9a~9b对其进行详细说明。[0117]图7是显示根据本发明第一实施例所述的转换程序的处理流程图。图7为如图1所示的转换程序145的处理流程图。请参照图2与图7,如图7所示,转换程序145获得上述接收指令的操作码(s705)。然后,转换程序145根据上述操作码判断上述接收指令是否为新增指令(s710)。当上述接收指令为新增指令时,转换程序145将上述接收指令转换为至少一个旧指令(s720),并生成一转换结果(s725)。详细说明如下:转换程序145先执行步骤s705。[0118]在步骤s705中,转换程序145根据上述接收指令的信息,获得上述接收指令的操作码。需要注意的是,由于此时还没有对上述接收指令进行译码,所以上述接收指令的信息不包含前缀、转义码及操作码等译码信息。根据前文对图4的步骤s415的描述可知,在一实施例中,上述接收指令的信息只包含上述接收指令的指令指针;在另一实施例中,上述接收指令的信息包含上述接收指令的指令指针和上述接收指令的机器码。转换程序145执行图7所示的处理流程时,可分为如下三种情形:[0119]第一种情形:当上述接收指令的信息只包含上述接收指令的指令指针时,转换程序145对上述接收指令进行译码时,根据上述接收指令的指令指针,每次读取并处理1个字节的机器码,直到译码完成;[0120]第二种情形:当上述接收指令的信息只包含上述接收指令的指令指针时,转换程序145先根据上述接收指令的指令指针读取完上述接收指令的机器码,然后再对读取到的机器码进行译码;[0121]第三种情形:当上述接收指令的信息包含上述接收指令的指令指针和上述接收指令的机器码时,转换程序145直接对上述接收指令的信息中的机器码进行译码;[0122]下面先描述在第一种情形下,转换程序145执行图7的处理流程的过程。转换程序145先执行步骤s705。[0123]在步骤s705中,转换程序145获得上述接收指令的操作码(opcode)。具体而言,转换程序145根据上述接收指令的信息获得上述接收指令的操作码。如前所述(图6的步骤s605),上述接收指令的信息是由模拟器142从系统管理内存中读取到的。上述接收指令的信息中只包含上述接收指令的指令指针,转换程序145是根据上述接收指令的指令指针获得上述接收指令的操作码的。详细来说,转换程序145根据上述接收指令的指令指针先从内存(即系统内存,systemmemory)读取上述接收指令的机器码的第1个字节,然后根据读取到的字节(即前1个字节)判断上述接收指令的操作码。如果根据上述机器码的第1个字节不能判断出上述接收指令的操作码,就再读取上述机器码的第2个字节,然后根据读取到的字节(即前2个字节)判断上述接收指令的操作码。依此类推,直到判断出上述接收指令的操作码为止。值得注意的是,如果上述接收指令包含前缀(prefix)和/或转义码(escape),转换程序145会先获取上述接收指令的前缀和/或转义码,然后再获取其操作码。在一实施例中,转换程序145通过如前所述的物理内存直接访问接口,根据上述接收指令的指令指针从内存读取机器码的。获得上述接收指令的操作码之后,转换程序145执行步骤s710。[0124]接着,在步骤s710中,转换程序145判断上述接收指令是否为新增指令。具体而言,转换程序145根据上述接收指令的操作码判断上述接收指令是否为新增指令。举例来说,可以将处理器200所支持的新增指令的操作码存放到一个查找表(lookuptable)中。转换程序145可以查看上述操作码是否存放在上述查找表中,如果存放在上述查找表中,则表示上述接收指令为新增指令,判断结果为“是”;否则,判断结果为“否”。在一实施例中,上述查找表存放在系统管理内存中。在一实施例中,转换程序145同时根据上述接收指令的转义码和操作码判断上述接收指令是否为新增指令。[0125]当上述接收指令不是新增指令(步骤s710判断结果为“否”)时,表示上述接收指令为无法辨识指令,转换程序145执行步骤s725,生成如下表2-1所示的转换结果。如下表2-1所示,转换结果的结果字段值为第二数值,表示转换失败;转换结果的内容字段为未知指令异常的异常编号#ud(值为6)。[0126]表2-1[0127]结果内容第二数值#ud[0128]当上述接收指令为新增指令时(步骤s710的判断结果为“是”),转换程序145执行步骤s712。在步骤s712中,转换程序145判断是否存在译码异常。具体而言,如前所述(图6的步骤s605),模拟程序142从系统管理内存中读取到了处理器200执行上述接收指令当时的运行环境信息,其中,上述运行环境信息包含处理器200的运行模式。转换程序145判断上述接收指令是否可以在上述运行环境下执行。举例来说,当上述运行模式为实模式时,如果上述接收指令不能运行在实模式下,则步骤s712的判断结果就为“是”;如果上述接收指令可以运行在实模式下,则步骤s712的判断结果就为“否”。[0129]在一实施例中,新增指令的操作码及其支持的运行环境被存放到一个查找表中。转换程序145可以根据上述接收指令的操作码,通过上述查找表查到上述接收指令可以在哪些运行环境下运行。在另一实施例中,上述查找表被存放在系统管理内存中。[0130]当转换程序145判断上述接收指令存在译码异常时(步骤s712的判断结果为“是”),执行步骤s725,生成如下表2-2所示的转换结果。如下表2-2所示,转换结果的结果字段值为第二数值,表示转换失败;转换结果的内容字段为未知指令异常的异常编号#ud(值为6)。[0131]表2-2[0132]结果内容第二数值#ud[0133]当转换程序145判断上述接收指令不存在译码异常时(步骤s712的判断结果为“否”),执行步骤s715。在步骤s715中,转换程序145获得上述接收指令的其它译码信息。具体而言,转换程序145继续一个字节一个字节地从内存读取上述接收指令的机器码,边读取边译码,直到译码出上述接收指令的其它译码信息,并计算出上述接收指令的长度,其中,上述其它译码信息包含操作数模式(modr/m)、源操作数和目的操作数,等等。本领域技术人员皆知,只有完成对上述接收指令的译码后,才能计算出上述接收指令的长度。然后,转换程序145执行步骤s720。[0134]在步骤s720中,转换程序145将上述接收指令转换为至少一个旧指令。具体而言,转换程序145可以通过查表的方式,将上述接收指令转换为至少一个旧指令。举例来说,可以先将上述接收指令对应的至少一个旧指令存放在一查找表中。然后,转换程序145根据上述接收指令的操作码,从上述查找表中获取上述至少一个旧指令。在一实施例中,当上述接收指令包含转义码时,转换程序145根据上述接收指令的转义码和操作码,从上述查找表中获取上述至少一个旧指令。在另一实施例中,转换程序145根据上述接收指令的转义码、操作码和操作数模式,从上述查找表中获取上述至少一个旧指令。[0135]值得注意的是,由于从上述查找表中获取到的上述至少一个旧指令中没有包含上述接收指令的源操作数和/或目的操作数等其它译码信息,所以需要将其它译码信息写入上述至少一个旧指令中,以使其可以模拟上述接收指令的执行。举例来说,转换程序145将上述接收指令的源操作数和/或目的操作数的具体值,写入上述至少一个旧指令中对应的位置。然后,处理器200就可以通过执行上述至少一个旧指令来模拟新增指令的执行了。在一实施例中,转换程序145是根据上述接收指令的前缀,将其它译码信息写入上述至少一个旧指令中的。[0136]在一实施例中,上述查找表被存放在基本输入输出系统(bios)中。本领域技术人员皆知,执行新增指令的系统100开机启动时,会执行上述基本输入输出系统。上述基本输入输出系统中包含对系统管理模式进行初始化的代码,当系统100执行到上述对系统管理模式进行初始化的代码时,会将上述查找表载入系统管理内存。然后,转换程序145便能根据上述接收指令的操作码,从上述查找表中获取上述至少一个旧指令。在另一实施例中,上述查找表被存放在私有只读存储器中。所以,在这2个实施例中,转换程序145是通过有硬件支持的查找表将接收指令转换为至少一个旧指令的。[0137]在另一实施例中,转换程序145将上述至少一个旧指令存入一内存或快取(cache)中。当处理器200执行另一指令时,如果上述另一指令为新增指令,则转换程序145判断上述接收指令与上述另一指令是否为同一指令。如果上述接收指令与上述另一指令为同一指令,则转换程序145会直接从上述内存或上述快取中获取上述至少一个旧指令。[0138]然后,转换程序145执行步骤s725,生成如下表2-3所示的转换结果。如下表2-3所示,转换结果的结果字段值为第一数值,表示转换成功;转换结果的内容字段为上述接收指令的长度和上述至少一个旧指令。[0139]表2-3[0140]结果内容第一数值接收指令的长度和至少一个旧指令[0141]下面描述在第二种情形下,转换程序145执行图7的处理流程的过程。在第二种情形下,转换程序145执行步骤s710、s712、s720以及s725的过程与在第一种情形下相同,此处就不赘述了。下面描述步骤s705和s715。[0142]与第一种情形不同的是,在第二种情形下,在步骤s705中,转换程序145先根据上述接收指令的指令指针从内存中读取到完整的上述接收指令的机器码,然后再对读取到的上述机器码进行译码处理,以获得上述接收指令的操作码。并且,在步骤s715中,转换程序145也是对在步骤s705中读取到的机器码进行译码,以获得上述接收指令的其它译码信息。在第二种情形下的其它处理都与第一种情形下相同,此处就不赘述了。[0143]值得注意的是,转换程序145根据上述接收指令的指令指针读取上述机器码时,由于还不知道上述接收指令的长度,所以需要读取足够长的上述机器码。举例来说,如果处理器200所能处理的新增指令中最长的新增指令的长度为15字节,那在步骤s705中,就需要读取至少15字节长的上述机器码。[0144]下面描述在第三种情形下,转换程序145执行图7的处理流程的过程。在第三种情形下,转换程序145执行步骤s710、s712、s715、s720以及s725的过程与在第二种情形下相同,此处就不赘述了。下面描述步骤s705。[0145]与第二种情形不同的是,在第三种情形下,在步骤s705中,转换程序145直接对上述接收指令的信息中的机器码进行译码处理,以获得上述接收指令的操作码。在第三种情形下的其它处理都与第二种情形下相同,此处就不赘述了。[0146]图8是显示根据本发明第一实施例所述的在系统管理模式下处理未知指令的例子。图8是以伪代码(pseudocode)的形式,展示如何实现如图6和图7所示的处理未知指令的处理流程,是模拟器的一个具体实现。[0147]如图8所示,第1-25行为实现模拟器的主函数simulator_start包含的代码。第27-36行为实现译码函数check_decode_excep包含的代码。第38-47行为实现新增指令功能的模拟函数unsupport_x_handle包含的代码,其中包含前文所述的与接收指令对应的至少一个旧指令。下面先描述主函数simulator_start。[0148]在主函数simulator_start中,先执行第3行代码。第3行代码完成图6的步骤s605的功能,处理器200建立模拟运行环境。在第3行代码中,处理器200通过函数setup_simulator_env来建立模拟运行环境。执行完第3行代码后,处理器200就把从系统管理内存读取到的模拟标识、接收指令的信息、接收指令的运行环境信息以及架构寄存器的信息保存到变量env中了。举例来说,在第4行代码中,通过env.emulation_flag访问的是模拟标识的值。第4行代码完成图6的步骤s610的功能,处理器200判断模拟标识是否为第一数值。如果第4行代码的判断结果为模拟标识不是第一数值,则执行第5行代码。第5行代码完成图6的步骤s645的功能,处理器200执行系统管理模式的正常处理流程。在第5行代码中,处理器200通过函数exit_to_normal_smm来执行进入系统管理模式的正常处理流程。如果第4行代码的判断结果为模拟标识是第一数值,则执行第8行代码,定义变量inst_emu,以作为第9行代码中的译码函数check_decode_excep的传出参数(后文将描述)。然后执行第9行代码。[0149]第9-15行代码完成图6的步骤s615的功能,处理器200通过转换程序转换上述接收指令,并生成一译码结果。具体来说,处理器200先执行第9行代码,通过译码函数check_decode_excep获得上述接收指令的操作码等译码信息,其中,上述译码信息被保存在传出参数inst_emu中。然后,处理器200执行第10行代码,判断译码是否成功。在第10行的代码中,处理器200根据译码结果decode_excep判断是否译码成功。如果译码失败,则表示转换失败,处理器200执行第11行的代码。第11行代码完成图6的步骤s630的功能,处理器200将转换失败的模拟执行结果写入系统管理内存。在第11行代码中,处理器200通过函数set_exception将转换失败的模拟执行结果写入系统管理内存。执行完第11行的代码后,执行第12行的代码,跳转到第23行的代码。在第12行代码中,处理器200通过指令goto跳转到标号out所在的位置(即第23行)。然后开始从第23行继续执行。由于第23行只有一个标号out,没有需要执行的代码,处理器200执行第24行的代码。第24行的代码完成图6的步骤s635的功能,处理器200执行退出系统管理模式指令。在第24行代码中,处理器200通过函数execute_rsm执行退出系统管理模式的指令。随后,处理器200将执行如图1所示的系统管理模式出口1144的微码。如果第10行代码的判断结果为译码成功,则执行第15行的代码。第15行代码完成图7的步骤s720的功能,处理器200根据接收指令的信息将上述接收指令转换为至少一个旧指令。如图8所示,在第15行代码中,是通过使用上述接收指令的操作码opcode,从表op_mapping中查找到上述至少一个旧指令的。以指针routine表示上述至少一个旧指令,routine的值为unsupport_x_handle函数的地址。然后,执行第16行的代码。[0150]第16行代码完成图6的步骤s625的功能,处理器200执行至少一个旧指令。执行routine时,处理器200实际执行的是模拟函数unsupport_x_handle(后文将详述)。执行完routine后,返回一值runtime_excep。然后,执行第18~19行的代码。第18~19行代码完成图6的步骤s630的功能,处理器200判断是否存在运行时异常。如果存在运行时异常,处理器200把出现运行时异常的模拟执行结果写入系统管理内存。在第18行代码中,处理器200根据返回值runtime_excep的值判断是否存在运行时异常。如果存在运行时异常,则执行第19行的代码。在第19行代码中,处理器200通过函数set_exception将上述运行时异常的模拟执行结果存入系统管理内存。然后,处理器200执行第20行的代码,通过goto指令跳转到第23行。如前所述,处理器200接下来会执行第24行的代码。第24行代码的功能前面已经描述,此处就不赘述了。[0151]下面描述译码函数check_decode_excep。[0152]在译码函数check_decode_excep中,先执行第29-30行代码,获得上述接收指令的操作码(图7的步骤s705)。在第29行中,处理器200通过函数read_instruction读取上述接收指令的机器码machine_code。此处是根据上述接收指令的指令指针ip从内存读取code_len字节长度的机器码machine_code(即前面讲解图7时所说的第二种情形),code_len的值可以是15。在第30行中,处理器200通过函数decode_opcode对上述机器码machine_code进行译码,得到上述接收指令的操作码opcode。在第31行中,处理器200通过函数is_emulate_op根据上述操作码opcode判断上述接收指令是否为新增指令(图7的步骤s710)。如果上述接收指令不是新增指令,处理器200执行第32行的代码,通过return指令向主函数simulator_start返回译码异常信息。如果上述接收指令是新增指令,处理器200先执行第33行代码,将上述操作码opcode存入传出参数inst_emu中;然后执行第34行的代码,获得上述接收指令的其它译码信息(图7的步骤s715),并将得到的其他译码信息存入传出参数inst_emu中。最后,处理器200执行第35行的代码,通过return指令向主函数simulator_start返回译码成功信息。主函数simulator_start可以通过传出参数inst_emu获得上述接收指令的操作码opcode和其它译码信息operands。[0153]下面描述模拟函数unsupport_x_handle。[0154]在模拟函数unsupport_x_handle中,先执行第40-41行代码。第40-41行代码完成读取操作数的值的操作,读取到的操作数的值存放在数组op中。在第41行中,处理器是通过函数read_op完成读取操作数的操作的。具体来说,read_op函数是从前文所述的env变量中获取操作数的值的。第42行代码完成图6的步骤s625的功能,处理器200执行至少一个旧指令,即处理器200模拟执行上述接收指令。在第42行中,op表示上述接收指令的操作数,operatewithop即表示将上述接收指令的操作数的值写入上述至少一个旧指令,并执行上述至少一个旧指令。然后执行第43行代码。第43行代码完成第6图的步骤s630的功能,处理器200将模拟执行结果(包含产生运行时异常的模拟执行结果和没有产生运行时异常的模拟执行结果)写入系统管理内存。更详细地说,在第43行代码中,处理器200通过函数write_result_to_smram将模拟执行结果存入系统管理内存。第44行代码判断执行第42行时是否产生了运行时异常,如果产生了运行时异常,执行第45行代码,将异常信息发送给主函数;否则,执行第46行代码,将执行正确的信息发送给主函数。在第45、46行代码中,处理器200是通过return指令将异常信息或执行正确的信息发送给主函数simulator_start的。[0155]图9a~9b是显示根据本发明第一实施例所述的退出系统管理模式的流程图。图9a~9b为与图1所示的系统管理模式出口1144对应的微码处理程序的处理流程。请参照图2与图9,如图9a~9b所示,退出系统管理模式时,处理器200判断模拟标识是否为第一数值(s901)。如果判断结果为“是”,处理器200重置模拟标识(s904),判断模拟执行结果是否存在异常(s905)。处理器200根据模拟执行结果是否存在异常以及异常的类型,执行退出系统管理模式的操作。详细说明如下:处理器200先执行步骤s901。[0156]在步骤s901中,处理器200判断模拟标识是否为第一数值。具体而言,处理器200从系统管理内存读取模拟标识(由前述对图5的步骤s520的描述可知,模拟标识被存入了系统管理内存),然后判断读取到的上述模拟标识是否为第一数值。如果上述模拟标识不为第一数值,处理器200执行步骤s903。在步骤s903中,处理器200执行退出系统管理模式的正常处理流程。对于退出系统管理模式的正常处理流程,为本领域技术人员的通常知识,此处就不赘述了。如果上述模拟标识为第一数值,处理器200执行步骤s904。[0157]在步骤s904中,处理器200重置模拟标识。具体而言,处理器200将微体系结构寄存器220和系统管理内存中的模拟标识设置为第二数值。重置模拟标识后,处理器200在后续的执行过程中,当发生正常的系统管理中断时,就会执行系统管理模式的正常处理流程了。然后,处理器200执行步骤s905。[0158]在步骤s905中,处理器200判断模拟执行结果是否存在异常。具体而言,处理器200从系统管理内存读取如前文表4所示的异常向量表。如果异常向量表的异常标识字段的值为第一数值,则表示模拟执行结果存在异常,判断结果为“是”;如果异常向量表的异常标识字段的值为第二数值,则表示模拟执行结果不存在异常,判断结果为“否”。如果判断结果为“否”,处理器200执行步骤s907。[0159]如图9b所示,在步骤s907中,处理器200将系统管理内存中保存的模拟执行结果存入架构寄存器。如前文所述,在图6的步骤s630中,处理器200已经将上述接收指令的模拟执行结果写入了系统管理内存中架构寄存器对应的区域。在本步骤中,处理器200将系统管理内存中架构寄存器对应的区域中的值存入架构寄存器260。这样,就相当于处理器200执行完了上述接收指令。[0160]如果上述接收指令的目的操作数为新增架构寄存器,由于处理器200的架构寄存器260中不包含新增架构寄存器,处理器200不会把系统管理内存中模拟新增架构寄存器的区域中的值存入架构寄存器260。如前所述,当处理器200在模拟执行另一新增指令,并且上述另一新增指令的操作数也为上述新增架构寄存器时,处理器200就可以直接使用保存在系统管理内存中的模拟上述新增架构寄存器的区域中的值,来模拟上述另一新增指令的执行。[0161]然后,处理器200执行步骤s909。在步骤s909中,处理器200启用中断。举例来说,处理器200设置if标识以启用可屏蔽中断,设置tf标识以启用单步中断,设置dr7以启用断点中断。然后,处理器200执行步骤s911。[0162]在步骤s911中,处理器200发出退出系统管理模式通知(deassert#smmact),以通知芯片组处理器200退出了系统管理模式。然后,处理器200执行步骤s913,退出系统管理模式。[0163]如图9a所示,当在步骤s905中,处理器200判断模拟执行结果存在异常时,执行步骤s915。[0164]在步骤s915中,处理器200判断异常类型是否为陷阱(trap)。具体而言,处理器200根据在步骤s905中从系统管理内存中读到的异常向量表中的异常标识及异常编号,判断模拟执行结果中的异常是否为陷阱。举例来说,当异常标识为第一数值,异常编号为3时(表4中内容如下表4-2所示),表示是溢出(overflow)异常。溢出异常的类型为陷阱,所以判断结果为“是”。当异常标识为第一数值,异常编号为0时(表4中内容如下表4-3所示),表示是除法错误异常。除法错误异常为错误(fault),不是陷阱,所以判断结果为“否”。[0165]表4-2[0166]异常标识异常编号第一数值3[0167]表4-3[0168]异常标识异常编号第一数值0[0169]当步骤s915的判断结果为“否”时,处理器200执行步骤s917、s919、s921以及s723。其中,步骤s917、步骤s919和步骤s921分别与步骤s909、步骤s911和步骤s913相同,此处就不赘述了。下面描述步骤s923。[0170]在步骤s923中,处理器200执行异常的微码处理程序。具体来说,处理器200根据系统管理内存中存储的异常向量表中的异常标识,判断是否产生了异常。如果产生了异常,处理器200根据上述异常向量表中存储的异常编号,执行上述异常的微码处理程序。即执行与上述异常编号对应的异常的微码处理程序。举例来说,当系统管理内存中存储的异常向量表中的异常标识为第一数值时,表示模拟执行结果存在异常。如果此时异常向量表中的异常编号为0,表示上述异常为除法错误,处理器200会执行除法错误的微码处理程序。[0171]在步骤s915中,当判断结果为“是”,即模拟执行结果的异常类型为陷阱时,处理器200执行图9b所示的步骤s925、s927、s929以及s933。其中,步骤s925、s927、s929分别于步骤s907、s909、s911相同,此处就不赘述了。下面描述步骤s933。[0172]在步骤s933中,处理器200执行异常的微码处理程序。举例来说,当模拟执行结果存在异常,并且异常为溢出异常时,处理器200执行溢出异常的微码处理程序。在图9a、9b所示的通过系统管理中断出口1144退出系统管理模式的实际操作上,本领域技术人员可在呼叫退出系统管理模式的指令(resumefromsystemmanagementmode,rsm)后,在退出系统管理模式对应的微码中加入一些将模拟执行结果从系统管理内存存入架构寄存器的微码,以将模拟执行结果传给应用程序130或操作系统120。由于这些微码会依处理器版本而不同,本领域技术人可依据实际状况撰写对应的微码。[0173]值得注意的是,在第一实施例中,微体系结构寄存器220是处理器200中本来就存在的寄存器。因此,在本发明的第一实施例中,在不对处理器的硬件结构进行修改的情况下,就可以在前代处理器上执行新增指令。所以,在本发明的第一实施例中,可以通过升级微码的方式,使得已经生产的处理器获得执行新增指令的功能。[0174][第二实施例][0175]图10是显示根据本发明第二实施例所述的执行新增指令的系统1000的示意图。与图1所示的第一实施例不同的是,图10所示的执行新增指令的系统1000中的转换程序145在与新增指令相同的执行模式下,直接运行于处理器之上。另外,由于第二实施例中的转换程序145是运行在与新增指令相同的执行模式下的,所以处理器执行转换程序145时不需要切换运行模式。下面详述第二实施例与第一实施例的不同之处。[0176]如图10所示,当指令118为未知指令132时,处理器110执行处理未知指令异常的微码处理程序。在处理未知指令异常的微码处理程序中,直接调用转换程序145(如图10中的实线箭头2所示)。转换程序145将判断未知指令132是否为新增指令。如果未知指令132为新增指令,转换程序145将其转换为至少一个旧指令,并将上述至少一个旧指令发送给处理未知指令异常的微码处理程序(如图10中的实线箭头6所示)。处理未知指令异常的微码处理程序接收上述至少一个旧指令,并通过呼叫指令(call)或跳转指令(jump)使处理器110执行上述至少一个旧指令。[0177]图11是依据本发明第二实施例所述的处理器的结构图。图11中和图2中相同名称的元件的功能相同,在此不再赘述。[0178]需注意的是,如图11所示,位于虚线左边的处理器1100为图10所示的处理器110的结构图,位于虚线右边的转换程序145运行于处于与新增指令相同的执行模式下的处理器1100之上(即,处理器不需要切换执行模式)。转换程序145可储存于处理器1100的处理核心内的中断预处理单元112中。在另一实施例中,转换程序145可储存于处理器1100的一非核心(uncore)中。因而,处理器1100的所有处理核心可以共享转换程序145。[0179]图12是显示根据本发明第二实施例所述的执行新增指令的流程图。图12所示的处理流程,可由图11的处理器1100执行。如图12所示,处理器1100接收一指令(s1205),当上述接收指令为未知指令时,发出一未知指令异常(s1210)。响应于上述未知指令异常,通过一转换程序判断上述接收指令是否为新增指令(s1215)。当上述接收指令为新增指令时,通过上述转换程序将上述接收指令转换为至少一个旧指令(s1220)。最后,处理器1100在与上述接收指令相同的执行模式下,执行上述至少一个旧指令(s1225)。图12的步骤s1205、s1210与图3的步骤s305、s310相同,此处就不赘述了。图3的步骤s320和s325与图12的步骤s1220和s1225的不同之处是,图3的步骤s320和s325运行在系统管理模式下,而图12的步骤s1220和s1225则是运行在与上述接收指令相同的执行模式下。图3的步骤s320和s325与图12的步骤s1220和s1225完成的功能是相同的,此处也不赘述了。下面只描述步骤s1215。[0180]在步骤s1215中,响应于上述未知指令异常,处理器1100通过一转换程序判断上述接收指令是否为新增指令。具体而言,指令提交单元245发出未知指令异常后,处理器1100执行处理未知指令异常的微码处理程序。在处理未知指令异常的微码处理程序中,处理器1100将上述接收指令的信息和运行环境信息发送给转换程序145。转换程序145根据上述接收指令的信息判断上述接收指令是否为新增指令。至于转换程序145是如何判断上述接收指令是否为新增指令的,已经在第一实施例中做了详细描述,此处就不赘述了。[0181]图13是显示根据本发明第二实施例所述的处理接收指令的流程图。图13的步骤s1305、s1310、s1325与图4的步骤s405、s410、s435相同,此处就不赘述了。下面描述步骤s1320。[0182]在步骤s1320中,图11的处理器1100处理上述接收指令。具体而言,当上述接收指令为未知指令时(步骤s1310的判断结果为“是”),处理器1100执行处理未知指令异常的微码处理程序。在处理未知指令异常的微码处理程序中,处理器1100通过转换程序145处理上述未知指令(后文将结合图14详述)。[0183]图14是显示根据本发明第二实施例所述的在处理未知指令异常的微码处理程序中处理接收指令的流程图。如图14所示,图11的处理器1100获取接收指令的信息(s1405),通过转换程序145转换上述接收指令,并生成转换结果(s1410)。如果转换成功(步骤s1415的判断结果为“是”),处理器1100从上述转换结果中获取至少一个旧指令,并执行上述至少一个旧指令(s1420)。详细说明如下:处理器1100先执行步骤s1405。[0184]在步骤s1405中,在未知指令异常的微码处理程序中获取接收指令的信息。上述接收指令的信息包含上述接收指令的指令指针。值得注意的是,由于此时还没有对上述接收指令进行译码,所以上述接收指令的信息不包含前缀、转义码及操作码等译码信息。执行未知指令异常的微码处理程序时,由于不需要进行模式转换,处理器1100的运行环境不会发生变化。所以,在未知指令异常的微码处理程序中,可以直接获取处理器1100的运行环境信息,这个运行环境信息就是上述接收指令的运行环境信息。然后,执行步骤s1410。[0185]在步骤s1410中,处理器1100通过转换程序145转换上述接收指令,并生成转换结果。至于如何通过转换程序145转换上述接收指令,与第一实施例中的处理过程相同,此处就不赘述了。步骤s1415与图6的步骤s620相同,此处就不赘述了。下面描述步骤s1420和s1425。[0186]当转换程序145转换成功时(步骤s1415中的“是”),处理器1100执行步骤s1420。在步骤s1420中,处理器1100从上述转换结果中获取至少一个旧指令,并执行上述至少一个旧指令。此外,处理器1100还可以从上述转换结果中获取上述接收指令的长度。在一实施例中,上述接收指令的下一条指令为另一指令。上述至少一个旧指令中的最后一条指令为跳转指令(jump)或呼叫指令(call),处理器1100通过上述跳转指令或上述呼叫指令跳转到上述另一指令。上述另一指令的指令指针为:eip length,其中,eip为上述接收指令的指令指针,length为上述接收指令的长度。[0187]当转换程序145转换失败时(步骤s1415中的“否”),处理器1100执行步骤s1425。在步骤s1425中,处理器1100处理异常。具体而言,当转换程序145转换上述接收指令时出现任何异常,都会导致转换失败。在中断预处理单元112的处理未知指令异常的微码处理程序中,可以从转换结果的内容字段中获得一异常编号。然后,处理未知指令异常的微码处理程序发出对应于上述异常编号的异常。响应于上述对应于上述异常编号的异常,处理器1100执行对应的微码处理程序,以处理上述异常。[0188]第二实施例的转换程序的处理流程与第一实施例中图7转换程序的处理流程相同,在此不再赘述。[0189]综上所述,与第一实施例不同的是,在本实施例中,当处理器1100执行到一未知指令时,处理器1100直接在与未知指令相同的执行模式下,执行转换程序145。转换程序145判断上述未知指令是否为新增指令。当上述未知指令为新增指令时,转换程序145将新增指令转换为至少一个旧指令。然后,处理器1100在与上述未知指令相同的执行模式下,执行上述至少一个旧指令。与第一实施例相比,在本实施例中,处理器不需要切换执行模式,因此模拟执行新增指令的效率更高。[0190][第三实施例][0191]图15a~15b是显示根据本发明第三实施例所述的执行新增指令的系统1500的示意图。与图1所示的第一实施例和图10所示的第二实施例不同的是,在第三实施例中,执行新增指令的系统1500中的转换程序145由操作系统120中的内核驱动程序150所运行。而转换程序145可位于内核驱动程序150的内部(如图15a所示)或是外部(如图15b所示)。请参照图11和图15a~15b,当处理器1100判断指令118为未知指令132后,会发出一未知指令异常。响应于上述未知指令异常,处理器1100执行未知指令异常的微码处理程序。在未知指令异常的微码处理程序中,处理器1100会调用内核驱动程序150,同时会把未知指令132的信息和运行环境信息发送给内核驱动程序150。内核驱动程序150通过转换程序145处理上述接收指令。[0192]在一实施例中,在未知指令异常的微码处理程序中,处理器1100通过自行定义的中断服务程序(中断服务程序的开发者,可以通过自行定义的中断向量#ne(non-supportinstructionemulator)调用自行定义的中断处理程序,其中,自行定义的中断向量#ne在中断向量表的保留编号中)去调用内核驱动程序150。值得注意的是,中断服务程序调用内核驱动程序150时必须将未知指令132的信息(包含指令指针等)和运行环境信息传给内核驱动程序150、或是将未知指令132的信息和运行环境信息的储存地址通知内核驱动程序150。再者,内核驱动程序150所使用的中断服务程序(自行定义的中断向量#ne对应的中断服务程序),可以是储存在中断预处理单元112中的微码并由中断预处理单元112调用(中断预处理单元112可用状态机或组合逻辑电路构筑)。在一实施例中,内核驱动程序150通过转换程序145处理未知指令132的方式,可以经由系统调用(systemcall)来呼叫操作系统120执行内核驱动程序150,例如把内核驱动程序150作为一回调函数(callbackfunction),未知指令132的信息和运行环境信息则被当成参数传给内核驱动程序150。如果未知指令132为新增指令,内核驱动程序150通过转换程序145处理完未知指令132后将至少一个旧指令回传处理器1100。此外,抑或是通过内部中断(internalinterrupt)或是陷阱(trap)来调用内核驱动程序150,例如处理器1100的设计者自行定义一中断向量#ne,并藉此进入操作系统的核心(kernel)去呼叫内核驱动程序150,熟习本领域技术人应知这部分的技术细节故不再赘述。在一实施例中,在未知指令异常的微码处理程序中发送未知指令132的信息和运行环境信息的过程为:将未知指令132的信息和运行环境信息压入(push)堆栈(stack)中,然后,内核驱动程序150从堆栈中获取未知指令132的信息和运行环境信息。[0193]在另一实施例中,可将操作系统中处理未知指令异常的中断服务程序修改为直接调用内核驱动程序150,以实现对未知指令132的处理。在修改后的处理未知指令异常的中断服务程序中,可以先读取未知指令132的信息和运行环境信息,并将读取到的未知指令132的信息和运行环境信息传送给内核驱动程序150。在本实施例中,不需要对处理器的硬件和/或微码进行修改,只需修改操作系统中处理未知指令异常的中断服务程序就可以实现如前文所述的对未知指令的处理,因而实现起来相当方便。在实际操作上,本领域技术人员可以对处理未知指令异常的中断服务程序进行修改,以添加读取未知指令132的信息和运行环境信息,以及调用内核驱动程序150的功能。由于处理未知指令异常的中断服务程序会依操作系统和/或处理器版本而不同,本领域技术人员可依实际情况撰写对应的代码。[0194]图16是依据本发明第三实施例所述的处理接收指令的流程图。图16的步骤s1605、s1610、s1625与第二实施例的图13的步骤s1305、s1310、s1325相同,此处就不赘述了。下面描述步骤s1620。[0195]请参照图11、图15a~15b和图16,图16所示的处理流程,可由图11的处理器1100执行。在步骤s1620中,处理器1100处理上述接收指令。具体而言,当上述接收指令为未知指令时,在处理未知指令异常的微码处理程序中,处理器1100是通过操作系统120的内核驱动程序150,调用转换程序145对上述接收指令进行处理的。需要说明的是,相较于本实施例,在上述第二实施例的图13的步骤s1320中,当上述接收指令为未知指令时,在处理未知指令异常的微码处理程序中,处理器1100是直接通过转换程序145对上述接收指令进行处理的。[0196]在一实施例中,转换程序145为上述操作系统120的一驱动程序或应用程序。第三实施例中的其它处理流程均与第二实施例相同,此处就不赘述了。[0197]综上所述,与第二实施例不同的是,在本实施例(第三实施例)中,当处理器1100执行到一未知指令时,处理未知指令异常的微码处理程序执行操作系统120的内核驱动程序150,以接续处理可转换的新增指令。与第二实施例相比,在本实施例中,使用操作系统的内核驱动程序通过转换程序转换新增指令,与更新处理器的硬件和/或处理器中的微码相比,更新内核驱动程序和转换程序更加方便、快捷,从而提高了开发效率。[0198][第四实施例][0199]图17是显示根据本发明第四实施例所述的执行新增指令的系统1700的示意图。与第三实施例相同,在本实施例(第四实施例)中,执行新增指令的系统1700中的转换程序145也由操作系统120中的内核驱动程序150所运行。不同之处是,在本实施例中,转换程序145运行于一专用处理核心190上。内核驱动程序150通过轮询(polling)或门铃(doorbell)机制将未知指令132的信息和运行环境信息发送给转换程序145。转换程序145也需要通过轮询或门铃机制,把转换结果发送给内核驱动程序150。下面将分别描述具体是如何通过轮询或门铃机制在内核驱动程序150和转换程序145之间传输数据的。[0200]下面先描述轮询机制。请参照图11与图17,在一实施例中,处理器1100的设计者可在处理器1100的非核心(uncore)中设置一传输寄存器(未绘示),用于存放未知指令132的信息、运行环境信息、一传输信息标识和一传输结果标识(皆未绘示于图17中),其中,传输信息标识和传输结果标识的默认值都为第二数值。内核驱动程序150将未知指令132的信息和运行环境信息存入上述传输寄存器,并将值为第一数值的传输信息标识存入上述传输寄存器。然后,内核驱动程序150每隔固定的时间(比如每隔100毫秒)就去读取传输寄存器中的传输结果标识,以等待接收转换结果。如果读取到传输结果标识为第一数值,表示转换程序145已经生成了转换结果,内核驱动程序150将从传输寄存器读取转换结果。另外,运行于专用处理核心190上的转换程序145被设置为,当空闲时,每隔固定的时间(比如每隔100毫秒)就去查看传输寄存器中的传输信息标识是否为第一数值。如果传输寄存器中的传输信息标识为第一数值,转换程序145从上述传输寄存器读取未知指令132的信息和运行环境信息,然后将传输寄存器中的传输信息标识设置为第二数值。然后,转换程序145按前文所述的方法对未知指令132进行转换处理,生成转换结果。然后,转换程序145将上述转换结果存入传输寄存器中,并将值为第一数值的传输结果标识存入传输寄存器。如前所述,由于传输结果标识为第一数值,内核驱动程序150会从传输寄存器读取转换结果,并将传输寄存器中的传输结果标识设置为第二数值。至此,内核驱动程序150和转换程序145之间就完成了一次数据传输。在另一实施例中,于多核心处理器架构下,还需要把处理核心的编号存入传输寄存器中或者在传输寄存器中为每个处理核心分配专用的存储空间,以使得运行于每个处理核心上的内核驱动程序150都可以与转换程序145进行数据传输。[0201]下面描述门铃机制。同样参照图11与图17,在一实施例中,处理器1100的设计者可在处理器1100的非核心中设置一传输寄存器(未绘示),用于存放未知指令132的信息和运行环境信息(皆未绘示于图17中)。内核驱动程序150将未知指令132的信息和运行环境信息存入上述传输寄存器之后,通过中断的方式通知运行于专用处理器190上的转换程序145。响应于上述中断,转换程序145从上述传输寄存器读取未知指令132的信息和运行环境信息,并生成转换结果。然后,转换程序145将转换结果存入传输寄存器,并通过中断的方式通知内核驱动程序150。响应于上述中断,内核驱动程序150从传输寄存器读取转换结果。至此,内核驱动程序150和转换程序145之间就完成了一次数据传输。至于如何设置中断,比如分别为内核驱动程序150和转换程序145自行定义中断服务程序、并自行定义各自对应的中断向量号,前文已经做了描述,此处就不赘述了。在另一实施例中,也可以单独为处理器1100和/或专用处理器190添加一硬件中断信号线(pin),内核驱动程序150和/或转换程序145可通过上述硬件中断信号线触发中断,以完成数据传输。[0202]本实施例中的其它处理流程均与第三实施例相同,此处就不赘述了。[0203]在另一实施例中,前述第一实施例、第二实施例以及第四实施例中所描述的转换程序145的功能,可以实现于一硬件电路中。[0204]由上可知,与第三实施例相同,在本实施例中,也是通过操作系统120的内核驱动程序150实现对新增指令的转换的。与第三实施例不同的是,在本实施例中,转换程序145运行于专用处理核心190之上。在本实施例中,由于转换程序145运行于专用处理核心190之上,因而执行速度较快;另外,由于不需要在每个处理核心中都运行一个转换程序145,从而减轻了处理器的其它处理核心的工作负担。[0205]图18是显示根据本发明一实施例所述的执行新增指令的流程图。请同时参照图11、17、18,由上述对第三实施例和本实施例的描述可知,处理器1100接收一指令(s1805),当上述接收指令为未知指令时,处理器1100通过操作系统120执行一转换程序(s1810)。在上述转换程序中,判断上述接收指令是否为新增指令(s1815),以及当上述接收指令为新增指令时,将上述接收指令转换为至少一个旧指令(s1820)。最后,处理器1100执行上述至少一个旧指令(s1825)。图18的步骤s1805、s1815、s1820、s1825已在第一实施例中做了详细描述,此处就不赘述了。下面描述步骤s1810。[0206]在步骤s1810中,当上述接收指令为未知指令时,处理器1100通过操作系统执行一转换程序。具体而言,如前对第三实施例和本实施例的描述可知,当上述接收指令为未知指令时,指令提交单元245会发出一未知指令异常。响应于上述未知指令异常,处理器1100执行未知指令异常的微码处理程序。在未知指令异常的微码处理程序中,调用操作系统的内核驱动程序150。操作系统的内核驱动程序150再调用转换程序145。[0207]图19是显示根据本发明一实施例所述的执行新增指令的流程图。请同时参照图11、17、19,由上述对第一实施例、第二实施例、第三实施例和本实施例的描述可知,处理器1100接收一指令(s1905),当上述接收指令为未知指令时,处理器1100启动一转换程序(s1910)。在上述转换程序中,判断上述接收指令是否为新增指令(s1915),以及当上述接收指令为新增指令时,将上述接收指令转换为至少一个旧指令(s1920)。最后,处理器1100通过执行上述至少一个旧指令,来模拟上述接收指令的执行(s1925)。图19的步骤s1905、s1915、s1920、s1925已在第一实施例中做了详细描述,此处就不赘述了。下面描述步骤s1910。[0208]在步骤s1910中,当上述接收指令为未知指令时,处理器1100启动一转换程序。具体而言,如前对第一实施例、第二实施例、第三实施例和本实施例的描述可知,当上述接收指令为未知指令时,指令提交单元245会发出一未知指令异常。响应于上述未知指令异常,处理器1100执行未知指令异常的微码处理程序。[0209]特别说明的是,在第一实施例中,未知指令异常的微码处理程序发出一系统管理中断(#smi)。响应于上述系统管理中断,处理器1100进入系统管理模式。在系统管理模式中,启动模拟器142,并由模拟器142启动转换程序145。在第二实施例中,未知指令异常的微码处理程序直接启动转换程序145。在第三实施例和本实施例中,未知指令异常的微码处理程序调用操作系统120的内核驱动程序150。然后操作系统120的内核驱动程序150再调用转换程序145。[0210]图20是显示根据本发明一实施例所述的转换新增指令的流程图。请同时参照图11、17、20,由上述对第一实施例、第二实施例、第三实施例和本实施例的描述可知,转换程序145接收一指令,其中上述指令为未知指令(s2005),判断上述接收指令是否为新增指令(s2010)。当上述接收指令为新增指令时,转换程序145将上述接收指令转换为至少一个旧指令(s2015)。在前文中,已经对图20的步骤s2005、s2010以及s2015做了详细描述,此处就不赘述了。[0211]对于本发明已描述的实施例,下文描述了可以实现本发明实施例的示例性操作环境。具体参考图21,图21是显示用以实现本发明实施例的示例性操作环境,一般可被视为计算装置2100。计算装置2100仅为一合适计算环境的一个示例,并不意图暗示对本发明使用或功能范围的任何限制。计算装置2100也不应被解释为具有与所示元件任一或组合相关任何的依赖性或要求。[0212]可在计算机或机器中使用指令来执行本发明,指令可为程序模块的计算机可执行指令,程序模块由计算机或其它机器,例如个人数字助理或其它可携式装置执行。一般而言,程序模块包括例程、程序、物件、元件、数据结构等,程序模块指的是执行特定任务或实现特定抽象数据类型的程序码。本发明可在各种系统配置中实现,包括可携式装置、消费者电子产品、通用计算机、更专业的计算装置等。本发明还可在分散式运算环境中实现,处理由通讯网络所连结的装置。[0213]请参考图21。计算装置2100包括直接或间接耦接以下装置的总线2110、内存2112、一或多个处理器2114、一或多个显示元件2116、输入/输出(i/o)端口2118、输入/输出(i/o)元件2120以及电源供应器2122。总线2110可为一或多个总线的元件(例如,地址总线、数据总线或其组合)。虽然图21的各个方块为简要起见以线示出,实际上,各个元件的分界并不是具体的,例如,可将显示装置的呈现元件视为i/o元件;处理器可具有内存。[0214]计算装置2100一般包括各种计算机可读取介质。计算机可读取介质可以是可被计算装置2100存取的任何可用介质,该介质同时包括易失性和非易失性介质、可移动和不可移动介质。举例但不局限于,计算机可读取介质可包括计算机储存介质和通讯介质。计算机可读取介质同时包括在用于储存像是计算机可读取指令、数据结构、程序模块或其它数据之类信息的任何方法或技术中实现的易失性和非易失性介质、可移动和不可移动介质。计算机储存介质包括但不局限于随机存取内存(randomaccessmemory,ram)、只读内存(read-onlymemory,rom)、电子抹除式可复写只读内存(electrically-erasableprogrammableread-onlymemory,eeprom)、快闪内存或其它内存技术、cd-rom、数字多功能光盘(dvd)或其它光盘储存装置、磁片、磁盘、磁片储存装置或其它磁储存装置,或可用于储存所需的信息并且可被计算装置2100存取的其它任何介质。计算机储存介质本身不包括信号。[0215]通讯介质一般包含计算机可读取指令、数据结构、程序模块或其它采用诸如载波或其他传输机制之类的模块化数据信号形式的数据,并包括任何信息传递介质。术语“模块化数据信号”是指具有一或多个特征集合或以在信号中编码信息之一方式更改的信号。举例但不局限于,通讯介质包括像是有线网络或直接有线连接的有线介质及无线介质,像是声频、射频、红外线以及其它无线介质。上述介质的组合包括在计算机可读取介质的范围内。[0216]内存2112包括以易失性和非易失性内存形式的计算机储存介质。内存可为可移动、不移动或可以为这两种的组合。示例性硬件装置包括固态内存、硬盘驱动器、光盘驱动器等。第一实施例中的系统管理内存位于内存2112中。[0217]计算装置2100包括一或多个处理器2114,其读取来自像是内存2112或i/o元件2120各实体的数据。显示元件2116向使用者或其它装置显示数据指示。示例性显示元件包括显示装置、扬声器、打印元件、振动元件等。[0218]i/o端口2118允许计算装置2100逻辑连接到包括i/o元件2120的其它装置,一些此种装置为内建装置。示例性元件包括麦克风、摇杆、游戏台、盘形卫星信号接收器、扫描器、打印机、无线装置等。i/o元件2120可提供一自然使用者接口(naturaluserinterface,nui),用于处理使用者生成的姿势、声音或其它生理输入。在一些例子中,这些输入可被传送到一合适的网络元件以便进一步处理。自然使用者接口可实现语言识别、触摸与手写笔辨识、面部识别、生物识别、在屏幕上以及邻近屏幕的姿势识别、空中手势、头部及眼部追踪以及与计算装置2100所显示相关联的触摸识别的任意组合。计算装置2100可装备有深度照相机,像是立体照相机系统、红外线照相机系统、rgb照相机系统和这些系统的组合,以侦测与识别姿势。另外,计算装置2100可以装备有侦测运动的加速度计或陀螺仪。加速度计或陀螺仪的输出可被提供给计算装置2100显示以呈现沉浸式增强现实或虚拟实境。[0219]此外,计算装置2100中的处理器2114也可执行内存2112中的程序及指令以呈现上述实施例所述的动作和步骤,或其它在说明书中描述的内容。[0220]在此所公开程序的任何具体顺序或分层的步骤纯为一举例的方式。基于设计上的偏好,必须了解到程序上的任何具体顺序或分层的步骤可在此文件所公开的范围内被重新安排。伴随的方法权利要求以一示例顺序呈现出各种步骤的元件,也因此不应被此所展示的特定顺序或阶层所限制。[0221]权利要求中用以修饰元件的“第一”、“第二”、“第三”等序数词的使用本身未暗示任何优先权、优先次序、各元件之间的先后次序、或方法所执行的步骤的次序,而仅用作标识来区分具有相同名称(具有不同序数词)的不同元件。[0222]通过本发明提供的执行新增指令的方法与执行新增指令的系统,在不对处理核心的硬件架构进行修改的情况下,就可以在前代处理器上执行新增指令。[0223]以上所述仅为本发明较佳实施例,然其并非用以限定本发明的范围,任何熟悉本项技术的人员,在不脱离本发明的精神和范围内,可在此基础上做进一步的改进和变化,因此本发明的保护范围当以本技术的权利要求书所界定的范围为准。当前第1页12当前第1页12

再多了解一些

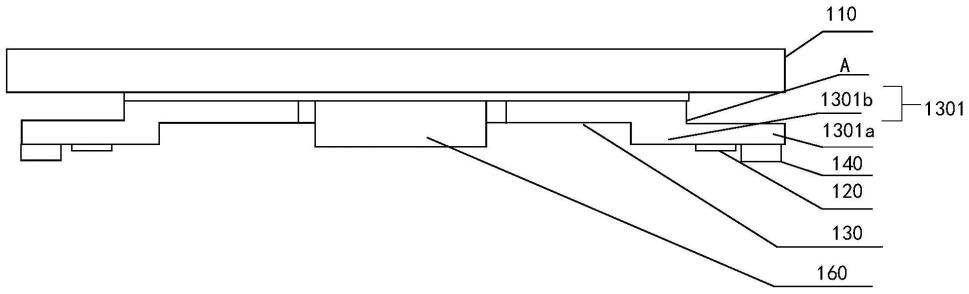

本文用于企业家、创业者技术爱好者查询,结果仅供参考。