1.本发明涉及射频脉冲信号源产生电路技术领域,特别涉及一种射频脉冲信号源产生电路。

背景技术:

2.现有通过使用三级负压控制的可变增益放大器进行脉冲调制,这样首先需要对脉冲进行反相调制,不仅电路复杂,而且调制深度不够。

技术实现要素:

3.本发明所要解决的技术问题是:提供一种射频脉冲信号源产生电路,实现对连续波的高抑制度。

4.为了解决上述技术问题,本发明采用的技术方案为:

5.一种射频脉冲信号源产生电路,包括频率源模块、射频开关模块、压控增益可调模块、数控衰减模块和主控模块,所述主控模块分别与频率源模块和数控衰减模块电连接,所述压控增益可调模块分别与射频开关模块和数控衰减模块电连接,所述射频开关模块与频率源模块电连接。

6.本发明的有益效果在于:

7.频率源模块与主控模块电连接,频率源模块与主控模块通信,获取相对应的频率设置码,频率源模块根据从主控模块获取的数据,设置频率源模块相对应的寄存器,频率源模块可以产生相应频率,当功率大小在一定范围内可以设置的连续波信号;设置射频开关模块和压控增益可调模块用以实现信号的脉冲调制,周期性的脉冲信号进入射频开关模块实现询问信号的分时通断,经过射频开关模块调制后的信号继续送入压控增益可调模块,调节其输出波形,隔离连续波,调节调制深度,最后把调制好的射频信号送入数控衰减模块,实现送入接收机的功率大小可控的目的,进而实现对连续波的高抑制度。

附图说明

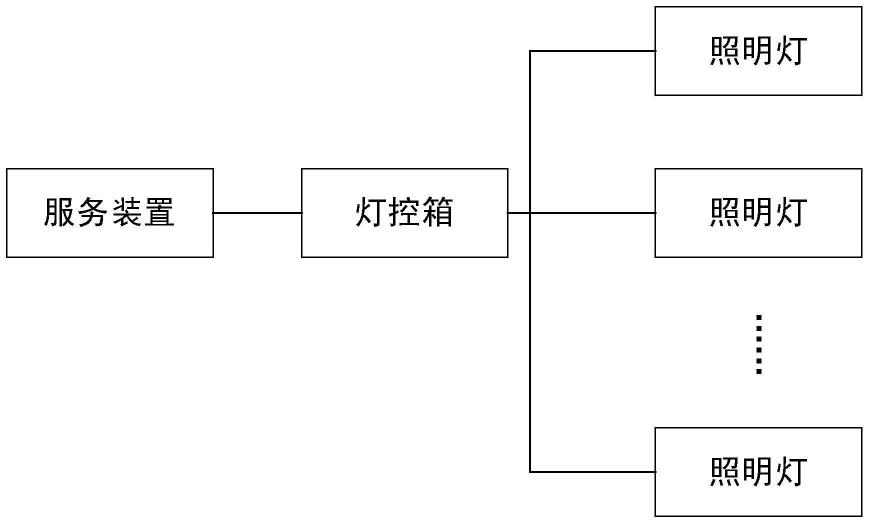

8.图1为根据本发明的一种射频脉冲信号源产生电路的模块连接框图;

9.图2为根据本发明的一种射频脉冲信号源产生电路的频率源模块的电路原理图;

10.图3为根据本发明的一种射频脉冲信号源产生电路的射频开关模块、压控增益可调模块和数控衰减模块的电路原理图;

11.图4为根据本发明的一种射频脉冲信号源产生电路的主控模块的电路原理图;

12.标号说明:

13.1、频率源模块;2、射频开关模块;3、压控增益可调模块;4、数控衰减模块;5、主控模块。

具体实施方式

14.为详细说明本发明的技术内容、所实现目的及效果,以下结合实施方式并配合附图予以说明。

15.请参照图1,本发明提供的技术方案:

16.一种射频脉冲信号源产生电路,包括频率源模块、射频开关模块、压控增益可调模块、数控衰减模块和主控模块,所述主控模块分别与频率源模块和数控衰减模块电连接,所述压控增益可调模块分别与射频开关模块和数控衰减模块电连接,所述射频开关模块与频率源模块电连接。

17.从上述描述可知,本发明的有益效果在于:

18.频率源模块与主控模块电连接,频率源模块与主控模块通信,获取相对应的频率设置码,频率源模块根据从主控模块获取的数据,设置频率源模块相对应的寄存器,频率源模块可以产生相应频率,当功率大小在一定范围内可以设置的连续波信号;设置射频开关模块和压控增益可调模块用以实现信号的脉冲调制,周期性的脉冲信号进入射频开关模块实现询问信号的分时通断,经过射频开关模块调制后的信号继续送入压控增益可调模块,调节其输出波形,隔离连续波,调节调制深度,最后把调制好的射频信号送入数控衰减模块,实现送入接收机的功率大小可控的目的,进而实现对连续波的高抑制度。

19.进一步的,所述频率源模块包括芯片n3,所述芯片n3的型号为adf4350,所述芯片n3的第十二引脚和芯片n3的第十三引脚均分别与射频开关模块电连接。

20.由上述描述可知,频率源模块通过芯片n3结合外部环路滤波器和外部基准频率,实现小数n分频锁相(pll)频率合成。外部基准频率采用13mhz有源晶振。寄存器参数通过spi接口进行设置。

21.进一步的,所述射频开关模块包括电阻r1、电阻r2、电容c1、电容c6、电容c7、接插件x2、接插件x4和芯片s1,所述芯片s1的第二引脚与芯片s1的第三引脚电连接且芯片s1的第二引脚和芯片s1的第三引脚均接地,所述芯片s1的第五引脚与电容c1的一端电连接,所述电容c1的另一端与频率源模块电连接,所述芯片s1的第六引脚与电阻r1的一端电连接,所述电阻r1的另一端分别与电容c8的一端和接插件x2电连接,所述芯片s1的第七引脚与电阻r2的一端电连接,所述电阻r2的另一端与接插件x4电连接,所述芯片s1的第八引脚与电容c7的一端电连接,所述电容c7的另一端与压控增益可调模块电连接。

22.由上述描述可知,射频开关模块包括电阻r1、电阻r2、电容c1、电容c6、电容c7、接插件x2、接插件x4和芯片s1,射频开关模块应用脉冲信号对频率源模块产生的连续波进行开关控制。

23.进一步的,所述压控增益可调模块包括电阻r9、电阻r10、电阻r13、电容c9、电容c13、电容c14、电容c15、电容c16、电容c17、电感l1、电感l2、接插件x5和芯片n1,所述芯片n1的第一引脚分别与电容c9的一端和电感l1的一端电连接,所述电感l1的另一端与芯片n1的第九引脚电连接,所述芯片n1的第三引脚与电阻r9的一端电连接,所述的电阻r9的另一端分别与电阻r13的一端、电容c14的一端、电容c15的一端、电容c16的一端和电感l2的一端电连接,所述电感l2的另一端分别与电容c17的一端和芯片n1的第六引脚电连接,所述电容c14的另一端分别与电容c15的另一端和电容c16的另一端电连接且电容c14的另一端、电容c15的另一端和电容c16的另一端均接地,所述电容c17的另一端与数控衰减模块电连接,所

述芯片n1的第七引脚与电阻r10的一端电连接,所述电阻r10的另一端分别与电容c13的一端和接插件x5电连接,所述芯片n1的第八引脚与电容c13的另一端电连接且芯片n1的第八引脚和电容c13的另一端均接地。

24.由上述描述可知,压控增益可调模块通过在芯片n1的第七引脚上应用脉冲信号,实现射频功率的脉冲调制。

25.进一步的,所述数控衰减模块包括电阻r3、电阻r4、电阻r5、电阻r6、电阻r7、电阻r8、电阻r11、电阻r12、电阻r14、电阻r15、电阻r17、电阻r18、电阻r19、电阻r20、稳压管v1、稳压管v2、稳压管v3、稳压管v4、稳压管v5、稳压管v6、反相器d2d、反相器d2e、反相器d2f、反相器d2c、反相器d2b、反相器d2a、电容c10、电容c11、电容c18、接插件xs1、芯片d1和芯片d3;

26.所述芯片d1的第一引脚分别与电阻r3的一端、芯片d1的第二引脚、芯片d1的第四引脚、芯片d1的第六引脚和芯片d1的第七引脚,所述芯片d1的第三引脚接地,所述芯片d1的第五引脚接地,所述电阻r3的另一端与反相器d2d输出端电连接,所述反相器d2d的输入端与稳压管v1的阳极电连接,所述稳压管v1的阴极与主控模块电连接,所述芯片d1的第九引脚分别与芯片d1的第十引脚、芯片d1的第十七引脚和电阻r11的一端电连接,所述芯片d1的第十一引脚分别与电阻r11的另一端和电容c12的一端电连接,所述电容c12的另一端与芯片d3的第十四引脚电连接,所述芯片d1的第十二引脚与芯片d1的第十三引脚电连接且均接地,所述芯片d1的第十四引脚与电容c11的一端电连接,所述电容c11的另一端分别与电阻r6的一端和电阻r4的一端电连接,所述电阻r4的另一端分别与电阻r7的一端和电容c10的一端电连接,所述电容c10的另一端与接插件xs1的第一引脚电连接,所述接插件xs1的第二引脚、接插件xs1的第三引脚、接插件xs1的第四引脚和接插件xs1的第五引脚均接地,所述电阻r6的另一端与电阻r7的另一端电连接且电阻r6的另一端和电阻r7的另一端均接地,所述芯片d1的第十五引脚与芯片d1的第十六引脚电连接且均接地;

27.所述芯片d3的第一引脚与电阻r5的一端电连接,所述电阻r5的另一端与反相器d2e的输出端电连接,所述反相器d2e的输入端与稳压管v2的阳极电连接,所述稳压管v2的阴极与主控模块电连接,所述芯片d3的第二引脚与电阻r8的一端电连接,所述电阻r8的另一端与反相器d2f的输出端电连接,所述反相器d2f的输入端与稳压管v3的阳极电连接,所述稳压管v3的阴极与主控模块电连接,所述芯片d3的第三引脚接地,所述芯片d3的第四引脚与电阻r12的一端电连接,所述电阻r12的另一端与反相器d2c的输出端电连接,所述反相器d2c的输入端与稳压管v4的阳极电连接,所述稳压管v4的阴极与与主控模块电连接,所述芯片d3的第五引脚接地,所述芯片d3的第六引脚与电阻r14的一端电连接,所述电阻r14的另一端与反相器d2b的输出端电连接,所述反相器d2b的输入端与稳压管v5的阳极电连接,所述稳压管v5的阴极与主控模块电连接,所述芯片d3的第七引脚与电阻r15的一端电连接,所述电阻r15的另一端与反相器d2a的输出端电连接,所述反相器d2a的输入端与稳压管v6的阳极电连接,所述稳压管v6的阴极与主控模块电连接,所述芯片d3的第九引脚分别与芯片d3的第十引脚、芯片d3的第十七引脚和电阻r19的一端电连接且芯片d3的第九引脚、芯片d3的第十引脚、芯片d3的第十七引脚和电阻r19的一端均接地,所述芯片d3的第十一引脚分别与电阻r19的另一端和电容c18的一端电连接,所述电容c18的另一端分别与电阻r17的一端和电阻r18的一端电连接,所述电阻r17的另一端分别与电阻r20的一端和压控增益可调模块电连接。

28.由上述描述可知,数控衰减模块将主控模块输入的i/o电平进行反相后,施加到芯片d1和芯片d3的第一引脚、第二引脚、第四引脚、第六引脚和第七引脚上,最终实现对输出功率值的调整。

29.进一步的,所述主控模块包括芯片n5,所述芯片n5的型号为stm32f103,所述芯片n5的第十四引脚、芯片n5的第十五引脚、芯片n5的第十六引脚、芯片n5的第十七引脚和芯片n5的第三十二引脚均分别与射频开关模块电连接,所述芯片n5的第二十五引脚、芯片n5的第二十六引脚、芯片n5的第二十七引脚、芯片n5的第二十八引脚和芯片n5的第二十九引脚均分别与数控衰减模块电连接。

30.从上述描述可知,主控模块通过芯片n5的第十四引脚、第十五引脚、第十六引脚和第十七引脚对频率源模块进行参数设定,同时通过i/o接口对数控衰减模块的衰减量进行控制。

31.请参照图1至图4,本发明的实施例一为:

32.请参照图1,一种射频脉冲信号源产生电路,包括频率源模块1、射频开关模块2、压控增益可调模块3、数控衰减模块4和主控模块5,所述主控模块5分别与频率源模块1和数控衰减模块4电连接,所述压控增益可调模块3分别与射频开关模块2和数控衰减模块4电连接,所述射频开关模块2与频率源模块1电连接。

33.请参照图2,所述频率源模块1包括芯片n3,所述芯片n3的型号为adf4350,所述芯片n3的第十二引脚和芯片n3的第十三引脚均分别与射频开关模块2电连接。

34.所述频率源模块1还包括电阻r21(电阻值为2kω)、电阻r23(电阻值为2kω)、电容c33(电容值为1μf)、电容c34(电容值为0.01μf)、电阻r24(电阻值为0ω)、电容c35(电容值为1nf)、电容c36(电容值为1nf)、接插件n4、电容c26(电容值为0.1μf)、电容c25(电容值为0.1μf)、电容c27(电容值为10pf)、电容c28(电容值为10pf)、电阻r22(电阻值为4.7kω)、电阻r25(电阻值为1kω)、发光二极管h1、电阻r27(电阻值为0ω)、电阻r26(电阻值为330ω)、电阻r28(电阻值为100ω)、电容c37(电容值为22nf)、电容c38(电容值为680nf)、电容c39(电容值为680pf)、电阻r29(电阻值为120ω)、电阻r30(电阻值为0ω)、电容c44(电容值为10pf)、电容c45(电容值为0.1μf)、电容c42(电容值为10pf)、电容c43(电容值为0.1μf)、电容c40(电容值为10pf)、电容c41(电容值为0.1μf)、电容c46(电容值为2.2pf)、电感l3(电感值为12nh)、电感l4(电感值为12nh)、电感l5(电感值为39nh)、电容c49(电容值为2.2pf)、电容c47(电容值为10pf)、电容c48(电容值为100pf)、电容c52(电容值为10pf)、电容c55(电容值为0.1μf)、电容c50(电容值为10pf)、电容c53(电容值为0.1μf)、电容c51(电容值为10pf)和电容c54(电容值为0.1μf),其各元器件之间的具体连接关系请参照图2;

35.请参照图3,所述射频开关模块2包括电阻r1(电阻值为0ω)、电阻r2(电阻值为0ω)、电容c1(电容值为330pf)、电容c6(电容值为1nf)、电容c7(电容值为330pf)、接插件x2、接插件x4和芯片s1(型号为hmc1055),所述芯片s1的第二引脚与芯片s1的第三引脚电连接且芯片s1的第二引脚和芯片s1的第三引脚均接地,所述芯片s1的第五引脚与电容c1的一端电连接,所述电容c1的另一端与频率源模块1电连接,所述芯片s1的第六引脚与电阻r1的一端电连接,所述电阻r1的另一端分别与电容c8的一端和接插件x2电连接,所述芯片s1的第七引脚与电阻r2的一端电连接,所述电阻r2的另一端与接插件x4电连接,所述芯片s1的第八引脚与电容c7的一端电连接,所述电容c7的另一端与压控增益可调模块3电连接。

36.请参照图3,所述压控增益可调模块3包括电阻r9(电阻值为1kω)、电阻r10(电阻值为0ω)、电阻r13(电阻值为0ω)、电容c9(电容值为2.2nf)、电容c13(电容值为200pf)、电容c14(电容值为2.2μf)、电容c15(电容值为0.1μf)、电容c16(电容值为10pf)、电容c17(电容值为100pf)、电感l1(电感值为82nh)、电感l2(电感值为82nh)、接插件x5和芯片n1(型号为alm80110),所述芯片n1的第一引脚分别与电容c9的一端和电感l1的一端电连接,所述电感l1的另一端与芯片n1的第九引脚电连接,所述芯片n1的第三引脚与电阻r9的一端电连接,所述的电阻r9的另一端分别与电阻r13的一端、电容c14的一端、电容c15的一端、电容c16的一端和电感l2的一端电连接,所述电感l2的另一端分别与电容c17的一端和芯片n1的第六引脚电连接,所述电容c14的另一端分别与电容c15的另一端和电容c16的另一端电连接且电容c14的另一端、电容c15的另一端和电容c16的另一端均接地,所述电容c17的另一端与数控衰减模块4电连接,所述芯片n1的第七引脚与电阻r10的一端电连接,所述电阻r10的另一端分别与电容c13的一端和接插件x5电连接,所述芯片n1的第八引脚与电容c13的另一端电连接且芯片n1的第八引脚和电容c13的另一端均接地。

37.请参照图3,所述数控衰减模块4包括电阻r3(电阻值为100ω)、电阻r4(电阻值为5.6ω)、电阻r5(电阻值为100ω)、电阻r6(电阻值为910ω)、电阻r7(电阻值为910ω)、电阻r8(电阻值为100ω)、电阻r11(电阻值为4.7kω)、电阻r12(电阻值为100ω)、电阻r14(电阻值为100ω)、电阻r15(电阻值为100ω)、电阻r17(电阻值为5.6kω)、电阻r18(电阻值为910ω)、电阻r19(电阻值为4.7kω)、电阻r20(电阻值为910ω)、稳压管v1、稳压管v2、稳压管v3、稳压管v4、稳压管v5、稳压管v6、反相器d2d(型号为snj54lso4fk)、反相器d2e(型号为snj54lso4fk)、反相器d2f(型号为snj54lso4fk)、反相器d2c(型号为snj54lso4fk)、反相器d2b(型号为snj54lso4fk)、反相器d2a(型号为snj54lso4fk)、电容c10(电容值为2200pf)、电容c11(电容值为2200pf)、电容c18(电容值为2200pf)、接插件xs1(型号为sma-khd)、芯片d1(型号为hmc307)和芯片d3(型号为hmc307);

38.所述芯片d1的第一引脚分别与电阻r3的一端、芯片d1的第二引脚、芯片d1的第四引脚、芯片d1的第六引脚和芯片d1的第七引脚,所述芯片d1的第三引脚接地,所述芯片d1的第五引脚接地,所述电阻r3的另一端与反相器d2d输出端电连接,所述反相器d2d的输入端与稳压管v1的阳极电连接,所述稳压管v1的阴极与主控模块5电连接,所述芯片d1的第九引脚分别与芯片d1的第十引脚、芯片d1的第十七引脚和电阻r11的一端电连接,所述芯片d1的第十一引脚分别与电阻r11的另一端和电容c12的一端电连接,所述电容c12的另一端与芯片d3的第十四引脚电连接,所述芯片d1的第十二引脚与芯片d1的第十三引脚电连接且均接地,所述芯片d1的第十四引脚与电容c11的一端电连接,所述电容c11的另一端分别与电阻r6的一端和电阻r4的一端电连接,所述电阻r4的另一端分别与电阻r7的一端和电容c10的一端电连接,所述电容c10的另一端与接插件xs1的第一引脚电连接,所述接插件xs1的第二引脚、接插件xs1的第三引脚、接插件xs1的第四引脚和接插件xs1的第五引脚均接地,所述电阻r6的另一端与电阻r7的另一端电连接且电阻r6的另一端和电阻r7的另一端均接地,所述芯片d1的第十五引脚与芯片d1的第十六引脚电连接且均接地;

39.所述芯片d3的第一引脚与电阻r5的一端电连接,所述电阻r5的另一端与反相器d2e的输出端电连接,所述反相器d2e的输入端与稳压管v2的阳极电连接,所述稳压管v2的阴极与主控模块5电连接,所述芯片d3的第二引脚与电阻r8的一端电连接,所述电阻r8的另

一端与反相器d2f的输出端电连接,所述反相器d2f的输入端与稳压管v3的阳极电连接,所述稳压管v3的阴极与主控模块5电连接,所述芯片d3的第三引脚接地,所述芯片d3的第四引脚与电阻r12的一端电连接,所述电阻r12的另一端与反相器d2c的输出端电连接,所述反相器d2c的输入端与稳压管v4的阳极电连接,所述稳压管v4的阴极与与主控模块5电连接,所述芯片d3的第五引脚接地,所述芯片d3的第六引脚与电阻r14的一端电连接,所述电阻r14的另一端与反相器d2b的输出端电连接,所述反相器d2b的输入端与稳压管v5的阳极电连接,所述稳压管v5的阴极与主控模块5电连接,所述芯片d3的第七引脚与电阻r15的一端电连接,所述电阻r15的另一端与反相器d2a的输出端电连接,所述反相器d2a的输入端与稳压管v6的阳极电连接,所述稳压管v6的阴极与主控模块5电连接,所述芯片d3的第九引脚分别与芯片d3的第十引脚、芯片d3的第十七引脚和电阻r19的一端电连接且芯片d3的第九引脚、芯片d3的第十引脚、芯片d3的第十七引脚和电阻r19的一端均接地,所述芯片d3的第十一引脚分别与电阻r19的另一端和电容c18的一端电连接,所述电容c18的另一端分别与电阻r17的一端和电阻r18的一端电连接,所述电阻r17的另一端分别与电阻r20的一端和压控增益可调模块3电连接。

40.请参照图4,所述主控模块5包括芯片n5(型号为stm32f103),所述芯片n5的型号为stm32f103,所述芯片n5的第十四引脚、芯片n5的第十五引脚、芯片n5的第十六引脚、芯片n5的第十七引脚和芯片n5的第三十二引脚均分别与射频开关模块2电连接,所述芯片n5的第二十五引脚、芯片n5的第二十六引脚、芯片n5的第二十七引脚、芯片n5的第二十八引脚和芯片n5的第二十九引脚均分别与数控衰减模块4电连接。

41.所述主控模块5还包括电容c57(电容值为22pf)、晶振n6(频率为12mhz)、电容c62(电容值为22pf)、电容c61(电容值为0.1μf)、电容c63(电容值为0.1μf)、电容c64(电容值为0.01μf)、电容c65(电容值为0.1μf)、开关s2(型号为td-13xax-a00)、电容c58(电容值为10μf)、电容c59(电容值为0.1μf)、电阻r31(电阻值为10kω)、接插件xs2、电容c60(电容值为0.1μf)、电容c67(电容值为30pf)、电容c68(电容值为30pf)、电容c69(电容值为30pf)、电容c70(电容值为30pf)、电阻r33(电阻值为10kω)、电容c66(电容值为0.1μf)和接插件rn1,其各元器件之间的具体连接关系请参照图4。

42.所述数控衰减模块4包括前端电阻衰减网络、反相器芯片、可控衰减器芯片和级间电阻衰减网络,采用两个5位可控衰减器芯片结合微处理器的控制信号实现,可以实现射频信号的峰值调整,可控衰减芯片(即芯片d1和芯片d3)的衰减码由主控模块5的芯片n5提供,使用的两片hmc307型号的芯片,一片实现5位衰减值分别是:16db、8db、4db、2db和1db,另一片5位级联实现31db的衰减值,因此最大可以实现的衰减值范围为62db。

43.本方案通过串口通信从上位机获取当前所需的工作频率及信号大小信息,并转换成相应的频率码和衰减码,分别送至频率合成器芯片(即芯片n3)和可控衰减器芯片(即芯片d1和芯片d3),频率合成器芯片根据频率码产生一定频率的连续射频信号,送至有钟形脉冲控制的射频开关芯片(即芯片s1),经开关调制后再送入由钟形脉冲控制的可变增益放大器。经过两级调制后,再送入衰减器,对信号的输出幅度进行控制,以产生适当的模拟测距询问信号。

44.可控衰减器芯片的衰减值的设定,同样是由主控模块5的芯片n5来设定,频率合成器芯片(即芯片n3)结合外部环路滤波器和外部基准频率使用时,可以实现小数n分频或整

数n分频锁相(pll)频率合成器。基准频率采用13mhz有源晶振。芯片中的rf n分频器可以在pll反馈路径中提供一个分频比,分频比由构成此分频器的int、frac和mod的值决定;频率合成器芯片(即芯片n3)的输出为差分结构,利用分立电感元件可以实现巴伦结构。

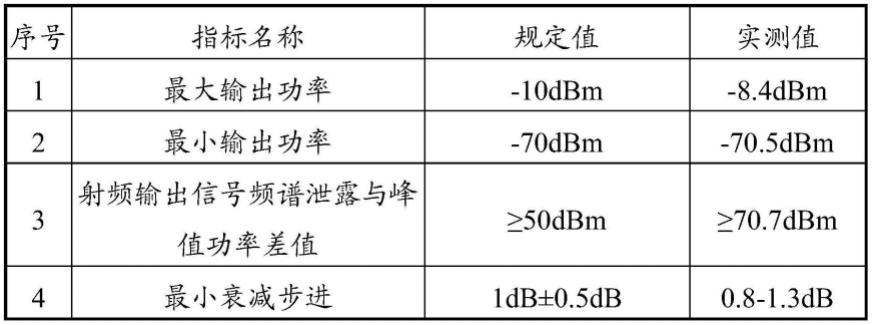

45.通过采用本方案设计的射频脉冲信号源产生电路的指标测试表如表1:

[0046][0047]

表1

[0048]

从表1可以看出,本方案设计的射频脉冲信号源产生电路,其输出脉冲信号幅度在-70.5dbm至-8.4dbm之间可调,连续波抑制大于70db。

[0049]

综上所述,本发明提供的一种射频脉冲信号源产生电路,频率源模块与主控模块电连接,频率源模块与主控模块通信,获取相对应的频率设置码,频率源模块根据从主控模块获取的数据,设置频率源模块相对应的寄存器,频率源模块可以产生相应频率,当功率大小在一定范围内可以设置的连续波信号;设置射频开关模块和压控增益可调模块用以实现信号的脉冲调制,周期性的脉冲信号进入射频开关模块实现询问信号的分时通断,经过射频开关模块调制后的信号继续送入压控增益可调模块,调节其输出波形,隔离连续波,调节调制深度,最后把调制好的射频信号送入数控衰减模块,实现送入接收机的功率大小可控的目的,进而实现对连续波的高抑制度。

[0050]

以上所述仅为本发明的实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等同变换,或直接或间接运用在相关的技术领域,均同理包括在本发明的专利保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。