1.本技术属于显示技术领域,具体涉及一种栅极驱动电路及显示面板。

背景技术:

2.gdl技术(gate driver less)即较少的栅极驱动器技术,是运用液晶显示面板的原有阵列制程,将水平扫描线的驱动电路制作在显示区周围的基板上,使之能替代外接集成电路板(integrated circuit,ic)来完成水平扫描线的驱动。gdl技术能减少外接ic的焊接(bonding)工序,有利于提升产能并降低产品成本,而且可以使液晶显示面板更适合制作窄边框或无边框的显示产品。

3.然而液晶显示器的分辨率越高,所需栅极驱动电路的时钟信号线数量会越多。各移位寄存器单元通过一连接线连接至对应的时钟信号线,由于各连接线长度不同,造成各时钟信号的电阻电容负载存在差异,进而导致显示界面容易产生水平亮暗线等问题。

技术实现要素:

4.本公开的目的在于提供一种栅极驱动电路及显示面板,能够有效降低不同时钟信号的负载差异,从而提升显示界面的显示效果。

5.本公开第一方面公开了一种栅极驱动电路,包括:

6.多个级联的移位寄存器单元,所述移位寄存器单元具有时钟信号端;

7.n根时钟信号线;

8.每个所述移位寄存器单元通过一连接线对应连接至一根所述时钟信号线,所述连接线包括传导段,所述传导段的第一端连接所述时钟信号线,所述传导段的第二端连接所述移位寄存器单元的所述时钟信号端,其中,n为大于1的正整数;

9.至少一根所述连接线还包括:

10.电容调节段,与所述传导段电连接,所述电容调节段用于调节相应所述时钟信号线与所述传导段之间的耦合电容,所述电容调节段叠设于与其连接的所述传导段所相对的至少一根时钟信号线上;

11.电阻调节段,与所述传导段电连接,所述电阻调节段用于调节相应所述时钟信号线与所述移位寄存器单元的时钟信号端之间的阻抗。

12.在本公开的一种示范性实施例中,

13.所述多个移位寄存器单元依次沿第一方向排布,所述n根时钟信号线依次沿第二方向排布,所述第一方向与所述第二方向相交;

14.所述时钟信号线的长度方向与所述第一方向平行,所述传导段沿所述第二方向延伸,所述电容调节段完全叠设于所述时钟信号线之内。

15.在本公开的一种示范性实施例中,

16.所述移位寄存器单元还具有控制信号端;

17.所述栅极驱动电路还包括控制线,所述控制线连接至所述控制信号端;

18.所述控制线的长度方向与所述第一方向平行,所述控制线相较于所述时钟信号线更靠近所述移位寄存器单元;

19.所述电阻调节段设置于相邻的所述时钟信号线与所述控制线之间,所述电阻调节段的一端与所述传导段的第二端连接,所述电阻调节段的另一端与所述移位寄存器单元的时钟信号端连接。

20.在本公开的一种示范性实施例中,

21.第1根时钟信号线至第n根时钟信号线由近及远的依次排布于所述移位寄存器单元一侧;

22.第1根连接线的传导段至第n根连接线的传导段与第1根时钟信号线至第n根时钟信号线一一对应连接,所述第1根连接线的传导段至第n根连接线的传导段的走线长度依次增加;

23.所述第1根连接线至第n-1根连接线均设有所述电容调节段和所述电阻调节段。

24.在本公开的一种示范性实施例中,每根所述时钟信号线设有开孔;

25.第m根连接线的传导段与第1根时钟信号线至第m-1根时钟信号线交叠区域内设有所述开孔,所述开孔的取值范围为1至m-1个,所述交叠区域内开孔的数量与所述电容调节段与所述时钟信号线交叠面积正相关;或

26.第m根连接线的传导段与第1根时钟信号线至第m-1根时钟信号线交叠区域内未设有所述开孔;

27.其中,1<m≤n,m为正整数。

28.在本公开的一种示范性实施例中,所述电容调节段与所述传导段同层设置且相连;其中,

29.所述电容调节段为一整块结构,所述电容调节段与其所对应的时钟信号线在所述第二方向上的尺寸相等;或

30.所述电容调节段可包括多段在所述第二方向上间隔设置的电容调节子段,所述电容调节子段与所述时钟信号线一一对应,所述电容调节子段与其对应的时钟信号线在所述第二方向上的尺寸相等。

31.在本公开的一种示范性实施例中,

32.所述连接线还包括与所述传导段同层设置的连接段,所述连接段与所述传导段的第一端连接,所述连接段与相应所述时钟信号线通过过孔连接;

33.第1根所述连接线的电容调节段与所述连接段相连,并叠设在第1根时钟信号线上;

34.第2根所述连接线至第n-1根所述连接线的电容调节段与相应所述传导段同层设置且相连。

35.在本公开的一种示范性实施例中,

36.第1至第n-1根所述连接线的电容调节段及传导段与所述时钟信号线交叠面积之和均等于第n根连接线的传导段与时钟信号线的交叠面积。

37.在本公开的一种示范性实施例中,

38.第1至第n-1根所述连接线的所述传导段、所述电容调节段及所述电阻调节段的等效阻值之和均等于第n根所述连接线的所述传导段的阻值。

39.本公开第二方面公开了一种显示面板,包括有效显示区和非显示区,所述非显示区包括如权利要求1至9中任一项所述的栅极驱动电路,所述有效显示区内包括多根扫描线,所述栅极驱动电路包括多个移位寄存器单元,任一移位寄存器单元的输出端至少为一根所述扫描线提供栅极驱动信号。

40.本技术方案具有以下有益效果:

41.本公开申请通过使至少一根连接线还包括电容调节段和电阻调节段,以调节连接线与时钟信号线之间的耦合电容及自身阻抗,从而解决由于时钟信号线以及移位寄存器单元排布方式不同造成各个时钟信号传输路径阻抗和耦合电容不同而导致的显示问题。本技术中电容调节段叠设于与其连接的传导段对应的时钟信号线上,可以最大化的利用电容调节段来补偿传导段,同时将电阻调节段设置于时钟信号线与控制线之间,不会额外占用栅极驱动电路所在基板板面空间,不会增加显示面板边框宽度,有利于窄边框产品的设计。

42.本技术的其他特性和优点将通过下面的详细描述变得显然,或部分地通过本技术的实践而习得。

43.应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本技术。

附图说明

44.此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本公开的实施例,并与说明书一起用于解释本公开的原理。显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

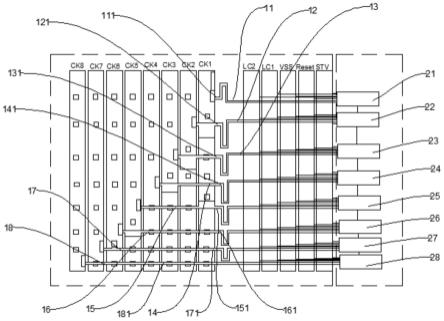

45.图1示出了本公开实施例一所述的栅极驱动电路的电路结构图。

46.图2示出了本公开实施例一所述的栅极驱动电路的部分电路结构图。

47.图3示出了本公开实施例一所述的第四连接线与时钟信号线的连接结构图一。

48.图4示出了本公开实施例一所述的第四连接线与时钟信号线的连接结构图二。

49.图5示出了本公开实施例一所述的第四连接线与时钟信号线的连接结构图三。

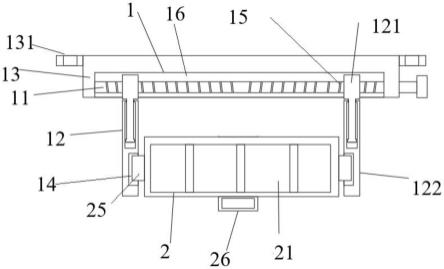

50.图6示出了本公开实施例二所述的显示面板的结构示意图。

51.附图标记说明:

52.11、第一连接线;12、第二连接线;13、第三连接线;14、第四连接线;15、第五连接线;16、第六连接线;17、第七连接线;18、第八连接线;19、开孔;111、第一传导段;121、第二传导段;131、第三传导段;141、第四传导段;151、第五传导段;161、第六传导段;171、第七传导段;181、第八传导段;112、第一电容调节段;122、第二电容调节段;132、第三电容调节段;142、第四电容调节段;152、第五电容调节段;162、第六电容调节段;172、第七电容调节段;113、第一电阻调节段;123、第二电阻调节段;133、第三电阻调节段;143、第四电阻调节段;153、第五电阻调节段;163、第六电阻调节段;173、第七电阻调节段;

53.21、第一移位寄存器单元;22、第二移位寄存器单元;23、第三移位寄存器单元;24、第四移位寄存器单元;25、第五移位寄存器单元;26、第六移位寄存器单元;27、第七移位寄存器单元;28、第八移位寄存器单元;

54.100、栅极驱动电路;

55.200、有效显示区;300、扫描线;400、数据线。

具体实施方式

56.现在将参考附图更全面地描述示例实施方式。然而,示例实施方式能够以多种形式实施,且不应被理解为限于在此阐述的范例;相反,提供这些实施方式使得本公开将更加全面和完整,并将示例实施方式的构思全面地传达给本领域的技术人员。

57.此外,所描述的特征、结构或特性可以以任何合适的方式结合在一个或更多实施例中。在下面的描述中,提供许多具体细节从而给出对本技术的实施例的充分理解。然而,本领域技术人员将意识到,可以实践本技术的技术方案而没有特定细节中的一个或更多,或者可以采用其它的方法、组元、装置、步骤等。在其它情况下,不详细示出或描述公知方法、装置、实现或者操作以避免模糊本技术的各方面。

58.下面结合附图和具体实施例对本技术作进一步详述。在此需要说明的是,下面所描述的本技术各个实施例中所涉及的技术特征只要彼此之间未构成冲突就可以相互组合。下面通过参考附图描述的实施例是示例性的,旨在用于解释本技术,而不能理解为对本技术的限制。

59.实施例一

60.请参见图1,图1是根据实施例一示出了一种栅极驱动电路结构图。本实施例提出一种栅极驱动电路,包括多个级联的移位寄存器单元、n根时钟信号线及控制线。移位寄存器单元具有时钟信号端,每个移位寄存器单元通过一连接线对应连接至一根时钟信号线。具体的,连接线包括传导段,传导段的第一端连接时钟信号线,传导段的第二端连接连接移位寄存器单元的时钟信号端,时钟信号通过传导段传递至移位寄存器单元,n为大于1的正整数,如2、3、4、5及6等。

61.在此,可以设置多个移位寄存器单元依次沿第一方向排布,每个移位寄存器单元是一级输出,n根时钟信号线依次沿第二方向排布,第一方向和第二方向相交,多个移位寄存器以n个移位寄存器单元为一组,每一组中的移位寄存器单元依次连接第1根时钟信号线至第n根时钟信号线,在本实施例中,第一方向和第二方向可垂直。并且,时钟信号线及控制线的长度方向与第一方向平行,传导段沿第二方向延伸,电容调节段完全叠设于时钟信号线内,也即电容调节段在电路板上的正投影完全位于时钟信号线在电路板上的正投影内,控制线相较于时钟信号线更靠近移位寄存器单元。

62.以图1及图2中方位为示例,第一方向为纵向,第二方向为横向。以n等于8为例,每8个移位寄存器单元为一组,。一组8个移位寄存器单元依次沿纵向排列,8根时钟信号线,以及控制线分别由近及远的依次排布于8个移位寄存器单元一侧。

63.在此以8ck架构gdl为例说明,栅极驱动电路包括8个移位寄存器单元,分别为第一移位寄存器单元21、第二移位寄存器单元22、第三移位寄存器单元23、第四移位寄存器单元24、第五移位寄存器单元25、第六移位寄存器单元26、第七移位寄存器单元27、第八移位寄存器单元28。时钟信号线分别有:第一时钟信号线ck1、第二时钟信号线ck2、第三时钟信号线ck3、第四时钟信号线ck4、第五时钟信号线ck5、第六时钟信号线ck6、第七时钟信号线ck7、第八时钟信号线ck8;控制线包括有起始触发信号线stv、第一下拉控制线lc1、第二下拉控制线lc2、恒压低电位线vss、重置信号线reset。

64.进一步的,8根时钟信号线,相应产生八个时钟信号:ck1、ck2、ck3、ck4、ck5、ck6、ck7、ck8。八个时钟信号产生的脉冲宽度和幅度均相等,工作方式如下:当第m条时钟信号ckm为第八条时钟信号ck8时,第m 1条时钟信号ckm 1为第一条时钟信号ck1;当第m条时钟信号ckm为第一条时钟信号ck1时,第m-1条时钟信号ckm-1为第八条时钟信号ck8。在面板进行正常显示时,所有时钟信号的脉冲周期相同,前一条时钟信号的脉冲信号结束的同时后一条时钟信号的脉冲信号产生,即第一条时钟信号ck1的第一个脉冲信号首先产生,第一时钟信号ck1的第一个脉冲信号结束的同时第二条时钟信号ck2的第一个脉冲信号产生,第二条时钟信号ck2的第一个脉冲信号结束的同时第三条时钟信号ck3的第一个脉冲信号产生,第三条时钟信号ck3的第一个脉冲信号结束的同时第四条时钟信号ck4的第一个脉冲信号产生,

……

第八条时钟信号ck8的第一个脉冲信号结束的同时第一条时钟信号ck1的第二个脉冲信号产生,以此类推。

65.对于下拉控制线lc1和lc2,在一个移位寄存器单元的电路中,包括预充单元、下拉单元、下拉控制单元以及输出单元。其中,预充单元用于输出预充电压,预充单元的输出端为预充点。下拉控制单元在lc信号的触发下,控制下拉单元下拉预充点电位,从而使移位寄存器单元停止输出下拉电压。在此下拉控制单元的数量可以设置为两个,以交替工作,提高电路可靠性,相应的,下拉控制单元设置两个,两个下拉控制单元分别用于连接第一下拉控制线lc1和第二下拉控制线lc2。

66.对于恒压低电位线vss。下拉单元连接在预充点和恒压低电位线vss之间,下拉单元在下拉控制单元的控制下,将预充点电位下拉至恒压低电位。

67.控制线还包括起始触发信号线stv和重置信号线reset,当起始触发信号线stv开始输出起始触发信号时,各个时钟信号线开始依照时序产生时序控制信号,当重置信号线reset开始输出重置信号时,各个时钟信号线重置时钟信号。

68.时钟信号线和控制线均是沿纵向延伸的,因此为了实现与移位寄存器单元的电连接,设置了连接线,连接线沿横向方向延伸,以每个时钟信号线连接至相应的移位寄存器单元的时钟信号端。

69.从图1和图2中可以看出,每个移位寄存器单元有一个时钟信号端,用于对应连接一个时钟信号线。同时每个移位寄存器单元与下拉控制线lc1或lc2、恒压低电位线vss、重置信号线reset以及起始触发信号线stv均电连接。

70.在此,设置连接线相应有8条,分别为第一连接线11、第二连接线12、第三连接线13、第四连接线14、第五连接线15、第六连接线16、第七连接线17、第八连接线18。其中,第一连接线11包括第一传导段111,第二连接线12包括第二传导段121,第三连接线13包括第三传导段131,第四连接线14包括第四传导段141,第五连接线15包括第五传导段151,第六连接线16包括第六传导段161,第七连接线17包括第七传导段171,第八连接线18包括第八传导段181。

71.具体的,第一时钟信号线ck1通过第一连接线11的第一传导段111连接至第一移位寄存器单元21,第二时钟信号线ck2通过第二连接线12的第二传导段121连接至第二移位寄存器单元22,第三时钟信号线ck3通过第三连接线13的第三传导段131连接至第三移位寄存器单元23,

……

,第八时钟信号线ck8通过第八连接线18的第八传导段181连接至第八移位寄存器单元28。

72.可以看出,由于时钟信号线是沿横向排布的,而移位寄存器单元是纵向排布的,因此各个连接线之间的长度不等而导致存在阻抗差,即第一根连接线的传导段至第n根连接线的传导段的走线长度依次增加。在本实施例中,第一传导段111至第八传导段181的走线长度依次增加,从而导致各连接线之间存在阻抗差,第一传导段111由于走线长度最短,阻抗最小,第八传导段181由于走线长度最长,阻抗最大。第一传导段111跨越的时钟信号线最小,第八传导段181跨越的信号时钟线最多,导致各连接线与时钟信号线的交叠面积不同,第一传导段111与时钟信号线的耦合电容最小,第八传导段181与时钟信号线间的耦合电容最大。

73.基于此,至少一根连接线还包括电容调节段和电阻调节段,电容调节段和电阻调节段与传导段电连接,电容调节段用于调节相应时钟信号线与传导段之间的耦合电容,电容调节段叠设于与其连接的传导段所相对的至少一根时钟信号线上,电阻调节段用于调节相应时钟信号线与移位寄存器单元的时钟信号端之间的阻抗。电容调节段和电阻调节段的数量可以为一根,也可以与传导段的数量相同,而为了使调节效果最佳和成本最低,可以使电容调节段和电阻调节段的数量少一个,对应于走线长度最长的传导段可以不连接电容调节段和电阻调节段。在此,“相应”是指具有电连接关系的时钟信号线与移位寄存器单元的时钟信号端。

74.在本实施例中,第一根连接线至第n-1根连接线均设有电容调节段,且第一根连接线的电容调节段至第n-1根连接线的电容调节段与时钟信号线的交叠面积逐渐减小,这样可以使得各电容调节段分别对第一根连接线的传导段至第n-1根连接线的传导段进行补偿,使得第一根连接线至第n根连接线与时钟信号线的交叠面积大体相等,同时根据平面电容的公式可知,电容只与平面间面积相关,即只与连接线与时钟信号线之间的交叠面积相关,从而使得各连接线与时钟信号线之间的耦合电容大体相等,进而消除电容不等带来的显示缺陷。

75.在对各电容进行补偿后,在本实施例中,第一根连接线至第n-1根连接线均设有电阻调节段,在通过电容调节段使各耦合电容相等后,再通过设置电阻调节段使各连接线的阻抗大体相等,从而使得各连接线的电阻和电容均能够大体相等,从而解决由于电阻电容负载差异带来的显示界面易产生水平亮暗线的问题。

76.具体的,第一连接线11至第七连接线17均设有电容调节段和电阻调节段,分别为第一电容调节段112、第二电容调节段122、第三电容调节段132、第四电容调节段142、第五电容调节段152、第六电容调节段162、第七电容调节段172、第一电阻调节段113、第二电阻调节段123、第三电阻调节段133、第四电阻调节段143、第五电阻调节段153、第六电阻调节段163及第七电阻调节段173。

77.进一步的,在设置时,以第八连接线为基准,可先使第一至第七电阻调节段173的长度逐渐减小,从而使得第一至第八连接线18的长度一致,各连接线的阻值大体相等,此时,再进行电容的调节,通过设置第一至第七电容调节段172,使得第一至第七传导段171与时钟信号线的交叠面积大体相等。

78.在本实施例中,电容调节段与传导段同层设置且相连,电容调节段为一整块结构,电容调节段与其对应的时钟信号线在第二方向上的尺寸相等,也即电容调节段与其中一根时钟信号线的线宽相等,这样可以采用同一工艺制成,降低成本。或者,电容调节段可包括

多段在第二方向上间隔设置的电容调节子段,电容调节子段与时钟信号线一一对应,且电容调节子段与其对应的时钟信号线在第二方向上的尺寸相等,也即电容调节子段与其对应的时钟信号线的线宽相等,分段的个数根据其传导段跨过的时钟信号线根数而定,只要保证多段电容调节子段的面积与一整块的电容调节段面积一致即可。

79.示例的,连接线还包括与传导段同层设置的连接段,连接段与传导段的第一端连接,连接段与相应时钟信号线通过过孔连接,第1根连接线即第一连接线11由于不跨其他时钟信号线,其电容调节段与连接段相连,并叠设在第1根时钟信号线上,第2根连接线至第n-1根连接线的电容调节段与相应传导段同层设置且相连。也即是,第一电容调节段112与第一连接线11的连接段相连,并叠设在第一时钟信号线ck1上,第二电容调节段122至第七电容调节段172与第二传导段121至第七传导段171相连。

80.在本实施例中,对于第一连接线11来说,相当于使第一传导段111长度变长,使得第一传导段111的电阻同步增大,此时需减少第一电阻调节段113的长度,使得第一连接线11的总电阻保持与第八连接线18的电阻一致,对于第二连接线12至第七连接线17来说,相当于增大了第二传导段121至第七传导段171的横截面积,使第二传导段121至第七传导段171的等效电阻降低,此时需增大第二电阻调节段123至第七电阻调节段173的长度,使得第二连接线12至第七连接线的总电阻与第八连接线18的电阻一致。

81.同时,为了降低电阻调节段对电容调节段的影响,以及方便设计,可将电阻调节段设置于相邻的时钟信号线与控制线之间。在本实施例中,可将电阻调节段设置于第一时钟信号线及第二下拉控制线之间,两者之间有较大间隔区域,便于设置电阻调节段,电阻调节段可呈弯曲线段设置于两者之间,电阻调节段的一端与传导段的第二端连接,电阻调节段的另一端与移位寄存器单元的时钟信号端连接。

82.可以理解的是,为了完全消除由于各连接线电阻电容负载差异导致的显示不良,可以通过调整各电容调节段的面积及各电阻调节段的长度,使得第1至第n-1根连接线的电容调节段及传导段与时钟信号线交叠面积之和均等于第n根连接线的传导段与时钟信号线的交叠面积,第1至第n-1根连接线的传导段、电容调节段及电阻调节段的等效阻值之和均等于第n根连接线的传导段的阻值。具体的,第一电容调节段112至第七电容调节段172与其对应连接的第一传导段111至第七传导段171与时钟信号线交叠面积之和均与第八连接线18与时钟信号线交叠面积相等,第一传导段111、第一电容调节段112及第一电阻调节段113至第七传导段171、第七电容调节段172及第七电阻调节段173的等效阻值之和均等于第八传导段181的阻值。

83.示例的,每根时钟信号线开设有开孔19,在开孔19位置处,传导段与时钟信号线之间不存在耦合电容,从而使得连接线与时钟信号线之间总的耦合电容降低,有利于时钟信号传输的稳定。可以理解的是,开孔19的宽度小于时钟信号线的宽度,以不至于使时钟信号线产生断路。

84.在本公开实施例中,可以通过设置开孔19的数量及位置来调节传导段与时钟信号线交叠的面积,从而调节电容调节段的面积。如第m根连接线的传导段与第1根时钟信号线至第m-1根时钟信号线交叠区域内设有上述开孔,开孔的取值范围为1至m-1个,交叠区域内开孔的数量与电容调节段与时钟信号线交叠面积正相关。当然,也可以挪动开孔的位置,使第m根连接线的传导段与第1根时钟信号线至第m-1根时钟信号线交叠区域内未设有上述开

孔。其中,1<m≤n,m为正整数。

85.当然,也可以不挪动开孔的位置,使第m根连接线的传导段错开时钟信号线上开孔的位置,如传导段为折线段,从开孔的上方或下方经过,这样时钟信号线所在的掩膜版无需更改设计,开孔的位置可以保持不变,简化制造工艺。

86.可以理解的是,为了使整体的耦合电容最小,可以使得第n根连接线的传导段与第1根时钟信号线至第n-1根时钟信号线的交叠区域内开设有n-1个开孔19,也即是说第n根连接线的传导段跨过的每条时钟信号线上的交叠区域均设有上述开孔19,从而使得作为基准的第n根连接线与时钟信号线之间的耦合电容最小,其余的连接线的电容调节段所要补偿的电容也就越低,能够节约材料及空间,使设计简化。为了使各时钟信号线本身的阻抗一致,传输的时钟信号均衡,每根时钟信号线开设的开孔19数量应相等,且应大于等于时钟信号线的根数。

87.下面以第四连接线14和第八连接线18为例进行举例说明,其他连接线均可由此类推。第四连接线14的连接段与第四时钟信号线ck4连接,其第四传导段141依次跨过第三时钟信号线ck3、第二时钟信号线ck2及第一时钟信号线ck1,第八连接线18的连接段与第八时钟信号线ck8连接,其第八传导段181依次跨过第七时钟信号线ck7......第一时钟信号线ck1。为方便计算,设各传导段的线宽为b,每根时钟信号线的线宽为3a,开孔的宽度和相邻时钟信号线间距均为a,则可以计算得到第八连接线18的传导段即第八传导段181与时钟信号线交叠面积e=14ab,第八传导段的长度c=28a,则第八传导段181的阻值r=ρc/s=28aρ/bd=28g,其中,ρ表示传导段的电阻率,d表示传导段的厚度,g=aρ/bd。

88.如图3所示,挪动第一时钟信号线ck1、第二时钟信号线ck2及第三时钟信号线ck3中开孔19位置,使的第四传导段141与第一至第三时钟信号线交叠区域内未设有开孔19,且第四电容调节段142为一整块结构,叠设于第三时钟信号线ck3上。此时,第四传导段141与第一至第三时钟信号线ck3交叠面积e1=9ab,则第四电容调节段142的面积e2=e-e1=5ab,第四电容调节段142的长度l=3a,第四电容调节段142的宽度w=s2/l=5/3b,则第四电容调节段142与第四传导段141对应的等效阻值r4=r

41

r

42

r

43

=r,r

41

=ρl/(8/3bd)=9/8aρ/bd=9/8g,则r

42

=9ρ/bd=9g,则r

43

=r-r

41-r

42

=143/8g,则h=143/8a,其中,r

41

表示第四电容调节段142与其叠设的时钟信号线所对应的传导段部分的等效阻值,r

42

表示第四传导段除去第四电容调节段对应的第四传导段部分的等效阻值,r

43

表示第四电阻调节段143的阻值,h表示第四电阻调节段143的长度。

89.如图4所示,挪动第一时钟信号线ck1和第二时钟信号线ck2中开孔位置,使得第四传导段141与第三时钟信号线ck3交叠区域内设有1个开孔,且第四电容调节段142包括两段第四电容调节子段,分别叠设在第一时钟信号线ck1和第二时钟信号线ck2上。此时,第四传导段141与第一至第三时钟信号线ck3交叠面积e1=8ab,则第四电容调节段142的面积e2=e-e1=6ab,第四电容调节子段的面积为3ab,每个第四电容调节子段的长度为3a,每个第四电容调节子段的宽度为b,同理可得,h=19a。

90.如图5所示,挪动第二时钟信号线ck2和第三时钟信号线ck3中开孔位置,使得第四传导段与第一至第三时钟信号线交叠区域内设有2个开孔,且第四电容调节段为一整块结构,叠设于第一时钟信号线上。此时,第四传导段与第一至第三时钟信号线交叠面积e1=7ab,则第四电容调节段的面积e2=e-e1=7ab,第四电容调节段的长度l=3a,第四电容调节

段的宽度w=e2/l=7/3b,同理可得,h=124/7a。

91.示例的,时钟信号线与扫描线300同层设置,连接线与数据线400同层设置,这样的话相当于和显示区进行关联,可以采用同一工艺制作,降低成本。

92.本技术通过设置电容调节段和电阻调节段,以调节传导段与时钟信号线之间的耦合电容,以及时钟信号线与移位寄存器单元的时钟信号端之间的阻抗,从而解决由于时钟信号线以及移位寄存器单元排布方式不同造成各个时钟信号传输路径阻抗和耦合电容不同而导致的显示问题。本技术中电容调节段叠设于与其连接的传导段对应的时钟信号线上,可以最大化的利用电容调节段来补偿传导段,同时将电阻调节段设置于时钟信号线与控制线之间,不会额外占用栅极驱动电路所在基板板面空间,不会增加显示面板边框宽度,有利于窄边框产品的设计。

93.实施例二

94.请参阅图6,图6是根据实施例二提出的一种显示面板的结构示意图。在实施例二中,还提出一种显示面板。

95.显示面板包括有效显示区200和非显示区,所述非显示区包括栅极驱动电路100,所述有效显示区200内包括多根扫描线300,栅极驱动电路100包括多个移位寄存器单元,任一移位寄存器单元的输出端至少为一根扫描线300提供栅极驱动信号。由于本实施例的显示面板具有上实施例中的栅极驱动电路,因此具有上述栅极驱动电路所具有的所有有益效果,此处不再赘述。

96.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

97.在本技术中,除非另有明确的规定和限定,术语“装配”、“连接”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本技术中的具体含义。

98.在本说明书的描述中,参考术语“一些实施例”、“示例地”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本技术的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

99.尽管上面已经示出和描述了本技术的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本技术的限制,本领域的普通技术人员在本技术的范围内可以对上述实施例进行变化、修改、替换和变型,故但凡依本技术的权利要求和说明书所做的变化或修饰,皆应属于本技术专利涵盖的范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。