技术特征:

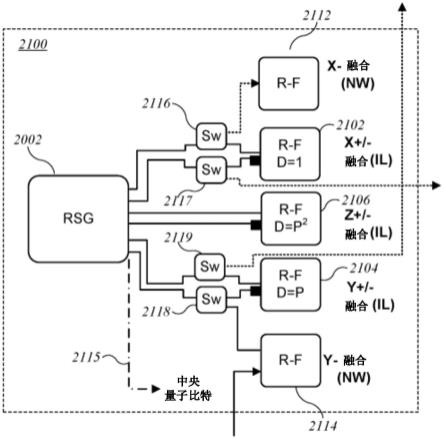

1.一种用于在量子比特之间生成纠缠的电路,所述电路包括:源态生成器,其具有用于在第一时钟周期期间生成第一源态、在第二时钟周期期间生成第二源态、在第三时钟周期期间生成第三源态以及在第四时钟周期期间生成第四源态的电路,其中所述第一源态、所述第二源态、所述第三源态和所述第四源态中的每一者包括纠缠的光子量子比特的系统,并且其中所述第一时钟周期、所述第二时钟周期、所述第三时钟周期和所述第四时钟周期是不同的时钟周期;第一类时融合电路,其被配置为通过在所述第一源态的第一量子比特和所述第二源态的第一量子比特之间执行纠缠测量操作来在所述第一源态和所述第二源态之间生成第一纠缠态;第二类时融合电路,其被配置为通过在所述第一源态的第二量子比特和所述第三源态的第一量子比特之间执行纠缠测量操作来在所述第一纠缠态和所述第三源态之间生成第二纠缠态;以及第三类时融合电路,其被配置为通过在所述第一源态的第三量子比特和所述第四源态的第一量子比特之间执行纠缠测量操作来在所述第二纠缠态和所述第四源态之间生成第三纠缠态。2.根据权利要求1所述的电路,其中所述第一时钟周期和所述第二时钟周期是连续的时钟周期。3.根据权利要求1所述的电路,其中:所述电路可操作以形成具有纠缠结构的量子比特大型纠缠系统,所述纠缠结构包括纠缠空间中的多个层;所述第一源态、所述第二源态和所述第三源态都与所述多个层中的第一层相关联;并且所述第四源态与所述多个层中的第二层相关联。4.根据权利要求1所述的电路,其中:所述源态限定在纠缠空间中的多个层;所述第一源态、所述第二源态和所述第三源态都与所述多个层中的第一层相关联;并且所述第四源态与所述多个层中的第二层相关联。5.根据权利要求4所述的电路,其中:所述纠缠空间中的每一层是具有尺寸为l的第一线性维度的二维层;所述第一时钟周期和所述第二时钟周期以第一时间间隔分开;并且所述第一时钟周期和所述第三时钟周期以l倍的第一时间间隔分开。6.根据权利要求5所述的电路,其中,所述纠缠空间中的每一层是具有尺寸为l的第二线性维度的二维层,并且其中所述第一时钟周期和所述第四时钟周期以l2倍的所述第一时间间隔分开。7.根据权利要求1所述的电路,其中,所述第一类时融合电路包括用于延迟所述第一源态的所述第一量子比特直至所述第二时钟周期的延迟线,并且所述第二类时融合电路包括用于延迟所述第一源态的所述第二量子比特直至所述第三时钟周期的延迟线。8.根据权利要求1所述的电路,其中,由所述第一类时融合电路执行的所述纠缠测量操

作包括对所述第一源态的所述第一量子比特和所述第二源态的所述第一量子比特的破坏性测量。9.根据权利要求8所述的电路,其中,由所述第二类时融合电路执行的所述纠缠测量操作包括对所述第一源态的所述第二量子比特和所述第三源态的所述第一量子比特的破坏性测量。10.一种用于在量子比特之间生成纠缠的电路,所述电路包括若干个(n个)单位单元,所述若干个(n个)单位单元形成网络以使得每个所述单位单元耦合至至少两个邻近单位单元,每个所述单位单元包括:源态生成器,其具有光子电路,所述光子电路用于在第一时钟周期期间生成第一本地源态、在第二时钟周期期间生成第二本地源态、在第三时钟周期期间生成第三本地源态以及在第四时钟周期期间生成第四本地源态,其中所述第一本地源态、所述第二本地源态、所述第三本地源态和所述第四本地源态中的每一者包括纠缠光子量子比特的系统,并且其中所述第一时钟周期、所述第二时钟周期和所述第三时钟周期是不同的时钟周期;多个融合电路,包括第一本地融合电路、第二本地融合电路、第三本地融合电路、第一联网融合电路和第二联网融合电路,所述多个融合电路中的每一者被配置为在两个输入量子比特之间执行纠缠测量操作;第一本地延迟线,其耦合至所述第一本地融合电路的第一输入并且具有第一数量的时钟周期的延迟;第二本地延迟线,其耦合至所述第二本地融合电路的第一输入并且具有第二数量的时钟周期的延迟,所述第二数量大于所述第一数量;第三本地延迟线,其耦合至所述第三本地融合电路的第一输入并且具有第三数量的时钟周期的延迟,所述第三数量大于所述第二数量;第一路由开关,其被配置为选择性地将每个源态的第一量子比特引导到所述单位单元的所述第一本地延迟线或第一邻近单位单元的所述第一联网融合电路的第一输入中的一者;第二路由开关,其被配置为选择性地将每个源态的第二量子比特引导到所述第一本地融合电路的第二输入或所述单位单元的所述第一联网融合电路的第二输入中的一者;第三路由开关,其被配置为选择性地将每个源态的第三量子比特引导到所述单位单元的所述第二本地延迟线或第二邻近单位单元的所述第二联网融合电路的第一输入中的一者;第四路由开关,其被配置为选择性地将每个源态的第四量子比特引导到第二本地融合电路的第二输入或所述单位单元的所述第二联网融合电路的第二输入中的一者;第一路由路径,用于将每个源态的第五量子比特引导到所述第三本地延迟线;以及第二路由路径,用于将每个源态的第六量子比特引导到所述第三本地融合电路。11.根据权利要求10所述的电路,其中:所述电路可操作以形成具有纠缠结构的量子比特大型纠缠系统,所述纠缠结构包括纠缠空间中的多个层;所述第一本地源态、所述第二本地源态和所述第三本地源态都与所述多个层中的第一层相关联;并且

所述第四本地源态与所述多个层中的第二层相关联。12.根据权利要求10所述的电路,其中:所述源态限定纠缠空间中的多个层;所述第一本地源态、所述第二本地源态和所述第三本地源态都与所述多个层中的第一层相关联;并且所述第四本地源态与所述多个层中的第二层相关联。13.根据权利要求12所述的电路,其中,所述量子比特大型纠缠系统的每一层是尺寸为l2的二维层,并且其中每个单位单元为所述量子比特大型纠缠系统的每一层生成若干个(p2个)源态,其中p2=l2/n。14.根据权利要求13所述的电路,其中:所述第一时钟周期和所述第二时钟周期以第一时间间隔分开;并且所述第一时钟周期和所述第三时钟周期以p倍的所述第一时间间隔分开。15.根据权利要求14所述的电路,其中,所述第一时钟周期和所述第四时钟周期以p2倍的所述第一时间间隔分开。16.根据权利要求10所述的电路,其中,所述多个融合电路中的每一个融合电路被配置成使得所述纠缠测量操作包括对所述两个输入量子比特的破坏性测量。17.一种用于生成多个纠缠结构的电路,其中,每个纠缠结构可表示为纠缠空间中的多个层,所述电路包括:层生成电路,其被配置为在第一时段期间产生第一层,在第二时段期间产生第二层,在第三时段期间产生第三层,其中所述第一层、所述第二层和所述第三层中的每个层包括在纠缠空间中以至少两个维度纠缠的光子量子比特的系统,并且其中所述第二时段在所述第一时段和所述第三时段之间;以及多个类时融合电路,每个所述类时融合电路被配置为在所述第三时段随后的第四时段期间在所述第一层的量子比特和所述第三层的量子比特之间执行纠缠测量操作。18.根据权利要求17所述的电路,其中:所述层生成电路还被配置为在所述第四时段期间产生第四层;并且所述多个类时融合电路被配置为在所述第四时段随后的第五时段期间在所述第二层的一个或多个量子比特和所述第四层的一个或多个量子比特之间执行纠缠测量操作。19.根据权利要求18所述的电路,还包括:边界电路,其被配置为接收与纠缠的量子比特的每一层的边界对应的外围量子比特,其中所述边界电路包括被配置为检测所述外围量子比特的检测器。20.根据权利要求18所述的电路,还包括:边界电路,其被配置为在纠缠的量子比特的每一层的边界处接收源态的外围量子比特作为边界量子比特,其中所述边界电路包括:检测器,其被配置为检测所述边界量子比特;类时融合电路,其用于融合来自在两个不同时段期间生成的层的两个边界量子比特;以及开关,其可配置成将所述边界量子比特路由到所述检测器或所述类时融合电路。21.根据权利要求20所述的电路,其中,所述开关针对每个时段是动态可重新配置的。

22.根据权利要求17所述的电路,其中所述纠缠测量操作包括对在其之间执行所述纠缠测量操作的量子比特的破坏性测量。23.一种用于在量子比特之间生成纠缠的方法,所述方法包括在多个时钟周期中的每个时钟周期期间:操作源态生成器以生成包括纠缠光子量子比特的系统的新源态;确定所述新源态在纠缠空间中的位置,其中所述位置限定在源态的层内;在所述纠缠空间中的所述位置不对应于所述层的行的末尾的情况下,将所述新源态的第一量子比特路由到第一延迟线中;在所述纠缠空间中的所述位置不对应于层的所述行的起始的情况下,在所述新源态的第二量子比特和从所述第一延迟线输出的量子比特之间执行纠缠测量;在所述纠缠空间中的所述位置不对应于所述层的最后一行的情况下,将所述新源态的第三量子比特路由到具有比所述第一延迟线更长的延迟的第二延迟线中;在所述纠缠空间中的所述位置不对应于所述层的第一行的情况下,在所述新源态的第四量子比特和从所述第二延迟线输出的量子比特之间执行纠缠测量;将所述新源态的第五量子比特路由到具有比所述第二延迟线更长的延迟的第三延迟线中;以及在所述新源态的第六量子比特和从所述第三延迟线输出的量子比特之间执行纠缠测量。24.根据权利要求23所述的方法,还包括:在所述纠缠空间中的所述位置对应于所述层的行的末尾的情况下,对所述新源态的所述第一量子比特执行层边缘处理操作。25.根据权利要求24所述的方法,其中,所述层边缘处理操作包括对所述新源态的所述第一量子比特执行测量操作。26.根据权利要求24所述的方法,其中,所述层边缘处理操作包括在所述新源态的所述第一量子比特和与所述大型纠缠系统的不同层的边缘相关联的量子比特之间执行纠缠测量。27.根据权利要求23所述的方法,还包括:在所述纠缠空间中的所述位置对应于所述层的行的起始的情况下,对所述新源态的第二量子比特执行层边缘处理操作。28.根据权利要求23所述的方法,还包括:在所述纠缠空间中的所述位置对应于所述层的最后一行的情况下,对所述新源态的所述第三量子比特执行层边缘处理操作。29.根据权利要求23所述的方法,还包括:在所述纠缠空间中的所述位置对应于所述层的第一行的情况下,对所述新源态的所述第四量子比特执行层边缘处理操作。30.根据权利要求23所述的方法,其中,所述层的每一行在所述纠缠空间中的尺寸为l,并且其中,所述第二延迟线具有对应于所述第一延迟线的延迟的l倍的延迟。31.根据权利要求30所述的方法,其中每个层在所述纠缠空间中的尺寸为l2,并且其中所述第三延迟线具有对应于所述第一延迟线的延迟的l2倍的延迟。

32.根据权利要求23所述的方法,其中,执行所述纠缠测量中的每个纠缠测量包括执行融合操作,所述融合操作包括对在其之间执行所述融合操作的量子比特中的一个量子比特或两个量子比特的破坏性测量。33.一种用于在量子比特之间生成纠缠的方法,所述方法包括在多个时钟周期的每个时钟周期期间:在多个单位单元中操作多个源态生成器,以使得每个单位单元生成包括纠缠光子量子比特的系统的新源态;以及对于每个单位单元:确定所述新源态在纠缠空间中的位置,其中所述位置限定在源态的层的连续贴片内;在所述纠缠空间中的所述位置不对应于所述贴片的行的末尾的情况下,将所述新源态的第一量子比特路由到第一延迟线中;在所述纠缠空间中的所述位置不对应于所述贴片的行的起始的情况下,在所述新源态的第二量子比特和从所述第一延迟线输出的量子比特之间执行纠缠测量;在所述纠缠空间中的所述位置不对应于所述贴片的最后一行的情况下,将所述新源态的第三量子比特路由到具有比所述第一延迟线更长的延迟的第二延迟线中;在所述纠缠空间中的所述位置不对应于所述贴片的第一行的情况下,在所述新源态的第四量子比特和从所述第二延迟线输出的量子比特之间执行纠缠测量;将所述新源态的第五量子比特路由到具有比所述第二延迟线更长的延迟的第三延迟线中;以及在所述新源态的第六量子比特和从所述第三延迟线输出的量子比特之间执行纠缠测量。34.根据权利要求33所述的方法,还包括,对于所述单位单元中的至少一个单位单元:在所述纠缠空间中的所述位置对应于所述贴片的行的末尾的情况下,将所述新源态的所述第一量子比特路由到第一邻近单位单元。35.根据权利要求34所述的方法,还包括,对于所述单位单元中的至少一个其他单位单元:在所述纠缠空间中的所述位置对应于所述贴片的行的起始的情况下,在所述新源态的所述第二量子比特和从第二邻近单位单元接收的联网量子比特之间执行纠缠测量操作。36.根据权利要求33所述的方法,还包括,对于所述单位单元中的至少一个单位单元:在所述纠缠空间中的所述位置对应于所述贴片的最后一行的情况下,将所述新源态的所述第三量子比特路由到第一邻近单位单元。37.根据权利要求36所述的方法,还包括,对于所述单位单元中的至少一个单位单元:在所述纠缠空间中的所述位置对应于所述贴片的第一行的情况下,在所述新源态的所述第四量子比特和从第二邻近单位单元接收的联网量子比特之间执行纠缠测量操作。38.根据权利要求33所述的方法,其中,所述贴片的每一行在所述纠缠空间中的尺寸为p,并且其中所述第二延迟线具有对应于所述第一延迟线的延迟的p倍的延迟。39.根据权利要求38所述的方法,其中,每个贴片在所述纠缠空间中的尺寸为p2,并且其中所述第三延迟线具有对应于所述第一延迟线的延迟的p2倍的延迟。40.根据权利要求33所述的方法,其中,执行所述纠缠测量中的每个纠缠测量包括:执

行融合操作,所述融合操作包括对在其之间执行所述融合操作的量子比特中的一个量子比特或两个量子比特的破坏性测量。

技术总结

可以使用“栅格化”和交织技术来生成量子比特之间的纠缠。电路可以包括每时钟周期生成一个源态的源态生成器,其中每个源态具有若干个纠缠的量子比特。该电路还可以包括对由不同的时钟周期中的同一源态生成器生成的源态的量子比特执行纠缠测量操作的电路和延迟线。通过适当选择延迟线,单个源态生成器可以生成用来生成大型纠缠结构所需的所有源态。也可以使用混合技术,其中源态电路的数量大于1但小于生成纠缠结构所需的源态的数量。生成纠缠结构所需的源态的数量。生成纠缠结构所需的源态的数量。

技术研发人员:N

受保护的技术使用者:普赛昆腾公司

技术研发日:2020.06.22

技术公布日:2022/6/14

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。