1.本发明涉及氮化镓材料半导体技术领域,尤其涉及一种基于介质图形化技术的氮化镓器件及其制备方法。

背景技术:

2.宽禁带半导体gan材料在微波毫米波领域具有重要应用优势,但是,相较于传统的si和gaas器件,gan器件的线性度特性具有较大差距,使得gan微波器件在宽带通信等应用领域未能发挥其潜力。因此,开发gan器件线性度增强技术成为业内十分关注的热点问题。

3.目前,主要通过finfet结构、源端掺杂、势垒层梯度极化等技术在器件级实现氮化镓电子器件线性度的提升。

4.但是,上述技术工艺复杂、成本高,不利于低成本、高线性度氮化镓器件的制备。

技术实现要素:

5.鉴于上述的分析,本发明实施例旨在提供一种基于介质图形化技术的氮化镓器件及其制备方法,用以解决现有氮化镓器件制备工艺复杂、成本高的问题,本发明的氮化镓器件的制备工艺简单,同时可以有效提升氮化镓电子器件在大信号和大功率工作状态下的线性度。

6.一方面,本发明实施例提供了一种基于介质图形化技术的氮化镓器件,该氮化镓器件包括:基质层、(al,in)gan/gan异质结沟外延材料层、源电极、漏电极和栅电极,所述(al,in)gan/gan异质结沟外延材料层覆盖在所述基质层上面,所述源电极和所述漏电极分别设置在所述(al,in)gan/gan异质结沟外延材料层的两端,所述栅电极设置在所述源电极和所述漏电极之间,所述源电极和所述栅电极之间的(al,in)gan/gan异质结沟外延材料层表面设置有lpcvd-氮化硅材料层,所述漏电极和所述栅电极之间的至少部分(al,in)gan/gan异质结沟外延材料层表面设置有非lpcvd工艺生长的钝化层。

7.基于上述氮化镓器件的进一步改进,所述lpcvd-氮化硅材料层的介质折射率为1.99-2.01,厚度大于5nm,非故意氧含量不超过25%。

8.优选地,所述非lpcvd工艺生长的钝化层为pecvd生长的氮化硅和/或氧化硅、ald生长的氧化铝和/或氮化硅、mocvd生长的原位氮化硅中的至少一种。

9.优选地,所述漏电极和所述栅电极之间的全部(al,in)gan/gan异质结沟外延材料层表面设置有非lpcvd工艺生长的钝化层,非lpcvd工艺生长的钝化层的厚度为lpcvd-氮化硅材料层厚度的1.5-5倍。

10.优选地,所述栅电极靠近所述源电极的一端搭在所述lpcvd-氮化硅材料层上,所述栅电极与所述源电极之间的lpcvd-氮化硅材料层表面设置有非lpcvd工艺生长的钝化层,所述栅电极表面以及所述栅电极与所述漏电极之间的部分非lpcvd工艺生长的钝化层表面设置有连续的栅场板。

11.优选地,所述漏电极和所述栅电极之间的10%-50%的(al,in)gan/gan异质结沟

外延材料层表面设置有非lpcvd工艺生长的钝化层,其余的(al,in)gan/gan异质结沟外延材料层表面以及所述非lpcvd工艺生长的钝化层表面设置有lpcvd-氮化硅材料层,所述非lpcvd工艺生长的钝化层的厚度大于10nm。

12.优选地,所述非lpcvd工艺生长的钝化层为条状或矩阵式分布,所述非lpcvd工艺生长的钝化层的z方向投影形状为矩形、菱形、椭圆形和圆形中的至少一种。

13.另一方面,本发明实施例提供了一种基于介质图形化技术的氮化镓器件的制备方法,该制备方法包括:

14.a.在基质层的表面生长(al,in)gan/gan异质结沟外延材料层;

15.b.采用lpcvd工艺在(al,in)gan/gan异质结沟外延材料层表面生长lpcvd-氮化硅材料层;

16.c.采用刻蚀图形化工艺将源极、栅极和栅漏区域的lpcvd-氮化硅材料层刻蚀去除;

17.d.采用电子束蒸发工艺在源极和漏极生长源电极和漏电极,并合金形成欧姆接触;

18.e.进行有源区隔离工艺;

19.f.采用电子束蒸发工艺生长栅电极;

20.g.采用非lpcvd工艺生长钝化层;

21.h.栅电极、源电极、漏电极表面开孔;

22.i.采用电子束蒸发工艺生长栅场板;

23.优选地,步骤b中,所述lpcvd工艺的生长温度为600-830℃,所述lpcvd工艺使得得到的lpcvd-氮化硅材料层的介质折射率为1.99-2.01,厚度大于5nm,非故意氧含量不超过25%;

24.优选地,所述非lpcvd工艺生长的钝化层为pecvd生长的氮化硅和/或氧化硅、ald生长的氧化铝和/或氮化硅、mocvd生长的原位氮化硅中的至少一种;

25.进一步优选地,所述非lpcvd工艺生长的钝化层的厚度为lpcvd-氮化硅材料层厚度的1.5-5倍。

26.另一方面,本发明实施例提供了另一种基于介质图形化技术的氮化镓器件的制备方法,该制备方法包括:

27.a.在基质层的表面生长(al,in)gan/gan异质结沟外延材料层;

28.b.采用非lpcvd工艺生长钝化层;

29.c.采用刻蚀图形化工艺将源极、栅极、漏极、栅源区域以及部分栅漏区域的非lpcvd工艺生长的钝化层刻蚀去除;

30.e.采用lpcvd工艺在(al,in)gan/gan异质结沟外延材料层和非lpcvd工艺生长的钝化层表面生长lpcvd-氮化硅材料层;

31.f.源极和漏极开孔,采用电子束蒸发工艺在源极和漏极生长源电极和漏电极,并合金形成欧姆接触;

32.g.进行有源区隔离工艺;

33.h.栅极开孔,并采用电子束蒸发工艺生长栅电极。

34.基于上述方法的进一步改进,非lpcvd工艺生长的钝化层为pecvd生长的氮化硅

和/或氧化硅、ald生长的氧化铝和/或氮化硅、mocvd生长的原位氮化硅中的至少一种;

35.优选地,步骤b中,所述非lpcvd工艺生长的钝化层的厚度大于等于10nm;

36.优选地,步骤c中,所述刻蚀使得栅漏区域的非lpcvd工艺生长的钝化层剩余10%-50%;

37.优选地,步骤c中,所述刻蚀图形化工艺使得栅漏区域剩余的非lpcvd工艺生长的钝化层呈条状或矩阵式分布,非lpcvd工艺生长的钝化层的z方向投影形状为矩形、菱形、椭圆形和圆形中的至少一种;

38.进一步优化地,步骤e中,所述lpcvd工艺的生长温度为600-830℃,所述lpcvd工艺使得得到的lpcvd-氮化硅材料层的介质折射率为1.99-2.01,厚度大于5nm,非故意氧含量不超过25%。

39.与现有技术相比,本发明至少可实现如下有益效果之一:

40.1、本发明氮化镓器件的栅源间材料和栅漏间材料不是同一种生长工艺制备的介质,栅源间为lpcvd-氮化硅材料,而栅漏间是非lpcvd工艺生长的钝化层;栅源间的lpcvd-sinx介质可增强(al,in)gan势垒层外界面正电荷,使得异质结沟道中二维电子气(2deg)密度提升,栅漏间的非lpcvd工艺生长的钝化层介质不能或仅少量增加(al,in)gan势垒层外界面正电荷,非lpcvd工艺生长的钝化层正下方2deg密度不变或略有增加,利用上述介质差异化调控界面正电荷的能力,从而实现源端电阻的下降以及沟道电场在源端的削弱效果,进而提升器件线性度;

41.2、在本发明的另一种实施方式中,非lpcvd工艺生长的钝化层存在于栅漏间有源区上lpcvd-氮化硅材料层与势垒层之间,且lpcvd-氮化硅材料层与非lpcvd工艺生长的钝化层相间排列,通过调控沟道中载流子疏密程度来调控载流子迁移率与沟道电场的依赖关系,进而找到改善器件线性度的图形化尺寸。

42.本发明中,上述各技术方案之间还可以相互组合,以实现更多的优选组合方案。本发明的其他特征和优点将在随后的说明书中阐述,并且,部分优点可从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过说明书以及附图中所特别指出的内容中来实现和获得。

附图说明

43.附图仅用于示出具体实施例的目的,而并不认为是对本发明的限制,在整个附图中,相同的参考符号表示相同的部件。

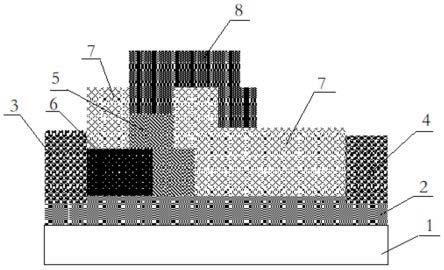

44.图1为本发明实施例1的氮化镓器件结构图;

45.图2为本发明实施例2的氮化镓器件结构图;

46.图3为本发明实施例2的氮化镓器件z方向投影图;

47.图4为本发明的一种实施方式的氮化镓器件z方向投影图;

48.图5为本发明实施例1、2和对比例1的氮化镓器件2deg密度分布图;

49.图6为本发明实施例1、2和对比例1的氮化镓器件源电阻随栅压变化图;

50.图7为本发明实施例1、2和对比例1的氮化镓器件跨导对比图;

51.图8为对比例1的现有技术中的氮化镓器件。

52.附图标记:

53.1-基质层;2-(al,in)gan/gan异质结沟外延材料层;3-源电极;4-漏电极;5-栅电极;6-lpcvd-氮化硅材料层;7-非lpcvd工艺生长的钝化层;8-栅场板。

具体实施方式

54.下面结合附图来具体描述本发明的优选实施例,其中,附图构成本技术一部分,并与本发明的实施例一起用于阐释本发明的原理,并非用于限定本发明的范围。

55.本发明的一个具体实施例,公开了一种基于介质图形化技术的氮化镓器件,如图1和2所示,该氮化镓器件包括:基质层1、(al,in)gan/gan异质结沟外延材料层2、源电极3、漏电极4和栅电极5,所述(al,in)gan/gan异质结沟外延材料层2覆盖在所述基质层1上面,所述源电极3和所述漏电极4分别设置在所述(al,in)gan/gan异质结沟外延材料层2的两端,所述栅电极5设置在所述源电极3和所述漏电极4之间,所述源电极3和所述栅电极5之间的(al,in)gan/gan异质结沟外延材料层2表面设置有lpcvd-氮化硅材料层6,所述漏电极4和所述栅电极5之间的至少部分(al,in)gan/gan异质结沟外延材料层2表面设置有非lpcvd工艺生长的钝化层7。

56.本发明创新性提出了非对称介质图形化定点调控器件有源区内2deg密度与迁移率分布的理念,利用有源区沟道势场扰动效应,降低器件源极电阻,人为改变载流子输运性质,改善器件跨导平坦度,从而提升器件线性度品质,为器件线性度调控与提升带来了全新的解决方案。

57.本发明中,氮化镓器件的栅源间材料和栅漏间材料不是同一种生长工艺制备的介质,栅源间为lpcvd-氮化硅材料,而栅漏间是非lpcvd工艺生长的钝化层;栅源间的lpcvd-sinx介质可增强(al,in)gan势垒层外界面正电荷,使得异质结沟道中二维电子气(2deg)密度提升,栅漏间的非lpcvd工艺生长的钝化层介质不能或仅少量增加(al,in)gan势垒层外界面正电荷,非lpcvd工艺生长的钝化层正下方2deg密度不变或略有增加,利用上述介质差异化调控界面正电荷的能力,从而实现源端电阻的下降以及沟道电场在源端的削弱效果,进而提升器件线性度。

58.本发明对所述基质层1没有特别的限定,可以为本领域用于制备半导体基板的常规选择,例如所述基质层1为si、sapphire和sic等衬底中的至少一种。所述基质层1的厚度也可以本领域的常规选择,优选地,所述基质层1的厚度为300um-1000um。

59.本发明中,所述(al,in)gan/gan异质结沟外延材料层2中的(al,in)gan和gan为单晶结构;ga在ga、al和in的总量中占比x为0-1,相应的al和/或in在ga、al和in的总量中占比为1-x。优选所述(al,in)gan/gan异质结沟外延材料层2的厚度为1-3um。

60.本发明中,为了进一步提高栅源间的(al,in)gan势垒层外界面正电荷,优选地,所述lpcvd-氮化硅材料层6的介质折射率为1.99-2.01,厚度大于5nm,进一步优选为10-120nm,更优选为20-80nm,非故意氧含量不超过25%。所述非故意氧含量是指非故意掺杂的氧占所有元素的原子比。

61.本发明中,所述非lpcvd工艺生长的钝化层7是指相较于lpcvd-氮化硅材料其能够减少甚至不能增加(al,in)gan势垒层外界面正电荷的材料层,为了最大程度减少栅漏间的(al,in)gan势垒层外界面正电荷,优选地,所述非lpcvd工艺生长的钝化层7为pecvd生长的氮化硅和/或氧化硅、ald生长的氧化铝和/或氮化硅、mocvd生长的原位氮化硅中的至少一

种。上述介质不能或仅少量增加(al,in)gan势垒层外界面正电荷。

62.本发明中,所述源电极3、漏电极4、栅电极5的材料可以为本领域的常规选择,例如,所述源电极3为tialniau合金,所述漏电极4为tialniau合金,所述栅电极5为niau叠层金属。

63.根据本发明的一种优选实施方式,如图1所示,所述漏电极4和所述栅电极5之间的全部(al,in)gan/gan异质结沟外延材料层2表面设置有非lpcvd工艺生长的钝化层7,非lpcvd工艺生长的钝化层7的厚度为lpcvd-氮化硅材料层6厚度的1.5-5倍,优选为3-4倍。该实施方式更适合尺寸较小的氮化镓器件。非lpcvd工艺生长的钝化层7的厚度和lpcvd-氮化硅材料层6的厚度用于调制栅电极5靠漏一层的电场峰值,若二者厚度相同,则栅脚靠漏侧的电场峰值比栅脚靠源侧的峰值要高很多,不利于器件2deg迁移率调控;将非lpcvd工艺生长的钝化层7和lpcvd-氮化硅材料层6的厚度限定上述范围内,可以使得峰值电场高度相近,有利于载流子迁移率和线性度调控。

64.本发明中,为了进一步提高氮化镓器件的线性关系,优选地,所述栅电极5靠近所述源电极3的一端搭在所述lpcvd-氮化硅材料层6上形成栅电极5和lpcvd-氮化硅材料层6搭接区域,所述栅电极5与所述源电极3之间的lpcvd-氮化硅材料层6表面的非搭接区域设置有非lpcvd工艺生长的钝化层7,所述栅电极5表面以及所述栅电极5与所述漏电极4之间的部分非lpcvd工艺生长的钝化层7表面设置有连续的栅场板8。所述栅电极5的一端搭载在所述lpcvd-氮化硅材料层6上,可降低栅脚靠源电极3一侧的电场,提高可靠性;优选地,搭接的宽度为0.1-0.8um。

65.本发明中,所述栅场板8的覆盖区域如图1所示,使得栅场板8靠近漏电极4的一侧与漏电极4之间的距离小于栅电极5靠近漏电极4的一侧与漏电极4之间的距离。

66.根据本发明的另一种优选实施方式,如图2所示,所述漏电极4和所述栅电极5之间的10-50%的(al,in)gan/gan异质结沟外延材料层2表面设置有非lpcvd工艺生长的钝化层7,其余的(al,in)gan/gan异质结沟外延材料层2表面以及所述非lpcvd工艺生长的钝化层7表面设置有lpcvd-氮化硅材料层6,所述非lpcvd工艺生长的钝化层7的厚度大于10nm,进一步优选为10-40nm,更优选为20nm。该优选实施方式适用于尺寸较大或栅漏距离较大的高压应用氮化镓器件。在该优选实施方式中,非lpcvd工艺生长的钝化层7存在于栅漏间有源区上lpcvd-氮化硅材料层6与势垒层之间,且优选lpcvd-氮化硅材料层6与非lpcvd工艺生长的钝化层7相间排列,通过调控沟道中载流子疏密程度来调控载流子迁移率与沟道电场的依赖关系,进而改善器件线性度。并且,所述非lpcvd工艺生长的钝化层7厚度在上述优选的范围内可以屏蔽上层lpcvd-sin材料层6对(al,in)gan/gan异质结沟外延材料层2外界面正电荷的调制影响,从而达到整体差异化调制效果。

67.在上述优选实施方式中,优选所述栅电极5的两端分别搭在栅源间的lpcvd-氮化硅材料层6上和栅漏间的lpcvd-氮化硅材料层6上,从而使得栅电极5呈t型设置。

68.本发明中,所述lpcvd-氮化硅材料层6与所述非lpcvd工艺生长的钝化层7相间排列更有利于提高器件的线性度,优选地,所述非lpcvd工艺生长的钝化层7为条状或矩阵式分布,如图2-4所示,所述非lpcvd工艺生长的钝化层7的z方向投影形状可以为矩形、菱形、椭圆形和圆形中的至少一种,进一步优选所述非lpcvd工艺生长的钝化层7的z方向投影形状为矩形、菱形、椭圆形和圆形中的一种。矩阵式分布式时,各个矩阵图形之间的间距优选

大于1um。条状分布时,即单排矩阵图形之间的间距为0。在该优选实施方式中,可以更好地调控2deg浓度与迁移率的关系,从而找到改善线性度的图形化尺寸。

69.本发明所述的z方向投影是指沿如图2所示ab线剖开后,下半部分剖面的俯视图。

70.另一方面,本发明具体实施例提供了一种基于介质图形化技术的氮化镓器件的制备方法,该制备方法包括:

71.a.在基质层1的表面生长(al,in)gan/gan异质结沟外延材料层2;

72.b.采用lpcvd工艺在(al,in)gan/gan异质结沟外延材料层2表面生长lpcvd-氮化硅材料层6;

73.c.采用刻蚀图形化工艺将源极、栅极和栅漏区域的lpcvd-氮化硅材料层6刻蚀去除;

74.d.采用电子束蒸发工艺在源极和漏极生长源电极3和漏电极4,并合金形成欧姆接触;

75.e.进行有源区隔离工艺;

76.f.采用电子束蒸发工艺生长栅电极5;

77.g.采用非lpcvd工艺生长钝化层7;

78.h.栅电极5、源电极3、漏电极4表面开孔;

79.i.采用电子束蒸发工艺生长栅场板8。

80.本发明的制备方法制备的氮化镓器件的栅源间材料和栅漏间材料不是同一种生长工艺制备的介质,栅源间为lpcvd-氮化硅材料,而栅漏间是非lpcvd工艺生长的钝化层;栅源间的lpcvd-sinx介质可增强(al,in)gan势垒层外界面正电荷,使得异质结沟道中二维电子气(2deg)密度提升,栅漏间的非lpcvd工艺生长的钝化层介质不能或仅少量增加(al,in)gan势垒层外界面正电荷,非lpcvd工艺生长的钝化层正下方2deg密度不变或略有增加,利用上述介质差异化调控界面正电荷的能力,从而实现源端电阻的下降以及沟道电场在源端的削弱效果,进而提升器件线性度。

81.本发明对所述基质层1没有特别的限定,可以为本领域用于制备半导体基板的常规选择,例如所述基质层1为si、sapphire和sic等衬底中的至少一种。所述基质层1的厚度也可以本领域的常规选择,优选地,所述基质层1的厚度为300um-1000um。

82.本发明中,所述(al,in)gan/gan异质结沟外延材料层2中的(al,in)gan和gan为单晶结构;ga在ga、al和in的总量中占比x为0-1,相应的al和/或in在ga、al和in的总量中占比为1-x。优选所述(al,in)gan/gan异质结沟外延材料层2的厚度为1-3unm。

83.本发明中,为了进一步提高栅源间的(al,in)gan势垒层外界面正电荷,优选地,步骤b中,所述lpcvd工艺的生长温度为600-830℃,所述lpcvd工艺使得得到的lpcvd-氮化硅材料层6的介质折射率为1.99-2.01,厚度大于5nm,进一步优选为10-120nm,更优选为20-80nm,非故意氧含量不超过25%。所述非故意氧含量是指非故意掺杂的氧占所有元素的原子比。

84.本发明中,所述非lpcvd工艺生长的钝化层7是指相较于lpcvd-氮化硅材料其能够减少甚至不能增加(al,in)gan势垒层外界面正电荷的材料层,为了最大程度减少栅漏间的(al,in)gan势垒层外界面正电荷,优选地,所述非lpcvd工艺生长的钝化层7为pecvd生长的氮化硅和/或氧化硅、ald生长的氧化铝和/或氮化硅、mocvd生长的原位氮化硅中的至少一

种。上述介质不能或仅少量增加(al,in)gan势垒层外界面正电荷。

85.本发明中,所述源电极3、漏电极4、栅电极5的材料可以为本领域的常规选择,例如,所述源电极3为tialniau合金,所述漏电极4为tialniau合金,所述栅电极5为niau叠层金属。

86.进一步优选地,所述非lpcvd工艺生长的钝化层7的厚度为lpcvd-氮化硅材料层(6)厚度的1.5-5倍,优选为3-4倍。该实施方式更适合制备尺寸较小的氮化硅器件。非lpcvd工艺生长的钝化层7的厚度和lpcvd-氮化硅材料层6的厚度用于调制栅电极5靠漏一层的电场峰值,若二者厚度相同,则栅脚靠漏侧的电场峰值比栅脚靠源侧的峰值要高很多,不利于器件2deg迁移率调控;将非lpcvd工艺生长的钝化层7和lpcvd-氮化硅材料层6的厚度限定上述范围内,可以使得峰值电场高度相近,有利于载流子迁移率和线性度调控。

87.本发明中,为了进一步提高制备的氮化硅器件的线性关系,优选地,所述栅电极5靠近所述lpcvd-氮化硅材料层6的一端搭在所述lpcvd-氮化硅材料层6上。

88.另一方面,本发明具体实施例提供了另一种基于介质图形化技术的氮化镓器件的制备方法,该制备方法包括:

89.a.在基质层1的表面生长(al,in)gan/gan异质结沟外延材料层2;

90.b.采用非lpcvd工艺生长钝化层7;

91.c.采用刻蚀图形化工艺将源极、栅极、漏极、栅源区域以及部分栅漏区域的非lpcvd工艺生长的钝化层7刻蚀去除;

92.e.采用lpcvd工艺在(al,in)gan/gan异质结沟外延材料层2和非lpcvd工艺生长的钝化层7表面生长lpcvd-氮化硅材料层6;

93.f.源极和漏极开孔,采用电子束蒸发工艺在源极和漏极生长源电极3和漏电极4,并合金形成欧姆接触;

94.g.进行有源区隔离工艺;

95.h.栅极开孔,并采用电子束蒸发工艺生长栅电极5。

96.该制备方法制备的氮化镓器件适用于尺寸较大的氮化镓器件。制备的氮化镓器件中,不仅通过介质差异化调控界面正电荷的能力,而且,非lpcvd工艺生长的钝化层7存在于栅漏间有源区上lpcvd-氮化硅材料层6与势垒层之间,且优选lpcvd-氮化硅材料层6与非lpcvd工艺生长的钝化层7相间排列,通过调控沟道中载流子疏密程度来调控载流子迁移率与沟道电场的依赖关系,进而改善器件线性度。

97.本发明对所述基质层1没有特别的限定,可以为本领域用于制备半导体基板的常规选择,例如所述基质层1为si、sapphire和sic等衬底中的至少一种。所述基质层1的厚度也可以本领域的常规选择,优选地,所述基质层1的厚度为300um-1000um。

98.本发明中,所述(al,in)gan/gan异质结沟外延材料层2中的(al,in)gan和gan为单晶结构;ga在ga、al和in的总量中占比x为0-1,相应的al和/或in在ga、al和in的总量中占比为1-x。优选所述(al,in)gan/gan异质结沟外延材料层2的厚度为1-3um。

99.本发明中,所述非lpcvd工艺生长的钝化层7是指相较于lpcvd-氮化硅材料其能够减少甚至不能增加(al,in)gan势垒层外界面正电荷的材料层,为了最大程度减少栅漏间的(al,in)gan势垒层外界面正电荷,优选地,所述非lpcvd工艺生长的钝化层7为pecvd生长的氮化硅和/或氧化硅、ald生长的氧化铝和/或氮化硅、mocvd生长的原位氮化硅中的至少一

种。上述介质不能或仅少量增加(al,in)gan势垒层外界面正电荷。

100.本发明中,优选地,步骤b中,所述非lpcvd工艺生长的钝化层7的厚度大于等于10nm,进一步优选为10-40nm,更优选为20nm。所述非lpcvd工艺生长的钝化层7厚度在上述优选的范围内可以屏蔽上层lpcvd-sin材料层6对(al,in)gan/gan异质结沟外延材料层2外界面正电荷的调制影响,从而达到整体差异化调制效果。

101.本发明中,为了进一步提高整体差异化调制效果,优选地,步骤c中,所述刻蚀使得栅漏区域的非lpcvd工艺生长的钝化层7剩余10%-50%。

102.本发明中,步骤c中,所述lpcvd-氮化硅材料层6与所述非lpcvd工艺生长的钝化层7相间排列更有利于调控器件的线性度,优选地,所述刻蚀介质图形化工艺使得栅漏区域剩余的非lpcvd工艺生长的钝化层7呈条状或矩阵式分布,非lpcvd工艺生长的钝化层7的z方向投影形状为矩形、菱形、椭圆形和圆形中的至少一种;进一步优选所述非lpcvd工艺生长的钝化层7的z方向投影形状为矩形、菱形、椭圆形和圆形中的一种。在该优选实施方式中,可以更好地调控2deg浓度与迁移率的关系,从而找到改善线性度的图形化尺寸。

103.本发明中,为了进一步提高栅源间的(al,in)gan势垒层外界面正电荷,进一步优化地,步骤e中,所述lpcvd工艺的生长温度为600-830℃,所述lpcvd工艺使得得到的lpcvd-氮化硅材料层6的介质折射率为1.99-2.01,厚度大于5nm,进一步优选为10-120nm,更优选为20-80nm,非故意氧含量不超过25%。

104.本发明中,优选步骤h使得所述栅电极5的两端分别搭在栅源间的lpcvd-氮化硅材料层6上和栅漏间的lpcvd-氮化硅材料层6上,从而使得栅电极5呈t型设置。

105.本发明中,可以采用mocvd工艺在基质层1的表面生长(al,in)gan/gan异质结沟外延材料层2。

106.本发明中,mocvd工艺、lpcvd工艺、刻蚀工艺、刻蚀图形化工艺、电子束蒸发工艺、有源区隔离工艺、pecvd工艺、ald工艺都是本领域的常规工艺,本领域技术人员可以通过现有技术确定具有的工艺步骤,在此不在赘述。

107.下面,通过具体实施例来进一步说明本发明的技术方案和技术效果。

108.实施例1

109.该实施例用于说明本发明的氮化镓器件及其制备方法。制备的氮化镓器件如图1所示。

110.a.采用mocvd工艺在600um基质层1(si材料,下同)的表面生长厚度为2um的(al,in)gan/gan异质结沟外延材料层2(ga元素组分含量比例x为0.6,相应的al和/或in元素组分含量比例为0.4);

111.b.采用lpcvd工艺,温度为600℃,在(al,in)gan/gan异质结沟外延材料层2表面生长厚度为40nm,宽0.5um的lpcvd-氮化硅材料层6(折射率为1.99,非故意氧含量为10%);

112.c.采用刻蚀图形化工艺将源极、栅极和栅漏区域的lpcvd-氮化硅材料层6刻蚀去除;

113.d.采用电子束蒸发工艺在源极和漏极生长源电极3(tialniau,厚300nm,宽30um)和漏电极4(tialniau,厚300nm,宽30um),并合金形成欧姆接触;

114.e.进行有源区隔离工艺;

115.f.采用电子束蒸发工艺生长栅电极5(niau,厚500nm,宽0.35um),并使得栅电极5

靠近lpcvd-氮化硅材料层6的一端搭在所述lpcvd-氮化硅材料层6上(搭载宽度0.2um);

116.g.采用pecvd工艺生长厚度为200nm、宽度为2um氧化硅钝化层7;

117.h.栅电极5、源电极3、漏电极4表面开孔;

118.i.采用电子束蒸发工艺生长栅场板8(tiau,厚300nm,宽1um)。

119.实施例1制备的氮化镓器件结构如图1所示。

120.实施例2

121.该实施例用于说明本发明的氮化镓器件及其制备方法。

122.a.采用mocvd工艺在厚600um基质层1的表面生长厚度为2um的(al,in)gan/gan异质结沟外延材料层2(ga元素组分含量比例x为0.5,相应的al和/或in元素组分含量比例为0.5);

123.b.采用ald工艺生长厚20nm、宽0.7um的氧化铝钝化层7;

124.c.采用刻蚀图形化工艺将源极、栅极、漏极、栅源区域以及部分栅漏区域的ald工艺生长的氧化铝钝化层7刻蚀去除,使得栅漏区域的氧化铝钝化层7呈如图2和3所示的矩阵式(氧化铝钝化层7的区域占栅漏间总区域的20%,0.7um*0.7um阵列,间距为2um);

125.e.采用lpcvd工艺,温度为830℃,在(al,in)gan/gan异质结沟外延材料层2和氧化铝钝化层7表面生长厚度为40nm的lpcvd-氮化硅材料层6,(折射率为2.01,非故意氧含量为20%);

126.f.源极和漏极开孔,采用电子束蒸发工艺在源极和漏极生长源电极3(tialniau,厚300nm,宽30um)和漏电极4(tialniau,厚300nm,宽30um),并合金形成欧姆接触;

127.g.进行有源区隔离工艺;

128.h.栅极开孔,并采用电子束蒸发工艺生长栅电极5(niau,厚500nm,底宽0.5um),并使得栅电极5的两端分别搭在栅源间的lpcvd-氮化硅材料层6上和栅漏间的lpcvd-氮化硅材料层6上(左侧搭载0.3um,右侧搭载1.2um,帽宽2um),即栅电极5呈t型,源电极3与栅电极5之间距离为1um,漏电极4与栅电极5之间距离为10um。

129.对比例1

130.该对比例用于现有技术的氮化镓器件及其制备方法。制备的氮化镓器件如图8示。

131.a.采用mocvd工艺在600um基质层1的表面生长厚度为2um的(al,in)gan/gan异质结沟外延材料层2(ga元素组分含量比例x为0.6,相应的al和/或in元素组分含量比例为0.4);

132.b.采用pecvd工艺生长200nm氧化硅钝化层7;

133.c.采用刻蚀工艺将源极、栅极和漏极的氧化硅钝化层7刻蚀去除;

134.d.采用电子束蒸发工艺在源极和漏极生长源电极3(tialniau)和漏电极4(tialniau),并合金形成欧姆接触;

135.e.采用电子束蒸发工艺生长栅电极5(niau),并使得栅电极5的两端分别分别搭在栅源间的氧化硅钝化层7上和栅漏间的氧化硅钝化层7上,即栅电极5呈t型。

136.采用传输线图形(tlm)方法测试实施例1-6对比例1的氮化镓器件的2deg密度分布;

137.采用栅传输线图形(gtlm)方法测试实施例1-6对比例1的氮化镓器件的源电阻随栅压的变化;

138.采用转移特性电学测量方法测试实施例1-6对比例1的氮化镓器件的跨导图。

139.实施例1-2和对比例1的测试结果如图5-7所示。

140.从图5可以看出:

141.实施例1制备得到的氮化镓器件由于栅源之间的lpcvd-氮化硅材料层6的正电荷增强效果,使得异质结沟道中二维电子气(2deg)密度(n

2deg

)提升70%-80%,而栅漏之间的pecvd工艺生长的氧化硅钝化层7不具备如此效果,其正下方2deg密度维持不变或略有增加。当漏端施加一定电压vds时,由于栅源间n

2deg

比栅漏间n

2deg

明显减小,使得栅源间的沟道分压及对应电场大大降低,这一方面降低了源端电阻rs,另一方面延缓了源端沟道载流子在高场下达到饱和速率的进度,从而有效改善跨导平坦度及器件线性度;

142.实施例2制备得到的氮化镓器件由于源漏之间绝大部分区域lpcvd-氮化硅材料层6的正电荷增强效果,使得异质结沟道中二维电子气(2deg)密度(n

2deg

)提升70%-80%,但栅漏之间图形化区域ald工艺生长的氧化铝钝化层7不具备如此效果,其正下方2deg密度维持不变或略有增加。当漏端施加一定电压vds时,栅漏间形成多个n

2deg

密度周期性变化的区间,密度梯度引起沟道电场或电势周期分布,从而人为引入载流子散射机制。该图形化结构利用二维电子气密度变化和散射机制的引入对载流子迁移率进行平衡调控,实现一定漏电流密度范围内器件载流子迁移率恒定,进而有效改善跨导平坦度及器件线性度。

143.从图6可以看出,相对现有技术中的氮化镓器件,实施例1和实施例2的氮化镓器件的源电阻随漏电流密度的变化率大大减小,有效抑制了由源电阻增加而导致的器件外观跨导在高栅压下的急剧衰退。

144.从图7可以看出,相对现有技术中的氮化镓器件,实施例1和实施例2的氮化镓器件的器件外观跨导在高栅压下更为平坦,有效增加器件在大功率输出时的线性输出范围。

145.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。