1.本发明属于系统模拟领域,具体涉及到使用翻译规则进行二进制翻译的动态二进制翻译方法。

背景技术:

2.动态二进制翻译技术是通过在运行时对源指令集架构的二进制程序进行翻译成目标指令架构的二进制程序(其还包括仿真cpu、内存管理和设备等)的一种技术。

3.一般来说,动态二进制翻译器有着两种运行模式:用户级(user-mode)的动态二进制翻译器和系统级(system-mode)的动态二进制翻译器。用户级的动态二进制翻译器通常只运行由源机器指令集架构编译好的一个进程,而系统级动态二进制翻译器需要去模拟整个虚拟机环境(包含源操作系统、内存管理单元、异常机制和设备等),因此系统级动态二进制翻译器有着更大的软件规模和复杂度。由于翻译流程简便且利于了宿主机的操作系统等特性,用户态的动态二进制翻译器的程序更接近本机性能,而系统级动态二进制翻译器的细粒度性翻译导致其有着较差的性能。

4.市面上传统的动态二进制翻译器为了更方便扩展更多指令集架构的支持,因此使用中间表示代码来进行设计。动态二进制翻译器的流程变成:首先将源指令序列经由前端解析器翻译成中间表示代码,随后通过后端编译器将中间表示代码生成目标机器代码。这种使用中间表示代码的设计,提升整个系统的可扩展性,极大的降低了从源指令架构到目标指令架构的整个翻译工作的耦合度和人工成本,但这种方式也随之带来较差的目标代码质量。

5.为了解决使用中间表示代码来进行翻译的性能较差问题,近年来,中国专利号cn202010625228.5提出了一种新型的动态二进制翻译方法,通过自动学习生成翻译规则,并将翻译规则应用在源架构和目标架构之间,以此来实现动态二进制翻译。但目前该方法只适用于用户级的动态二进制翻译器上,而无法直接应用到系统级的动态二进制翻译器。主要是因为系统级的动态二进制翻译器有着更为复杂的实现:其主要有两点原因:一是因为在系统级下,一些系统指令无法被学习过程所学习到而该系统指令又会影响基于规则学习方法中的状态管理方案,因此其无法直接应用。二是因为在基于规则学习的方法中,其由于是实现在已有的动态二进制翻译器上,且无法保证代码覆盖率达到100%,因此其存在着两种上下文管理环境,而在系统级下由于内存管理、异常/处理等特殊情形,需要进行时刻进行基于规则学习的上下文和翻译器自身上下文的完整切换,在之前的方法中无法保证切换成功。

技术实现要素:

6.本发明是为解决上述问题而进行的,目的在于提供一种基于翻译规则的全系统动态二进制翻译方法,主要是通过对客户指令解析、翻译规则匹配和应用、条件码优化阶段进行调整和设计来解决系统级的实现问题,本发明采用了如下技术方案:

7.本发明提供了一种基于翻译规则的全系统动态二进制翻译方法,其特征在于,包括:步骤s1,通过解析器对客户指令序列进行解析,并对所述客户指令序列中的特殊指令进行识别监控;步骤s2,通过翻译器并应用预先生成的翻译规则对所述客户指令序列进行匹配并翻译,其中,对所述特殊指令进行指令行为检查处理,从而生成正确的目标机器代码;步骤s3,通过优化器并使用系统级条件码优化策略对所述目标机器代码进行优化,从而提高所述目标机器代码的质量。

8.本发明提供的基于翻译规则的全系统动态二进制翻译方法,还可以具有这样的技术特征,其中,步骤s1中,用中间表示代码记录所述特殊指令的操作数、条件码信息以及对应的操作信息,从而对所述特殊指令进行识别监控;步骤s2中,从所述中间表示代码中提取出所述对应的所述操作信息,并根据所述操作信息进行所述指令行为检查处理。

9.本发明提供的基于翻译规则的全系统动态二进制翻译方法,还可以具有这样的技术特征,其中,所述特殊指令包括系统指令,步骤s2中,对所述系统指令进行指令行为检查处理包括以下步骤:步骤a1,判断所述系统指令是否为cpsr/spsr寄存器的读取指令或修改指令;步骤a2,步骤a1判断为所述读取指令时,将cpu状态信息同步至最新值;步骤a3,步骤a1判断为所述修改指令时,在执行完该修改指令后,即时通知所述翻译器所述条件码信息的存储位置的改变。

10.本发明提供的基于翻译规则的全系统动态二进制翻译方法,还可以具有这样的技术特征,其中,所述特殊指令包括访存指令,所述翻译规则中包含有所述访存指令的翻译实现过程,步骤s2中,对所述访存指令进行指令行为检查处理包括以下步骤:步骤b1,在翻译所述访存指令之前,判断当前的固定寄存器、eflags寄存器以及其他cpu状态信息是否需要被保存;步骤b2,步骤b1判断为是时,将所述固定寄存器、所述eflags寄存器以及所述其他cpu状态信息同步回内存。

11.本发明提供的基于翻译规则的全系统动态二进制翻译方法,还可以具有这样的技术特征,其中,所述翻译器以基本块为单位进行翻译,所述特殊指令包括异常指令,所述异常指令对应于内部异常的或切换异常,所述内部异常为翻译时所述基本块内发生的异常/中断,所述切换异常为切换所述基本块时发生的异常/中断,步骤s2中,对所述异常指令进行指令行为检查处理包括以下步骤:步骤c1,当所述异常指令对应于所述内部异常时,在发生所述内部异常前保存cpu状态信息,并在所述内部异常结束后恢复保存的所述cpu状态信息;步骤c2,当所述异常指令对应于所述切换异常时,在每个所述基本块的尾部将暂存在eflags寄存器中的条件码信息进行解析,并将解析得到的结果存回对应的内存位置中,从而在处理所述切换异常时能使用正确的所述条件码信息。

12.本发明提供的基于翻译规则的全系统动态二进制翻译方法,还可以具有这样的技术特征,其中,步骤s3中,所述系统级条件码优化策略包括条件码延迟存储优化策略,包括以下步骤:步骤d1,直接将存储有条件码信息的eflags寄存器的值存回内存;步骤d2,在发生异常/中断时,在对应的异常/中断处理函数执行前,将存储在所述内存中的所述eflags寄存器的值解析为各个条件码标志位。

13.本发明提供的基于翻译规则的全系统动态二进制翻译方法,还可以具有这样的技术特征,其中,所述目标机器代码为目标机器指令序列,步骤s3中,所述系统级条件码优化策略包括连续条件执行指令优化策略,包括以下步骤:步骤e1,对所述目标机器指令序列进

行指令流分析;步骤e2,基于步骤e1的分析结果,生成指令条件码使用依赖图;步骤e3,基于所述指令条件码使用依赖图,将所述目标机器指令序列中连续需要使用条件码的指令只加载一次,而省略其他冗余的加载操作。

14.发明作用与效果

15.根据本发明的基于翻译规则的全系统动态二进制翻译方法,由于通过在客户指令解析阶段中标识出会影响系统级实现的特殊指令,并将其单独分离出来进行识别监控,随后在翻译规则应用阶段,对识别出的特殊指令进行检查和对应处理,因此本发明的方法能够应对系统级动态二进制翻译器中特殊场景下的冲突,从而实现基于翻译规则的全系统动态二进制翻译。此外,本发明的方法还采用了系统级条件码优化策略对翻译得到的目标机器代码进行优化,因此,还能够提高二进制翻译的质量以及效率,在保证正确翻译的情况下,实现高效的动态二进制翻译。

附图说明

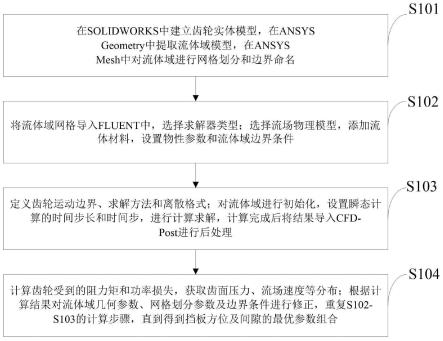

16.图1是本发明实施例中基于翻译规则的全系统动态二进制翻译方法的流程示意图;

17.图2是本发明实施例中基于翻译规则的全系统动态二进制翻译方法的流程图;

18.图3是本发明实施例中对系统指令问题处理的流程示意图;

19.图4是本发明实施例中对访存指令问题处理的流程示意图;

20.图5是本发明实施例中对异常指令问题处理的流程示意图;

21.图6是本发明实施例中条件码延迟优化策略的流程示例图;

22.图7是本发明实施例中连续条件执行指令优化策略的流程示例图。

具体实施方式

23.为了使本发明实现的技术手段、创作特征、达成目的与功效易于明白了解,以下结合实施例及附图对本发明的基于翻译规则的全系统动态二进制翻译方法作具体阐述。

24.《实施例》

25.本实施例中,基于动态二进制翻译系统qemu,在实验过程中采用arm指令集作为源指令集架构,使用x86架构的指令集为目标指令集架构。

26.图1是本实施例中基于翻译规则的全系统动态二进制翻译方法的流程示意图。

27.图2是本实施例中基于翻译规则的全系统动态二进制翻译方法的流程图。

28.如图1和图2所示,基于翻译规则的全系统动态二进制翻译方法包括如下步骤:

29.步骤s1,通过解析器对客户指令序列进行解析,并对客户指令序列中的特殊指令进行识别监控。

30.具体地,步骤s1中,对特殊指令进行识别监控,主要是通过特别设计的几种中间表示代码(intermediate representations,ir),用来在翻译基本块时,标识该基本块中存在的系统级指令(主要为读写cpsr/spsr寄存器的指令)、所有会涉及到地址转换的访存指令、以及可能会产生异常/中断的指令,并利用ir记录这些指令的操作数、条件码使用情况、以及说在处理时需要进行的操作(如寄存器检测、是否需要保存或恢复cpu状态等),以便在应用翻译规则时能提取出保存的ir信息进行实现。

31.步骤s2,通过翻译器并应用预先生成的翻译规则对客户指令序列进行匹配并翻译,并对特殊指令进行指令行为检查处理,从而生成正确的目标机器代码。

32.本实施例中,特殊指令包括系统指令、访问指令以及异常指令。在翻译规则应用阶段时进行指令行为检查,主要是利用在步骤s1中收集到的特殊指令的ir信息,并对在翻译系统级指令、访存指令和可能出现的异常/中断指令进行约束操作,具体讲就是在翻译上述指令时在该指令翻译的结果前后插入约束检测和状态保存和恢复步骤。以便于在该步骤后能初步生成语义正确的系统级翻译结果。

33.具体地,步骤s2中,从上述中间表示代码中提取出对应的操作信息,并根据操作信息进行指令行为检查处理。

34.图3是本实施例中对系统指令问题处理的流程示意图。

35.步骤s2中,如图3所示,对系统指令进行行为检查处理具体包括以下步骤:

36.步骤a1,判断系统指令是否为cpsr/spsr寄存器的读取指令或修改指令;

37.步骤a2,步骤a1判断为cpsr/spsr寄存器的读取指令时,将cpu状态信息同步至最新值;

38.步骤a3,步骤a1判断为cpsr/spsr寄存器的修改指令时,在执行完该修改指令后,即时通知翻译器条件码信息的存储位置的改变,以便在后续流程中其能重新定义最新cpu状态信息。

39.由于系统指令无法通过翻译规则的方式翻译,只能用翻译器自身的机制来翻译,因此需要通过上述步骤来对其进行对应处理。

40.图4是本实施例中对访存指令问题处理的流程示意图。

41.如图4所示,对访问指令进行行为检查处理具体包括以下步骤:

42.步骤b1,在翻译访存指令之前,判断当前的固定寄存器、eflags寄存器以及其他cpu状态信息是否需要被保存;

43.步骤b2,步骤b1判断为是时,将所述固定寄存器、所述eflags寄存器以及所述其他cpu状态信息同步回内存。

44.由于在系统级的动态二进制翻译器中,其在翻译访存指令时为了适配系统级模拟的内存管理单元的地址转换功能,其通过在快转换路径中插入额外的目标机器指令和慢转换路径中跳出当前基本块来满足该需求。因此,为了解决这两个问题,需要通过上述步骤对其进行对应处理。

45.图5是本实施例中对异常指令问题处理的流程示意图。

46.如图5所示,对异常指令进行行为检查处理具体包括以下步骤:

47.步骤c1,当异常指令对应于所述内部异常时,在发生内部异常前保存cpu状态信息,并在内部异常结束后恢复保存的cpu状态信息。

48.对于翻译块内部发生的异常,其最主要的问题也是cpu状态丢失问题,因此需要监控这类可能发生异常的位置,通过在异常前保存cpu状态,异常结束后恢复cpu状态的过程来进行监控。

49.步骤c2,当异常指令对应于所述切换异常时,在每个基本块的尾部将暂存在eflags寄存器中的条件码信息进行解析,并将解析得到的结果存回对应的内存位置中,从而在处理切换异常时能使用正确的条件码信息。

50.对于翻译块切换时发生的异常/中断的情况,主要原因是原先的跨基本块的条件码优化策略需要确定的程序执行流支持,而设备中断随时都可能发生,其会改变程序的执行流,导致无效的跨基本块的分析。由于不知道当前基本块执行后的切换过程是否会有异常/中断发生,因此需要在每个基本块的尾部将原先优化策略中暂存在eflags寄存器中条件码信息进行解析,并将解析得到的结果存回对应的内存位置中,以便在处理异常/中断过程能使用正确的条件码信息。

51.步骤s3,通过优化器并使用系统级条件码优化策略对目标机器代码进行优化,从而提高所述目标机器代码的质量。

52.具体地,步骤s3中,对上述的目标机器代码进行系统级条件优化策略,提高代码质量。

53.在本实施例中,系统级条件优化策略包括条件码延迟存储优化和连续条件执行指令优化。

54.图6是本实施例中条件码延迟优化策略流程示例图。

55.步骤3中,如图6所示,对目标机器代码进行条件码延迟存储优化包括以下步骤:

56.步骤d1,直接将存储有条件码信息的eflags寄存器的值存回内存;

57.步骤d2,在发生异常/中断时,在对应的异常/中断处理函数执行前,将存储在所述内存中的所述eflags寄存器的值解析为各个条件码标志位。

58.图7是本发明实施例中连续条件执行指令优化策略流程示例图。

59.如图7所示,对目标机器代码进行连续条件执行指令优化包括以下步骤:

60.步骤e1,对所述目标机器指令序列进行指令流分析;

61.步骤e2,基于步骤e1的分析结果,生成指令条件码使用依赖图;

62.步骤e3,基于所述指令条件码使用依赖图,将所述目标机器指令序列中连续需要使用条件码的指令只加载一次,而省略其他冗余的加载操作。

63.如上所述,条件码延迟优化的主要是修正每个基本块尾部的条件码存储方式,将存储所有客户条件码的指令替换为较少的存储eflags指令,并在异常函数处理前插入解析eflags的操作,便于在每个基本块的翻译过程中省下十条左右的目标机器指令,有效提高翻译指令质量。连续条件执行指令优化方法主要是对客户指令流进行分析,包含指令健寄存器依赖关系和条件码依赖关系俩种,并对其中可进行删减的冗余指令进行优化。便于省去连续条件执行指令翻译过程中生成的部分冗余指令,提高了翻译的质量。

64.实施例作用与效果

65.根据本实施例提供的基于翻译规则的全系统动态二进制翻译方法,由于通过实施在客户指令解析阶段中标识出会影响系统级实现的特殊指令,并将其单独分离出来进行识别监控,随后在翻译规则应用阶段,对系统级指令问题、内存管理问题以及异常/中断问题会涉及到的特殊指令进行检查和对应处理,最后通过分析指令流信息提出了两种对条件码优化策略以提高翻译质量以及效率,因此,本实施例的翻译方法既能高效地利用翻译规则进行翻译,同时又能保证系统级实现的准确性,能较好的生成高质量的目标机器代码。

66.实施例中,通过实验评估,评估了在系统级下性能结果、代码覆盖率情况。本实施例使用标准测试集spec cpu 2006测试集进行测试,可以看到,比起qemu4.1版本,本实施例有着1.12倍的性能提升,其动态代码覆盖率也达到94.13%,验证了本实施例的动态二进制

翻译方法在系统级下的有效性。

67.上述实施例仅用于举例说明本发明的具体实施方式,而本发明不限于上述实施例的描述范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。