1.本发明实施例涉及芯片制造技术领域,尤其涉及一种芯片的制备方法及采用该制备方法制备的芯片。

背景技术:

2.sic(碳化硅)是一种合适的用于工业化生产功率半导体器件的衬底材料。在工艺问题解决之后,价格成为了影响sic器件普及的重要因素。其中,sic片的成本占据了制造成本的很大一部分。

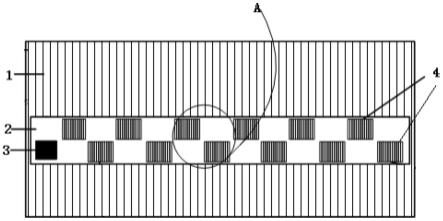

3.主要原因在于sic晶锭生长速度很慢,一周大概生长5cm,所以切割每一片sic的厚度,直接影响sic芯片成本。如图1所示,现有的sic晶锭1在满足芯片制造工艺的前提下,所能切割出的sic片2的厚度较厚,增加了芯片的制造成本。

技术实现要素:

4.本发明实施例提供一种芯片的制备方法,能够有效降低芯片的制造成本。

5.为了解决上述技术问题,本发明是这样实现的:

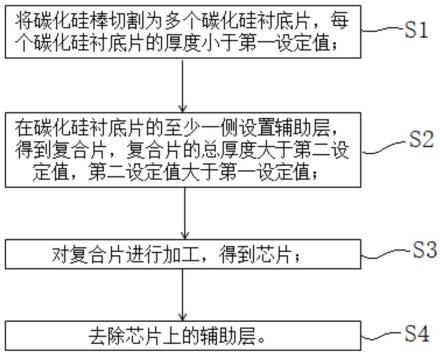

6.第一方面,本发明实施例提供了一种芯片的制备方法,包括以下步骤:

7.s1、将碳化硅棒切割为多个碳化硅衬底片,每个所述碳化硅衬底片的厚度小于第一设定值;

8.s2、在所述碳化硅衬底片的至少一侧设置辅助层,得到复合片,所述复合片的总厚度大于第二设定值,所述第二设定值大于所述第一设定值;

9.s3、对所述复合片进行加工,得到芯片;

10.s4、去除所述芯片上的所述辅助层。

11.进一步地,所述第一设定值小于200μm。

12.进一步地,所述第二设定值为200μm-350μm。

13.进一步地,步骤s2包括:

14.s21、将所述辅助层键合在所述碳化硅衬底片的一侧上,得到所述复合片;

15.s22、对所述复合片进行研磨以调整其厚度、平整度和粗糙度。

16.进一步地,所述辅助层为多晶碳化硅层或氧化铝层。

17.进一步地,步骤s2包括:

18.s21’、将辅料混合后,在所述碳化硅衬底片的碳面进行流延成型;

19.s22’、对所述碳化硅衬底片进行烧结,在所述碳化硅衬底片的碳面形成所述辅助层,得到所述复合片;

20.s23’、对所述复合片进行研磨以调整其厚度、平整度和粗糙度。

21.进一步地,所述辅料为:以碳化硅粉末或氧化铝粉末为骨料,加黏土和聚乙烯醇进行混合得到的混合料。

22.进一步地,步骤s2包括:

23.s21”、在所述碳化硅衬底片的碳面设置粘接剂;

24.s22”、将所述辅助层粘结在所述碳化硅衬底片的碳面上;

25.s23”、对所述碳化硅衬底片进行烧结,得到所述复合片;

26.s24”、对所述复合片进行研磨以调整其厚度、平整度和粗糙度。

27.进一步地,所述粘接剂为:以碳化硅粉末或氧化铝粉末为骨料,加黏土和聚乙烯醇进行混合得到的混合料,所述辅助层为多晶碳化硅层或氧化铝层。

28.第二方面,本发明实施例提供了一种芯片,所述芯片由上述实施例中所述的制备方法制备而成。

29.在本发明实施例中,通过将碳化硅晶锭切割成多个薄衬底片,并在每个薄衬底片上设置辅助层,得到复合片,防止薄衬底片在加工过程破碎,最后再将复合片加工得到碳化硅芯片后,去除辅助层,得到厚度较薄的碳化硅芯片,有效降低芯片制造的成本。

附图说明

30.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本发明的限制。而且在整个附图中,用相同的参考符号表示相同的部件。在附图中:

31.图1为现有技术的芯片的制备方法中的碳化硅棒的切割示意图;

32.图2为本发明实施例的芯片的制备方法的工艺流程图;

33.图3为本发明实施例的芯片的制备方法的流程框图。

34.附图标记:

35.碳化硅棒10;

36.碳化硅衬底片20;

37.辅助层30;

38.芯片40。

具体实施方式

39.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

40.下面根据附图并结合具体实施例描述本发明实施例的芯片的制备方法。

41.根据本发明实施例的芯片的制备方法,包括以下步骤:

42.s1、将碳化硅棒切割为多个碳化硅衬底片,每个碳化硅衬底片的厚度小于第一设定值;

43.s2、在碳化硅衬底片的至少一侧设置辅助层,得到复合片,复合片的总厚度大于第二设定值,第二设定值大于第一设定值;

44.s3、对复合片进行加工,得到芯片;

45.s4、去除芯片上的辅助层。

46.具体地,参见图2和图3,在本发明实施例的芯片的制备方法中,首先,可以将碳化

硅棒10切割为多个碳化硅衬底片20,该碳化硅棒10为碳化硅(sic)晶锭,并且该碳化硅晶锭为单晶碳化硅。每个碳化硅衬底片20的厚度可以小于第一设定值,以使同一个碳化硅棒10可以切割出尽可能薄、尽可能多的衬底片。因为sic晶锭生长速度很慢,一周大概生长5cm,所以切割每一片的厚度越薄,制备出的sic芯片40成本越低。

47.然后,在碳化硅衬底片20的至少一侧上设置辅助层30,碳化硅衬底片20的一侧可以作为外延片(epi),辅助层30可以与薄的碳化硅衬底片20复合得到复合片,复合片的总厚度大于第二设定值,并且第二设定值大于第一设定值。即复合之后的碳化硅衬底片20厚度得到增加,可以有效防止对切割之后的薄的碳化硅衬底片20直接加工而造成在加工过程破碎。

48.接着,可以对复合片进行mosfet(mosfet:metal-oxide-semiconductor field-effect transistor,金氧半场效晶体管)工艺加工处理,得到芯片40。最后,可以将芯片40上的辅助层30去除,得到的芯片40厚度较薄,且整体结构完整,不会破损。通过利用本发明的制备方法可以在同一个碳化硅棒10上切割出更多更薄的碳化硅衬底片20,从而制备出更多更薄的芯片40,有效降低芯片40的制备成本。

49.其中需要说明的是,在本技术中,碳化硅棒10可以是棒状结构,也可以是其他可以切割出碳化硅衬底片20的碳化硅晶锭,将碳化硅棒10切割成碳化硅衬底片20的结构和工作原理,以及对于碳化硅衬底片20的切割厚度的控制方法,这对于本领域技术人员而言是可以理解并且容易实现的,因此不再详细描述。

50.由此,在本发明实施例中,通过将碳化硅棒10切割成多个薄碳化硅衬底片20,使得同一个碳化硅棒10可以切割出更多、更薄的碳化硅衬底片20,再在每个薄碳化硅衬底片20上设置辅助层30,得到复合片,增加碳化硅衬底片20的厚度,防止薄的碳化硅衬底片20在加工过程破碎,最后再将复合片加工得到碳化硅芯片40后,去除辅助层30,得到厚度较薄的碳化硅芯片40,该方法简单可行,可以有效降低芯片40制造的成本。

51.根据本发明的一个实施例,第一设定值小于200μm。第二设定值为200μm-350μm。

52.也就是说,如图2所示,从单晶碳化硅棒10切割的碳化硅衬底片20的厚度可以小于200μm,优选碳化硅衬底片20的厚度为100μm或者更薄,保证可以从碳化硅棒10上切割出尽可能多的碳化硅衬底片20,从而可以从同一碳化硅棒10上制备出更多的芯片40,降低芯片40的制造成本。切割出的碳化硅衬底片20上可以复合有辅助层30,碳化硅衬底片20和辅助层30的总厚度可以为200μm-350μm。

53.需要说明的是,现有的碳化硅衬底片20在平整度ttv(total thickness variation),粗糙度等值,以便能达到芯片40制造要求的前提下,碳化硅衬底片20经标准研磨后的标准厚度为350μm,若碳化硅衬底的厚度小于350μm,容易造成碳化硅衬底在后续工艺制造过程中破损。

54.本技术通过对切割出的更薄的碳化硅衬底上进行增厚处理,保证碳化硅衬底片20和辅助层30的总厚度可以达到后续芯片40制造工艺的要求,最后在制备出的芯片40上通过刻蚀等方法去除辅助层30,使得制备出的芯片40厚度更薄,保证一个碳化硅晶锭可以制备出更多的芯片40,从而有效降低芯片40制造成本。

55.下面对在碳化硅衬底片20设置辅助层30的方法进行详细描述。

56.在本发明的一些具体实施方式中,步骤s2包括:

57.s21、将辅助层30键合在碳化硅衬底片20的一侧上,得到复合片;

58.s22、对复合片进行研磨以调整其厚度、平整度和粗糙度。

59.也就是说,在本发明的芯片的制备方法中,辅助层30可以键合在碳化硅衬底片20上,得到复合片,然后通过对复合片进行研磨以调整其厚度、平整度和粗糙度,保证复合片(碳化硅衬底片20和辅助层30的总厚度为350μm)。

60.可选地,在本技术中,辅助层30可以采用多晶碳化硅层或氧化铝层。单晶sic通过bonding(绑定)的方式来增加碳化硅棒10所切割碳化硅衬底片20的个数。通过利用标准bonding方式,将耐高温材料bonding在单晶sic上,然后标准研磨,调整复合片厚度(350um,现在sic衬底片的标准厚度),平整度ttv(total thickness variation),粗糙度等值,以便能达到芯片40制造要求,防止碳化硅衬底片20在制造过程中破损。

61.同时,在碳化硅衬底片20上bonding的辅助层30可以为相同或者不同的材料,例如:多晶碳化硅,氧化铝等耐高温材料,保证合成材料(复合片)可以承受高于1800℃的温度的半导体工艺。通过采用本技术的制备方法,可以在同一个碳化硅棒10上切割出更多更薄的碳化硅衬底片20,从而制备出更多更薄的芯片40,有效降低芯片40的制备成本。当然,对于本领域技术人员来说,bonding工艺是可以理解并且能够实现的,在本技术中不再详细赘述。

62.在本发明的另一些具体实施方式中,步骤s2包括:

63.s21’、将辅料混合后,在碳化硅衬底片20的碳面进行流延成型;

64.s22’、对碳化硅衬底片20进行烧结,在碳化硅衬底片20的碳面形成辅助层30,得到复合片;

65.s23’、对复合片进行研磨以调整其厚度、平整度和粗糙度。

66.也就是说,在本发明的芯片的制备方法中,还可以利用流延法或多次cvd等方式选择合适的耐高温材料将碳化硅衬底片20增厚。该耐高温材料可以是以碳化硅粉末或氧化铝粉末为骨料,加黏土和聚乙烯醇进行混合得到的辅料。将辅料混合后,在碳化硅衬底片20的碳面进行流延成型。然后通过对碳化硅衬底片20进行高温烧结,在碳化硅衬底片20的碳面形成辅助层30,得到复合片,最后,对复合片进行研磨,调整复合片的厚度、平整度和粗糙度,得到350um的复合片。

67.具体地,在的流延法标准流程中,可以以碳化硅粉末或氧化铝粉末为骨料,加黏土和质量分数为3%-8%的聚乙烯醇(pva)进行混合,在碳化硅衬底的碳面进行流延成型,得到的辅助层30的厚度大致在200um-600um左右,然后通过在800℃-1400℃的温度条件下进行高温烧结。烧结完成后通过标准研磨,可以得到350um的复合片。在后续的芯片40制造过程中,将复合片上的辅助层30通过刻蚀等方式去除后,可以得到厚度在100μm以内的芯片40。

68.通过采用本技术的制备方法,可以在同一个碳化硅棒10上切割出更多更薄的碳化硅衬底片20,从而制备出更多更薄的芯片40,有效降低芯片40的制备成本。当然,流延法的工艺原理是本领域技术人员可以理解并且能够实现的,在本技术中不再详细赘述。

69.在本发明的一些具体实施方式中,步骤s2包括:

70.s21”、在碳化硅衬底片20的碳面设置粘接剂;

71.s22”、将辅助层30粘结在碳化硅衬底片20的碳面上;

72.s23”、对碳化硅衬底片20进行烧结,得到复合片;

73.s24”、对复合片进行研磨以调整其厚度、平整度和粗糙度。

74.换句话说,在本发明的芯片的制备方法中,辅助层30还可以通过粘接剂复合在碳化硅衬底上。

75.具体地,首先,可以在碳化硅衬底片20的碳面涂覆粘接剂,然后将辅助层30粘结在碳化硅衬底片20的碳面上,并对碳化硅衬底片20进行烧结,得到复合片。最后,通过对复合片进行研磨以调整其厚度、平整度和粗糙度,保证可以得到350um的复合片。

76.粘接剂可以采用以碳化硅粉末或氧化铝粉末为骨料,加黏土和聚乙烯醇进行混合得到的混合料,辅助层30可以采用多晶碳化硅层或氧化铝层等耐温温度大于2000℃高温的材料制备而成。通过利用以碳化硅粉末或氧化铝粉末为骨料,加黏土和质量分数为3%-8%的聚乙烯醇(pva)混合后作为粘结剂,将的多晶碳化硅、氧化铝等材料粘结在碳化硅衬底片20的碳面,并进行高温烧结,高温烧结的温度可以达到1700℃以上,烧结完成后进行标准研磨,调整复合片的厚度、平整度和粗糙度,得到350um的复合片。

77.在后续的芯片40制造过程中,将复合片上的辅助层30通过刻蚀等方式去除后,可以得到厚度在100μm以内的芯片40。通过采用本技术的制备方法,可以在同一个碳化硅棒10上切割出更多更薄的碳化硅衬底片20,从而制备出更多更薄的芯片40,有效降低芯片40的制备成本。

78.总而言之,在本发明实施例中,通过将碳化硅晶锭切割成多个薄衬底片,并在每个薄衬底片上设置辅助层30,得到复合片,防止薄衬底片在加工过程破碎,最后再将复合片加工得到碳化硅芯片40后,去除辅助层30,得到厚度较薄的碳化硅芯片40,有效降低芯片40制造的成本。

79.本发明还提供一种芯片40,该芯片40由上述实施例中的制备方法制备而成(参见图2和图3)。由于根据本发明实施例的芯片的制备方法具有上述技术效果,因此,根据本发明的制备方法制备出的芯片40,厚度较薄,成本较低。

80.当然,对于芯片40的具体制备工艺是本领域技术人员可以理解并且能够实现的,在本技术中不再详细赘述。

81.上面结合附图对本发明的实施例进行了描述,但是本发明并不局限于上述的具体实施方式,上述的具体实施方式仅仅是示意性的,而不是限制性的,本领域的普通技术人员在本发明的启示下,在不脱离本发明宗旨和权利要求所保护的范围情况下,还可做出很多形式,均属于本发明的保护之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。