1.本发明涉及一种封装结构。

背景技术:

2.随着集成电路朝向高效能、高密度、低功耗及小尺寸的方向发展,使得前瞻封装的开发也跟着加速。目前,扇出型晶片级封装(fan-out wafer level package,fowlp)可应用于高阶产品。为了降低价格及提高生产率,相关业者亦积极开发扇出型面板级封装(fan-out panel level package,foplp)技术。

3.然而,由于机械取放(pick&place)的误差及介电层材料的热胀冷缩,foplp技术仍有芯片偏移(die shift)的问题,导致芯片无法精确接合于重布线层(redistribution layer,rdl)上,而且,当载板面积愈大时,芯片偏移的幅度愈大,造成封装良率难以提升。

技术实现要素:

4.本发明的目的在于提供一种封装结构,具有提高的封装良率。

5.本发明的一个实施例提出一种封装结构,包括:载板;重布线层,位于载板上,且包括:介电层;导电图案,位于介电层中;以及接垫,位于介电层上,且电性连接导电图案;以及定位层,位于重布线层上,且具有开口,其中,开口于载板的正投影重叠接垫于载板的正投影,且定位层的高度大于接垫的高度。

6.在本发明的一实施例中,上述的定位层的热膨胀系数小于介电层的热膨胀系数。

7.在本发明的一实施例中,上述的定位层的热膨胀系数小于40ppm/℃。

8.在本发明的一实施例中,上述的定位层的厚度大于介电层的厚度。

9.在本发明的一实施例中,上述的定位层的厚度介于10μm至100μm。

10.在本发明的一实施例中,上述的定位层的顶面高度高于接垫的顶面高度。

11.在本发明的一实施例中,上述的定位层的材料为聚酰亚胺(pi)、聚苯并恶唑(pbo)、环氧树脂或硅氧烷(siloxane)。

12.在本发明的一实施例中,上述的封装结构,还包括芯片,位于定位层的开口中,且电性连接接垫。

13.在本发明的一实施例中,上述的芯片具有宽度y,接垫具有宽度x,且开口的口径介于(y 1/2x)至(y 2x)之间。

14.在本发明的一实施例中,上述的定位层的顶面高度低于芯片的顶面高度。

15.本发明的有益效果在于,本发明的封装结构通过设置具有开口的定位层于重布线层上,能够在后续芯片接合的过程中调整芯片的偏移幅度与方位,使得芯片的引脚能够精准对接于重布线层的接垫,从而提高封装结构的良率。

16.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附附图作详细说明如下。

附图说明

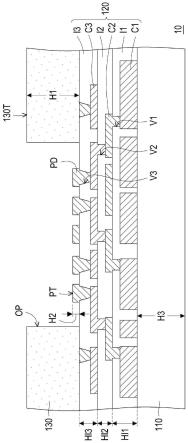

17.图1是依照本发明一实施例的封装结构的剖面示意图。

18.图2a是依照本发明一实施例的封装结构的局部俯视示意图。

19.图2b是沿图2a的剖面线a-a’所作的剖面示意图。

20.附图标记如下:

21.10、20:封装结构

22.110:载板

23.120:重布线层

24.130:定位层

25.130t:顶面

26.140:芯片

27.140t:顶面

28.141:引脚

29.a-a’:剖面线

30.c1、c2、c3:导电图案

31.cl:连接材

32.g:间隙

33.h1:厚度/高度

34.h2、h4:高度

35.h3:厚度

36.hi1、hi2、hi3:厚度

37.i1、i2、i3:介电层

38.op:开口

39.pd:接垫

40.pt:顶面

41.sw:侧壁

42.v1、v2、v3:通孔

43.w:口径

44.x:宽度

45.y:宽度

具体实施方式

46.在附图中,为了清楚起见,放大了层、膜、面板、区域等的厚度。在整个说明书中,相同的附图标记表示相同的元件。应当理解,当诸如层、膜、区域或基板的元件被称为在另一元件“上”或“连接到”另一元件时,其可以直接在另一元件上或与另一元件连接,或者中间元件可以也存在。相反地,当元件被称为“直接在另一元件上”或“直接连接到”另一元件时,不存在中间元件。如本文所使用的,“连接”可以指物理及/或电性连接。再者,“电性连接”或“耦合”可为二元件间存在其它元件。

47.这里使用的术语仅仅是为了描述特定实施例的目的,而不是限制性的。如本文所

使用的,除非内容清楚地指示,否则单数形式“一”、“一个”和“该”旨在包括复数形式,包括“至少一个”或表示“及/或”。如本文所使用的,术语“及/或”包括一个或多个相关所列项目的任何和所有组合。还应当理解,当在本说明书中使用时,术语“包含”及/或“包括”指定所述特征、区域、整体、步骤、操作、元件及/或部件的存在,但不排除一个或多个其它特征、区域、整体、步骤、操作、元件、部件及/或其组合的存在或添加。

48.此外,诸如“下”或“底部”和“上”或“顶部”的相对术语可在本文中用于描述一个元件与另一元件的关系,如图所示。应当理解,相对术语旨在包括除了图中所示的方位之外的装置的不同方位。例如,如果一个附图中的装置翻转,则被描述为在其他元件的“下”侧的元件将被定向在其他元件的“上”侧。因此,示例性术语“下”可以包括“下”和“上”的取向,取决于附图的特定取向。类似地,如果一个附图中的装置翻转,则被描述为在其它元件“下”或“下方”的元件将被定向为在其它元件“上方”。因此,示例性术语“下”或“下方”可以包括上方和下方的取向。

49.考虑到所讨论的测量和与测量相关的误差的特定数量(即,测量系统的限制),本文使用的“约”、“近似”、或“实质上”包括所述值和在本领域普通技术人员确定的特定值的可接受的偏差范围内的平均值。例如,“约”可以表示在所述值的一个或多个标准偏差内,或

±

30%、

±

20%、

±

10%、

±

5%内。再者,本文使用的“约”、“近似”、或“实质上”可依光学性质、蚀刻性质或其它性质,来选择较可接受的偏差范围或标准偏差,而可不用一个标准偏差适用全部性质。

50.图1是依照本发明一实施例的封装结构10的剖面示意图。封装结构10包括:载板110;重布线层120,位于载板110上,且包括:介电层i1;导电图案c1,位于介电层i1中;以及接垫pd,位于介电层i1上,且电性连接导电图案c1;以及定位层130,位于重布线层120上,且具有开口op,其中,开口op于载板110的正投影重叠接垫pd于载板110的正投影,且定位层130的高度h1大于接垫pd的高度h2。

51.在本发明的一实施例的封装结构10中,通过设置具有开口op的定位层130,能够在后续芯片接合的过程中减小芯片偏移的幅度,从而有助于提高封装良率。

52.以下,配合图1,继续说明封装结构10的各个元件的实施方式,但本发明不以此为限。

53.在本实施例中,载板110例如是用以承载重布线层120以及定位层130的载具。在一些实施例中,载板110的热膨胀系数可以介于3至10ppm/℃。载板110的材料可以是玻璃、晶片、或是其它可适用的材料。举例而言,在本实施例中,载板110的材料是热膨胀系数约为8.5ppm/℃的玻璃,但本发明不以此为限。在其他实施例中,载板110可以是晶片,且晶片可具有约为3ppm/℃的热膨胀系数。

54.在本实施例中,介电层i1位于载板110上,且覆盖导电图案c1。介电层i1还可以具有通孔v1,使得接垫pd可以经由通孔v1电性连接导电图案c1。在一些实施例中,除了介电层i1之外,重布线层120还可以包括介电层i2、i3,且接垫pd可以位于介电层i3上,但不以此为限。在其他实施例中,重布线层120可以视需要包括更少或更多层的介电层,例如两层、四层或更多层的介电层。

55.在本实施例中,重布线层120的介电层i1、i2、i3可以依序叠置于载板110上,且介电层i1、i2、i3的热膨胀系数可以分别介于30至80ppm/℃,但不限于此。介电层i1、i2、i3的

材料可以分别选自于聚酰亚胺(polyimide,pi)、聚苯并恶唑(polybenzoxazole,pbo)、苯并环丁烯(benzocyclobutene,bcb)以及其他适合的材料。另外,介电层i1、i2、i3也可以分别具有单层结构或多层结构,多层结构例如上述材料中任意两层或更多层的叠层,可视需要进行组合与变化。

56.在本实施例中,除了导电图案c1之外,重布线层120还可以包括导电图案c2、c3,且导电图案c1、c2、c3可以分别位于介电层i1、i2、i3中,但不以此为限。在其他实施例中,重布线层120可以视需要或配合介电层的层数而包括更少或更多层的导电图案,例如两层、四层或更多层的导电图案。重布线层120可以通过导电图案c1、c2、c3于介电层i1、i2、i3中形成所需的电性连接,且重布线层120可以通过接垫pd电性连接至外部的元件或走线。

57.举例而言,在本实施例中,介电层i1、i2、i3可以分别具有通孔v1、v2、v3,且接垫pd可以穿过通孔v3而连接导电图案c3,导电图案c3可以穿过通孔v2而连接导电图案c2,导电图案c2可以穿过通孔v1而连接导电图案c1,使得接垫pd能够电性连接导电图案c1。接垫pd的数量并无特殊限制,且可视需要设置所需数量的接垫pd。

58.导电图案c1、c2、c3以及接垫pd的材质可以包括导电性良好的金属或合金,例如铝、钼、钛、铜、镍、金、锡、银等金属、其合金、或其组合。举例而言,在一实施例中,导电图案c1、c2、c3以及接垫pd可以各自独立为单层结构或多层结构,多层结构例如包括依续堆叠的钛层、铝层以及钛层,但不以此为限。

59.定位层130可以露出全部的接垫pd。举例而言,在本实施例中,定位层130可以完全不覆盖接垫pd。然而,在一些实施例中,定位层130还可以部分覆盖各个接垫pd,且露出每个接垫pd的一部分。

60.在一些实施例中,定位层130的热膨胀系数可以小于介电层i1、i2、i3中任一层的热膨胀系数。如此一来,还能够有助于抑制或消除封装结构10的翘曲。举例而言,在一些实施例中,定位层130的热膨胀系数可以介于载板110的热膨胀系数与介电层i1、i2、i3中任一层的热膨胀系数之间,且定位层130的厚度h1可以大于载板110的厚度h3,使得定位层130与载板110对重布线层120施加的应力能够互相抵销。在一些实施例中,定位层130的热膨胀系数可以小于40ppm/℃,例如,定位层130的热膨胀系数可以约为30ppm/℃或15ppm/℃。举例而言,定位层130的材料可以是聚酰亚胺(pi)、聚苯并恶唑(pbo)、环氧树脂或硅氧烷(siloxane),但不以此为限。

61.在一些实施例中,定位层130的厚度h1可以大于介电层i1、i2、i3中任一层的厚度。例如,定位层130的厚度h1可以大于介电层i1的厚度hi1;或者,定位层130的厚度h1可以大于介电层i2的厚度hi2;或者,定位层130的厚度h1可以大于介电层i3的厚度hi3;或者,定位层130的厚度h1可以大于介电层i1、i2、i3中的最大厚度。在一些实施例中,定位层130的厚度h1可以介于10μm至100μm,例如约为20μm、50μm或80μm。在一些实施例中,定位层130的顶面130t距离重布线层120的高度h1还可以大于接垫pd的顶面pt距离重布线层120的高度h2。

62.定位层130的开口op的形成方式并无特殊限制。举例而言,在一些实施例中,可以通过光刻工艺来形成开口op。在其他实施例中,可以通过激光钻孔的方式来形成开口op。

63.以下,使用图2a至图2b继续说明本发明的其他实施例,并且,沿用图1的实施例的元件标号与相关内容,其中,采用相同的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明,可参考图1的实施例,在以下的说明中不再重述。

64.图2a是依照本发明一实施例的封装结构20的局部俯视示意图。图2b是沿图2a的剖面线a-a’所作的剖面示意图。封装结构20包括载板110、重布线层120以及定位层130。重布线层120可以包括介电层i1、i2、i3、导电图案c1、c2、c3以及多个接垫pd。定位层130可以具有多个开口op,且多个开口op可以以阵列的方式分布于定位层130中。

65.与如图1所示的封装结构10相比,图2a至图2b所示的封装结构20的不同之处在于:封装结构20还包括多个芯片140,芯片140分别位于定位层130的开口op中,且电性连接接垫pd。

66.举例而言,在本实施例中,芯片140还可以包括多个引脚141,且引脚141可以分别通过连接材cl电性连接至接垫pd。连接材cl例如为焊料、导电胶或其他材料。在一些实施例中,连接材cl与引脚141或接垫pd之间还可以包括其他导电材料或导电胶。

67.在本实施例中,设芯片140具有宽度y,接垫pd具有宽度x,则开口op的口径w可以介于(y 1/2x)至(y 2x)之间。也就是说,芯片140的侧壁sw与定位层130之间的间隙g可以介于1/4x至x之间,即间隙g较佳小于接垫pd的宽度x。如此一来,当通过机械取放将芯片140放置于开口op内以对接引脚141与接垫pd时,能够调整芯片140的偏移幅度与方位,而有助于引脚141精准对接接垫pd,使得芯片140能够精准接合于重布线层120上。

68.在一些实施例中,定位层130的顶面130t距离重布线层120的高度h1可以低于芯片140的顶面140t距离重布线层120的高度h4,但不限于此。在某些实施例中,定位层130的顶面130t距离重布线层120的高度h1仍可以高于芯片140的顶面140t距离重布线层120的高度h4。

69.综上所述,本发明的封装结构通过设置具有开口的定位层于重布线层上,能够在后续芯片接合的过程中调整芯片的偏移幅度与方位,使得芯片的引脚能够精准对接于重布线层的接垫,从而提高封装结构的良率。

70.虽然本发明已以实施例公开如上,然而其并非用以限定本发明,本领域技术人员在不脱离本发明的精神和范围内,当可作些许的更动与润饰,故本发明的保护范围当视随附的权利要求所界定者为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。