用于减少极紫外图案掩模上的可印缺陷的系统及方法

1.相关申请案的交叉参考

2.本技术案主张名叫杨晓春(xiaochun yang)、维克拉姆

·

托拉尼(vikram tolani)及张尧(yao zhang)的发明者在2019年10月10日申请的标题为“极紫外光掩模坯料缺陷优化的快速方法(fast method for extreme ultraviolet photomask blank defect optimization)”的第62/913,659号美国临时申请案的优先权,所述案的全文以引用方式并入本文中。

技术领域

3.本发明大体上涉及用于光刻系统中的图案掩模且更特定来说,涉及一种用于使用成本函数减少euv图案掩模上的可印缺陷的系统及方法。

背景技术:

4.极紫外光刻(euvl)仍是用于下一代光刻的领先技术。然而,euvl面临的一个关键挑战是掩模坯料缺陷率。euv掩模是包含钼及硅的若干交替层的布拉格(bragg)反射器。设计图案以吸收层的形式放置于此多层反射器的顶部上。在掩模坯料的制造期间形成的掩模坯料缺陷显著更改打印于掩模坯料上的随后在euvl期间被转印到样本上的设计图案。修复这些缺陷是具有挑战性的,这是因为缺陷掩埋在euv掩模坯料的多层下方。用于大批量制造的euvl的实施方案需要半导体产业克服这些挑战,然而,当前不存在可用于制造无缺陷掩模坯料的可行解决方案且无用于修复掩埋缺陷的具成本效益的工具。因此,将可期望提供一种解决上文识别的先前方法的缺点的系统及方法。

技术实现要素:

5.根据本公开的一或多个实施例,公开一种用于减少图案掩模上的可印缺陷的系统。在一个实施例中,所述系统包含经配置以通信地耦合到特性化子系统的控制器,所述控制器包含经配置以执行程序指令的一或多个处理器,所述程序指令引起所述一或多个处理器:引导所述特性化子系统执行掩模坯料的检验以产生所述掩模坯料中的一或多个缺陷的缺陷图;基于第一特性及第二特性产生成本函数,所述第一特性包括所述掩模坯料上的所述一或多个缺陷的缺陷暴露面积,所述第二特性包括缺陷区域内的设计图案的图案复杂性;经由非线性优化程序确定指示所述成本函数的最小值的一或多个值;及基于指示所述成本函数的所述最小值的所述经确定一或多个值产生用以调整所述掩模坯料相对于所述设计图案的旋转及平移的一或多个控制信号。

6.根据本公开的一或多个实施例,公开一种用于减少图案掩模上的可印缺陷的系统。在一个实施例中,所述系统包含经配置以通信地耦合到特性化子系统的控制器,所述控制器包含经配置以执行程序指令的一或多个处理器,所述程序指令引起所述一或多个处理器:引导所述特性化子系统执行掩模坯料的检验以产生所述掩模坯料中的一或多个缺陷的缺陷图;基于第一特性及第二特性产生成本函数,所述第一特性包括所述掩模坯料上的所

述一或多个缺陷的缺陷暴露面积,所述第二特性包括缺陷区域内的设计图案的图案复杂性;经由非线性优化程序确定指示所述成本函数的最小值的一或多个值;确定指示所述掩模坯料对于所述设计图案的良好程度的一或多个度量;及基于指示所述成本函数的所述最小值的所述经确定一或多个值或指示所述掩模坯料对于所述设计图案的良好程度的所述一或多个度量中的至少一者产生用以调整所述掩模坯料相对于所述设计图案的旋转及平移的一或多个控制信号。

7.根据本公开的一或多个实施例,公开一种用于减少图案掩模上的可印缺陷的方法。在一个实施例中,所述方法包含引导特性化子系统执行掩模坯料的检验以产生所述掩模坯料中的一或多个缺陷的缺陷图。在另一实施例中,所述方法包含基于第一特性及第二特性产生成本函数,所述第一特性包括所述掩模坯料上的所述一或多个缺陷的缺陷暴露面积,所述第二特性包括缺陷区域内的设计图案的图案复杂性。在另一实施例中,所述方法包含经由非线性优化程序确定指示所述成本函数的最小值的一或多个值。在另一实施例中,所述方法包含基于指示所述成本函数的所述最小值的所述经确定一或多个值产生用以调整所述掩模坯料相对于所述设计图案的旋转及平移的一或多个控制信号。

8.根据本公开的一或多个实施例,公开一种用于减少图案掩模上的可印缺陷的方法。在一个实施例中,所述方法包含引导特性化子系统执行掩模坯料的检验以产生所述掩模坯料中的一或多个缺陷的缺陷图。在另一实施例中,所述方法包含基于第一特性及第二特性产生成本函数,所述第一特性包括所述掩模坯料上的所述一或多个缺陷的缺陷暴露面积,所述第二特性包括缺陷区域内的设计图案的图案复杂性。在另一实施例中,所述方法包含经由非线性优化程序确定指示所述成本函数的最小值的一或多个值。在另一实施例中,所述方法包含确定指示所述掩模坯料对于所述设计图案的良好程度的一或多个度量。在另一实施例中,所述方法包含基于指示所述成本函数的所述最小值的所述经确定一或多个值或指示所述掩模坯料对于所述设计图案的良好程度的所述一或多个度量中的至少一者产生用以调整所述掩模坯料相对于所述设计图案的旋转及平移的一或多个控制信号。

9.应理解,前文概述及下文详细描述两者仅是示范性及解释性的且未必限制如主张的本发明。并入本说明书中且构成本说明书的部分的随附图式说明本发明的实施例且与概述一起用于解释本发明的原理。

附图说明

10.所属领域的技术人员通过参考附图可更佳理解本公开的许多优点,其中:

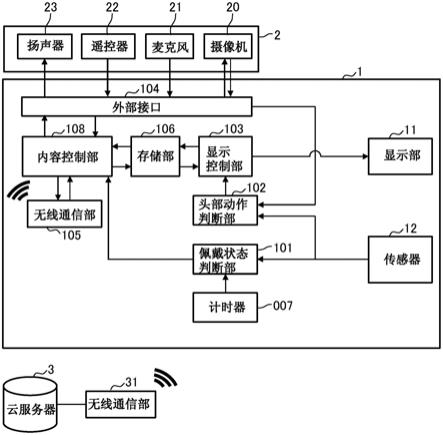

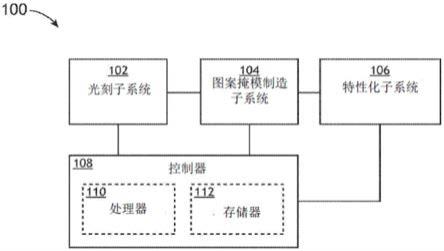

11.图1a是说明根据本公开的一或多个实施例的用于减少图案掩模中的可印缺陷的系统的概念图。

12.图1b是说明根据本公开的一或多个实施例的极紫外光刻子系统的概念图。

13.图1c是说明根据本公开的一或多个实施例的特性化子系统的概念图。

14.图2a是说明根据本公开的一或多个实施例的在将设计图案打印到掩模坯料上之前具有瑕疵的掩模坯料的概念图。

15.图2b是说明根据本公开的一或多个实施例的在已将设计图案打印到掩模坯料上之后具有瑕疵的图案掩模的概念图。

16.图3a是说明根据本公开的一或多个实施例的经转印掩模坯料缺陷对样本的设计

图案的影响的概念图。

17.图3b是说明根据本公开的一或多个实施例的经转印掩模坯料缺陷对样本的设计图案的影响的概念图。

18.图4是根据本公开的一或多个实施例的用于减少图案掩模中的可印缺陷的方法的概念流程图。

19.图5是说明根据本公开的一或多个实施例的掩模坯料移位的实例的概念图。

20.图6是说明根据本公开的一或多个实施例的基于成本函数的设计图案移位建议的实例的概念图。

21.图7a是说明根据本公开的一或多个实施例的图案复杂性的概念图。

22.图7b是说明根据本公开的一或多个实施例的图案复杂性的概念图。

23.图8是说明根据本公开的一或多个实施例的将一裕度添加到掩模坯料缺陷的概念图。

24.图9说明根据本公开的一或多个实施例的用于使用成本函数减少图案掩模中的可印缺陷的方法的流程图。

25.图10说明根据本公开的一或多个实施例的用于使用成本函数减少图案掩模中的可印缺陷的方法的流程图。

具体实施方式

26.已关于某些实施例及其特定特征特别展示且描述本公开。将本文中陈述的实施例视为说明性而非限制性。所属领域的技术人员将容易了解,可做出形式及细节上的各种改变及修改而不脱离本公开的精神及范围。现将详细参考在随附图式中说明的所公开标的物。

27.现将详细参考在随附图式中说明的所公开标的物。

28.euvl仍是用于下一代光刻的领先技术。然而,此技术面临的一个关键挑战是掩模坯料缺陷率。当前,不存在可用于制造无缺陷掩模坯料的可行解决方案且无用于修复掩模坯料上的缺陷的具成本效益的工具。因此,在对良率无任何影响的情况下容忍一些这些缺陷的能力是至关重要的。已出现缺陷避免及缓解技术作为用于增加掩模缺陷的容忍度的高度有效方法。当前掩模缺陷缓解/避免方法使用缺陷与吸收边缘之间的距离以计算缺陷对图案临界尺寸的影响,这是不足够的。此类方法未能考虑复杂图案区域上的缺陷的扩展受影响区域。接着计算禁止移位矩形/禁止重新定位立方体(psr/prc)以寻找最小化经重叠psr/prc的数目的点。替代地,当前使用的另一方法是开发经配置以通过梯度下降而解决非凸优化问题的光学模型。

29.本公开的实施例涉及一种根据本公开的一或多个实施例的用于减少euv光掩模上的可印缺陷的系统及方法。具体来说,本公开的实施例涉及基于缺陷的暴露区域及图案复杂性使用成本函数,使得成本函数可经配置以缓解用于euvl中的euv光掩模中的可印掩模缺陷。可使用快速非线性优化程序最小化成本函数以估计用于最佳地隐藏吸收层中的一或多个缺陷的一组参数(例如,旋转及平移)。成本函数可经配置以提供对于euv掩模制造的在合理过程时间内最小化掩模坯料缺陷对晶片的影响的一或多个缺陷隐藏解决方案。例如,系统可经配置以建议隐藏解决方案,使得掩模坯料缺陷由光掩模的吸收层隐藏而对图案可

印性具有最小化缺陷影响。隐藏坯料缺陷(而非经暴露缺陷)在样本中较不可印,因此其对图案阈值尺寸的不利影响在制造期间是可容忍的。此外,缺陷缓解减少euv坯料(其制造非常昂贵)的浪费,借此改进良率。

30.大体上参考图1a到10,描述根据本公开的一或多个实施例的用于使用成本函数减少euv图案掩模上的可印缺陷的系统及方法。

31.图1a是说明根据本公开的一或多个实施例的用于使用成本函数减少euv图案掩模上的可印缺陷的系统100的概念图。在一个实施例中,系统100包含用于将一或多个图案光刻打印到样本128的极紫外(euv)光刻子系统102。euv光刻子系统102可包含所属领域中已知的任何光刻打印工具。例如,euv光刻子系统102可包含(但不限于)扫描仪或步进器。euv光刻子系统102可通过照明图案掩模而操作,所述图案掩模接着根据所述图案掩模上的掩模元件而反射照明。光刻系统内的光学元件(例如,一组投影光学器件)可接着基于由所述组投影光学器件收集的从图案掩模反射的照明而产生样本上的图案掩模的图像。

32.在另一实施例中,系统100包含用于制造用于euv光刻子系统102中的图案掩模的一或多个图案掩模制造子系统104。一或多个图案掩模制造子系统104可包含所属领域中已知的适用于图案掩模制造的任何制造工具。例如,一或多个图案掩模制造子系统104可包含(但不限于)一或多个沉积工具、一或多个计量工具或类似者。一或多个图案掩模制造子系统104可经配置以制造所属领域中已知的任何类型的图案掩模,包含(但不限于)极紫外图案掩模。euv图案掩模可包含多层反射器部分、封盖层及吸收层中的至少一者。例如,一或多个图案掩模制造子系统104可经配置以基于成本函数产生具有经调整设计图案的euv图案掩模,如本文中相对于图4到10进一步论述。

33.在另一实施例中,系统100包含经配置以在掩模坯料500(图5中展示)的层中执行缺陷检验的特性化子系统106。本文中应注意,特性化子系统106可包含(但不限于)检验子系统或计量子系统。特性化子系统106可包含所属领域中已知的任何检验子系统106,其包含(但不限于)基于光学的检验工具、基于带电粒子的检验工具、检视工具及类似者。特性化子系统106可包含所属领域中已知的任何基于成像的计量子系统106,其包含(但不限于)基于光学成像的计量工具、扫描电子显微镜(sem)工具或类似者。

34.在另一实施例中,系统100包含控制器108。在另一实施例中,控制器108包含经配置以执行维持于存储器媒体112上的程序指令的一或多个处理器110。在此方面,控制器108的一或多个处理器110可执行贯穿本公开描述的各种过程步骤中的任何者。此外,控制器108可通信地耦合到掩模支撑装置124及/或样本载物台130以引导图案掩模122上的图案元素到样本128的转印。本文中应注意,本发明的euv光刻子系统102可实施贯穿本公开描述的任何图案掩模设计。

35.特性化子系统106可提供与掩模坯料层有关的各种类型的特性化资料。例如,特性化子系统106可提供缺陷特性化数据。例如,特性化子系统106可提供掩模坯料层中的缺陷的位置、大小、数目或类型。

36.图1b是说明根据本公开的一或多个实施例的euv光刻子系统102的概念图。在一个实施例中,euv光刻子系统102包含经配置以产生一或多个照明光束116的照明源114。照明光束116可包含一或多个所选择的波长的euv光。例如,照明光束116的光谱的至少一部分可包含与适用于半导体制造的基于euv的光刻装置相关联的波长,例如(但不限于)13.5nm或

类似者。在2014年12月23日颁予王(wang)的第8,916,831号美国专利中大体上描述基于euv的光刻,所述专利的全文以引用方式并入本文中。

37.在一个实施例中,照明源114包含极紫外照明源114。例如,euv照明源114可包含宽带等离子体(bbp)照明源。在此方面,照明光束116可包含由等离子体发射的辐射。例如,bbp照明源114可包含(但不需要包含)经配置以将照明聚焦到气体体积中,从而引起能量由气体吸收以便产生或维持适用于发射辐射的等离子体的一或多个泵激源(例如,一或多个激光器)。此外,等离子体辐射的至少一部分可用作照明光束116。在另一实施例中,照明源114可包含能够依一或多个所选择的波长发射辐射的一或多个激光器。

38.在另一实施例中,照明源114经由照明路径118将照明光束116引导到图案掩模122。照明路径118可包含适用于将照明光束116引导、聚焦于图案掩模122上及/或塑形照明光束116的一或多个照明光学器件120。例如,照明光学器件120可包含一或多个透镜、一或多个聚焦元件或类似者。此外,照明光学器件120可包含所属领域中已知的适用于引导及/或聚焦照明光束116的任何反射光学元件。例如,照明光学器件120可包含适用于引导及/或聚焦低波长光(例如,euv光及类似者)的反射光学器件,例如(但不限于)平面镜或曲面镜(例如,椭圆镜、抛物面镜或类似者)。

39.照明光学器件120可进一步包含适用于塑形照明光束116及/或控制照明光束116在掩模122上的入射角的范围(例如,照明光瞳分布)的一或多个额外照明路径组件。例如,照明路径组件可包含(但不限于)一或多个孔隙、一或多个变迹器、一或多个均质器、一或多个扩散器、一或多个偏光器或一或多个滤波器。

40.在另一实施例中,euv光刻子系统102可包含掩模支撑装置124。掩模支撑装置124可经配置以固定掩模122。

41.在另一实施例中,euv光刻子系统102包含经配置以将由一或多个照明光束116照明的图案掩模122的图像投影到安置于样本载物台130上的样本128的表面上的一组投影光学器件126。例如,所述组投影光学器件126可经配置以将图案掩模122的图像投影到样本128上的抗蚀剂层132上以在抗蚀剂层132上产生(例如,暴露或类似者)对应于图案掩模122上的图案元素的经打印图案元素。在另一实施例中,掩模支撑装置124可经配置以致动或定位图案掩模122。例如,掩模支撑装置124可将图案掩模122致动到相对于euv光刻子系统102的投影光学器件126的所选择的位置。

42.可(例如,通过euv光刻子系统102)以所属领域中已知的任何成像配置利用图案掩模122。例如,图案掩模122可为其中图案元素被正成像为样本128的抗蚀剂层132的经打印图案元素的正掩模(例如,明场掩模)。通过另一实例,图案掩模122可为其中图案掩模122的图案元素形成样本128的抗蚀剂层132的经负打印图案元素(例如,间隙、空间或类似者)的负掩模(例如,暗场掩模)。

43.如贯穿本公开使用,术语“样本”大体上是指由半导体或非半导体材料形成的衬底(例如,晶片或类似者)。例如,半导体或非半导体材料可包含(但不限于)单晶硅、砷化镓及磷化铟。样本可包含一或多个层。例如,此类层可包含(但不限于)抗蚀剂、电介质材料、导电材料及半导电材料。许多不同类型的此类层在所属领域中已知,且如本文中使用的术语样本希望涵盖其上可形成全部类型的此类层的样本。形成于样本上的一或多个层可经图案化或未经图案化。例如,样本可包含各自具有可重复图案化特征的多个裸片。此类材料层的形

成及处理可最终导致完成装置。许多不同类型的装置可形成于样本上,且如本文中使用的术语样本希望涵盖其上制造所属领域中已知的任何类型的装置的样本。此外,为了本公开的目的,术语样本及晶片应被解译为可互换的。另外,为了本公开的目的,术语图案化装置、图案掩模、掩模及分划板应被解译为可互换的。

44.图1c是说明根据本公开的一或多个实施例的特性化子系统106的概念图。在一个实施例中,特性化子系统106包含用于产生照明光束142的照明源140。照明光束142可包含一或多个所选择的波长的光,包含(但不限于)紫外光(uv)辐射、可见光辐射或红外光(ir)辐射。本文中应注意,特性化子系统106可包含所属领域中已知的任何类型的特性化子系统106而不限制本公开的范围。例如,虽然在图1c中未描绘,但特性化子系统106可包含极紫外(euv)特性化子系统、深紫外光(duv)特性化子系统或类似者而不脱离本公开的范围。

45.在另一实施例中,照明源140经由照明路径144将照明光束142引导到样本128。照明路径144可包含一或多个透镜146。此外,照明路径144可包含适用于修改及/或调节照明光束142的一或多个额外光学组件148。例如,一或多个光学组件148可包含(但不限于)一或多个偏光器、一或多个滤波器、一或多个光束分离器、一或多个扩散器、一或多个均质器、一或多个变迹器或一或多个光束塑形器。在一个实施例中,照明路径144包含光束分离器150。在另一实施例中,特性化子系统106包含用于将照明光束142聚焦到样本128上的物镜152。

46.在另一实施例中,特性化子系统106包含经配置以通过集光路径156捕获从样本128发出的辐射的一或多个检测器154。集光路径156可包含用于引导及/或修改由物镜152收集的照明的多个光学元件,包含(但不限于)一或多个透镜146、一或多个滤波器、一或多个偏光器、一或多个光束阻断器或一或多个光束分离器。

47.例如,检测器158可接收由集光路径156中的元件(例如,物镜152、一或多个透镜146或类似者)提供的样本128的图像。通过另一实例,检测器158可接收(例如,经由镜面反射、漫反射及类似者)从样本128反射或散射的辐射。通过另一实例,检测器158可接收由样本产生的辐射(例如,与照明光束142的吸收相关联的发光及类似者)。此外,本文中应注意,一或多个检测器158可包含所属领域中已知的适用于测量从样本128接收的照明的任何光学检测器。例如,检测器158可包含(但不限于)ccd检测器、tdi检测器、光电倍增管(pmt)、突崩光电二极管(apd)或类似者。

48.在另一实施例中,特性化子系统106通信地耦合到系统100的控制器108。在此方面,控制器108可经配置以接收特性化数据,例如(但不限于)缺陷特性化数据。

49.控制器108的一或多个处理器110可包含所属领域中已知的任何处理器或处理元件。为了本公开的目的,术语“处理器”或“处理元件”可被广泛地定义以涵盖具有一或多个处理或逻辑元件(例如,一或多个微处理器装置、一或多个专用集成电路(asic)装置、一或多个场可编程门阵列(fpga)或一或多个数字信号处理器(dsp))的任何装置。在此意义上,一或多个处理器110可包含经配置以执行算法及/或指令(例如,存储于存储器中的程序指令)的任何装置。在一个实施例中,一或多个处理器110可体现为桌面计算机、主计算机系统、工作站、图像计算机、并行处理器、网络计算机或经配置以执行程序(其经配置以操作系统100或结合系统100操作)的任何其它计算机系统,如贯穿本公开所描述。

50.此外,系统100的不同子系统(例如系统100的子系统102、104、106)可包含适用于实行本公开中描述的步骤的至少一部分的处理器或逻辑元件。因此,上文描述不应被解译

为对本公开的实施例的限制而仅为说明。此外,贯穿本公开描述的步骤可通过单个控制器108或替代地多个控制器实行。另外,控制器108可包含容置于共同外壳中或多个外壳内的一或多个控制器。以此方式,任何控制器或控制器的组合可被单独封装为适用于集成到系统100中的模块。

51.存储器媒体112可包含所属领域中已知的适用于存储可由相关联的一或多个处理器110执行的程序指令的任何存储媒体。例如,存储器媒体112可包含非暂时性存储器媒体。通过另一实例,存储器媒体112可包含(但不限于)只读存储器(rom)、随机存取存储器(ram)、磁性或光学存储器装置(例如,磁盘)、磁带、固态驱动及类似者。应进一步注意,存储器媒体112可与一或多个处理器110一起容置于共同控制器外壳中。在一个实施例中,存储器媒体112可相对于一或多个处理器110及控制器108的物理位置远程定位。例如,控制器108的一或多个处理器110可存取可通过网络(例如,因特网、内部网络及类似者)存取的远程存储器(例如,服务器)。

52.图2a到2b说明图案化前瑕疵及图案化后瑕疵的比较。在一个实施例中,掩模坯料200中的一或多个缺陷202(或瑕疵202)在掩模制造之后显现为图案掩模206上的一或多个缺陷。这些缺陷可在光刻之后打印且显著影响转印到样本的图案。例如,缺陷208可与设计图案的暴露区域的部分重叠,而其它缺陷204可不与设计图案的暴露区域重叠。与图案的暴露区域重叠的缺陷208可显著影响在光刻期间转印到样本的图案。

53.图3a到3b说明经转印坯料缺陷对样本的设计图案的影响。如本文中先前论述,euvl的一个关键挑战是euv掩模坯料缺陷率。euv掩模是包含钼及硅的若干交替层的布拉格反射器。设计图案以吸收层的形式放置于此多层反射器的顶部上。掩模坯料缺陷在坯料的制造期间形成。在掩模的制造期间形成的掩模坯料缺陷显著更改打印于样本上的设计图案。图3a描绘其中掩模坯料300无缺陷的样本图案,且图3b描绘其中掩模坯料304在掩模坯料304的多层部分302中包含掩埋粒子缺陷306的样本图案。如图3b中展示,此掩埋粒子缺陷306影响转印到样本的设计图案。例如,如图3b中展示,掩埋粒子缺陷308经转印到样本且在样本图案中产生类似缺陷308。修复这些缺陷是非常具有挑战性的,这是因为缺陷掩埋在多层下方。

54.图4是根据本公开的一或多个实施例的用于减少euv图案掩模中的可印缺陷的方法400的概念流程图。本文中应注意,方法400的步骤可全部或部分通过系统100实施。然而,应进一步认识到,方法400不限于系统100,其中额外或替代系统级实施例可实行方法400的步骤的全部或部分。

55.在一个实施例中,系统100经配置以执行掩模坯料500的图案化前检验(步骤402)。例如,系统100可经配置以引导特性化子系统106检验掩模坯料500的层。例如,特性化子系统104可经配置以产生掩模坯料500的层的缺陷图(如由图5展示),所述缺陷图包含掩模坯料500的层中的一或多个缺陷502的位置、大小、数目及类型。在此方面,可调整(旋转及/或平移)掩模坯料500以避免将设计图案504放置于掩模坯料500上的一或多个缺陷502上(如由510展示)。在508中展示不良解决方案,其中设计图案504触碰一或多个缺陷502的部分。

56.在另一实施例中,系统100的控制器108经配置以基于掩模制造的第一特性及第二特性,以旋转及平移作为参数来产生成本函数(步骤404)。例如,成本函数可为基于缺陷暴露面积及图案复杂性。例如,成本函数可为基于包含缺陷暴露面积(例如图1b到1c中展示的

掩模122)的第一特性。在另一例子中,成本函数可为基于包含缺陷区域内的设计图案的图案复杂性的第二特性。本文中应注意,经产生成本函数可经配置以避免高优先级缺陷、由吸收层隐藏缺陷且避免具有高复杂性的图案上的缺陷。

57.成本函数可由方程式1(eqn.1)展示并描述:

58.cost

θ

(δx,ay)=∑iwi(waarea(d

θ,i

(δx,δy)∩p) wccomplexity(d

θ,i

(δx,δy)∩p))

ꢀꢀꢀ

eqn.1

59.其中θ是绕坯料中心旋转有缺陷掩模坯料500的角度。在一个实施例中,系统100经配置以支持绕坯料中心按90度增量的旋转。例如,系统100可经配置以支持绕坯料中心的0

°

、90

°

、180

°

、270

°

或类似者的旋转。本文中应注意,对旋转角度的限制可由掩模写入器确定。掩模坯料500相对于设计图案在x方向及y方向上的平移(或移位)分别由δx、δy表示。本文中应注意,在确定指示成本函数的最小值的一或多个值之后,可将掩模坯料旋转及/或平移的结果包含于经建议解决方案的输出参数中(例如,步骤406)。

60.经掩模旋转及平移的缺陷的区域由d

θ,i

(δx,θy)表示。相交计算由计算符∩表示,且掩模图案由p表示。因此,d

θ,i

(δx,θy)∩p表示以坯料旋转及平移作为参数且由掩模图案p(其由多边形(或图像)表示)确定的缺陷i的暴露面积。

61.wa及wc分别是缺陷上方的暴露面积及图案复杂性的权重。每一特性的权重控制哪一特性比另一特性更重要。例如,缺陷暴露的更高权重指示在吸收层下方隐藏缺陷比将缺陷放置于复杂图案上更关键。通过另一实例,图案复杂性的更高权重指示避免具有高复杂性的图案上的缺陷比缺陷暴露更关键。本文中应注意,图案复杂性通常更关键,这是因为高复杂性图案上的缺陷对图案临界尺寸(cd)的影响更大。

62.在一个实施例中,图案复杂性(complexity(d

θ,i

(δx,δy)∩p)是由缺陷区域中的图案的临界尺寸(cd)及缺陷区域内的小cd图案的密度确定。例如,如图7a到7b中展示,图案cd越小,此类图案的密度越高且因此,其图案复杂性越高。

63.在一个实施例中,经坯料旋转及平移的缺陷的暴露面积(area(d

θ,i

(δx,δy)∩p))由未被吸收层覆盖的缺陷的部分确定。例如,可使用一或多个缺陷区域与设计图案的暴露区域的经累加重叠面积确定缺陷暴露面积。area(d

θ,i

(δx,δy)∩p)表示函数,所述函数计算具有掩模图案的缺陷的暴露面积相较于总缺陷面积的比率。例如,area(d

θ,i

(δx,δy)∩p)可等于1.0,使得缺陷区域与掩模图案的暴露区域之间存在完全重叠(例如,100%暴露)。通过另一实例,area(d

θ,i

(δx,δy)∩p)可等于0.0,使得缺陷完全被吸收剂覆盖(例如,0%暴露)。

64.wi表示基于缺陷类别或类型的缺陷优先级。本文中应注意,一些缺陷相对易于修复。此外,一些缺陷对晶片cd的负面影响比其它缺陷小。在此方面,这些缺陷将被给予比难以修复的缺陷(例如坯料多层中的掩埋缺陷)或对于晶片cd更关键的缺陷更低的权重。难以修复或对于晶片cd更关键的所述缺陷将被给予更高权重以确保此类缺陷由吸收层最大地隐藏且避免具有高复杂性的设计图案。

65.在另一实施例中,系统100经配置以使用非线性优化程序确定指示成本函数的最小值的一或多个值(步骤406)。例如,系统100的控制器108可经配置以使用方程式2(eqn.2)确定指示成本函数的最小值的一或多个值。例如,eqn.2可经配置以确定成本函数的最佳参数(例如,旋转及平移)。在此方面,成本函数的最小值可经配置以对用户建议旋转掩模坯料

的角度。此外,成本函数的最小值可经配置以对用户建议在x方向及y方向上平移(移位)掩模坯料的量(如图5到6中展示)。例如,可将掩模坯料500旋转270度,使得一或多个缺陷502不影响设计图案504。

66.eqn.2由以下项展示并描述:

[0067][0068]

在一个实施例中,系统100利用成本函数(eqn.2)的最小值以确定最佳离散旋转角度及移位量,使得缺陷被吸收层隐藏,如图6中展示。在另一实施例中,系统100利用成本函数的最小值以确定最佳离散旋转角度及移位量,使得避免高复杂性图案上的缺陷,如图7a到7b中展示。

[0069]

图6是说明根据本公开的一或多个实施例的掩模坯料移位的实例的概念图。在一个实施例中,系统100经配置以基于在步骤406中确定的成本函数的最小值调整掩模坯料的旋转及平移。例如,如图6中展示,可调整掩模坯料的旋转及平移,使得缺陷被掩模600的吸收层602隐藏。例如,可通过调整掩模坯料的旋转及平移而使定位于暴露区域604中的缺陷606a隐藏在吸收层602下方(如由缺陷606b指示)。在另一例子中,可通过调整掩模坯料的旋转及平移而使定位于暴露区域604中的缺陷608a隐藏在吸收层602下方(如由缺陷608b指示)。相较于原始图案层设计,优化结果提供掩模坯料平移及旋转的解决方案。

[0070]

在一些实施例中,系统100经配置以产生指示经调整掩模坯料对于设计图案的良好程度的一或多个度量。例如,系统100的控制器108可经配置以产生指示掩模坯料对于设计图案的良好程度的一或多个度量(步骤408)。指示掩模坯料对于指定图案的良好程度的一或多个度量由方程式3到4(eqn.3到4)展示并描述:

[0071][0072][0073]

其中n是缺陷的总数。在一个实施例中,一或多个度量包含在0到1之间的分数。例如,系统100的控制器108可经配置以使用eqn.3到4确定在0到1之间的分数。更接近1的分数指示掩模坯料是对于指定设计图案p的良好匹配。分数给予用户坯料对于掩模图案p的良好程度的直观指示。本文中应注意,此分数可由用户使用以针对给定掩模图案p从掩模库选择最适合掩模坯料。例如,可选择来自掩模坯料库的最佳掩模坯料,使得全部掩模坯料被最佳利用。因此,其可最大地减少坯料浪费且大大地改进制造环境中的良率。

[0074]

在一个实施例中,系统100经配置以产生用以调整掩模坯料相对于设计图案的旋转及平移的一或多个控制信号(步骤410)。例如,可基于成本函数的最小值产生一或多个控制信号。例如,成本函数的最小值可包含最佳旋转及平移量,使得当在掩模坯料上写入设计图案时缺陷将被吸收层隐藏。

[0075]

在一些实施例中,系统100的一或多个图案掩模制造子系统104可经配置以将经调整设计图案打印于掩模坯料500上以产生euv掩模(例如图1b到1c中展示的掩模122)(步骤412)。例如,一或多个图案掩模制造子系统104可经配置以将经调整图案打印于掩模坯料上,使得掩模坯料上的一或多个缺陷被掩模坯料的吸收层隐藏。在此方面,一或多个坯料缺陷经隐藏,使得其不显著影响转印到样本的图案。

[0076]

本文中应注意,利用由eqn.1展示并描述的成本函数允许用户在合理时间量内执行坯料缺陷优化。例如,针对近似120个缺陷,系统100的运行时间可为近似1分钟及33秒。通过另一实例,针对近似1000个缺陷,系统100的运行时间可为近似30分钟。

[0077]

本文中应注意,可期望将缺陷定位成远离吸收边缘所选择的距离,这是因为即使被吸收层隐藏的缺陷在其太接近吸收边缘的情况下仍可被暴露。此外,此类缺陷还可影响晶片cd。在一些实施例中,如在图8中展示,可通过将裕度800添加到成本函数中的缺陷大小而扩展缺陷。例如,在成本函数优化(步骤406)期间,优化器可移位掩模坯料比其将以其它可能方式被移位的情况更多(例如,如由图8中的806b及806c展示),使得缺陷定位成远离吸收边缘808所选择的距离。例如,优化器可移位掩模坯料,使得缺陷806a定位于点806b处而非位置806c处,使得缺陷定位成进一步远离吸收边缘808。

[0078]

在一些实施例中,系统100经配置以使用在步骤412中产生的euv掩模执行euv光刻(euvl)(步骤414)。例如,euv光刻子系统102可经配置以使用euv掩模执行euv光刻以将euv掩模上的设计图案转印到样本128。

[0079]

在额外/替代实施例中,可从一或多个经模拟空间像计算图案复杂性。例如,可通过正向光刻模拟从设计图案获得空间像。在此方面,接着可通过经模拟空间像的对数斜率计算图案复杂性。

[0080]

图9说明根据本公开的一或多个实施例的用于使用成本函数减少euv光掩模中的可印缺陷的方法900的流程图。本文中应注意,方法900的步骤可全部或部分通过系统100实施。然而,应进一步认识到,方法900不限于系统100,其中额外或替代系统级实施例可实行方法900的步骤的全部或部分。

[0081]

在步骤902中,执行掩模坯料500的坯料检验以产生缺陷图。在一个实施例中,系统100经配置以引导特性化子系统106执行掩模坯料的图案化前检验以产生掩模坯料500的层的缺陷图。例如,特性化子系统106可经配置以识别掩模坯料500中的一或多个缺陷502的数目、大小、类型及位置。

[0082]

在步骤904中,使用旋转及平移作为参数产生成本函数。在一个实施例中,系统100的控制器108经配置以基于成本函数(例如eqn.1中展示的成本函数)的第一特性及第二特性以旋转及平移作为成本函数的参数来产生成本函数。例如,成本函数的第一特性可包含掩模坯料上的缺陷区域的暴露面积。通过另一实例,成本函数的第二特性可包含缺陷位于其下方的设计图案的图案复杂性。

[0083]

在一个实施例中,系统100经配置以通过缺陷区域中的图案的cd及缺陷区域内的小cd图案的密度确定图案复杂性。在另一实施例中,系统100经配置以使用未被吸收层覆盖的缺陷的部分确定在设计图案的暴露区域下方的缺陷的暴露面积。

[0084]

在步骤906中,经由非线性优化程序产生指示成本函数的最小值的一或多个值。在一个实施例中,使用系统100的控制器108,通过非线性优化程序最小化成本函数以确定一

或多个最佳旋转及平移参数。例如,可使用约束二次近似优化(bobyqa)最小化成本函数以确定旋转及平移的参数(如由eqn.2展示)。例如,成本函数的最小值可指示应将具有特定图案的掩模坯料相对于掩模坯料中心旋转90度且在x方向上移位近似-1.1268μm且在y方向上移位0.1956μm。

[0085]

本文中应注意,可使用任何非线性优化程序。因此,不应将上文描述解释为限制本公开的范围。

[0086]

在步骤908中,基于在步骤906中确定的一或多个值产生用以调整掩模坯料相对于设计图案的旋转及平移的一或多个控制信号。例如,如图5中展示,可基于成本函数的最小值的最佳旋转及平移参数将掩模坯料500旋转及平移所选择的量,使得掩模坯料500上的缺陷502不位于设计图案504的暴露区域下方(例如,被吸收层隐藏)。

[0087]

在步骤910中,使用经调整设计图案产生掩模以执行样本的光刻。例如,所产生的掩模可为待由euv光刻子系统(例如在图1b到1c中展示的euv光刻子系统102)使用的euv光掩模。

[0088]

图10说明根据本公开的一或多个实施例的用于使用成本函数减少euv光掩模中的可印缺陷的额外/替代方法1000的流程图。本文中应注意,方法1000的步骤可全部或部分通过系统100实施。然而,应进一步认识到,方法1000不限于系统100,其中额外或替代系统级实施例可实行方法1000的步骤的全部或部分。

[0089]

在步骤1002中,执行掩模坯料500的坯料检验以产生缺陷图。在一个实施例中,系统100经配置以引导特性化子系统106产生掩模坯料500的层的缺陷图。例如,特性化子系统106可经配置以识别掩模坯料500中的缺陷的数目、其大小、类型及位置。

[0090]

在步骤1004中,使用旋转及平移作为参数产生成本函数。在一个实施例中,系统100的控制器108经配置以基于成本函数(例如通过eqn.1展示的成本函数)的第一特性及第二特性产生成本函数。例如,成本函数的第一特性可包含掩模坯料上的缺陷区域的暴露面积。通过另一实例,成本函数的第二特性可包含缺陷区域内的设计图案的图案复杂性。

[0091]

在步骤1006中,经由非线性优化程序产生指示成本函数的最小值的一或多个值。在一个实施例中,通过非线性优化程序最小化成本函数以寻找旋转及平移的参数。例如,可使用约束二次近似优化(bobyqa)最小化成本函数以确定旋转及平移的最佳参数。本文中应注意,可使用任何非线性优化程序。因此,不应将上文描述解释为限制本公开的范围。

[0092]

在步骤1008中,产生指示经调整掩模坯料对于特定设计图案的良好程度的一或多个度量。例如,系统100的控制器108可经配置以使用本文中先前描述的eqn.3到4产生指示掩模坯料对于设计图案的良好程度的一或多个度量。在一个实施例中,一或多个度量包含在0到1之间的分数。例如,系统100的控制器108可经配置以使用eqn.3到4确定在0到1之间的分数。更接近1的分数指示具有设计图案的经调整掩模坯料更可能缓解掩模坯料上的一或多个缺陷。例如,分数1指示具有设计图案的经调整掩模坯料缓解掩模坯料上的一或多个缺陷,而分数0指示具有设计图案的经调整掩模坯料未良好地缓解掩模坯料上的一或多个缺陷。在此方面,分数给予用户坯料对于掩模图案p的良好程度及图案掩模将如何有效地隐藏坯料中的一或多个缺陷的直观指示。

[0093]

在步骤1010中,基于步骤1006中确定的成本函数的最小值的经估计参数或在步骤1008中确定的指示经调整掩模坯料对于特定图案的良好程度的一或多个度量产生用以调

整掩模坯料的旋转及平移的一或多个控制信号。例如,可使用在步骤1008中确定的一或多个度量选择来自掩模坯料库的最佳掩模坯料,使得基于指定图案最佳利用全部掩模坯料。例如,系统100的控制器108可经配置以在优化之后(例如,一旦已将掩模坯料旋转90度并在x方向上平移-1.1268μm且在y方向上平移0.1956μm)在具有特定掩模图案的掩模坯料当中获得0.9355的最高分数。在此例子中,最高分数指示在已将掩模坯料旋转90度且在x方向上平移-1.1268μm且在y方向上平移0.1956μm之后,掩模坯料是设计图案的最佳对。因此,其可最大地减少坯料浪费且大大地改进制造环境中的良率。

[0094]

在步骤1012中,使用经调整掩模坯料产生掩模以执行样本的光刻。例如,所产生的掩模可为待由euv光刻子系统(例如在图1b到1c中展示的光刻子系统102)使用的euv光掩模。

[0095]

本文中描述的全部方法可包含将方法实施例的一或多个步骤的结果存储于存储器中。结果可包含本文中描述的任何结果且可依所属领域中已知的任何方式存储。存储器可包含本文中描述的任何存储器或所属领域中已知的任何其它适合存储媒体。在已存储结果之后,结果可在存储器中存取且通过本文中描述的任何方法或系统实施例使用、经格式化以显示给用户、通过另一软件模块、方法或系统使用及类似情况。此外,结果可“永久地”、“半永久地”、“暂时地”存储或存储达某一时段。例如,存储器可为随机存取存储器(ram),且结果可能不一定无限期地保存于存储器中。

[0096]

进一步经考虑,上文描述的方法的实施例中的每一者可包含本文中描述的(若干)任何其它方法的(若干)任何其它步骤。另外,上文描述的方法的实施例中的每一者可通过本文中描述的任何系统执行。

[0097]

所属领域的技术人员将认识到,本文中所描述的组件、操作、装置、对象及其随附论述为了概念清楚起见而用作实例且考虑各种配置修改。因此,如本文中所使用,所陈述的特定实例及随附论述希望表示其更一般类别。通常,使用任何特定实例希望表示其类别,且不包含特定组件、操作、装置及对象不应被视为限制性。

[0098]

如本文中所使用,方向性术语(例如“顶部”、“底部”、“上方”、“下方”、“上”、“向上”、“下面”、“下”及“向下”)希望出于描述目的而提供相对位置,且并非希望指定绝对参考系。所描述实施例的各种修改对于所属领域的技术人员将是显而易见的,且本文中所定义的一般原理可应用于其它实施例。

[0099]

关于本文中的基本上任何复数及/或单数术语的使用,所属领域的技术人员可根据上下文及/或应用从复数转换为单数及/或从单数转换为复数。为了清楚起见,本文未明确陈述各种单数/复数排列。

[0100]

本文中所描述的标的物有时说明其它组件内所含或与其它组件连接的不同组件。应理解,如此描绘的架构仅仅是实例性的,且实际上可实施实现相同功能的诸多其它架构。在概念意义上,实现相同功能的组件的任何布置有效地“相关联”,使得实现所期望功能。因此,本文中经组合以实现特定功能的任何两个组件可被视为彼此“相关联”,使得实现所期望功能,而与架构或中间组件无关。同样地,如此相关联的任何两个组件还可被视为彼此“连接”或“耦合”以实现所期望功能,且能够如此相关联的任何两个组件还可被视为“可耦合”到彼此以实现所期望功能。可耦合的特定实例包含(但不限于)物理上可配合及/或物理上互动的组件及/或无线可互动及/或无线互动的组件及/或逻辑上互动及/或逻辑上可互

动的组件。

[0101]

此外,应理解,本发明是由随附权利要求书定义。所属领域的技术人员将理解,通常,本文中及尤其随附权利要求书(例如,随附权利要求书的主体)中所使用的术语通常希望作为“开放”术语(例如,术语“包含(including)”应被解释为“包含(但不限于)”,术语“具有”应被解释为“至少具有”,术语“包含(includes)”应被解释为“包含(但不限于)”及类似者)。所属领域的技术人员将进一步理解,如果希望特定数目个所介绍权利要求叙述,那么将在权利要求书中明确叙述此意图,且在缺失此叙述的情况下不存在此意图。例如,为了辅助理解,下文随附权利要求书可含有介绍性词组“至少一个”及“一或多个”的使用以介绍权利要求叙述。然而,此类词组的使用不应被解释为暗示由不定冠词“一”或“一个”介绍权利要求叙述将任何特定权利要求含有此所介绍权利要求叙述限于本发明仅含有一个此叙述,即使在同一权利要求包含介绍性词组“一或多个”或“至少一个”及不定冠词(例如“一”或“一个”(例如,“一”及/或“一个”通常应被解释为意味着“至少一个”或“一或多个”)时也如此;用来介绍权利要求叙述的定冠词的使用也是如此。另外,即使明确叙述特定数目个所介绍权利要求叙述,所属领域的技术人员仍将认识到,此叙述通常应被解释为意味着着至少所叙述数目(例如,“两个叙述”的纯粹叙述而没有其它修饰词通常意味着至少两个叙述,或两个或更多个叙述)。此外,在其中使用类似于“a、b及c中的至少一者,及类似者”的惯例的那些例子中,通常此构造希望具有所属领域的技术人员将理解所述惯例的意义(例如,“具有a、b及c中的至少一者的系统”将包含(但不限于)仅具有a,仅具有b,仅具有c,一起具有a及b,一起具有a及c,一起具有b及c及/或一起具有a、b及c,及类似者的系统)。在其中使用类似于“a、b或c中的至少一者,及类似者”的惯例的那些例子中,通常此构造希望具有所属领域的技术人员将理解所述惯例的意义(例如,“具有a、b或c中的至少一者的系统”将包含(但不限于)仅具有a,仅具有b,仅具有c,一起具有a及b,一起具有a及c,一起具有b及c及/或一起具有a、b及c,及类似者的系统)。所属领域的技术人员将进一步理解,实际上无论在描述、权利要求书或图式中,呈现两个或更多个替代术语的任何转折词及/或词组应被理解为考虑包含所述术语中的一者、所述术语的任一者或两个术语的可能性。例如,词组“a或b”将被理解为包含“a”或“b”或包含“a及b”的可能性。

[0102]

据信本公开及许多其伴随优点将通过前文描述来理解,且将显而易见的是,在不脱离所公开标的物的情况下或在不牺牲其全部重要优点的情况下,可对组件的形式、构造及布置进行各种改变。所描述形式仅仅是解释性的,且下文权利要求书希望涵盖及包含此类改变。此外,应理解,本发明是由随附权利要求书定义。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。