一种基于融合逻辑的具有多层优先级的静态rs触发器

技术领域

1.本发明提出一种基于融合逻辑的具有多层优先级的静态rs触发器,在常规的置位、复位基础上创新的增加一组高优先级的置位、复位功能和低优先级使能功能,有助于处理复杂异步时序之间的优先级问题,大幅提高可靠性,借助融合逻辑,又具有很高的器件使用效。

背景技术:

2.数字电路作为集成电路的基石,一直备受重视,得到了长足的发展。数字电路以其逻辑的严密性、可靠性使得高可靠的逻辑运算成为可能,极大的扩展了人类意识的边界,先进的逻辑运算单元已经成为开启ai时代的钥匙。数字集成电路设计具有一系列标准单元和工具,更有fpga、cpld等可编程逻辑器件,基于这些资源设计的数字系统具有良好的稳健性,能实现各种复杂且精妙的运算,且能在制程的进步中获得巨大收益。任何完美的事物总包含一些缺点,作为半导体产业的宠儿的数字集成电路也不例外,标准的数字设计流程对诸如,电源、数据转换器等数模混合系统显得力不从心。这些系统可能没有时钟,需要通过延迟或者状态触发自定时逻辑事件,产生异步时钟,并在异步时钟的各个阶段完成不同的工作的调度,异步时序系统有不同于时序逻辑的一系列可靠性问题。

3.这类电路往往需要定制人工数字逻辑来实现,标准工具的缺乏,需花费大量的时间和精力考究其功能性与可靠性问题,更高的要求还涉及逻辑器件的使用效率和结构的强壮性。定制数字电路设计会使用到大量存储器,其中rs触发只需8个开关器件就可实现,以其功能明确、结构简单的优点倍受青睐,但rs触发器作为电平触发存储单元,置位、复位功能同时用于自定时逻辑会有亚稳态和复位风险。更加复杂的功能还需要配合一定的基本逻辑单元才可实现,比如jk触发器,往往逻辑效率并不高,占用大量版图面积。

技术实现要素:

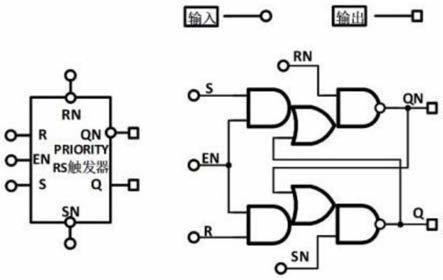

4.本发明为一种基于融合逻辑的具有多层优先级的静态rs触发器,采用两个三级融合静态逻辑门高效的实现目标逻辑功能。本发明的静态rs触发器的引脚框图如图1左,除了标准的输出端(q、qn),一组低优先级置位、复位端(s、r)外,还包含一组高优先级置位、复位输入端(sn、rn)和一个中优先级的低优先级置位、复位的使能端(en)。

5.本发明的逻辑结构分为三个层次,三个层次分别对应不同功能的优先级,逻辑框图如图1右所示。第一个层次是普通置位、复位功能,为高电平有效,低电平无动作,对应图中的s、r引脚;第二个层次是输入使能,优先级高于普通置位、复位功能,为高电平有效,低电平屏蔽普通的置位和复位功能,对应图中的en引脚;第三个层次是高优先级置位、复位功能,在正反馈内部直接修改输出,优先级最高,高于普通置位、复位和使能端,低电平有效,高电平无效,对应图中的sn、rn引脚。

6.逻辑信号的动作波形如图3所示,其中电平波动表示信号电平在该区间一直变化,用来表征信号优先级,梯形的底表示默认无效电平极性,梯形的顶表示有效电平极性。信号

的优先级在图中一目了然,但不包含亚稳态特征,原则上任意一对置位、复位受限正反馈竞争,不可同时无效,但本发明有两套不同优先级的置位、复位功能,可以很大程度避免亚稳态和复位问题。

7.本发明的电路结构使用两个三级融合静态逻辑门,这种门逻辑实际上是单级静态门逻辑,只有一次非逻辑,却可实现多级正逻辑功能,且功耗与延迟接近单级门逻辑,同时具有很高的器件效率。每个三级融合静态逻辑门的逻辑功能由一个与门、或门、与非门的级联构成,如图1右所示,第一级与门连接中低优先级逻辑,第二级连接正反馈逻辑,第三级连接高优先级逻辑输入。这种方式实现了与非门与或非门的转换,低优先级逻辑通过或非门传递,高优先级逻辑动作通过一个与非门传递,借助与非与或非正反馈交织出现的逻辑锁定实现高优先级。

8.本发明的开关级实现如图2所示,由mp1-mp4(pmos)、mn1-mn4(nmos)共8 个开关器件构成三级融合静态逻辑门,对应六个逻辑输入端,每逻辑运算只消耗不到3个器件。图中画圈的mos管与低优先级置位、复位的使能相关,如果不需要可以删除,实线圈的器件源漏短路(mn3),虚线圈的器件源漏断路(mp1)。当然高优先级的置位功能和复位功能也可选择屏蔽,mp4断路,mn4短路可删除高优先级复位功能,高优先级置位功能同理。本发明的传统逻辑实现需要32开关器件,本发明的融合逻辑共只消耗16个开关器件,还缩短门级串联,获得更优的速度性能。应用中并不是所有功能都是必须的,删除单侧使能功能可节省2个开关器件,任意一个置位复位功能删除也可节省2个开关器件。本发明只需十个开关器件就可获得一个具有强制复位或置位的rs触发器,在双延迟线异步时钟电路中具有重大应用价值,多出的高优先级控制端可在任意时刻可靠复位系统,无需关注低优先级端口的输入状态。

9.本发明创新的多层次优先级结构,具有极强的可靠性与可控性,融合逻辑构架实现控制信号的分层管理,打破了传统逻辑短平的控制过程,通过与非门与或非门的转换将各优先级的信号融合在一起。

附图说明

10.图1为本发明的引脚框图与逻辑门级结构图。

11.图2为本发明管级结构图。

12.图3为本发明时序图。

具体实施方式

13.在本发明为一种基于融合逻辑的具有多层优先级的静态rs触发器,具体实施可通过任意可控开关单元组合构成,具体的开关单元可为继电器、晶体管,机械阀门等,实际上逻辑功能的实现多使用体积小、功耗低的晶体管,这完全得益于半导体技术的发展。

14.本发明的逻辑结构包含4个与、2个或、2个非静态逻辑运算功能单元,所有单元的输入端口共有12个,每个静态逻辑输入信号端对应一组交替导通的开关,开关以逻辑对偶分布于上拉逻辑开关单元和下拉逻辑开关单元。本发明整体结构采用两个三级融合静态逻辑门,融合后的逻辑门的连线如图1右所示,电路共有5个输入端,2个输出端。五个输入端包含一组低优先级置位、复位功能,一个中优先级使能,一组高优先级置位、复位功能,两个输出端为一组常规存储器都有的反相端口。

15.本发明的设计通过标准28nm工艺仿真验证,采用标准阈值的互补mos管制作电路,具体器件摆放如图2所示,共消耗8个pmos和8个nmos。通过瞬态仿真枚举各种逻辑组合分析其逻辑功能,逻辑功能波形的简化图如图3所示,图中可以清晰看到的中优先级的使能和高优先级的置位、复位。

技术特征:

1.一种基于融合逻辑的具有多层优先级的静态rs触发器,其特征在于与非门、或非门逻辑转换的翻转和锁定特性,实现不同优先级的置位、复位控制,将不同层次的信号直接联系起来;同时采用逻辑融合结构,实现了逻辑功能的集成,极大的提升了开关逻辑器件的利用率,缩短的门级结构,也极大的降低了延迟特性。2.根据权利要求1所描述的一种基于融合逻辑的具有多层优先级的静态rs触发器,其与非门、或非门逻辑转换的翻转和锁定特性是设计的核心,也是高优先级功能实现的基础;低优先级工作路径通过两个或非门正反馈,和传统rs触发器没有差异,高优先级工作路径转换一个或非门为与非门与另外一个或非门正反馈耦合,实现对输出状态的强制控制,让高优先级的置位、复位成为可能。3.根据权利要求1所描述的一种基于融合逻辑的具有多层优先级的静态rs触发器,不同优先级置位、复位控制端口,在全功能结构中包含一组低优先级置位、复位端口,一个中优先级的低优先级端口使能端口,还有一组重要的高优先级置位、复位端口;低优先级置位、复位功能具有正常置位、复位功能,低优先级使能端口可以禁用低优先级置位、复位功能;高优先级置位与复位端口可以覆盖低优先级置位、复位端口及其使能端口的功能,强制实现置位与复位功能;非全功能结构以保留一个高优先级置位或复位端口为核心,可以减少不同优先级的置位、复位、使能端口。4.根据权利要求1所描述的一种基于融合逻辑的具有多层优先级的静态rs触发器,其中的逻辑实现采用两个三级融合静态逻辑门,实现了逻辑功能的集成,将传统逻辑实现的32个开关降低一倍,单侧逻辑融合成一级,大大的降低了中低优先级功能端口的逻辑延迟,提升了工作速度。

技术总结

数字电路作为集成电路的基石,以其逻辑的严密性、可靠性成就了高可靠的逻辑运算,极大的扩展了人类意识的边界,先进的逻辑运算单元已经成为开启AI时代的钥匙。数字系统具有良好的稳健性,能实现各种复杂且精妙的运算,可是,标准的数字设计流程对诸如,电源、数据转换器等数模混合系统显得力不从心。这些系统可能没有时钟,需要通过延迟或者状态触发自定时逻辑事件,产生异步时钟,并在异步时钟的各个阶段完成不同的工作的调度,异步时序系统有不同于时序逻辑的一系列可靠性问题。本发明提出一种基于融合逻辑的具有多层优先级的静态RS触发器,在常规的置位、复位基础上创新的增加一组高优先级的置位、复位功能和低优先级使能功能,有助于处理复杂时序之间的优先级问题,大幅提高可靠性,借助融合逻辑,又具有很高的器件使用效率。件使用效率。件使用效率。

技术研发人员:李强 杨光亮 王银浩

受保护的技术使用者:电子科技大学

技术研发日:2022.02.28

技术公布日:2022/5/31

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。