1.本发明涉及振动器件等。

背景技术:

2.以往,作为使用振动元件的器件,公知有振荡器等振动器件。例如,专利文献1公开了一种温度补偿型的振荡器,该振荡器在截面为h型的封装的第1凹部中收纳振动元件,在第2凹部中收纳具有温度传感器电路、温度补偿电路、振荡电路和放大电路的ic(integrated circuit)芯片。

3.专利文献1:日本特开2010-206443号公报

4.输出基于振荡电路的振荡信号的时钟信号的输出缓冲电路与其他电路块相比,消耗电力大,容易发热。而且,在上述专利文献1中,放大电路即输出缓冲电路和温度传感器电路形成于同一ic芯片,因此,温度传感器电路容易受到输出缓冲电路中的发热的影响。另一方面,在专利文献1中,输出缓冲电路和振动元件经由收纳ic芯片和振动元件的封装的内部布线等连接。因此,在输出缓冲电路与振动元件之间,相比于输出缓冲电路与温度传感器电路之间,不容易传递热。因此,在使用专利文献1这种构造来构成温度补偿型的振荡器时,由于输出缓冲电路的发热的影响,在温度传感器电路的检测温度与振动元件的实际温度之间产生误差。

技术实现要素:

5.本发明的一个方式涉及一种振动器件,所述振动器件包含:基座,其包含具有第1面和与所述第1面处于正反关系的第2面的半导体基板、以及贯通所述第1面与所述第2面之间的贯通电极;以及振动元件,其隔着导电性的接合部件固定于所述第1面,在所述第2面配置有:振荡电路,其经由所述贯通电极与所述振动元件电连接,使所述振动元件振荡而生成振荡信号;温度传感器电路;温度补偿电路,其根据所述温度传感器电路的输出进行所述振荡信号的温度补偿;以及输出缓冲电路,其输出基于温度补偿后的所述振荡信号的时钟信号,在设所述输出缓冲电路与所述贯通电极的距离为dbx1、设所述温度传感器电路与所述贯通电极的距离为dsx1时,dsx1《dbx1。

附图说明

6.图1是示出本实施方式的振动器件的结构例的剖视图。

7.图2是示出本实施方式的振动器件的具体结构例的剖视图。

8.图3是示出振动器件的振动元件的一例的俯视图。

9.图4是示出集成电路的结构例的图。

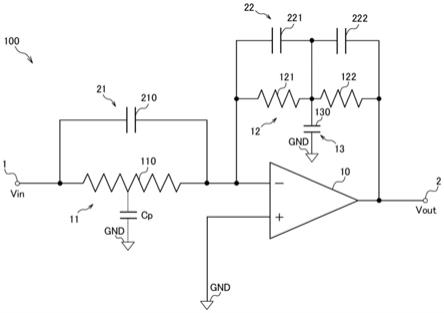

10.图5是示出振荡电路的结构例的图。

11.图6是示出输出缓冲电路的结构例的图。

12.图7是示出振动器件的制造方法的一例的制造工序图。

13.图8是示出输出缓冲电路、温度传感器电路、贯通电极的配置关系的俯视图。

14.图9是示出外部连接端子的配置例的俯视图。

15.图10是示出输出缓冲电路、温度传感器电路、贯通电极的配置关系的俯视图。

16.图11是示出贯通电极与集成电路的各电路的配置关系的俯视图。

17.图12是示出贯通电极与集成电路的各电路的配置关系的另一例的俯视图。

18.图13是示出贯通电极的另一例的剖视图。

19.图14是示出输出缓冲电路的输出驱动器的另一个结构例的图。

20.图15是示出输出缓冲电路的输出驱动器的另一个结构例的图。

21.图16是示出外部连接端子的另一个配置例的俯视图。

22.标号说明

23.1:振动器件;2:基座;5:振动元件;7:盖;8:再配置布线层;10:集成电路;11:振荡电路;12:输出缓冲电路;13:逻辑电路;14:电源电路;15:温度补偿电路;16:温度传感器电路;17:存储器;20:半导体基板;21:第1面;22:第2面;23、24:晶体管;25:元件分离膜;30:布线层;31、32:金属层;33、34、35:绝缘层;36、37、38、39:接触盘;40、41:贯通电极;44:绝缘层;45:树脂层;50:振动基板;52、53:激励电极;54、55:布线;56、57:端子;60、61:接合部件;62:凸块;64:端子;68、69:接触盘;71、72:接合部件;80:绝缘层;82:布线;91、91a、91b、92、93、94、95:外部连接端子;101:第1金属层;102:第2金属层;ck、ckx:时钟信号;cl:中心线;cv1、cv2:可变电容电路;dv1、dv2:反相器电路;iv1、iv2、iv3:反相器电路;la、lb:布线;na:nand电路;oe:输出使能信号;osc:振荡信号;sd1、sd2、sd3、sd4:边;sp:收纳空间;tck、tgnd、toe、tvc、tvdd、txa、txb:端子;vl:假想线;dbx1、dbx2、dsx1、dsx2、dsx:距离。

具体实施方式

24.下面,对本实施方式进行说明。另外,以下说明的本实施方式并非不当地限定权利要求书的记载内容。此外,本实施方式中说明的全部结构不一定是必须结构要件。此外,在以下的各图中,为了便于说明,有时省略一部分结构要素。此外,在各图中,为了容易理解,各结构要素的尺寸比率与实际不同。

25.1.振动器件

26.图1是示出本实施方式的振动器件1的结构例的剖视图。如图1所示,本实施方式的振动器件1包含基座2、振动元件5。此外,振动器件1能够包含盖7、再配置布线层8、外部连接端子91、92。基座2包含半导体基板20和贯通电极40。半导体基板20具有第1面21和与第1面21处于正反关系的第2面22。第1面21是半导体基板20的例如上表面,第2面22是半导体基板20的例如下表面。贯通电极40是贯通半导体基板20的第1面21和第2面22的电极。振动元件5配置于半导体基板20的第1面21侧。例如,振动元件5配置于与半导体基板20的第1面21分开给定的分离距离的位置。具体而言,振动元件5例如隔着导电性的接合部件60固定于半导体基板20的第1面21。外部连接端子91、92隔着绝缘层80等设置于半导体基板20的第2面22侧。绝缘层80例如是构成再配置布线层8的绝缘层。

27.另外,在本实施方式中说明的各图中,作为彼此正交的3个轴,图示了x轴、y轴和z轴。将沿着x轴的方向称为“x轴方向”,将沿着y轴的方向称为“y轴方向”,将沿着z轴的方向称为“z轴方向”。此外,将各轴方向的箭头末端侧称为“正侧”,将基端侧称为“负侧”,将z轴

方向正侧称为“上”,将z轴方向负侧称为“下”。例如,z轴方向沿着铅垂方向,xy平面沿着水平面。图1是从y轴方向剖视观察时的振动器件1的剖视图。此外,半导体基板20的第1面21和第2面22是沿着xy平面的面,是与z轴正交的面。另外,“正交”除了包含以90

°

相交的情况以外,还包含以相对于90

°

稍微倾斜的角度相交的情况。

28.振动器件1例如是振荡器。具体而言,振动器件1是温度补偿石英振荡器(tcxo)、带恒温槽的石英振荡器(ocxo)、压控石英振荡器(vcxo)、saw(surface acoustic wave)振荡器、压控型saw振荡器、mems(micro electro mechanical systems)振荡器等振荡器。mems振荡器能够通过在硅基板等基板配置压电膜和电极而成的mems的振动元件实现。但是,振动器件1也可以是加速度传感器、角速度传感器这样的惯性传感器、倾斜传感器这样的力传感器等。

29.基座2由半导体基板20构成。半导体基板20例如是硅基板。但是,半导体基板20不限于硅基板,也可以是ge、gap、gaas、inp等半导体基板。

30.此外,基座2包含集成电路10。半导体电路即集成电路10形成于半导体基板20的第2面22。集成电路10由多个电路元件构成。电路元件例如是晶体管等有源元件、或者电容器或电阻等无源元件。具体而言,集成电路10由各电路块包含多个电路元件的多个电路块构成。此外,集成电路10由对半导体基板20掺杂杂质而形成的杂质区域即扩散区域、以及层叠金属层和绝缘层而成的布线层形成。通过扩散区域形成集成电路10的电路元件即晶体管的源极区域和漏极区域,通过布线区域形成连接电路元件之间的布线。

31.此外,基座2包含贯通电极40。贯通电极40由贯通半导体基板20的第1面21和第2面22的导电性材料构成。例如,针对半导体基板20形成贯通孔,利用导电性材料填埋该贯通孔,由此,形成贯通电极40。导电性材料可以是铜等金属,也可以是导电性的多晶硅等。导电性的多晶硅例如是掺杂磷(p)、硼(b)、砷(as)等杂质而赋予了导电性的多晶硅。在使用多晶硅作为导电性材料时,能够实现对于在集成电路10的形成工序中施加的热具有足够耐性的贯通电极40。

32.贯通电极40的一端经由导电性的接合部件60与振动元件5电连接。在图1中,导电性的接合部件60通过一端与振动元件5电连接、另一端与贯通电极40电连接的凸块62等实现。具体而言,凸块62的另一端经由端子64与贯通电极40连接。凸块62是导电性的凸块,具体而言是金属凸块。另外,也可以通过导电性的粘接材料等实现导电性的接合部件60。

33.贯通电极40的另一端与集成电路10电连接。具体而言,贯通电极40的另一端经由形成于集成电路10的接触盘36与集成电路10的电路元件连接。由此,能够经由贯通电极40使振动元件5和集成电路10电连接。

34.盖7隔着接合部件71、72与基座2接合。而且,通过基座2和盖体即盖7形成具有气密性的收纳空间sp,振动元件5收纳于该收纳空间sp内。收纳空间sp被气密密封,收纳空间sp内例如处于减压状态。由此,能够稳定地驱动振动元件5。另外,收纳空间sp内的状态不限于减压状态,例如,收纳空间sp内也可以是惰性气体环境。

35.再配置布线层8设置于半导体基板20的第2面22侧,包含绝缘层80和再配置布线用的布线82。绝缘层80例如通过聚酰亚胺等树脂层实现,布线82例如通过铜箔等金属布线实现。绝缘层80需要具有耐受振动器件1的安装时的焊接的耐热性,优选使用聚酰亚胺。此外,关于布线82的材料,除了铜以外,也可以使用银等金属材料。此外,再配置布线层8中的布线

层、端子的厚度例如是50μm左右。通过设置再配置布线层8,能够使形成于集成电路10的接触盘38、39和外部连接端子91、92电连接。而且,通过进行将振动器件1的外部连接端子91、92与安装振动器件1的电路基板等的端子或布线连接的安装,能够将振动器件1嵌入电子设备中。此外,通过设置这种再配置布线层8,能够进行集成电路10的部分的机械保护,能够保护集成电路10等不受振动器件1的安装时的焊接工序中的热的影响。

36.图2是示出振动器件1的具体结构例的剖视图,图3是示出振动器件1的振动元件5的一例的俯视图。首先,使用图3对振动元件5的详细情况进行说明。

37.振动元件5是通过电信号产生机械振动的元件。例如,如图3所示,振动元件5具有振动基板50和配置于振动基板50的表面的电极。振动基板50具有厚度剪切振动模式,在本实施方式中,由at切石英基板形成。at切石英基板具有三次的频率温度特性,因此,成为具有优异温度特性的振动元件5。此外,电极具有配置于振动基板50的上表面的激励电极52、以及与激励电极52对置地配置于下表面的激励电极53。上表面是z轴方向正侧的面,下表面是z轴方向负侧的面。此外,激励电极52、53中的一方是第1激励电极,激励电极52、53中的另一方是第2激励电极。此外,电极具有配置于振动基板50的下表面的一对端子56、57、使端子56和激励电极52电连接的布线54、以及使端子57和激励电极53电连接的布线55。

38.另外,振动元件5的结构不限于上述结构。例如,振动元件5可以是被激励电极52、53夹着的振动区域从其周围突出的台面型,相反,也可以是振动区域从其周围凹陷的倒台面型。此外,也可以实施对振动基板50的周围进行磨削的斜面加工、使上表面和下表面成为凸曲面的凸面加工。此外,振动元件5不限于以厚度剪切振动模式进行振动。例如,振动元件5也可以是多个振动臂在面内方向进行弯曲振动的音叉型振动元件、多个振动臂在面外方向进行弯曲振动的音叉型振动元件、具有进行驱动振动的驱动臂和进行检测振动的检测臂且检测角速度的陀螺仪传感器元件、或者具有检测加速度的检测部的加速度传感器元件。此外,振动基板50不限于由at切石英基板形成,也可以由at切石英基板以外的石英基板例如x切石英基板、y切石英基板、z切石英基板、bt切石英基板、sc切石英基板、st切石英基板等形成。此外,在本实施方式中,振动基板50由石英构成,但不限于此,例如,也可以由铌酸锂、钽酸锂、四硼酸锂、铌酸钾、磷酸镓等压电单晶体构成,还可以由它们以外的压电单晶体构成。此外,振动元件5不限于压电驱动型的振动元件,也可以是使用静电力的静电驱动型的振动元件。

39.而且,如图2、图3所示,振动元件5经由导电性的接合部件60、61固定于半导体基板20的上表面即第1面21。另外,虽然在图2中没有图示,但是,如图3所示,例如沿着y轴方向设置有2个接合部件60、61。此外,如后述的图8所示,在半导体基板20例如沿着y轴方向设置有2个贯通电极40、41,这些贯通电极40、41经由导电性的接合部件60、61与振动元件5电连接。贯通电极40、41中的一方是第1贯通电极,贯通电极40、41中的另一方是第2贯通电极。具体而言,贯通电极40的一端经由接合部件60、振动元件5的端子56以及布线54与振动元件5的激励电极52电连接。此外,贯通电极41的一端经由接合部件61、振动元件5的端子57以及布线55与振动元件5的激励电极53电连接。而且,贯通电极40、41的另一端与集成电路10电连接。由此,振动元件5和集成电路10经由贯通电极40、41电连接。具体而言,贯通电极40、41的另一端经由图2、图8所示的接触盘36、37与集成电路10的振荡电路11电连接。由此,振动元件5和振荡电路11经由贯通电极40、41电连接。

40.接合部件60、61只要兼具导电性和接合性,则没有特别限定,例如能够通过金凸块、银凸块、铜凸块、焊料凸块、树脂芯凸块等各种导电性的凸块62实现。或者,接合部件60、61也可以使用使银填料等导电性填料分散于聚酰亚胺系、环氧系、硅酮系、丙烯酸系的各种粘接剂中而成的导电性粘接剂等。如果使用导电性的凸块62作为接合部件60、61,则能够抑制从接合部件60、61产生气体,能够有效地抑制收纳空间sp的环境变化、特别是压力的上升。另一方面,如果使用导电性粘接剂作为接合部件60、61,则与接合部件60、61是导电性的凸块62的情况相比,具有更柔软、应力不容易传递到振动元件5的优点。

41.此外,半导体基板20在形成有贯通孔后被热氧化,由此,在半导体基板20的第1面21或贯通孔的内表面形成例如由氧化硅(sio2)构成的绝缘膜即绝缘层44。通过热氧化而形成绝缘层44,由此,能够在半导体基板20的表面形成致密且均质的绝缘层44。此外,还能够减小绝缘层44与半导体基板20的线膨胀系数差。因此,能够实现不容易产生热应力、具有优异振荡特性的振动器件1。绝缘层44的构成材料没有特别限定,例如可以由氮化硅(sin)构成,也可以由树脂构成。此外,作为绝缘层44的形成方法,不限于热氧化,例如也可以通过cvd(chemical vapor deposition)形成。

42.而且,在贯通孔的绝缘层44的内侧填充铜或导电性多晶硅等导电性材料,由此形成贯通电极40、41。即,利用导电性材料在贯通孔内进行填埋,由此形成贯通电极40、41。而且,贯通电极40、41的一端与振动元件5电连接。具体而言,贯通电极40、41的一端与振动元件5的激励电极52、53电连接。另一方面,贯通电极40、41的另一端与集成电路10电连接。具体而言,贯通电极40、41的另一端经由接触盘36、37与集成电路10的振荡电路11电连接。

43.如图2所示,集成电路10例如由n型的晶体管23或p型的晶体管24构成。这些晶体管23、24由形成于半导体基板20的扩散区域即源极区域和漏极区域、栅极电极、以及栅极氧化膜构成。此外,晶体管23、24通过被称为locos(local oxidation of silicon)的元件分离膜25进行元件分离。此外,集成电路10包含实现晶体管23、24等多个电路元件之间的连接布线的布线层30。例如,图2的布线层30包含金属层31、32、绝缘层33、34、35。金属层31、32分别是第1金属层、第2金属层,绝缘层33、34、35分别是第1绝缘层、第2绝缘层、第3绝缘层。金属层31形成于绝缘层33与绝缘层34之间,金属层32形成于绝缘层34与绝缘层35之间。这些金属层31、32例如通过铝等金属实现。此外,通过最上层的绝缘层35形成钝化膜。此外,金属层31和金属层32通过被称为通路接触的接触而电连接,金属层31和晶体管23、24的源极区域或漏极区域通过接触而电连接。而且,如图2所示,与贯通电极40、41的另一端电连接的接触盘36由下层的金属层31形成。此外,与外部连接端子91、92电连接的接触盘38、39由上层的金属层32形成。另外,在布线层30中,将集成电路10中接近晶体管23、24的一侧的层设为下层,将远离晶体管23、24的一侧的层设为上层。此外,在图2中,示出布线层30具有2层的金属层31、32的情况,但本实施方式不限于此,布线层30也可以具有3层以上的金属层。该情况下,通过多个金属层中的最下层的金属层形成接触盘36、37,通过最上层的金属层形成接触盘38、39。此外,通过最上层的绝缘层形成钝化膜。

44.此外,再配置布线层8包含通过聚酰亚胺等树脂层实现的绝缘层80、以及通过铜箔等实现的布线82。而且,接触盘38与外部连接端子91电连接,接触盘39经由布线82与外部连接端子92电连接。

45.此外,在图2中,外部连接端子91、92分别成为具有第1金属层101和第2金属层102

的双层构造。作为聚酰亚胺的绝缘层80侧的第1金属层101,例如使用钛钨层以提高与聚酰亚胺之间的密接性。作为第2金属层102,例如使用容易与外部的端子或布线进行焊接等的铜或金等的金属层。

46.图4示出集成电路10的结构例。集成电路10包含振荡电路11、输出缓冲电路12、温度补偿电路15和温度传感器电路16。此外,集成电路10能够包含逻辑电路13、电源电路14、存储器17。

47.振荡电路11是使振动元件5振荡的电路。例如,振荡电路11与端子txa、txb电连接,生成振荡信号osc。具体而言,振荡电路11经由布线la、lb、端子txa、txb与振动元件5电连接,使振动元件5振荡,由此,生成振荡信号osc。端子txa、txb中的一方是第1端子,端子txa、txb中的另一方是第2端子。例如,振荡电路11能够通过设置于端子txa与端子txb之间的振荡用的驱动电路、电容器或电阻等无源元件实现。驱动电路例如能够通过cmos的反相器电路或双极晶体管实现。驱动电路是振荡电路11的核心电路,驱动电路对振动元件5进行电压驱动或电流驱动,由此,使振动元件5振荡。作为振荡电路11,例如能够使用inverter型、皮尔斯型、考毕兹型或哈特莱型等各种类型的振荡电路。此外,在振荡电路11中设置有可变电容电路,通过调整该可变电容电路的电容,能够调整振荡频率。可变电容电路例如能够通过变容二极管等可变电容元件实现。或者,也可以通过电容器阵列以及与电容器阵列连接的开关阵列实现可变电容电路。例如,也可以通过电容器阵列和开关阵列构成可变电容电路,该电容器阵列具有以二进制方式对电容值进行加权的多个电容器,该开关阵列具有多个开关,各开关进行电容器阵列的各电容器与端子txa或txb之间的连接的接通、断开。另外,本实施方式中的连接是电连接。电连接是以能够传递电信号的方式连接,是能够利用电信号传递信息的连接。电连接也可以是经由有源元件等的连接。

48.输出缓冲电路12输出基于振荡信号osc的时钟信号ck。例如,输出缓冲电路12对振荡信号osc进行缓冲,作为时钟信号ck输出到端子tck。然后,该时钟信号ck经由振动器件1的外部连接端子91输出到外部。例如,输出缓冲电路12以单端的cmos的信号形式输出时钟信号ck。例如,在来自端子toe的输出使能信号oe有效的情况下,来自逻辑电路13的使能信号成为有效,输出缓冲电路12输出对振荡信号osc进行缓冲后的时钟信号ck。另一方面,在输出使能信号oe无效的情况下,输出缓冲电路12将时钟信号ck设定为例如低电平等固定电压电平。由此,端子tck的电压电平被设定为固定电压电平。另外,信号有效是指,例如在正逻辑的情况下是高电平,在负逻辑的情况下是低电平。此外,信号无效是指,例如在正逻辑的情况下是低电平,在负逻辑的情况下是高电平。另外,输出缓冲电路12也可以以cmos以外的信号形式输出时钟信号ck。

49.逻辑电路13是控制电路,进行各种控制处理。例如,逻辑电路13进行集成电路10的整体的控制,或进行集成电路10的动作顺序的控制。此外,逻辑电路13也可以进行振荡电路11的控制用的各种处理,或进行电源电路14的控制。逻辑电路13例如能够通过门阵列等基于自动配置布线的asic(application specific integrated circuit)电路实现。

50.电源电路14从端子tvdd被供给电源电压vdd,从端子tgnd被供给接地电压即gnd。而且,电源电路14将集成电路10的各内部电路用的电源电压供给到各内部电路。电源电路14也可以生成集成电路10中使用的基准电压或基准电流等。例如,电源电路14具有调节器,将由调节器生成的调节电压供给到振荡电路11、输出缓冲电路12、逻辑电路13。该情况下,

电源电路14也可以具有生成向振荡电路11供给的调节电压的调节器、以及生成向输出缓冲电路12、逻辑电路13供给的调节电压的调节器。

51.温度补偿电路15进行振荡电路11的振荡信号osc的温度补偿。振荡信号osc的温度补偿是振荡电路11的振荡频率的温度补偿。而且,输出缓冲电路12输出基于温度补偿后的振荡信号osc的时钟信号ck。具体而言,温度补偿电路15根据来自温度传感器电路16的温度检测信息进行温度补偿。例如,温度补偿电路15根据来自温度传感器电路16的温度检测电压生成温度补偿电压,将生成的温度补偿电压输出到振荡电路11,由此,进行振荡电路11的振荡信号osc的温度补偿。例如,温度补偿电路15对振荡电路11具有的可变电容电路输出成为该可变电容电路的电容控制电压的温度补偿电压,由此,进行温度补偿。该情况下,振荡电路11的可变电容电路通过变容二极管等可变电容元件实现。温度补偿是抑制由于温度变动而引起的振荡频率的变动并进行补偿的处理。例如,温度补偿电路15进行基于多项式近似的模拟方式的温度补偿。例如,在对振动元件5的频率温度特性进行补偿的温度补偿电压通过多项式来近似的情况下,温度补偿电路15根据该多项式的系数信息进行模拟方式的温度补偿。模拟方式的温度补偿例如是通过模拟信号即电流信号、电压信号的相加处理等实现的温度补偿。具体而言,在存储器17中存储有温度补偿用的多项式的系数信息,逻辑电路13从存储器17读出该系数信息,例如设定在温度补偿电路15的寄存器中。然后,温度补偿电路15根据寄存器中设定的系数信息进行模拟方式的温度补偿。

52.另外,温度补偿电路15也可以进行数字方式的温度补偿。该情况下,温度补偿电路15例如通过逻辑电路实现。具体而言,温度补偿电路15根据温度传感器电路16的温度检测信息即温度检测数据进行数字的温度补偿处理。例如,温度补偿电路15根据温度检测数据求出频率调整数据。然后,根据求出的频率调整数据对振荡电路11的可变电容电路的电容值进行调整,由此,实现振荡电路11的振荡频率的温度补偿处理。该情况下,振荡电路11的可变电容电路通过具有以二进制方式进行加权的多个电容器的电容器阵列以及开关阵列实现。此外,存储器17存储表示温度检测数据与频率调整数据的对应关系的查找表,温度补偿电路15使用由逻辑电路13从存储器17读出的查找表,进行根据温度数据求出频率调整数据的温度补偿处理。

53.温度传感器电路16是检测温度的传感器电路。具体而言,温度传感器电路16输出根据环境的温度而变化的温度依赖电压作为温度检测电压。例如,温度传感器电路16利用具有温度依赖性的电路元件生成温度检测电压。具体而言,温度传感器电路16通过使用pn结的正向电压具有的温度依赖性,输出电压值依赖于温度而变化的温度检测电压。pn结的正向电压例如能够使用双极晶体管的基极/发射极间电压等。

54.另外,在进行数字方式的温度补偿处理的情况下,温度传感器电路16测定环境温度等温度,输出其结果作为温度检测数据。温度检测数据是相对于温度例如单调增加或单调减少的数据。作为该情况下的温度传感器电路16,能够使用利用环形振荡器的振荡频率具有温度依赖性的特性的温度传感器电路。具体而言,温度传感器电路16包含环形振荡器和计数器电路。计数器电路在由基于来自振荡电路11的振荡信号osc的时钟信号规定的计数期间内,对环形振荡器的振荡信号即输出脉冲信号进行计数,输出其计数值作为温度检测数据。

55.存储器17存储集成电路10中使用的各种信息。存储器17例如能够通过非易失性存

储器等实现。非易失性存储器是famos(floating gate avalanche injection mos)存储器或monos(metal-oxide-nitride-oxide-silicon)存储器等eeprom,但是不限于此,也可以是otp(one time programmable)存储器或熔丝型rom等。或者,存储器17也可以通过ram等易失性存储器实现。

56.而且,图4的端子txa、txb通过图2、图8等的接触盘36、37实现。即,振荡电路11经由通过接触盘36、37实现的端子txa、txb与振动元件5电连接。此外,端子tck通过接触盘38实现。即,来自输出缓冲电路12的时钟信号ck经由通过接触盘38实现的端子tck从外部连接端子91输出到外部。此外,端子tvdd、tgnd通过图2、图8等的接触盘39、68实现。即,电源电压vdd、gnd经由通过接触盘39、68实现的端子tvdd、tgnd供给到集成电路10。具体而言,vdd、gnd供给到电源电路14。此外,端子toe通过接触盘69实现。即,输出使能信号oe经由通过接触盘69实现的端子toe输入到集成电路10。例如输入到逻辑电路13。

57.图5示出振荡电路11的结构例。如图5所示,振荡电路11包含反相器电路dv1、dv2和可变电容电路cv1、cv2。反相器电路dv1是振动元件5的驱动电路,输入节点与振动元件5的一端连接,输出节点与振动元件5的另一端连接。反相器电路dv2对反相器电路dv1的输出信号进行缓冲,作为振荡信号osc进行输出。反相器电路dv1、dv2被供给调节电源电压vreg1和gnd而进行动作。调节电源电压vreg1由电源电路14具有的调节器生成。

58.可变电容电路cv1的一端与振动元件5的一端连接,另一端与gnd节点连接。可变电容电路cv2的一端与振动元件5的另一端连接,另一端与gnd连接。如上所述,这些可变电容电路cv1、cv2可以通过电容被温度补偿电压即电容控制电压控制的变容二极管等可变电容元件实现,也可以通过具有电容器阵列和开关阵列且电容值被频率控制数据控制的电路实现。

59.图6示出输出缓冲电路12的结构例。如图6所示,输出缓冲电路12包含nand电路na和反相器电路iv1、iv2、iv3。这样,输出缓冲电路12例如由多个信号反转电路等缓冲电路构成。而且,向nand电路na的第1输入节点输入来自振荡电路11的振荡时钟信号即振荡信号osc,向第2输入节点输入来自逻辑电路13的使能信号en。例如,在从端子toe输入的输出使能信号oe成为有效电平即高电平时,使能信号en成为高电平,通过nand电路na和反相器电路iv1、iv2、iv3对振荡信号osc进行缓冲,作为时钟信号ck进行输出。另一方面,在从端子toe输入的输出使能信号oe成为无效电平即低电平时,使能信号en成为低电平,输出缓冲电路12的输出被固定为低电平。

60.接着,对本实施方式的振动器件1的制造方法进行说明。图7是示出振动器件1的制造方法的一例的制造工序图。

61.在集成电路形成工序(s11)中,准备半导体基板20,如图1、图2所示,在半导体基板20的下表面即第2面22形成集成电路10。在再配置布线层形成工序(s12)中,例如形成具有绝缘层80、布线82、外部连接端子91、92等的再配置布线层8,使集成电路10的接触盘38、39等和外部连接端子91、92等电连接。在基座薄壁化工序(s13)中,对半导体基板20的振动元件5的搭载面侧即第1面21进行研磨,使基座2薄壁化。即,进行基座2的薄板化。

62.在孔形成工序(s14)中,形成贯通孔。具体而言,通过干式蚀刻在半导体基板20形成孔,进而,通过湿式蚀刻将孔形成到图2的布线层30的第1金属层即金属层31为止。在绝缘层形成工序(s15)中,对半导体基板20进行热氧化,在半导体基板20的表面、特别是贯通孔

的内表面形成基于氧化硅(sio2)或树脂层的绝缘膜即绝缘层44。在贯通电极形成工序(s16)中,利用铜等导电性材料在贯通孔内进行填埋,形成贯通电极40、41。在振动元件配置工序(s17)中,准备振动元件5,经由接合部件60、61将该振动元件5与半导体基板20的第1面21接合。在盖接合工序(s18)中,准备盖7,在减压环境下经由接合部件71、72将盖7与基座2接合。在单片化工序(s19)中,通过切割机等进行振动器件1的单片化。通过以上工序,得到振动器件1。

63.如上所述,在本实施方式中,将形成有分别具有振动元件5和集成电路10的多个基座2的第1半导体晶片与形成有多个盖7的第2半导体晶片贴合,由此,接合多个基座2和多个盖7。然后,进行振动器件1的单片化,由此,制造多个振动器件1。例如,制造纵、横为1mm~几mm左右、且厚度小于1mm的小型的振动器件1。这样,能够实现晶片级封装(wlp)的振动器件1,能够制造高生产量且低成本的振动器件1。即,能够通过晶片级的批量处理一并制造具有振动元件5和集成电路10的振动器件1。

64.2.贯通电极与输出缓冲电路的配置关系

65.图8是示出本实施方式的振动器件1中的输出缓冲电路12、温度传感器电路16、贯通电极40、41的配置关系的俯视图。此外,在图8中,还示出集成电路10的各电路的配置位置与贯通电极40、41、外部连接端子91、92、93、94的配置位置的关系。图8是从z轴方向负侧观察基座2的俯视时的俯视图,利用虚线示出相对于形成有集成电路10的基座2位于z轴方向正侧的贯通电极40、41的外形、以及相对于基座2位于z轴方向负侧的外部连接端子91、92、93、94的外形。图9示出振动器件1的底面中的外部连接端子91、92、93、94的配置位置,是从z轴方向负侧观察振动器件1的底面的俯视时的俯视图。另外,在图8、图9中,外部连接端子91、92、93、94成为矩形形状,但是,这些端子也可以不是严格的矩形形状,例如也可以是角部被倒角的形状,还可以是矩形形状以外的形状。

66.如上所述,本实施方式的振动器件1包含:基座2,其包含半导体基板20和贯通半导体基板20的第1面21与第2面22之间的贯通电极40;以及振动元件5,其隔着导电性的接合部件60、61固定于半导体基板20的第1面21。而且,如图8所示,在半导体基板20的第2面22配置有振荡电路11、温度补偿电路15、温度传感器电路16和输出缓冲电路12。振荡电路11经由贯通电极40、41与振动元件5电连接,使振动元件5振荡而生成振荡信号osc。温度补偿电路15根据温度传感器电路16的输出进行振荡信号osc的温度补偿。例如,如上所述,温度补偿电路15根据温度传感器电路16的输出即温度检测电压而生成温度补偿电压,根据生成的温度补偿电压对振荡电路11的可变电容电路的电容值进行调整,由此,进行振荡信号osc的温度补偿。或者,温度补偿电路15根据温度传感器电路16的输出即温度检测数据求出频率调整数据,根据求出的频率调整数据对振荡电路11的可变电容电路的电容值进行调整,由此,进行振荡信号osc的温度补偿。然后,输出缓冲电路12输出基于温度补偿后的振荡信号osc的时钟信号ck。例如,通过输出缓冲电路12对由温度补偿电路15进行温度补偿后的振荡信号osc进行缓冲,作为时钟信号ck进行输出。例如,来自输出缓冲电路12的时钟信号ck经由接触盘38从外部连接端子91输出到振动器件1的外部。该输出缓冲电路12是对振动器件1的外部负载进行驱动的电路,因此,在外部负载的驱动时有时流过例如10ma以上的电流,发热量非常大。

67.而且,如图8所示,将输出缓冲电路12与贯通电极41的距离设为dbx1,将温度传感

器电路16与贯通电极41的距离设为dsx1。这里,将连结输出缓冲电路12的区域内的任意的点和贯通电极41的区域内的任意的点的线的距离中的最短距离设为距离dbx1。此外,将连结温度传感器电路16的区域内的任意的点和贯通电极41的区域内的任意的点的线的距离中的最短距离设为距离dsx1。此时,在本实施方式中,如图8所示,dsx1《dbx1的关系成立。即,跟输出缓冲电路12与贯通电极41的距离dbx1相比,温度传感器电路16与贯通电极41的距离dsx1较小,温度传感器电路16配置于与输出缓冲电路12相比更接近贯通电极41的位置。即,在形成有振荡电路11、输出缓冲电路12、温度补偿电路15、温度传感器电路16的半导体基板20上连接固定振动元件5后,在半导体基板20的电路布局中,与输出缓冲电路12相比,将温度传感器电路16配置于离贯通电极41较近的位置。例如,在从与第1面21正交的方向俯视时,以与贯通电极41相邻的方式配置温度传感器电路16。例如,以在其间不存在其他电路块的方式将贯通电极41和温度传感器电路16配置成在俯视时相邻。

68.例如,在陶瓷的封装的第1凹部中收纳振动元件、且在第2凹部中收纳ic芯片的现有的温度补偿型的振荡器中,由ic芯片的输出缓冲电路产生的热不容易传递到振动元件。即,振动元件未直接固定于ic芯片,ic芯片和振动元件只是通过封装的内部布线等进行电连接,因此,在该内部布线的路径中,ic芯片的输出缓冲电路中的发热不容易传递到振动元件。此外,在收纳于陶瓷封装的第1凹部中的振动元件与收纳于第2凹部中的ic芯片之间存在导热率比半导体基板低的陶瓷,因此,来自ic芯片的辐射热也不容易传递到振动元件。另一方面,温度传感器电路与输出缓冲电路一起形成于同一ic芯片内,因此,输出缓冲电路中的发热立即传递到温度传感器电路。因此,在温度传感器电路中的检测温度与振动元件的实际温度之间产生误差,由于该误差而使振荡频率等振荡特性劣化。例如,在振荡器的启动时,输出缓冲电路中的发热立即传递到同一ic芯片内的温度传感器电路,由此,温度传感器电路的检测温度立即变高,另一方面,输出缓冲电路中的发热不容易传递到振动元件,因此,振动元件的实际温度不会立即变高。因此,温度传感器电路中的检测温度与振动元件的实际温度之间产生误差,产生振荡特性劣化的情况。

69.与此相对,在本实施方式中,振动元件5隔着导电性的接合部件60、61固定于半导体基板20,并且,温度传感器电路16与贯通电极41的距离dsx1比输出缓冲电路12与贯通电极41的距离dbx1小。这样,在本实施方式中,振动元件5隔着接合部件60、61直接固定于半导体基板20,因此,与使用陶瓷封装的现有振荡器相比,输出缓冲电路12中的发热容易传递到振动元件5。即,在本实施方式这样的wlp的振动器件1中,集成电路10的输出缓冲电路12中的发热容易传递到振动元件5,由于输出缓冲电路12中的发热,振动元件5的温度也在短时间内上升。此外,在输出缓冲电路12与振动元件5之间不存在导热率低的陶瓷,因此,输出缓冲电路12中的发热作为辐射热容易传递到振动元件5。另一方面,温度传感器电路16与贯通电极41的距离dsx1小,因此,温度传感器电路16能够在短时间内检测由于输出缓冲电路12中的发热而上升的振动元件5的实际温度。即,振动元件5的实际温度经由导热率高的贯通电极41等传递到集成电路10,能够通过配置于从贯通电极41起的距离dsx1较短的位置的温度传感器电路16,在短时间内检测该实际温度。例如,在振动器件1的启动时,输出缓冲电路12中的发热经由热传导路径在短时间内传递到振动元件5,由此,振动元件5的实际温度变高,经由贯通电极41等,通过配置于贯通电极41附近的温度传感器电路16检测该振动元件5的实际温度。然后,温度补偿电路15根据温度传感器电路16的检测温度进行温度补偿处理,

由此,进行与振动元件5的实际温度对应的适当的振荡频率的温度补偿。因此,能够有效地抑制以温度传感器电路16中的检测温度与振动元件5的实际温度之间的误差为原因的振荡特性的劣化的产生。

70.此外,在本实施方式中,基座2包含第1贯通电极即贯通电极41和第2贯通电极即贯通电极40。而且,振荡电路11经由贯通电极41以及贯通电极40与振动元件5电连接。这里,如图10所示,将输出缓冲电路12与第1贯通电极即贯通电极41的距离设为dbx1,将输出缓冲电路12与第2贯通电极即贯通电极40的距离设为dbx2。此外,将温度传感器电路16与贯通电极41的距离设为dsx1,将温度传感器电路16与贯通电极40的距离设为dsx2。而且,将温度传感器电路16与贯通电极41、40的距离dsx1、dsx2中的较短的距离设为dsx。在图10中,与贯通电极40相比,贯通电极41配置于离温度传感器电路16较近的位置,dsx1《dsx2,因此,dsx=dsx1。此时,在本实施方式中,dsx《dbx1且dsx《dbx2成立。即,温度传感器电路16与贯通电极41之间的较短的距离即dsx=dsx1比输出缓冲电路12与贯通电极41的距离dbx1短,并且比输出缓冲电路12与贯通电极40的距离dbx2短。

71.即,在振动元件5和集成电路10经由2个贯通电极40、41电连接的情况下,振动元件5的实际温度通过经由贯通电极41的热传导路径传递到集成电路10,并且,还通过经由贯通电极40的热传导路径传递到集成电路10。而且,在图10中,与贯通电极40相比,贯通电极41配置于离温度传感器电路16较近的位置,dsx1《dsx2的关系成立。因此,为了尽可能快速地检测由于来自输出缓冲电路12的发热而上升的振动元件5的实际温度,重要的是与离温度传感器电路16较近的一侧的贯通电极41之间的距离dsx1较短。因此,在将温度传感器电路16与贯通电极41、40的距离dsx1、dsx2中的较短的距离设为dsx=dsx1时,dsx《dbx1且dsx《dbx2的关系成立。如果这种关系成立,则与离温度传感器电路16的距离较近的一个贯通电极41之间的距离dsx1变短这样的关系成立,位于贯通电极41的附近的温度传感器电路16能够在短时间内检测通过经由贯通电极41的热传导路径传递的振动元件5的实际温度。因此,能够抑制以温度传感器电路16中的检测温度与振动元件5的实际温度之间的误差为原因的振荡特性的劣化的产生。

72.另外,以上将与图3的振动基板50的下表面侧的激励电极53电连接的贯通电极41设为第1贯通电极,将与振动基板50的上表面侧的激励电极52电连接的贯通电极40设为第2贯通电极,但是,本实施方式不限于此。例如,也可以是,与上表面侧的激励电极52电连接的贯通电极40是第1贯通电极,与下表面侧的激励电极53电连接的贯通电极41是第2贯通电极。

73.此外,在本实施方式中,基座2具有边sd1和与边sd1对置的边sd2。边sd1是第1边,边sd2是第2边。此外,基座2具有边sd3和与边sd3对置的边sd4。边sd3是第3边,边sd4是第4边。例如,在俯视时,基座2成为具有边sd1、sd2、sd3、sd4的矩形形状。另外,矩形形状不需要是严格的矩形形状,例如也可以是角部被倒角的形状。

74.而且,如图11所示,温度传感器电路16配置于与贯通电极40、41相比离边sd1较近的位置。例如,振荡电路11也配置于与贯通电极40、41相比离边sd1较近的位置,温度传感器电路16和振荡电路11沿着边sd1配置。具体而言,温度传感器电路16配置于边sd1和边sd4交叉的角部。例如,将边sd1与边sd2之间的中心线设为cl。例如,边sd1与中心线cl的距离和边sd2与中心线cl的距离相等。该情况下,温度传感器电路16和贯通电极40、41例如配置于边

sd1与中心线cl之间的区域即第1区域。另一方面,输出缓冲电路12配置于边sd2与中心线cl之间的区域即第2区域。而且,温度传感器电路16在边sd1与中心线cl之间的第1区域中配置于与贯通电极40、41相比离边sd1较近的位置。这样,能够有效利用边sd1与贯通电极40、41之间的区域,将温度传感器电路16配置于离贯通电极41等较近的位置。由此,能够进行温度传感器电路16等的高效的布局配置,并且,例如在贯通电极41的附近配置温度传感器电路16,由此,能够抑制以温度传感器电路16中的检测温度与振动元件5的实际温度之间的误差为原因的振荡特性的劣化的产生。

75.具体而言,如图11所示,将与第1边即边sd1平行且穿过贯通电极40、41的线设为假想线vl。该情况下,温度传感器电路16配置于边sd1与假想线vl之间的区域。例如,如图1、图2所示,在贯通电极40、41的x轴方向负侧存在基座2和盖7的接合部分。即,基座2和盖7在该接合部分处通过接合部件72接合。因此,贯通电极40、41与该基座2和盖7的接合部分相比位于x轴方向正侧。因此,在集成电路10中,贯通电极40、41的x轴方向负侧的区域可能成为死区。关于这点,在本实施方式中,如图11所示,在可能成为死区的边sd1与假想线vl之间的区域配置温度传感器电路16。由此,能够防止在集成电路10的布局中产生死区,能够进行集成电路10的高效的布局配置。此外,通过在边sd1与穿过贯通电极40、41的假想线vl之间的区域配置温度传感器电路16,能够拉近温度传感器电路16与贯通电极40、41的距离。由此,还能够抑制以温度传感器电路16中的检测温度与振动元件5的实际温度之间的误差为原因的振荡特性的劣化的产生。

76.此外,在图11中,在边sd1与假想线vl之间的区域配置有温度传感器电路16和振荡电路11。例如,在边sd1与假想线vl之间的区域中,温度传感器电路16和振荡电路11沿着边sd1配置。例如,以与贯通电极40、41相邻的方式配置有温度传感器电路16和振荡电路11。

77.这样,能够有效利用可能成为死区的边sd1与假想线vl之间的区域来配置温度传感器电路16和振荡电路11。由此,能够防止在集成电路10的布局中产生死区,能够进行集成电路10的高效的布局配置。此外,通过在这种区域中配置振荡电路11,能够利用布线la、lb以最短路径的方式连接振荡电路11与贯通电极40、41之间。因此,能够减少布线la、lb中的寄生电阻或寄生电容,能够抑制以该寄生电阻或寄生电容为原因的振荡电路11的振荡特性的劣化。

78.此外,如图11、图1、图2所示,在从与半导体基板20的第1面21正交的方向俯视时,在用于接合振动元件5的接合部件60、61与边sd1之间配置有贯通电极40、41。例如,从边sd1朝向边sd2,在俯视时按照贯通电极40、41、接合部件60、61的顺序进行配置。例如,从边sd1朝向边sd2,以在俯视时相邻的方式配置贯通电极40、41和接合部件60、61。

79.这样,振动元件5的实际温度沿着从边sd2朝向边sd1的方向以较短的热传导路径经由接合部件60、61热传递到贯通电极40、41,通过配置于贯通电极40、41的附近的温度传感器电路16检测被传递热的振动元件5的实际温度。因此,能够以较短的热传导路径检测振动元件5的实际温度,能够进行基于检测到的振动元件5的实际温度的振荡频率的温度补偿。其结果,能够实现误差少的温度补偿,能够抑制以温度传感器电路16中的检测温度与振动元件5的实际温度之间的误差为原因的振荡特性的劣化的产生。

80.此外,如图11所示,贯通电极40、41配置于输出缓冲电路12与温度传感器电路16之间。例如,在将从输出缓冲电路12朝向温度传感器电路16的方向设为dr的情况下,在输出缓

冲电路12的方向dr侧配置贯通电极41等,在贯通电极41等的方向dr侧配置温度传感器电路16。例如,也可以说从边sd1朝向边sd2按照温度传感器电路16、贯通电极40、41、输出缓冲电路12的顺序进行配置。

81.例如,在振动器件1的启动时,相比于在输出缓冲电路12发热时该发热的影响出现在温度传感器电路16中为止的时间,振动元件5被加热而使加热的影响出现在振荡频率中为止的时间较长。因此,以贯通电极40、41配置于输出缓冲电路12与温度传感器电路16之间的方式配置输出缓冲电路12、贯通电极40、41、温度传感器电路16,由此,与温度传感器电路16相比,与贯通电极40、41电连接的振动元件5容易受到输出缓冲电路12的发热的影响。例如,输出缓冲电路12的发热经由贯通电极40、41传递到振动元件5,此后传递到温度传感器电路16。由此,能够使温度传感器电路16的检测温度和振动元件5的实际温度接近,能够抑制以温度传感器电路16中的检测温度与振动元件5的实际温度之间的误差为原因的振荡特性的劣化的产生。

82.此外,温度补偿电路15配置于输出缓冲电路12与温度传感器电路16之间。例如,在连结输出缓冲电路12和温度传感器电路16的区域的范围内配置有温度补偿电路15的至少一部分。例如,在将从输出缓冲电路12朝向温度传感器电路16的方向设为dr的情况下,在输出缓冲电路12的方向dr侧配置温度补偿电路15,在温度补偿电路15的方向dr侧配置温度传感器电路16。具体而言,在温度补偿电路15的方向dr侧配置贯通电极41等,在贯通电极41等的方向dr侧配置温度传感器电路16。

83.例如,温度补偿电路15是与输出缓冲电路12相比消耗电流较小、且与输出缓冲电路12相比不容易发热的电路块。因此,通过将这种温度补偿电路15配置于输出缓冲电路12与温度传感器电路16之间,输出缓冲电路12的发热不容易传递到温度传感器电路16。由此,能够减少温度传感器电路16中的检测温度与振动元件5的实际温度之间的误差。此外,能够在有限的集成电路10的布局面积中高效地配置输出缓冲电路12、温度补偿电路15、温度传感器电路16等各电路块,因此,能够实现集成电路10的布局面积的小面积化。

84.此外,在图11中,输出缓冲电路12沿着边sd3配置,但是,如图12所示,也可以沿着边sd2配置输出缓冲电路12。例如,以输出缓冲电路12的长边沿着边sd2的方式配置输出缓冲电路12。而且,如图12所示,在半导体基板20的第2面22中,在输出缓冲电路12与温度传感器电路16之间配置逻辑电路13。例如,集成电路10中的进行各种控制的控制电路即逻辑电路13配置于输出缓冲电路12与温度传感器电路16之间。另外,与图11同样,在图12中,温度补偿电路15也配置于输出缓冲电路12与温度传感器电路16之间。

85.例如,逻辑电路13是与输出缓冲电路12相比消耗电流较小、且与输出缓冲电路12相比不容易发热的电路块。因此,通过将这种逻辑电路13配置于输出缓冲电路12与温度传感器电路16之间,输出缓冲电路12的发热不容易传递到温度传感器电路16。由此,能够减少温度传感器电路16中的检测温度与振动元件5的实际温度之间的误差。此外,能够在有限的集成电路10的布局面积中高效地配置输出缓冲电路12、逻辑电路13、温度传感器电路16等各电路块,因此,能够实现集成电路10的布局面积的小面积化。

86.另外,在图11、图12中,将从边sd1朝向边sd2的方向设为第1方向,将从边sd3朝向边sd4的方向设为第2方向。第1方向是沿着x轴的方向,第2方向是沿着y轴的方向。此外,将第1方向的相反方向设为第3方向,将第2方向的相反方向设为第4方向。此时,在边sd1的第1

方向侧配置有振荡电路11,在振荡电路11的第1方向侧配置有贯通电极40、41。此外,在振荡电路11的第2方向侧配置有温度传感器电路16。此外,在贯通电极40、41的第1方向侧配置有输出缓冲电路12、逻辑电路13、电源电路14、温度补偿电路15、存储器17。即,在贯通电极40、41与边sd2之间的区域配置有输出缓冲电路12、逻辑电路13、电源电路14、温度补偿电路15、存储器17。而且,在图11中,在输出缓冲电路12的第2方向侧配置有温度补偿电路15,在温度补偿电路15的第2方向侧配置有逻辑电路13、电源电路14,在逻辑电路13的第2方向侧配置有存储器17。另一方面,在图12中,在输出缓冲电路12的第3方向侧配置有逻辑电路13、温度补偿电路15。而且,在逻辑电路13的第3方向侧配置有电源电路14,在逻辑电路13的第2方向侧配置有存储器17。第3方向是第1方向的相反方向,是从边sd2朝向边sd1的方向。

87.此外,如图1、图2所示,接合部件60包含一端与振动元件5电连接、且另一端与贯通电极40电连接的凸块62。另外,接合部件61也包含与凸块62相同的未图示的凸块,但是,这里省略说明。例如,在图1、图2中,凸块62的另一端经由端子64与贯通电极40电连接。作为凸块62,例如能够使用金凸块、银凸块、铜凸块、焊料凸块等金属凸块。通过使用这种金属凸块等凸块62作为接合部件60,输出缓冲电路12中的发热容易从贯通电极40等经由凸块62等传递到振动元件5。而且,能够使用温度传感器电路16,以较少的误差检测基于输出缓冲电路12的发热的振动元件5的实际温度。

88.此外,在本实施方式中,如图1所示,振动器件1包含盖7,该盖7以收纳振动元件5的方式与基座2接合。例如,盖7通过接合部件71、72与基座2接合。如果设置这种盖7,则能够在通过接合基座2和盖7而形成的收纳空间sp中配置振动元件5。例如,能够在被气密密封的收纳空间sp中配置振动元件5,能够适当地保护振动元件5等不受冲击、尘埃、热或湿气等影响。

89.这里,与基座2同样,盖7能够通过硅基板实现。由此,基座2和盖7的线膨胀系数相等,抑制由于热膨胀而产生热应力,能够实现具有优异的振动特性的振动器件1。此外,能够通过半导体制造工艺形成基座2和盖7双方。因此,能够高精度地制造振动器件1,并且能够实现其小型化。但是,盖7不限于硅基板,也可以通过ge、gap、gaas、inp等半导体基板实现。

90.另外,振动器件1也可以构成为不包含与基座2接合的盖7。例如,也可以将在第1面21侧配置有振动元件5、且在第2面22形成有集成电路10的基座2收纳于其他封装,或者收纳于在带恒温槽的石英振荡器(ocxo)中成为恒温槽的容器中。

91.此外,如图1、图2、图8等所示,在本实施方式的振动器件1中,贯通电极40、41和外部连接端子91被配置成,在从与第1面21正交的方向俯视时不重叠。例如,使振动元件5和集成电路10电连接的贯通电极40、41以及输出时钟信号ck的外部连接端子91被配置成,在从z轴方向俯视时不重叠。这样,在本实施方式中,在包含具有振荡电路11和输出缓冲电路12的集成电路10以及振动元件5的wlp(wafer level package)的振动器件1中,使振动元件5和集成电路10的振荡电路11电连接的贯通电极40、41以及时钟信号ck的输出用的外部连接端子91被配置成在俯视时不重叠。即,将与振动元件5电连接的布线的一部分即贯通电极40、41、以及基于振荡信号osc的时钟信号ck的输出用的外部连接端子91这样的流过ac信号的外部连接端子配置成在俯视时不重叠,由此,能够减少贯通电极40、41与外部连接端子91之间的电容耦合的电容。

92.例如,在本实施方式中,与使用现有的陶瓷封装的情况不同,在半导体基板20上直

接安装振动元件5,构成振动器件1,因此,产生以下这种特有的课题。在基于wlp的小型的振动器件1的封装中,在构成气密封装的一部分的半导体基板20的下表面即第2面22形成有集成电路10,与振动元件5电连接的被称为导通孔或通孔的贯通电极40、41形成于半导体基板20。而且,与振动元件5电连接的贯通电极40、41特别是在附近配置有交流信号即ac信号的端子或电极而进行电容耦合时,对振荡频率等振荡特性产生不良影响。而且,在硅基板等半导体基板20的第2面22侧形成有由聚酰亚胺等树脂层形成的膜厚较薄的绝缘层80,进而,在绝缘层80的下表面形成有例如4个外部连接端子91~94。这里,绝缘层80的膜厚比半导体基板20薄,例如为0.1mm以下。此外,如图2所示,在贯通电极40、41的周围也形成有较薄的绝缘层44。此外,与现有的陶瓷封装不同,可能成为电介质或导电体的半导体基板20介于贯通电极40、41与外部连接端子91~94之间。因此,在假设在俯视时重叠地配置贯通电极40、41和ac信号即时钟信号ck的输出用的外部连接端子91时,由于它们隔着这些较薄的绝缘层80、44等而配置,因此,电容耦合增大,对振荡特性产生不良影响。即,电容值与电极之间的距离成反比,因此,基于较薄的绝缘层80、44的电容增大。而且,当贯通电极40、41与外部连接端子91之间的电容耦合的电容增大时,外部连接端子91中的时钟信号ck的信号成分作为噪声而经由贯通电极40、41传递到振动元件5或振荡电路11,产生振荡特性劣化等问题。

93.因此,在本实施方式中,如图8等所示,将与振动元件5电连接的贯通电极40、41和输出ac信号即时钟信号ck的外部连接端子91配置成在俯视时不重叠。这样,如果将贯通电极40、41和外部连接端子91配置成在俯视时不重叠,则与贯通电极40、41和外部连接端子91被配置成在俯视时重叠的情况相比,能够拉开贯通电极40、41与外部连接端子91之间的距离。由此,能够减少贯通电极40、41与外部连接端子91之间的电容耦合的电容,能够有效地抑制振动元件5的振荡特性劣化等情况。

94.另外,对振动器件1的外部连接端子91~94进行这样的安装:通过焊接等与安装振动器件1的电路基板等的端子或布线连接。因此,作为外部连接端子91~94,优选是适于焊接等安装的端子,还需要在安装时不会破损的热耐性和强度。

95.关于这点,考虑使用集成电路的焊盘作为外部连接端子的方法。例如,使用由布线层的最上层的金属层形成的焊盘作为外部连接端子。但是,集成电路的焊盘不是适于焊接等安装的端子,面积较小,热耐性和强度较低,因此,可能产生在安装时破损等问题。

96.与此相对,在本实施方式的振动器件1中,使用隔着绝缘层80设置于半导体基板20的第2面22侧的外部连接端子91~94。即,不使用集成电路10的接触盘38、39、68、69,而使用与这些焊盘分开设置的、例如在再配置布线层8的制造工序中形成的外部连接端子91~94。因此,能够使用适于基于焊接等的安装的端子作为外部连接端子91~94。例如,外部连接端子91~94与接触盘38、39、68、69相比,能够大面积化,并且使膜厚增大而确保强度。因此,能够容易地将外部连接端子91~94与外部的端子或布线连接来进行安装,并且,还能够抑制安装时产生破损等。

97.另一方面,这样,在外部连接端子91~94成为大面积时,例如贯通电极40、41与外部连接端子91之间的电容耦合的电容可能增大。关于这点,在本实施方式中,将贯通电极40、41和外部连接端子91配置成在俯视时不重叠,因此,即使外部连接端子91成为大面积,也能够抑制以电容耦合为原因的振荡特性的劣化。因此,根据本实施方式,能够同时实现基于与外部的端子或布线之间的连接的安装容易、热耐性和强度较高且不易破损的外部连接

端子91~94的提供、以及以贯通电极40、41与外部连接端子91之间的电容耦合为原因的振荡特性的劣化的抑制。

98.3.变形例

99.接着,对本实施方式的各种变形例进行说明。例如,图13是贯通电极40的另一例。另外,贯通电极41也同样,因此,省略说明。在图13中,在基座2的贯通孔的内壁形成有绝缘层44,在绝缘层44的更内侧形成有树脂层45。而且,通过形成于树脂层45的内侧的金属层构成贯通电极40。通过这种贯通电极40,能够使振动元件5和集成电路10的振荡电路11电连接。即,振动元件5和集成电路10的接触盘36通过由凸块62构成的接合部件60以及贯通电极40而电连接,接触盘36作为图4的端子txa、txb与振荡电路11电连接,由此,振动元件5和振荡电路11电连接。

100.此外,输出缓冲电路12也可以以lvds(low voltage differential signaling)、pecl(positive emitter coupled logic)、hcsl(high speed current steering logic)或差动cmos(complementary mos)等信号形式,将差动的时钟信号ck、ckx输出到外部。即,输出缓冲电路12也可以具有lvds用、pecl用、hcsl用或差动cmos用的输出驱动器。例如,图14是lvds用的输出驱动器的结构例。该输出驱动器具有:电流源用的p型晶体管,其流过3.5ma的驱动电流;p型和n型晶体管,它们构成被输入差动的输入信号in、inx而输出差动的时钟信号ck、ckx的差动部;以及n型晶体管,其设置于gnd侧。对成为电流源的p型的晶体管的栅极施加偏置电压bsp。由此,流过3.5ma的驱动电流。图15是pecl用的输出驱动器的结构例。该输出驱动器具有:p型的晶体管,其流过15.25ma的驱动电流;2个p型的晶体管,它们构成差动部;以及2个p型的晶体管,它们构成在时钟信号ck、ckx的节点流过5.7ma的偏置电流的偏置电流电路。

101.图16是如图14、图15那样输出差动的时钟信号ck、ckx的情况下的外部连接端子配置的例子。在图16中,成为具有外部连接端子91a、91b、92、93、94、95这样6端子的外部连接端子的振动器件1。外部连接端子91a、91b是输出差动的时钟信号ck、ckx的端子。外部连接端子92、93是vdd、gnd用的端子,外部连接端子94是输出使能信号oe用的端子。外部连接端子95是nc(non connection)端子。图16的外部连接端子91a、91b、92、93、94、95也在振动器件1中隔着绝缘层80设置于基座2的半导体基板20的第2面22侧。而且,贯通电极40、41和差动的时钟信号ck、ckx的输出用的外部连接端子91a、91b被配置成在俯视时不重叠。

102.如上所述,本实施方式的振动器件包含:基座,其包含具有第1面和与第1面处于正反关系的第2面的半导体基板、以及贯通第1面与第2面之间的贯通电极;以及振动元件,其隔着导电性的接合部件固定于第1面。在第2面配置有:振荡电路,其经由贯通电极而与振动元件电连接,使振动元件振荡而生成振荡信号;温度传感器电路;温度补偿电路,其根据温度传感器电路的输出进行振荡信号的温度补偿;以及输出缓冲电路,其输出基于温度补偿后的振荡信号的时钟信号。而且,在将输出缓冲电路与贯通电极的距离设为dbx1、将温度传感器电路与贯通电极的距离设为dsx1时,dsx1《dbx1。

103.这样,本实施方式的振动器件包含:基座,其具有半导体基板和贯通半导体基板的贯通电极;以及振动元件,其隔着导电性的固定部件固定于半导体基板的第1面侧。此外,在半导体基板的第2面配置有振荡电路、温度传感器电路、温度补偿电路和输出缓冲电路。而且,将输出缓冲电路与贯通电极的距离设为dbx1,关于温度传感器电路与贯通电极的距离

dsx1,dsx1《dbx1的关系成立。这样,在本实施方式的振动器件中,振动元件隔着接合部件固定于半导体基板,因此,输出缓冲电路中的发热容易传递到振动元件。另一方面,温度传感器电路与贯通电极的距离dsx1较小,因此,温度传感器电路能够在短时间内检测由于输出缓冲电路中的发热而上升的振动元件的实际温度。因此,能够抑制以温度传感器电路中的检测温度与振动元件的实际温度之间的误差为原因的振荡特性的劣化的产生。

104.此外,在本实施方式中,也可以是,基座包含作为贯通电极的第1贯通电极和第2贯通电极,振荡电路经由第1贯通电极以及第2贯通电极与振动元件电连接。在设输出缓冲电路与第2贯通电极的距离为dbx2、温度传感器电路与第1贯通电极的距离dsx1和温度传感器电路与第2贯通电极的距离dsx2中的较短的距离为dsx时,dsx《dbx1且dsx《dbx2。

105.这样,与离温度传感器电路的距离较近的一个贯通电极之间的距离dsx1变短这样的关系成立,位于贯通电极的附近的温度传感器电路能够在短时间内检测通过经由贯通电极的热传导路径传递的振动元件的实际温度。

106.此外,在本实施方式中,也可以是,基座具有第1边和与第1边对置的第2边,温度传感器电路配置于相比于贯通电极更接近第1边的位置。

107.这样,能够进行温度传感器电路的高效的布局配置,并且,通过在贯通电极的附近配置温度传感器电路,能够抑制以温度传感器电路中的检测温度与振动元件的实际温度之间的误差为原因的振荡特性的劣化的产生。

108.此外,在本实施方式中,也可以是,温度传感器电路配置于第1边与假想线之间的区域,该假想线与第1边平行且穿过贯通电极。

109.这样,能够有效利用第1边与假想线之间的区域来配置温度传感器电路,能够进行高效的布局配置。此外,能够拉近温度传感器电路与贯通电极的距离,还能够抑制以温度传感器电路中的检测温度与振动元件的实际温度之间的误差为原因的振荡特性的劣化的产生。

110.此外,在本实施方式中,也可以是,在上述区域配置有温度传感器电路和振荡电路。

111.这样,能够有效利用第1边与假想线之间的区域来配置温度传感器电路和振荡电路,能够进行高效的布局配置。

112.此外,在本实施方式中,也可以是,在从与第1面正交的方向俯视时,贯通电极配置在接合部件与第1边之间。

113.这样,振动元件的实际温度沿着从第2边朝向第1边的方向以较短的热传导路径经由接合部件热传递到贯通电极,能够通过配置于贯通电极的附近的温度传感器电路检测被传递热的振动元件的实际温度。

114.此外,在本实施方式中,也可以是,贯通电极配置于输出缓冲电路与温度传感器电路之间。

115.这样,输出缓冲电路的发热经由贯通电极传递到振动元件,此后传递到温度传感器电路,能够使温度传感器电路的检测温度和振动元件的实际温度接近。

116.此外,在本实施方式中,也可以是,温度补偿电路配置于输出缓冲电路与温度传感器电路之间。

117.这样,通过将与输出缓冲电路相比不容易发热的温度补偿电路配置于输出缓冲电

路与温度传感器电路之间,输出缓冲电路的发热不容易传递到温度传感器电路,能够减少温度传感器电路中的检测温度与振动元件的实际温度之间的误差。

118.此外,在本实施方式中,也可以是,在第2面中,在输出缓冲电路与温度传感器电路之间配置有逻辑电路。

119.这样,通过将与输出缓冲电路相比不容易发热的逻辑电路配置于输出缓冲电路与温度传感器电路之间,输出缓冲电路的发热不容易传递到温度传感器电路,能够减少温度传感器电路中的检测温度与振动元件的实际温度之间的误差。

120.此外,在本实施方式中,也可以是,接合部件包含一端与振动元件电连接、且另一端与贯通电极电连接的凸块。

121.这样,通过使用凸块作为接合部件,输出缓冲电路中的发热容易从贯通电极经由凸块传递到振动元件,能够使用温度传感器电路,以较少的误差检测基于输出缓冲电路的发热的振动元件的实际温度。

122.此外,在本实施方式中,也可以是,振动器件包含盖,盖以收纳振动元件的方式与基座接合。

123.这样,能够在由基座和盖形成的收纳空间中配置振动元件,因此,能够适当地保护振动元件不受冲击、尘埃、热或湿气等影响。

124.另外,如上所述详细说明了本实施方式,但是,本领域技术人员能够容易地理解到能够进行实质上不脱离本发明的新事项和效果的多种变形。因此,这种变形例全部包含在本发明的范围内。例如,在说明书或附图中,至少一次与更加广义或同义的不同用语一起记载的用语能够在说明书或附图的任意部位置换为该不同的用语。此外,本实施方式和变形例的全部组合也包含在本发明的范围内。此外,振动器件的结构、动作等也不限于本实施方式中说明的内容,能够进行各种变形实施。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。