1.本发明涉及一种静电放电技术,且特别涉及一种双向静电放电保护装置。

背景技术:

2.静电放电(esd)损坏已成为纳米级互补式金氧半(cmos)制程中制造的cmos集成电路产品的主要可靠性问题。esd保护元件通常设计用于释放esd能量,从而可以防止集成电路芯片的esd损坏。

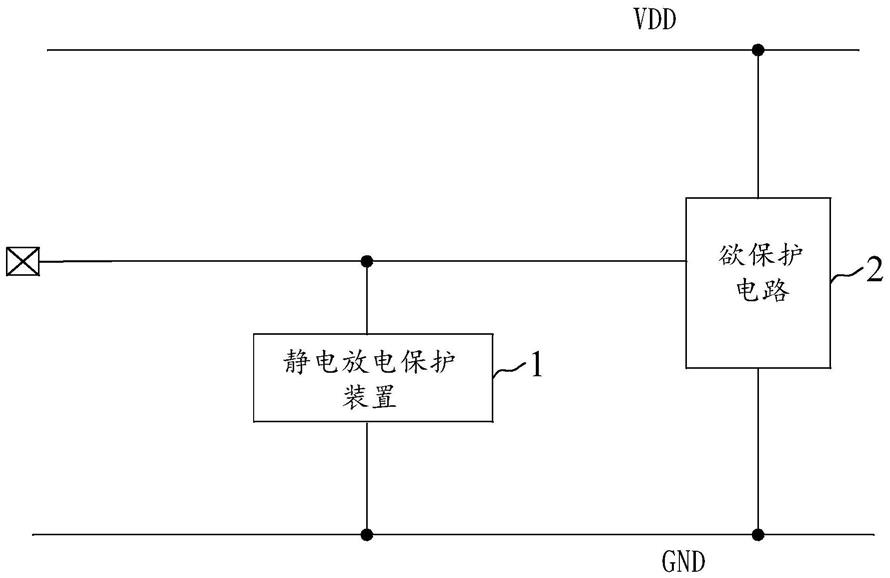

3.静电放电保护装置的工作原理如图1所示,在集成电路芯片上,静电放电(esd)保护装置1并联欲保护电路2,当esd情况发生时,esd保护装置1瞬间被触发,同时,esd保护装置1亦可提供一低电阻路径,以供瞬时的esd电流进行放电,让esd瞬时电流的能量通过esd保护装置1得以释放。为了达到双向静电放电的目的,在美国专利证号10573635b2与10468513b1皆有实现双向瞬时电压抑制器。美国专利证号10573635b2公开两个互相串联的双极性接面晶体管,美国专利证号10468513b1公开硅控整流器。在实务中,双极性接面晶体管与硅控整流器的握持(holding)电压与崩溃电压皆须高于欲保护装置的操作电压,使闩锁事件得以避免。然而,在设计双极性接面晶体管具有所需崩溃电压时,双极性接面晶体管的握持电压将会过高。因此,在静电放电事件发生时,双极性接面晶体管具有较高导通电阻。当设计硅控整流器具有所需握持电压时,硅控整流器的崩溃电压也是过高。

4.因此,本发明在针对上述的困扰,提出一种双向静电放电保护装置,以解决现有技术所产生的问题。

技术实现要素:

5.本发明提供一种双向静电放电保护装置,其在不需要牺牲静电放电耐受度及不会遭受到闩锁(latch-up)事件的前提下设计所需崩溃电压时,双向静电放电保护装置具有仍然高于欲保护装置的操作电压的较低的箝位电压与较低的握持电压。

6.在本发明的一实施例中,提供一种双向静电放电保护装置,其包括至少一个双极性接面晶体管与至少一个硅控整流器,硅控整流器串联耦接双极性接面晶体管。在静电放电电压施加在双极性接面晶体管与硅控整流器时,双极性接面晶体管的崩溃电压的绝对值小于硅控整流器的崩溃电压的绝对值,且双极性接面晶体管的握持(holding)电压的绝对值大于硅控整流器的握持电压的绝对值。

7.在本发明的一实施例中,在正静电放电电压施加在双极性接面晶体管与硅控整流器时,双极性接面晶体管与硅控整流器具有一第一代表性电流对电压曲线。在负静电放电电压施加在双极性接面晶体管与硅控整流器时,双极性接面晶体管与硅控整流器具有一第二代表性电流对电压曲线。第一代表性电流对电压曲线与第二代表性电流对电压曲线以零电压为中心彼此呈对称或非对称。

8.在本发明的一实施例中,第一代表性电流对电压曲线具有一第一崩溃电压、一第一握持电压与一第一箝位电压,第二代表性电流对电压曲线具有一第二崩溃电压、一第二

握持电压与一第二箝位电压,第一崩溃电压、第一握持电压与第一箝位电压的绝对值分别等于第二崩溃电压、第二握持电压与第二箝位电压的绝对值。

9.在本发明的一实施例中,双向静电放电保护装置还包括一半导体基板与一隔离结构。半导体基板具有第一导电型,半导体基板上设有一磊晶层,磊晶层具有与第一导电型相反的第二导电型。双极性接面晶体管、一第一掺杂阱区与至少一个第二掺杂阱区设于磊晶层中,第一掺杂阱区与第二掺杂阱区具有第一导电型。一第一重掺杂区与一第二重掺杂区设于第一掺杂阱区中,第一重掺杂区与第二重掺杂区分别具有第二导电型与第一导电型。至少一个第三重掺杂区与至少一个第四重掺杂区设于第二掺杂阱区中,第三重掺杂区与第四重掺杂区分别具有第一导电型与第二导电型。磊晶层、第一掺杂阱区、第二掺杂阱区、第一重掺杂区、第二重掺杂区、第三重掺杂区与第四重掺杂区形成硅控整流器,双极性接面晶体管经由一外部导线耦接第一重掺杂区与第二重掺杂区。隔离结构设于磊晶层中,并位于硅控整流器与双极性接面晶体管之间。隔离结构接触半导体基板,并将硅控整流器与双极性接面晶体管隔离,隔离结构的底部位置等于或深于磊晶层的底部位置。

10.在本发明的一实施例中,隔离结构设于半导体基板中。

11.在本发明的一实施例中,隔离结构环绕硅控整流器与双极性接面晶体管。

12.在本发明的一实施例中,双向静电放电保护装置还包括一重掺杂埋层,其设于半导体基板与磊晶层之间,并设于双极性接面晶体管与硅控整流器的下方,其中重掺杂埋层具有第二导电型,隔离结构贯穿重掺杂埋层。

13.在本发明的一实施例中,第一导电型为n型,第二导电型为p型。

14.在本发明的一实施例中,第一导电型为p型,第二导电型为n型。

15.在本发明的一实施例中,双极性接面晶体管包括至少一个第三掺杂阱区、至少一个第五重掺杂区与至少一个第六重掺杂区。第三掺杂阱区设于磊晶层中,第五重掺杂区与第六重掺杂区设于第三掺杂阱区。第五重掺杂区与第六重掺杂区的导电型与第三掺杂阱区的导电型相反,第六重掺杂区耦接外部导线。

16.在本发明的一实施例中,第五重掺杂区耦接一第一接脚,第三重掺杂区与第四重掺杂区耦接一第二接脚。

17.在本发明的一实施例中,在正静电放电电压施加在第一接脚与第二接脚时,静电放电电流依序通过第五重掺杂区、第三掺杂阱区、第六重掺杂区、外部导线、第一重掺杂区、第一掺杂阱区、磊晶层、第二掺杂阱区与第三重掺杂区。

18.在本发明的一实施例中,在负静电放电电压施加在第一接脚与第二接脚时,静电放电电流依序通过第四重掺杂区、第二掺杂阱区、磊晶层、第一掺杂阱区、第二重掺杂区、外部导线、第六重掺杂区、第三掺杂阱区与第五重掺杂区。

19.在本发明的一实施例中,至少一个双极性接面晶体管包括多个双极性接面晶体管。

20.在本发明的一实施例中,至少一个硅控整流器包括多个硅控整流器。

21.基于上述,双向静电放电保护装置串联耦接双极性接面晶体管与硅控整流器,故在不需要牺牲静电放电耐受度及不会遭受到闩锁(latch-up)事件的前提下设计所需崩溃电压时,双向静电放电保护装置具有仍然高于欲保护装置的操作电压的较低的箝位电压与较低的握持电压。

附图说明

22.图1为现有技术的集成电路芯片上的静电放电保护装置连接一欲保护电路的示意图。

23.图2为本发明的双向静电放电保护装置的第一实施例的示意图。

24.图3为本发明的一实施例的双向静电放电保护装置的电流对电压曲线图。

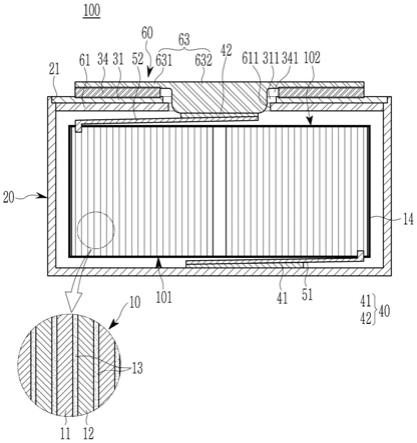

25.图4为本发明的双向静电放电保护装置的第二实施例的结构剖视图。

26.图5为本发明的双向静电放电保护装置的第三实施例的结构剖视图。

27.图6为本发明的双向静电放电保护装置的第四实施例的结构剖视图。

28.图7为本发明的双向静电放电保护装置的第五实施例的结构剖视图。

29.图8为本发明的双向静电放电保护装置的第六实施例的结构剖视图。

30.图9为本发明的双向静电放电保护装置的第七实施例的结构剖视图。

31.图10为本发明的双向静电放电保护装置的第八实施例的结构剖视图。

32.图11为本发明的双向静电放电保护装置的第九实施例的结构剖视图。

33.附图标记说明:1-静电放电保护装置;2-欲保护电路;3-双向静电放电保护装置;30-双极性接面晶体管;300-第三掺杂阱区;301-第五重掺杂区;302-第六重掺杂区;31-硅控整流器;310-第一掺杂阱区;311-第二掺杂阱区;312-第一重掺杂区;313-第二重掺杂区;314-第三重掺杂区;315-第四重掺杂区;32-第一接脚;33-第二接脚;34-半导体基板;35-隔离结构;36-磊晶层;37-外部导线;38-重掺杂埋层;ve-静电放电电压;vb-第一崩溃电压;vh-第一握持电压;vc-第一箝位电压;vb

’‑

第二崩溃电压;vh

’‑

第二握持电压;vc

’‑

第二箝位电压。

具体实施方式

34.本发明的实施例将通过下文配合相关图式进一步加以解说。尽可能的,于图式与说明书中,相同标号代表相同或相似构件。于图式中,基于简化与方便标示,形状与厚度可能经过夸大表示。可以理解的是,未特别显示于图式中或描述于说明书中的元件,为所属技术领域中具有通常技术者所知的形态。本领域的通常技术者可依据本发明的内容而进行多种的改变与修改。

35.除非特别说明,一些条件句或字词,例如“可以(can)”、“可能(could)”、“也许(might)”,或“可(may)”,通常是试图表达本案实施例具有,但是也可以解释成可能不需要的特征、元件或步骤。在其他实施例中,这些特征、元件或步骤可能是不需要的。

36.于下文中关于“一个实施例”或“一实施例”的描述指关于至少一实施例内所相关连的一特定元件、结构或特征。因此,于下文中多处所出现的“一个实施例”或“一实施例”的多个描述并非针对同一实施例。再者,于一或多个实施例中的特定构件、结构与特征可依照一适当方式而结合。

37.在说明书及权利要求书中使用了某些词汇来指称特定的元件。然而,所属技术领域中具有通常知识者应可理解,同样的元件可能会用不同的名词来称呼。说明书及权利要求书并不以名称的差异做为区分元件的方式,而是以元件在功能上的差异来做为区分的基准。在说明书及权利要求书所提及的“包括”为开放式的用语,故应解释成“包括但不限定于”。另外,“耦接”在此包括任何直接及间接的连接手段。因此,若文中描述第一元件耦接于

第二元件,则代表第一元件可通过电性连接或无线传输、光学传输等信号连接方式而直接地连接于第二元件,或者通过其他元件或连接手段间接地电性或信号连接至所述第二元件。

38.本发明特别以下述例子加以描述,这些例子仅用以举例说明而已,因为对于熟习此技艺者而言,在不脱离本揭示内容的精神和范围内,当可作各种的更动与润饰,因此本揭示内容的保护范围当视权利要求书所界定者为准。在通篇说明书与权利要求书中,除非内容清楚指定,否则“一”以及“所述”的意义包括这一类叙述包括“一或至少一”所述元件或成分。此外,如本发明所用,除非从特定上下文明显可见将复数个排除在外,否则单数冠词亦包括复数个元件或成分的叙述。而且,应用在此描述中与下全部权利要求书中时,除非内容清楚指定,否则“在其中”的意思可包括“在其中”与“在其上”。在通篇说明书与权利要求书所使用的用词(terms),除有特别注明,通常具有每个用词使用在此领域中、在此发明的内容中与特殊内容中的平常意义。某些用以描述本发明的用词将于下或在此说明书的别处讨论,以提供从业人员(practitioner)在有关本发明的描述上额外的引导。在通篇说明书的任何地方的例子,包括在此所讨论的任何用词的例子的使用,仅用以举例说明,当然不限制本发明或任何例示用词的范围与意义。同样地,本发明并不限于此说明书中所提出的各种实施例。

39.在下面的描述中,将提供一种双向静电放电保护装置,其串联耦接双极性接面晶体管与硅控整流器,故在不需要牺牲静电放电耐受度及不会遭受到闩锁(latch-up)事件的前提下设计所需崩溃电压时,双向静电放电保护装置具有仍然高于欲保护装置的操作电压的较低箝位电压与较低握持电压。

40.图2为本发明的双向静电放电保护装置的第一实施例的示意图,图3为本发明的一实施例的双向静电放电保护装置的电流对电压曲线图。请参照图2与图3,双向静电放电保护装置3包括至少一个双极性接面晶体管30与至少一个硅控整流器31。为了清晰与方便,第一实施例以一个双极性接面晶体管30与一个硅控整流器31为例。在另一实施例中,使用一个或更多双极性接面晶体管与一个或更多硅控整流器以适用于高电压应用。硅控整流器31串联耦接双极性接面晶体管30,双极性接面晶体管30可为npn双极性接面晶体管或pnp双极性接面晶体管。双极性接面晶体管30的基极为浮接。双极性接面晶体管30与硅控整流器31分别耦接一第一接脚32与一第二接脚33。在静电放电电压施加在双极性接面晶体管30与硅控整流器31时,双极性接面晶体管30的崩溃电压的绝对值小于硅控整流器31的崩溃电压的绝对值,且双极性接面晶体管30的握持(holding)电压的绝对值大于硅控整流器31的握持电压的绝对值。在正静电放电电压ve施加在双极性接面晶体管30与硅控整流器31时,双极性接面晶体管30与硅控整流器31具有一第一代表性电流对电压曲线。在负静电放电电压ve施加在双极性接面晶体管30与硅控整流器31时,双极性接面晶体管30与硅控整流器31具有一第二代表性电流对电压曲线。电流对电压曲线的静电放电电流以ie表示,第一代表性电流对电压曲线与第二代表性电流对电压曲线以零电压为中心彼此呈对称,如粗实线所示。或者,第一代表性电流对电压曲线与第二代表性电流对电压曲线以零电压为中心彼此呈非对称。

41.在静电放电电压ve施加在双极性接面晶体管30上时,双极性接面晶体管30具有一代表性电流对电压曲线,如虚线所示。在静电放电电压ve施加在硅控整流器31上时,硅控整

流器31具有一代表性电流对电压曲线,如细实线所示。双极性接面晶体管30具有较低的崩溃电压、较高的握持电压与较高的箝位电压。硅控整流器31具有较低的崩溃电压、较低的握持电压与较低的箝位电压。结合双极性接面晶体管30与硅控整流器31的特性,在不需要牺牲静电放电耐受度及不会遭受到闩锁(latch-up)事件的前提下设计所需崩溃电压时,双向静电放电保护装置2具有仍然高于欲保护装置的操作电压的较低箝位电压与较低握持电压。具体而言,第一代表性电流对电压曲线具有一第一崩溃电压vb、一第一握持电压vh与一第一箝位电压vc,第二代表性电流对电压曲线具有一第二崩溃电压vb’、一第二握持电压vh’与一第二箝位电压vc’,第一崩溃电压vb、第一握持电压vh与第一箝位电压vc的绝对值分别等于第二崩溃电压vb’、第二握持电压vh’与第二箝位电压vc’的绝对值。双极性接面晶体管30为双向双极性接面晶体管,此即表示当正或负静电放电电压施加在双向双极性接面晶体管上时,双极性接面晶体管30都会具有一崩溃电压、一握持电压与一箝位电压。同样地,硅控整流器31为双向硅控整流器,此即表示当正或负静电放电电压施加在双向硅控整流器上时,硅控整流器31都会具有一崩溃电压、一握持电压与一箝位电压。

42.当正静电放电电压施加在双极性接面晶体管30与硅控整流器31时,第一崩溃电压vb等于双极性接面晶体管30与硅控整流器31的崩溃电压的总和。当负静电放电电压施加在双极性接面晶体管30与硅控整流器31时,第二崩溃电压vb’等于双极性接面晶体管30与硅控整流器31的崩溃电压的总和。当正静电放电电压施加在双极性接面晶体管30与硅控整流器31时,第一握持电压vh等于双极性接面晶体管30与硅控整流器31的握持电压的总和。当负静电放电电压施加在双极性接面晶体管30与硅控整流器31时,第二握持电压vh’等于双极性接面晶体管30与硅控整流器31的握持电压的总和。当正静电放电电压施加在双极性接面晶体管30与硅控整流器31时,第一箝位电压vc等于双极性接面晶体管30与硅控整流器31的箝位电压的总和。当负静电放电电压施加在双极性接面晶体管30与硅控整流器31时,第二箝位电压vc’等于双极性接面晶体管30与硅控整流器31的箝位电压的总和。因此,串联耦接的双极性接面晶体管30与硅控整流器31可以在不需要牺牲静电放电耐受度与遭受到闩锁事件的前提下,设计出所需的崩溃电压,同时达成仍然高于欲保护装置的操作电压的较低的箝位电压与较低的握持电压。

43.图4为本发明的双向静电放电保护装置的第二实施例的结构剖视图。请参照图4,双向静电放电保护装置3还包括一半导体基板34与一隔离结构35。半导体基板34具有第一导电型,半导体基板34上设有一磊晶层36。磊晶层36具有与第一导电型相反的第二导电型。在第二实施例中,第一导电型为n型,第二导电型为p型。双极性接面晶体管30、一第一掺杂阱区310与至少一个第二掺杂阱区311设于磊晶层36中,第一掺杂阱区310与第二掺杂阱区311具有第一导电型。一第一重掺杂区312与一第二重掺杂区313设于第一掺杂阱区310中,第一重掺杂区312与第二重掺杂区313分别具有第二导电型与第一导电型。至少一个第三重掺杂区314与至少一个第四重掺杂区315设于第二掺杂阱区中311。为了清晰度与方便,第二实施例以一个第二掺杂阱区中311、一个第三重掺杂区314与一个第四重掺杂区315为例。第三重掺杂区314与第四重掺杂区315分别具有第一导电型与第二导电型。磊晶层36、第一掺杂阱区310、第二掺杂阱区311、第一重掺杂区312、第二重掺杂区313、第三重掺杂区314与第四重掺杂区315形成硅控整流器31。双极性接面晶体管30经由一外部导线37耦接第一重掺杂区312与第二重掺杂区313。

44.隔离结构35包括绝缘材质。隔离结构35设于磊晶层36中,并位于硅控整流器31与双极性接面晶体管30之间,其中隔离结构35接触半导体基板34,并将硅控整流器31与双极性接面晶体管30隔离。也就是说,隔离结构35与半导体基板34之间呈无结构设置。举例来说,隔离结构35可位于半导体基板34中。换句话说,隔离结构35的底部位置等于或深于磊晶层36的底部位置。此外,隔离结构35可环绕硅控整流器31与双极性接面晶体管30。双极性接面晶体管30可包括至少一个第三掺杂阱区300、至少一个第五重掺杂区301与至少一个第六重掺杂区302。为了清晰度与方便,第二实施例以一个第三掺杂阱区300、一个第五重掺杂区301与一个第六重掺杂区302为例。第五重掺杂区301耦接第一接脚32,第三重掺杂区314与第四重掺杂区315耦接第二接脚33。在第二实施例中,第三掺杂阱区300、第五重掺杂区301与第六重掺杂区302分别为p型掺杂阱区、n型重掺杂区与n型重掺杂区。

45.以下介绍第二实施例的双向静电放电保护装置3的操作过程。当正静电放电电压施加在第一接脚32与第二接脚33时,静电放电电流依序流过第五重掺杂区301、第三掺杂阱区300、第六重掺杂区302、外部导线37、第一重掺杂区312、第一掺杂阱区310、磊晶层36、第二掺杂阱区311与第三重掺杂区314。通过外部导线37的路径称作第一电流路径。介于第五重掺杂区301与第三掺杂阱区300之间的界面与介于第一掺杂阱区310与磊晶层36之间的界面作为崩溃界面。因为介于第五重掺杂区301与第三掺杂阱区300之间的界面的能带间隙小于介于第一掺杂阱区310与磊晶层36之间的界面的能带间隙,所以介于第五重掺杂区301与第三掺杂阱区300之间的界面的崩溃电压低于介于第一掺杂阱区310与磊晶层36之间的界面的崩溃电压。当正静电放电电压施加在第一接脚32与第二接脚33时,静电放电电流亦依序流过第五重掺杂区301、第三掺杂阱区300、磊晶层36、半导体基板34、磊晶层36、第二掺杂阱区311与第三重掺杂区314。通过半导体基板34的路径称作第二电流路径。然而,因为第二电流路径较第一电流路径更长,所以第二电流路径会被压抑,即较少静电放电电流会通过第二电流路径。

46.当负静电放电电压施加在第一接脚32与第二接脚33时,静电放电电流依序通过第四重掺杂区315、第二掺杂阱区311、磊晶层36、第一掺杂阱区310、第二重掺杂区313、外部导线37、第六重掺杂区302、第三掺杂阱区300与第五重掺杂区301。通过外部导线37的路径称作第一电流路径。介于第六重掺杂区302与第三掺杂阱区300之间的界面与介于第二掺杂阱区311与磊晶层36之间的界面作为崩溃界面。因为介于第六重掺杂区302与第三掺杂阱区300之间的界面的能带间隙小于介于第二掺杂阱区311与磊晶层36之间的界面的能带间隙,所以介于第六重掺杂区302与第三掺杂阱区300之间的界面的崩溃电压低于介于第二掺杂阱区311与磊晶层36之间的界面的崩溃电压。当负静电放电电压施加在第一接脚32与第二接脚33时,静电放电电流亦依序通过第四重掺杂区315、第二掺杂阱区311、磊晶层36、半导体基板34、磊晶层36、第三掺杂阱区300与第五重掺杂区301。通过半导体基板34的路径称作第二电流路径。然而,因为第二电流路径较第一电流路径更长,所以第二电流路径会被压抑,即较少静电放电电流会通过第二电流路径。

47.图5为本发明的双向静电放电保护装置的第三实施例的结构剖视图。请参照图5,第三实施例与第二实施例的差异在于第三实施例还包括一重掺杂埋层38,其设于半导体基板34与磊晶层36之间,并设于双极性接面晶体管30与硅控整流器31的下方。重掺杂埋层38具有第二导电型,隔离结构35贯穿重掺杂埋层38。重掺杂埋层38的掺杂浓度大于磊晶层36

的掺杂浓度。

48.当正静电放电电压施加在第一接脚32与第二接脚33时,静电放电电流依序流过第五重掺杂区301、第三掺杂阱区300、磊晶层36、重掺杂埋层38、半导体基板34、重掺杂埋层38、磊晶层36、第二掺杂阱区311与第三重掺杂区314。因为重掺杂埋层38的掺杂浓度大于磊晶层36的掺杂浓度,所以此电流路径会被大幅压抑。换句话说,重掺杂埋层38会大幅压抑此电流路径的电流增益。类似地,当负静电放电电压施加在第一接脚32与第二接脚33时,静电放电电流依序流过第四重掺杂区315、第二掺杂阱区311、磊晶层36、重掺杂埋层38、半导体基板34、重掺杂埋层38、磊晶层36、第三掺杂阱区300与第五重掺杂区301,其中此电流路径也是被大幅压抑。

49.图6为本发明的双向静电放电保护装置的第四实施例的结构剖视图。请参照图6,第四实施例与第二实施例差别在于双极性接面晶体管30。在第四实施例中,第三掺杂阱区300、第五重掺杂区301与第六重掺杂区302可分别为n型掺杂阱区、p型重掺杂区与p型重掺杂区,其余结构已于第二实施例中介绍过,于此不再赘述。介于第三掺杂阱区300与第六重掺杂区302之间的界面与介于第一掺杂阱区310与磊晶层36之间的界面作为崩溃界面。因为介于第三掺杂阱区300与第六重掺杂区302之间的界面的能带间隙小于介于第一掺杂阱区310与磊晶层36之间的界面的能带间隙,所以介于第三掺杂阱区300与第六重掺杂区302之间的界面的崩溃电压小于介于第一掺杂阱区310与磊晶层36之间的界面的崩溃电压。

50.图7为本发明的双向静电放电保护装置的第五实施例的结构剖视图。请参照图7,第五实施例与第三实施例差别在于双极性接面晶体管30。在第五实施例中,第三掺杂阱区300、第五重掺杂区301与第六重掺杂区302可分别为n型掺杂阱区、p型重掺杂区与p型重掺杂区,其余结构已于第三实施例介绍过,于此不再赘述。

51.图8为本发明的双向静电放电保护装置的第六实施例的结构剖视图。第六实施例与第二实施例差别仅在于半导体基板34、磊晶层36、第一掺杂阱区310与第二掺杂阱区311的导电型。第六实施例的第一导电型与第二导电型分别为p型与n型,其余结构已于第二实施例介绍过,于此不再赘述。

52.图9为本发明的双向静电放电保护装置的第七实施例的结构剖视图。第七实施例与第三实施例差别仅在于半导体基板34、磊晶层36、第一掺杂阱区310、重掺杂埋层38与第二掺杂阱区311的导电型。第七实施例的第一导电型与第二导电型分别为p型与n型,其余结构已于第三实施例介绍过,于此不再赘述。

53.图10为本发明的双向静电放电保护装置的第八实施例的结构剖视图。第八实施例与第四实施例差别仅在于半导体基板34、磊晶层36、第一掺杂阱区310与第二掺杂阱区311的导电型。第八实施例的第一导电型与第二导电型分别为p型与n型,其余结构已于第四实施例介绍过,于此不再赘述。

54.图11为本发明的双向静电放电保护装置的第九实施例的结构剖视图。第九实施例与第五实施例差别仅在于半导体基板34、磊晶层36、第一掺杂阱区310、重掺杂埋层38与第二掺杂阱区311的导电型。第九实施例的第一导电型与第二导电型分别为p型与n型,其余结构已于第五实施例介绍过,于此不再赘述。

55.根据上述实施例,双向静电放电保护装置串联耦接双极性接面晶体管与硅控整流器,故在不需要牺牲静电放电耐受度及不会遭受到闩锁(latch-up)事件的前提下设计所需

崩溃电压时,双向静电放电保护装置具有仍比欲保护装置的操作电压更高的较低箝位电压与较低握持电压。

56.以上所述仅为本发明一优选实施例而已,并非用来限定本发明实施的范围,故举凡依本发明权利要求书所述的形状、构造、特征及精神所为的均等变化与修饰,均应包括于本发明的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。