1.本发明是有关于电子电路的数据安全,特别是有关于防止旁通道攻击的方法以及系统。

背景技术:

2.被称为旁通道攻击的各种技术已被开发以从电子装置抽取信息。为了存取储存在装置内的机密信息,旁通道攻击通常由未被授权方执行。一些旁通道攻击利用电子装置通常在逻辑元件变迁时消耗功率的事实。所述攻击通过非侵略性地测量电子信号及/或从装置发射的电磁辐射抽取信息,不需电连接携带信息的所述装置。

3.各种反制对策已被提出以保护电子装置免于旁通道攻击。举例而言,在标题为”hardware level countermeasures against differential power analysis”,2012年2月university of southampton,faculty of physical and applied sciences,school of electronics and computer science的博士论文中,baddam描述数种型态的反制对策,特别是dual rail precharge(drp)电路。

4.美国专利10,521,530描述一种设计逻辑电路的方法,具有使用电子设计自动化系统的数据相关延迟,用以减轻功率分析攻击。所述逻辑电路包含从逻辑输入到至少一个逻辑输出的逻辑通道。所述方法包括获得初始电路设计,为初始电路设计中的多个逻辑路径指定相应的延迟,使得至少一些输出在一个时钟周期中的不同时间切换到不同逻辑输入的组合,以及通过基于所述指定的相应延迟增加延迟元件到初始电路设计,形成第二电路设计,所述第二电路设计在相应的逻辑路径上具有所述指定的相应的延迟。

技术实现要素:

5.在此描述的本发明的一种实施例,提供一种电子电路,包括:驱动单元、至少一个被驱动单元以及至少一个反向器。所述驱动单元包括至少两个输入以及至少一个输出,且被配置以将所述至少一个输出在第一逻辑状态及第二逻辑状态之间切换以回应所述至少两个输入。所述至少一个被驱动单元中的每一个包括至少两个输入,其中所述至少两个输入中至少一个被配置以被所述驱动单元的所述输出所驱动。所述至少一个反向器被设置于一将所述驱动单元连接至所述被驱动单元的信号网络中,所述至少一个反向器被配置以在所述信号网络中平衡第一电容负载以及第二电容负载,其中所述第一电容负载是回应由从所述第一逻辑状态到所述第二逻辑状态的变迁导致的电流,所述第二电容负载是回应由从所述第二逻辑状态到所述第一逻辑状态的变迁导致的电流。

6.通常,所述至少一个反向器被配置以平衡第一电流以及第二电流,所述第一电流在所述信号网络中被消耗以回应所述驱动单元从所述第一逻辑状态到所述第二逻辑状态的变迁,所述第二电流在所述信号网络中被消耗以回应所述驱动单元从所述第二逻辑状态到所述第一逻辑状态的变迁。

7.在一些实施例中,所述第一电容负载以及所述第二电容负载的至少一个接地。在

一些实施例中,所述第一电容负载以及所述第二电容负载的至少一个连接所述电子电路的供应电压轨。

8.在一种实施例中,所述至少一个被驱动单元包括一个被驱动单元,其中所述信号网络包括布线在所述驱动单元的所述输出以及所述被驱动单元的所述输入的至少一个之间的导体,且其中所述至少一个反向器被沿着导体设置。在另一种实施例中,所述至少一个被驱动单元包括多个被驱动单元,其中所述信号网络包括分支,所述分支连接多个被布线到相应的所述被驱动单元的所述输入的导体,且其中所述至少一个反向器包括被设置在所述分支以及所述被驱动单元的所述输入之间的反向器。

9.另外,根据本发明的一种实施例,提供一种设计电子电路的方法。所述方法包括:指定驱动单元,所述驱动单元包括至少两个输入以及至少一个输出,且被配置以将所述至少一个输出在第一逻辑状态及第二逻辑状态之间切换以回应所述至少两个输入。指定至少一个被驱动单元,所述至少一个被驱动单元包括至少两个输入,其中所述至少两个输入中至少一个被所述驱动单元的所述至少一个输出所驱动。在连接所述驱动单元与所述被驱动单元的信号网络中设置至少一个反向器,所述至少一个反向器被设置在所述信号网络中平衡第一电容负载与第二电容负载,所述第一电容负载回应从所述第一逻辑状态到所述第二逻辑状态的变迁导致的电流,所述第二电容负载回应从所述第二逻辑状态到所述第一逻辑状态的变迁导致的电流。

10.在一种实施例中,所述至少一个反向器包括在所述驱动单元与所述被驱动单元之间的给定路径中增加奇数个反向器,以及在所述驱动单元或所述被驱动单元之一个嵌入额外的反向器。

11.另外,根据本发明的一种实施例,亦提供一种在电子电路中的数据处理方法。所述方法包括:使用驱动单元,所述驱动单元包括至少两个输入以及至少一个输出,且被配置以将所述输出在第一逻辑状态及第二逻辑状态之间切换以回应所述至少两个输入。通过所述驱动单元的所述至少一输出驱动至少一个被驱动单元,所述至少一个被驱动单元中的每一个包括至少两个输入,其中所述至少两个输入中至少一个被所述驱动单元的所述至少一输出所驱动。使用至少一个反向器在信号网络中平衡第一电容负载与第二电容负载,所述第一电容负载回应从所述第一逻辑状态到所述第二逻辑状态的变迁导致的电流,所述第二电容负载回应从所述第二逻辑状态到所述第一逻辑状态的变迁导致的电流。

12.由以下对其实施例的详细描述并结合附图,本发明将被更完整地理解。

附图说明

13.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。在附图中:

14.图1为图示描绘根据本发明的一种实施例的包括安全电路以及不安全电路的集成电路(integrated circuit,ic)的方块图。

15.图2~图4为图示描绘根据本发明的一些实施例的具有被平衡的电容负载的电子电路的方块图。

16.图5a及图5b为图示描绘根据本发明的一种实施例的反向器中,

‘0’

到

‘1’

以及

‘1’

到

‘0’

的状态变迁的电路图。

17.图6为图示描绘根据本发明的一种实施例的设计电子电路的方法的流程图。

具体实施方式

18.在此描述的本发明的实施例,提供用以保护电子电路免于旁通道攻击的改良的方法。本技术的技术可以被用于多种形态的安全装置,例如安全嵌入式控制器以及存储装置。

19.在一些实施例中,一种电子电路包含多个逻辑单元,各逻辑单元包括一个或更多输入以及一个或更多输出。各输出通过电导体,例如电路追踪,连接一个或更多其他逻辑单元的一个或更多输入。在各时钟周期中,一些逻辑单元可以从一种逻辑状态变迁其输出到另外一种(

‘0’

到

‘1’

或

‘1’

到

‘0’

)以回应一个或更多其输入的变迁。除非被减轻,否则所述逻辑单元状态变迁的序列可以导致整体电路的电流消耗的变化,其可以被攻击者测量并协助攻击者。

20.这种电流消耗的变化其中一个主要的原因为电容负载在状态变迁期间被充电。电容负载通常包括在电路导体与地之间的电容、在电路导体与供应电压(vdd)之间的电容、在电路导体之间的电容(对其他信号线的电容)、及/或逻辑单元本身的电容。

21.考虑一复杂逻辑单元(即具有多个输入并执行一些逻辑运算以产生输出的逻辑单元),所述复杂逻辑单元的输出驱动一个或更多其他复杂逻辑单元的输入。前者的逻辑单元在此被称为「驱动单元」,后者的逻辑单元被称为「被驱动单元」。将(复杂)驱动单元的输出连接到(复杂)被驱动单元的输入的路径在此被称为「信号网络」。

22.将驱动单元连接到一个或更多被驱动单元的信号网络对地具有特定的电容(或者,更广泛地说,对地的特定电容以及对其他电压源的另一个电容,其他电压源例如供应电压轨(supply voltage rail)或其他信号)。当驱动单元的输出从一个逻辑状态变迁到另一个,驱动单元的输出的电压变迁导致电流流动并对上述电容充电。产生的电流造成电路的总瞬时电流消耗。

23.然而,一般而言,驱动单元的输出由

‘0’

到

‘1’

的变迁导致的电流消耗可能与由

‘1’

到

‘0’

的变迁导致的电流消耗不同。当

‘0’

到

‘1’

的变迁的电流消耗与

‘1’

到

‘0’

的变迁不同,电路的瞬时电流消耗可能表示涉及敏感信息的内部运算。这种不平衡引发了可能被功率分析攻击利用的安全漏洞。

24.在此描述的本发明的一些实施例,提供电路配置以及相关的设计方法,用以减少在电路电流消耗上状态变迁的冲击。在本技术的实施例中,一个或更多额外的反向器被添加到驱动单元以及其被驱动单元之间的信号网络。反向器以平衡因为驱动单元的输出的

‘0’

到

‘1’

的变迁被充电的电容负载以及因为驱动单元的输出的

‘1’

到

‘0’

的变迁被充电的电容负载的方式被添加。若需要,驱动单元及/或被驱动单元的逻辑可以被修改,使额外的反向器不会改变电路的逻辑功能。

25.本技术的技术可以被用以平衡整个电路的电容负载,或电路中操控敏感信息的被选择的部分。以这种方式,电路的瞬时电流消耗可以基本上与正在被处理的敏感信息不相关。因此,本技术的技术减少了电路对功率分析攻击的敏感性。在此描述数个使用本技术的技术的范例电路配置。用以导致设计工具通过插入反向器平衡电容负载的范例设计技术亦

被描述。

26.一种用以减少电路对功率分析攻击的敏感性的可选择的方法,是应用被称为双轨预充电逻辑(dual-rail pre-charge logic,dpl)的技术。在dpl中,电路被平行运作的互补电路保护。每个保护电路的网络在互补电路中具有相应的经历相反状态变迁的网络。因此,在每个时钟周期,无论被处理的数据值如何,由

‘0’

到

‘1’

的变迁的总数与由

‘1’

到

‘0’

的变迁的总数相同。然而,此结果的代价为使硬件加倍,且因此使成本、尺寸以及电路的功率消耗加倍。比起dpl,实施本技术的技术相当简单,且比起硬件加倍,需要的硬件相当少。

27.在一些实施例中,本技术的技术可以被用以实施诸如加密引擎的安全电路,例如先进加密标准(advanced encryption standard,aes)引擎,结合其他减轻功率分析攻击的技术。举例而言,范例技术被公开于美国专利申请号16/741,799,标题为“coupling of combinational logic circuits for protection against side-channel attacks”,以及美国专利申请号16/194,342,标题为“mitigation of side-channel attacks using small-overhead random pre-charging”。这两个专利申请均已让与给本专利申请的受让人,它们的申请内容通过引用并入本文。

28.系统描述

29.图1为图示描绘根据本发明的一种实施例的安全集成电路(integrated circuit,ic)20的方块图。举例而言,安全ic 20可以包括具有集成的加密电路的存储装置、包含加密或验证电路的嵌入式控制器(embedded controller,ec)或基板管理控制器(baseboard management controller,bmc),或任何其他合适的安全电子装置。

30.虽然在本例中非必要,ic 20包含不安全电路24以及安全电路28两个。举例而言,安全电路28可以包括加密引擎或任何其他需要被保护以免于旁通道攻击的电路。不安全电路24可以包括任何保护是没那么重要的电路。

31.在本例中,不安全电路24包括驱动单元32以及被驱动单元36。为了清楚起见,图1仅描绘一个驱动单元,一个被驱动单元,以及一个在它们之间的网络。实际上,电路24通常包括一起实现逻辑功能的大量的单元,例如乘法器、aes s盒(s-box)或任何其他合适的逻辑功能。

32.驱动单元32以及被驱动单元36两个皆为复杂逻辑单元,即具有多个输入(与缓冲器以及反向器相反,举例而言)。驱动单元32包括多个输入40以及一输出44。被驱动单元36包括多个输入,其中一个输入48被驱动单元32的输出44驱动。驱动单元32以及被驱动单元36之间的信号网络包括电路追踪,其对地电容表示为c。

33.信号网络的电容c作为被驱动单元32的输出44的电容负载。在此例中,在输出44从

‘0’

到

‘1’

的变迁的期间被充电的电容,以及在输出44从

‘1’

到

‘0’

的变迁的期间被充电的电容之间没有平衡。因此,输出44的

‘0’

到

‘1’

的变迁以及

‘1’

到

‘0’

的变迁的电流消耗会逐渐不同。

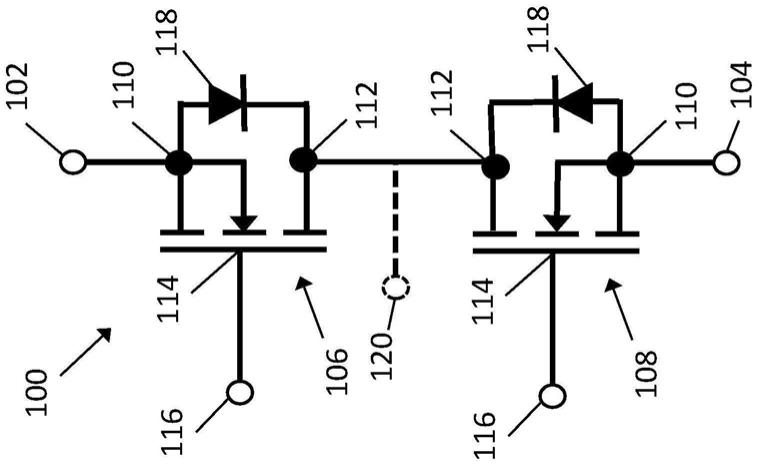

34.在图1的范例中的安全电路28包括驱动单元52以及被驱动单元56。此处也为了清楚起见,仅描绘一个驱动单元,一个被驱动单元,以及一个在它们之间的网络。实际上安全电路28通常包括互相驱动的大量的单元。

35.驱动单元52包括多个输入60以及一输出64。被驱动单元56包括多个输入,其中一个输入68被驱动单元52的输出64驱动。为了防止电容负载的不平衡,额外的反向器72被设

置于输出64以及输入68之间的网络。设置得当时,反向器72之前(以c1表示)的信号网络的电容部分,与反向器72之后(以c2表示)的信号网络的电容部分相同。

36.用这个方式设置反向器72平衡了输出64由

‘0’

到

‘1’

的变迁导致的电流消耗以及输出64由

‘1’

到

‘0’

的变迁导致的电流消耗。

37.考量输出64由

‘0’

到

‘1’

的变迁。在此变迁中,输出64的电压从代表逻辑

‘0’

的电压变迁为代表逻辑

‘1’

的电压。此电压变迁导致特定电流流经电容c1。此电流以i(

‘0’

到

‘1’

,c1)表示,且为代表

‘0’

和

‘1’

的电压以及电容c1的函数。输出64由

‘0’

到

‘1’

的变迁在反向器72引发相反的变迁,即

‘1’

到

‘0’

。反向器72的输出的电压因此从代表逻辑

‘1’

的电压变迁为代表逻辑

‘0’

的电压。此电压变迁导致特定电流流经电容c2。此电流以i(

‘1’

到

‘0’

,c2)表示,且为代表

‘0’

和

‘1’

的电压以及电容c2的函数。

38.现在考量输出64的反向变迁,从

‘1’

到

‘0’

。在此变迁中,输出64的电压从代表逻辑

‘1’

的电压变迁为代表逻辑

‘0’

的电压。此电压变迁导致特定电流流经电容c1。此电流以i(

‘1’

到

‘0’

,c1)表示,且为代表

‘0’

和

‘1’

的电压以及电容c1的函数。输出64由

‘1’

到

‘0’

的变迁在反向器72引发相反的变迁,即

‘0’

到

‘1’

。反向器72的输出的电压因此从代表逻辑

‘0’

的电压变迁为代表逻辑

‘1’

的电压。此电压变迁导致特定电流流经电容c2。此电流以i(

‘0’

到

‘1’

,c2)表示,且为代表

‘0’

和

‘1’

的电压以及电容c2的函数。

39.假设在输出64由

‘0’

到

‘1’

变迁期间的信号网络中的总电流消耗为i(

‘0’‑

to

‑‘1’

)=i(

‘0’‑

to

‑‘1’

,c1) i(

‘1’‑

to

‑‘0’

,c2),且总假设在输出64由

‘1’

到

‘0’

变迁期间的信号网络中的总电流消耗为i(

‘1’‑

to

‑‘0’

)=i(

‘1’‑

to

‑‘0’

,c1) i(

‘0’‑

to

‑‘1’

,c2)。可以看到弱c1=c2,则i(

‘0’‑

to

‑‘1’

)=i(

‘1’‑

to

‑‘0’

)。因此,当电容负载被反向器72平衡,信号网络中的总电流消耗与状态变迁的方向不相关(即与输出64从

‘1’

到

‘0’

或从

‘0’

到

‘1’

变迁不相关)。

40.在上述描述中,电流消耗的完美平衡被证明是通过电容负载的完美平衡而达成。可以理解的是,在特定实施例中,电容c1和c2之间可能会保留一些剩余差异。尽管如此,此剩余差异通常足够小,因此允许有效地减轻安全电路28上的功率分析攻击,也可以结合其他反制对策。在本专利申请的内容以及权利要求中,诸如「被平衡的电容」、「被平衡的电容负载」以及「被平衡的电流消耗」表示电容、电容负载或电流消耗的剩余差异低于被认为足以有效缓解攻击的预先定义的阈值。

41.具有被平衡的电容负载的可选择的网络设计

42.图2~图4为图示描绘根据本发明的可选择的实施例的具有被平衡的电容负载的电子电路的方块图。

43.在图2中,两个反向器72被设置于驱动单元52的输出以及驱动单元56的输入之间的网络。在此实施例中,当驱动单元52的输出状态变迁时,表示为c3及c5的电容被往一个方向(从

‘0’

到

‘1’

或从

‘1’

到

‘0’

)驱动,且表示为c4的电容被往反方向(相应地,从

‘1’

到

‘0’

或从

‘0’

到

‘1’

)。因此,为了在电容负载中达成平衡,电容必须满足c4=c3 c5的条件。

44.图3描绘驱动单元52的输出被分为两支并用以平行驱动两个被驱动单元56的输入的情况。在此例中,被分为两支前的信号网络的电容以c6表示,被分为两支后的两个分支的电容以c7、c8表示。两个反向器72被设置在信号网络中,在所述分支与被驱动单元的输入之间邻接所述分支。在此情况下,为了在电容负载中达成平衡,电容必须满足c6=c7 c8的条

件。在一个可选择的实施例中,一个反向器可以被设置在分支之前(在驱动单元的输出与分支之间,在c6之后,邻接所述分支)以替代图中琐事的两个反向器。

45.图4描绘信号网络对地和电压轨vdd都具有电容的情况。一个反向器72被设置于信号网络中。在反向器之前的部分的电容以c01(对地)以及c11(对vdd)表示。在反向器之后的部分的电容以c02(对地)以及c12(对vdd)表示。在此情况下,为了在电容负载中达成平衡,电容必须满足c11 c02=c01 c12的条件。

46.图5a及图5b为图示描绘根据本发明的一种实施例的反向器72中的状态变迁的电路图。在本例中,反向器72包括以p表示的p型金属氧化物半导体场效电晶体(p-type metal-oxide-semiconductor field-effect transistor,pmos fet)以及以n表示的n型金属氧化物半导体场效电晶体(nmos fet),在vdd与地之间以源极到汲极的方式连接。反向器72的输入被施加到两个电晶体的闸极。反向器72的输出取自p型电晶体的源极和n型电晶体的汲极之间的连接点。

47.图5a描绘输出和地之间的电容负载(表示为c0)的情况。图5b描绘输出和电源电压(vdd)之间的电容负载(表示为c1)的情况。在两个图中,标示「0

→

1」的箭头描绘在输出由

‘0’

到

‘1’

变迁之期间的电流,标示「1

→

0」的箭头描绘在输出由

‘1’

到

‘0’

变迁的期间的电流。多数实际情形包括两种情况的叠加。

48.在图5a及图5b中可以看到,电流消耗并非对称。举例而言,在图5a中,从vdd到地的电流只在由

‘0’

到

‘1’

变迁的期间流经。在由

‘1’

到

‘0’

变迁的期间,电流大致从一个电容极流向另一个,且不必到达地。设置电容以满足上述图4的条件平衡了由

‘0’

到

‘1’

的变迁及由

‘1’

到

‘0’

的变迁的电流消耗。

49.多种电子电路的配置显示于图1~图4,图5a及图5b为仅为概念的清晰而描绘的范例配置。在可选择的实施例中,可以使用任何其他合适的电路配置。举例而言,可以使用图1~图4中的配置的任何合适的组合。

50.作为另一个例子,在上述例子中,驱动单元以及被驱动单元为三输入or或nor单元。然而,这样的选择仅为了举例。在可选择的实施例中,任何驱动单元以及被驱动单元可以包括任何其他具有两个或更多输入以及一个或更多输出的合适的逻辑单元,例如多种or、and、nor、nand以及xor门。

51.再者,作为另一个例子,在给定的驱动单元以及给定的被驱动单元之间设置的反向器72的数量不限于一个或两个,可以包含任何合适的数量。作为另一个例子,驱动单元的输出可以分为为多于两个分支,以驱动多于两个被驱动单元。一般而言,被驱动单元可以彼此不同,及/或与驱动单元不同,以适于执行电路需要的逻辑功能。

52.在多种实施例中,任何本技术的电路可以使用任何合适的硬件或固件实施,例如使用一个或更多离散元件,一个或更多特殊应用集成电路(application specificintegrated circuit,asic)及/或一个或更多现场可程式化逻辑门阵列(fieldprogrammable gate array,fpga)。

53.用以达成被平衡的电容负载的设计方法

54.在一些实施例中,根据本发明实施例的安全电路,例如显示于图1~图4的例子,可以使用现有的超大型集成电路(very-large-scale integration,vlsi)设计工具设计并处理。设计的范例准则可以包括下列内容:

55.诱导合成程序使用小尺寸逻辑单元,例如使用后接反向器的nor单元代替or单元。

56.限制最大变迁时间,以诱导转换器的插入。

57.避免使用缓冲器,并使用反向器代替(或将已存在的替换为一对反向器)。

58.使用驱动强度低的单元,以诱导转换器的插入。

59.诱导合成程序以避免在输出级使用具有多余反向器的单元(例如and、or以及缓冲器),并使用相应的更简单的版本替代(例如nand、mor、反向器)。这会强迫合成程序以外部反向器完善逻辑,其稍后可以被用于平衡电容。

60.若在驱动单元以及被驱动单元之间没有反向器,可以明确地添加一对串联连接的反向器在需要保护的网络上。

61.作为设计的后端阶段的一部分,平衡反向器的位置。

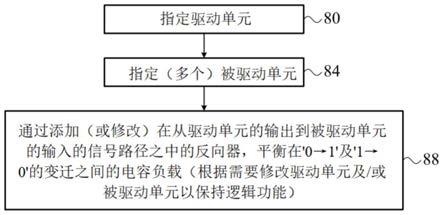

62.图6为图示描绘根据本发明的一种实施例的设计电子电路的方法的流程图。所述方法从设计者或设计工具在驱动单元指定步骤80指定驱动单元开始。在被驱动单元指定步骤84,设计者或设计工具指定一个或更多由驱动单元驱动的被驱动单元。

63.如本文所阐述的,在平衡步骤88,设计者或设计工具添加或修改一个或更多在驱动单元与被驱动单元的信号网络中的反向器。添加或修改反向器可以用多种方式执行。举例而言,在一些情况中,修改现有的反向器便已充足,例如调整一个或更多现有反向器的大小,或改变一个或更多现有反向器在网络中的位置。作为另一个例子,可以通过以另一个逻辑门取代现有逻辑门添加反向器,例如以nor门取代or门,反之亦然,或以nand门取代and门,反之亦然。再者,作为另一个例子,额外的反向器可以被嵌入被驱动单元的输入,从而保证只插入一个反向器。

64.须留意的是,一般而言,若在驱动单元以及被驱动单元之间的路径添加奇数个反向器,驱动单元或被驱动单元之一个需要被修改以维持正确的电路功能。所述修改通常包括在驱动单元的输出或在被驱动单元的输入嵌入额外的反向器。

65.图6的流程可以实施于整个电子电路,例如ic或部分需要额外保护的电路。

66.在一些实施例中,本技术的设计技术,例如图6的方法,可以由通用电脑执行,所述通用电脑以软体编程以执行本文所述的功能。举例而言,软体可以被以电子形式从网络下载到电脑中,或者也可以选择性地或额外地被提供及/或储存于非暂时性有形媒体,例如磁性、光学或电子存储器。

67.虽然本文的实施例主要解决在状态变迁中平衡电容负载,本文所述的方法及系统也可以被使用于其他应用,例如在数据不改变的情况(静止数据)下平衡电容负载。在这样的应用中,要被平衡的参数为在逻辑

‘0’

的漏电流与在逻辑

‘1’

的漏电流。

68.因此,应理解上述实施例仅作为示例引用,本发明不限于上文中特别显示及描述的内容。更确切地说,本发明的范围包括实施例以及上文所述的多种特征的子组合,还有本领域的通常知识者在阅读前述内容想到的未公开于先前技术的变化及修改。以引用方式并入本专利申请中的文件应被视为本技术的组成部分,除非在这些并入文件中,以和本说明书中明确或隐含的定义冲突的方式定义的任何术语,仅应考虑本说明书中的定义。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。