1.本发明涉及晶圆处理用粘结膜,应用于晶圆加工,例如,晶圆背磨等工序。更具体地,本发明涉及如下的晶圆处理用粘结膜,即,具有在晶圆处理工序中防止半导体芯片产生碰撞的优秀效果。

2.并且,本发明涉及在晶圆粘附有粘结膜的晶圆粘结膜组件。

背景技术:

3.最近,随着技术的发展,逐渐需求半导体芯片的小型化及薄型化。

4.作为芯片薄型化的代表一例有通过研磨形成芯片的晶圆背面来减少厚度的方法。

5.最近,可通过晶背面研磨(dbg,dicing before grinding)方法来获得薄型化的芯片,利用切割钻刃在晶圆的表面形成凹槽后,在晶圆的背面进行研磨来从晶圆获得划片化的芯片。在使用晶圆背面研磨方法的情况下,由于同时进行晶圆的背面研磨及晶圆的划片化,因此,可有效制造薄型化的半导体芯片。

6.通常,当进行晶圆的背面研磨时,为了维持半导体芯片,需在使粘结膜附着于晶圆表面的状态下执行晶圆的背面研磨。这种粘结膜包含用于粘结基材和晶圆表面的粘结剂层,可在基材背面形成有具备缓冲效果的缓冲层或减振层,例如,氨基甲酸乙酯丙烯酸酯。

7.在由氨基甲酸乙酯丙烯酸酯形成缓冲层或减振层的情况下,通过能量射线固化形成。在这种能量射线固化方式中,由于包含具有双键的官能基的高分子形成一个大分子,因此,存在因模量增加而导致缓冲效果降低的缺点。

技术实现要素:

8.技术问题

9.本发明的目的在于,提供防芯片碰撞效果优秀的晶圆处理用粘结膜。

10.并且,本发明的另一目的在于,提供适用于背面研磨工序等晶圆处理的晶圆粘结膜组件。

11.本发明所要实现的技术目的并不局限于以上提及的目的,本发明所属技术领域的普通技术人员可通过以下内容明确理解未提及的其他目的。

12.技术方案

13.为了实现上述目的,本发明实施例的晶圆处理用粘结膜包括:多层基材;以及第一粘结剂层,配置在上述多层基材的上表面。上述多层基材形成第二粘结剂层设置于上部基材层与下部基材层之间的夹层式结构,上述下部基材层及上部基材层具有1000mpa以上的模量,上述第二粘结剂层具有10mpa以下的模量。

14.上述下部基材层和上部基材层分别可包含选自由聚对苯二甲酸乙二醇酯、聚萘二甲酸乙二醇酯、聚对苯二甲酸丁二醇酯、全芳香族聚酯、聚酰亚胺、聚酰胺、聚碳酸酯、聚缩醛、改性聚苯醚、聚苯硫醚、聚砜、聚醚酮及双向拉伸聚丙烯组成的组中的一种以上。

15.上述下部基材层及上部基材层的材质可以为聚对苯二甲酸乙二醇酯(pet)。

16.上述第二粘结剂层的玻璃化转变温度可以为10℃以下。

17.上述第二粘结剂层可包含热固性丙烯酸类粘结剂。

18.上述第二粘结剂层可具有100μm以下的厚度。

19.在上述上部基材层的上表面、上述上部基材层的下表面及上述下部基材层的上表面中的至少一面还可额外形成有底漆层。

20.为了实现上述目的,在本发明实施例的晶圆粘结膜组件中,可在形成有多个半导体芯片的晶圆的表面粘附有如上所述的粘结膜。

21.发明的效果

22.本发明的晶圆处理用粘结膜可包括多层基材,上述多层基材为夹层式结构,第二粘结剂层设置于多个基材层之间,上述基材层具有1000mpa以上的高模量,上述第二粘结剂层具有10mpa以下的低模量。在晶圆背磨等晶圆处理工序中,具有1000mpa以上的高模量的多个基材层提供用于支撑晶圆的充分模量。并且,低模量的第二粘结剂层可进一步有效减少在晶圆背磨等晶圆处理工序中由高模量的多个基材层所传递的冲击,因此,可防止产生半导体芯片的碰撞并防止产生裂纹。

23.并且,当第二粘结剂层具有10mpa以下的低模量和10℃以下的低玻璃化转变温度时,可提供较高的冲击减少效果。

24.并且,当第二粘结剂层具有10mpa以下的低模量和100μm以下的厚度时,可防止在晶圆背面研磨等晶圆处理工序中产生粘结膜的变形或第二粘结膜的脱离。

附图说明

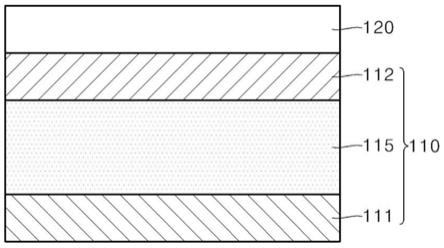

25.图1为简要示出本发明实施例的晶圆处理用粘结膜的剖视图。

26.图2为简要示出本发明另一实施例的晶圆处理用粘结膜的剖视图。

27.附图标记的说明

28.110:基材

29.111:下部基材层

30.112:上部基材层

31.113:底漆层

32.115:第二粘结剂层

33.120:第一粘结剂层。

具体实施方式

34.本发明的目的、特定优点及新特征可通过与附图相关的详细说明和优选实施例而变得更加明确。本说明中的“一面”、“另一面”“双面”等术语仅用于对一个结构要素和其他结构要素进行区分,结构要素并不限定于上述术语。以下,在说明本发明的过程中,将省略有可能不必要地混淆本发明的主旨的有关公知技术的详细说明。

35.以下,参照附图,针对本发明的晶圆处理用粘结膜进行详细说明。

36.在本发明中,晶圆处理不仅包括晶圆背磨工序,而且,可包括切割工序、划片化半导体芯片的拾取工序等。

37.图1为简要示出本发明实施例的晶圆处理用粘结膜的剖视图。

38.参照图1,本发明的晶圆处理用粘结膜可包括:多层基材110;以及第一粘结剂层120,配置在多层基材的上表面。

39.多层基材

40.多层基材110包括下部基材层111、上部基材层112及第二粘结剂层115。第二粘结剂层115配置在下部基材层111与上部基材层112之间。在本发明的晶圆处理用粘结膜中,多层基材形成第二粘结剂层115配置在下部基材层111与上部基材层112之间的夹层式结构。

41.下部基材层111和上部基材层112可由高模量的材质制成。更具体地,下部基材层111及上部基材层112具有1000mpa以上的模量,例如,可具有1200mpa以上、1500mpa以上、2000mpa以上、3000mpa以上的模量。模量以23℃测定值为基准。本发明的特征在于,在粘结晶圆的一侧,上部基材层112及下部基材层111均由高模量的材料制成。

42.当上部基材层112及下部基材层111的模量相对较低时,换言之,在小于1000mpa的情况下,可因晶圆或划片化的半导体芯片的支撑力降低而导致在背面研磨工序中有可能产生半导体芯片的碰撞。但是,本发明可提供如下效果:通过高模量的下部基材层111及上部基材层112来充分提高晶圆或划片化的半导体芯片的支撑力,并且,可防止在晶圆背面研磨等晶圆处理工序中产生半导体芯片的碰撞。

43.并且,当下部基材层111及上部基材层112的模量相对较高时,在向粘结膜附着晶圆或从晶圆粘结膜剥离晶圆或半导体芯片的情况下,可减少晶圆或半导体芯片所受到的应力。

44.下部基材层111及上部基材层112分别可包含由聚对苯二甲酸乙二醇酯(pet)、聚萘二甲酸乙二醇(pen)、聚对苯二甲酸丁二醇酯(pbt)、全芳香族聚酯等聚酯、聚酰亚胺(pi)、聚酰胺(pa)、聚碳酸酯(pc)、聚缩醛、改性聚苯醚、聚苯硫醚、聚砜、聚醚酮、双向拉伸聚丙烯(oriented poly-propylene)组成的组中的一种以上。

45.优选地,下部基材层111和上部基材层112的材质可相同。作为一例,上述下部基材层111及上部基材层112可以为聚对苯二甲酸乙二醇酯(pet)材质。由于聚对苯二甲酸乙二醇酯(pet)可具有1000mpa以上的模量,因此,非常适用于下部基材层111及上部基材层112。

46.下部基材层111及上部基材层112的模量可调节,例如,在合成聚对苯二甲酸乙二醇酯的过程中,可通过减少共聚合成分中的乙烯成分的含量来提高基材层的模量。

47.虽然下部基材层111及上部基材层112可具有相同厚度,但并不限定于此。下部基材层111及上部基材层112可分别具有约10μm~150μm的厚度。另一方面,在本发明中,虽然下部基材层111及上部基材层112具有较高的模量,但是,当下部基材层111及上部基材层112的厚度相对较厚时,尤其,若上部基材层112的厚度太厚,则难以抵挡在背面研磨等晶圆处理过程中产生的冲击。因此,优选地,下部基材层111及上部基材层112的厚度应定为150μm以下。

48.另一方面,下部基材层111和/或上部基材层112可包含少量的各种添加剂,例如,偶联剂、可塑剂、防静电剂、抗氧化剂等。

49.第二粘结剂层

50.在本发明中,第二粘结剂层115的模量为10mpa以下。作为一例,满足这种条件的第二粘结剂层115可由热固性丙烯酸类粘结剂制成。可通过将包含树脂及热固化剂的组合物进行热固化来制备热固性丙烯酸类粘结剂。

51.通常的能量射线聚合性氨基甲酸乙酯丙烯酸酯减振层因能量射线固化而导致层整体由一个巨大高分子形成,因此,具有较高的模量,这种高模量有可能阻碍减振。相反,应用于本发明的第二粘结剂层115可由热固性丙烯酸类粘结剂制成,由于具有10mpa以下的低模量,因此,可具有更优秀的减振能力。另一方面,第二粘结剂层115的模量或玻璃化转变温度可基于树脂的组成、固化剂的含量等而变得不同。

52.例如,在热固性丙烯酸类粘结剂中,树脂可以为丙烯酸酯化合物。可用于热固性丙烯酸类粘结剂的丙烯酸酯化合物有(甲基)丙烯酸酯、具有4个以上碳原子的(甲基)丙烯酸烷基酯、非氨基甲酸乙酯类多官能(甲基)丙烯酸酯等。

53.可用于热固性丙烯酸类粘结剂的固化剂有异氰酸酯类交联剂、碳二亚胺类交联剂、恶唑啉类交联剂、环氧类交联剂、氮丙啶类交联剂、过氧化物等。相对于100重量份的树脂,固化剂的含量可达到0.1重量份~2重量份,但并不限定于此。

54.在本发明中,下部基材层111及上部基材层112具有1000mpa以上的高模量,可通过在其多个基材层之间形成10mpa以下的低模量的第二粘结剂层115来充分发挥减振功能。例如,随着因在晶圆背面研磨工序中产生的压缩及前端应力而导致多个半导体芯片产生振动或移动,多个半导体芯片可相互碰撞。但是,本发明可通过在高模量的下部基材层111和上部基材层112之间形成低模量的第二粘结剂层115来减少冲击,从而可防止这种半导体芯片产生碰撞。

55.如上所述,第二粘结剂层115具有10mpa以下的模量,优选为0.01mpa以上且5mpa以下,更优选地,可具有0.05mpa以上且5mpa以下的模量。当第二粘结剂层的模量大于10mpa时,由于缓冲效果很差,因而会因无法缓冲在进行研磨的过程中通过高模量的基材传递的冲击,因此,有可能在晶圆产生裂纹并难以防止芯片碰撞。另一方面,当上述第二粘结剂层的模量小于0.01mpa时,由于粘结剂的固化度过于低下,因此,随着粘结剂因在晶圆背磨时的热量和压力而流入到晶圆,可使得晶圆受到污染并导致加工后的晶圆的厚度精准度不佳。

56.另一方面,上述第二粘结剂层115可具有100μm以下的厚度。例如,当第二粘结剂层的厚度大于100μm时,随着低模量的第二粘结剂层因晶圆背磨时粘结膜受到的应力而产生变形,可导致维持在粘结膜上的芯片产生移动,或者,有可能因处理时的冲击而导致第二粘结剂层产生分离。即,可导致研磨后的厚度均匀度不佳。因此,优选地,第二粘结剂层的厚度应为100μm以下,更优选地,可以为5μm~70μm。

57.并且,上述第二粘结剂层115的玻璃化转变温度(tg)可以为10℃以下,优选地,玻璃化转变温度可达到-40℃~10℃之间,更优选地,玻璃化转变温度可达到-35℃~10℃之间,最优选地,玻璃化转变温度可达到-30℃~8℃之间。这种第二粘结剂层可通过低玻璃化转变温度而具备强力的粘结力,最终,当研磨时,即使在从常温到最高90℃的温度条件下执行晶圆背磨,也可防止产生第一基材与第二基材分离的现象。但是,当玻璃化转变温度过于低下时,即,在小于-40℃的情况下,随着粘结剂因晶圆背磨时的热量和压力而流入到晶圆,可导致晶圆受到污染。

58.第一粘结剂层

59.图1所示的第一粘结剂层120为与晶圆粘结的部分。

60.对于第一粘结剂层120并无特别限制,只要在常温条件下具备适当粘结性即可,可

应用多种粘结剂,例如,公知的紫外线(uv)粘结剂等。

61.对于第一粘结剂层120的厚度并无特别限制,例如,可以为10μm~100μm。

62.图2为简要示出本发明另一实施例的晶圆处理用粘结膜的剖视图。

63.参照图2,在多层基材的上部基材层112的上表面还可额外包含底漆层113。这种底漆层113可用于提高第一粘结剂层120与多层基材110之间的附着力。

64.底漆层113形成在上部基材层112的上表面,即,可在形成第一粘结剂层120的一面形成单独的层。作为另一例,底漆层113可通过上部基材层112的上表面的改性而成。

65.作为一例,虽然图2示出底漆层113形成在上部基材层112的上表面,但是,本发明并不限定于此,底漆层也可形成在上部基材层112的下表面或下部基材层111的上表面。

66.晶圆的处理可在将本发明的粘结膜附着在晶圆表面的状态下执行。

67.以下,针对晶圆背面研磨工序的例进行说明。首先,通过激光切割、等离子切割等方式在粘结有本发明的粘结膜的晶圆中形成槽或改性区域。这可在晶圆表面中进行,也可在背面中进行。随后,通过研磨工序执行晶圆背磨并基于槽或改性区域划片成多个芯片,从而剥离粘结膜。

68.实施例

69.以下,为了进一步帮助理解本发明,将公开优选实施例。但是,以下实施例仅用于理解本发明而提供,本发明的内容并不限定于以下实施例。

70.1.第二粘结剂层用粘结树脂的制备

71.向配置有冷却管、氮气引入管、温度计及搅拌器的反应容器放入120份的乙酸乙酯,并通过将装置内部的空气置换成氮气来使得其内部不含氧气后,将容器的内部温度提升至75℃。将0.05份的偶氮二异丁腈(聚合引发剂)全部添加于溶解5份的乙酸乙酯的溶液后,维持74℃~76℃的内部温度,同时,向反应体系滴加具有表1所示的组成成分的单体混合物2小时。并且,通过在内部温度为74℃~76℃的条件下维持5小时来完成反应。最后,通过添加乙酸乙酯来调节(甲基)丙烯酸类树脂的浓度变为40%,从而制备树脂。

72.测定所制备的树脂的重均分子量(mw)、数均分子量(mn)及玻璃化转变温度(tg)。所制备的树脂的分子量(mw及mn)可通过如下方法进行。在gpc装置(模型名称:agilent-1200)中串联配置柱,在使用四氢呋喃作为洗脱液、试样浓度为5mg/ml、试样导入量为100μl、温度为40℃、流速为1ml/分钟的条件下,基于标准聚苯乙烯换算进行测定。

73.所制备的树脂的玻璃化转变温度(tg)可通过如下方法进行,在测定温度范围为-80℃~50℃及升温速度为10℃/分钟的条件下,利用ta instruments公司的动态机械分析仪q-800装置进行测定。用于制备第二粘结剂层的单体混合物的单体组成成分(重量百分比)、所制备的树脂的重均分子量(mw)、分子量分布(mw/mn)及玻璃化转变温度(tg)如表1所示。

74.表1

[0075][0076][0077]

ba:丙烯酸正丁酯

[0078]

eha:丙烯酸2-乙基己酯

[0079]

ma:甲基丙烯酸酯

[0080]

hea:丙烯酸2-羟乙酯

[0081]

aa:丙烯酸

[0082]

2.粘结膜的制备

[0083]

通过在表3所记载的上部基材与下部基材之间涂敷粘结剂组合物并进行热固化来第二粘结剂层,上述粘结剂组合物包含表2所示的组成成分。

[0084]

表2

[0085] 树脂1树脂2树脂3固化剂添加剂填充剂实施例1100

ꢀꢀ2ꢀꢀ

实施例2100

ꢀꢀ1ꢀꢀ

实施例3 100 2

ꢀꢀ

实施例4

ꢀꢀ

1000.30.1 实施例5 100 2

ꢀꢀ

比较例1 100 1

ꢀꢀ

比较例2

ꢀꢀ

1000.3

ꢀꢀ

比较例3100

ꢀꢀ

1 20

[0086]

在表2中,作为固化剂使用了u-cat 5003(san apro制造),作为添加剂使用了kbm-403(shinyetsu制造)环氧硅烷偶联剂,作为填充剂使用了sfp-30m(平均粒径为0.7μm)(电化学工业有限公司制造)二氧化硅。

[0087]

随后,通过相同的紫外线粘结剂在上部基材的上表面形成第一粘结剂层来制备多个粘结膜样品。

[0088]

3.粘结膜的背面研磨特性评估

[0089]

在所制备的多个粘结膜粘结包含320个半导体芯片的晶圆后,在相同条件下执行研磨,随后,针对研磨后的晶圆厚度均匀度、是否浸入有沉淀物及芯片角龟裂特性进行评估。

[0090]

表3中的针对研磨后厚度均匀度及是否浸入有沉淀物的评估在以下条件下执行。

[0091]

a:研磨后的晶圆的厚度偏差小于10μm

[0092]

b:研磨后的晶圆的厚度偏差大于10μm

[0093]

c:未产生沉淀物浸入

[0094]

d;产生沉淀物浸入

[0095]

表3

[0096][0097]

参照表3,在上部基材及下部基材的模量为1000mpa以上且第二粘结剂层的模量为10mpa以下的实施例1至实施例5的试片中,产生芯片角龟裂相对较少。相反,在基材的模量小于1000mpa的比较例1及比较例2的试片及在第二粘结剂层的模量为10mpa以上的比较例3的试片中,产生芯片角龟裂相对较多。

[0098]

并且,在实施例1至实施例5中,实施例1至实施例3的试片在研磨后的厚度均匀度评估层面上具有尤为优秀的特性。即,相比于第二粘结剂层的模量为0.005mpa的实施例4及第二粘结剂层的厚度大于100μm的实施例的试片,实施例1至实施例3中的试片在研磨后的厚度均匀度评估层面上具有相对优秀的特性。

[0099]

如上所述,本发明的晶圆处理用粘结膜包括多层基材,上述多层基材形成低模量的第二粘结剂层设置于多个基材层之间的夹层式结构。可通过高模量的多个基材层提供充分模量来获得防止在晶圆背磨等晶圆处理工序中产生芯片碰撞的效果,并且,可通过低模量的第二粘结剂层来提供充分的缓冲效果。

[0100]

以上,虽然说明了本发明,但是,本发明并不限定于本说明书中所公开的实施例,显而易见的是,本发明所属技术领域的普通技术人员可在本发明的技术思想范围内进行多种修改。并且,应当理解的是,即使在说明本发明实施例的过程中未明确说明的本发明结构的作用效果也包含可通过相应结构进行预测的效果。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。