1.本发明属于集成电路技术领域技术领域,特别涉及一种线性稳压模组及片上系统。

背景技术:

2.稳压器模组,例如低压差线性稳压器(low dropout regulator,ldo),因其结构简单、速度快、所需元件少、易于集成的特点,被广泛应用于芯片的电源管理系统中。

3.无片外电容的低压差线性稳压器不需要外接芯片外部的电容器件,可以节省芯片引脚,在很多芯片引脚数目紧张的设计中具有很大的优势。

4.然而,目前无片外电容的低压差线性稳压器仍存在问题,例如适应的负载电流和负载电容范围比较小,且往往对负载电流的快速瞬态变化响应较差。

技术实现要素:

5.本发明的目的在于提供一种线性稳压模组及片上系统,可适应大的负载电流范围和负载电容范围,可快速响应负载电流的瞬态变化,且输出精度受工艺偏差、电源纹波、温度变化的影响很小。

6.为实现上述目的,本发明提供了一种线性稳压模组,包括:

7.电压输出单元,依据基准偏置电压,并通过调节串联的电阻的大小,获取第一输出电压;

8.电压钳位单元,将线性稳压模组输出端的输出电压钳位至第一输出电压;以及

9.反馈单元,依据所述输出端的负载,快速动态调整反馈环路。

10.在本发明一实施例中,所述电压输出单元包括:

11.误差放大器,其正向输入端输入所述基准偏置电压,

12.第一晶体管,其源极电性连接供电电压端,漏极输出第一输出电压,栅极电性连接于所述误差放大器的输出端;以及

13.分压电阻,电性连接于所述第一晶体管的漏极和所述误差放大器的负向输入端。

14.在本发明一实施例中,所述电压输出单元还包括:

15.第一电容,一端电性连接于所述第一晶体管的漏极;以及

16.第一电阻,一端电性连接于所述第一电容,另一端电性连接于所述第一晶体管的栅极。

17.在本发明一实施例中,所述电压钳位单元包括:

18.电压钳位晶体管,所述电压钳位晶体管的源极电性连接于所述第一晶体管的漏极,所述电压钳位晶体管的栅极和漏极连接,且所述电压钳位晶体管的漏极通过电流镜结构电性连接于接地端;以及

19.第一共栅放大管,所述第一共栅放大管的源极为输出端,所述第一共栅放大管的栅极电性连接于所述电压钳位晶体管的栅极,且所述第一共栅放大管的漏极通过电流镜结

构电性连接于接地端;所述第一共栅放大管的栅源电压等于所述电压钳位晶体管的栅源电压。

20.在本发明一实施例中,所述第一共栅放大管的宽长比wl

m11

与所述电压钳位晶体管的宽长比wl

m7

的关系为:wl

m11

:wl

m7

=9:1。

21.在本发明一实施例中,所述电流镜结构中包括多个晶体管,其中一个晶体管电性连接在电压钳位晶体管和接地端之间,另一个晶体管电性连接在第一共栅放大管和接地端之间。

22.在本发明一实施例中,所述电流镜结构中,电性连接在电压钳位晶体管和接地端之间的晶体管的宽长比wl

m8

,与电性连接在第一共栅放大管和接地端之间的晶体管的宽长比wl

m12

的关系为:wl

m12

:wl

m8

=10:1。

23.在本发明一实施例中,所述反馈单元包括:

24.第一共栅放大管,所述第一共栅放大管的源极为输出端;

25.第二共栅放大管,所述第二共栅放大管的源极电性连接于所述第一共栅放大管的漏极,且所述第二共栅放大管的漏极通过一晶体管电性连接于供电电压端;

26.共源输出管,所述共源输出管的栅极电性连接于所述第二共栅放大管的漏极,所述共源输出管的源极电性连接于供电电压端,所述共源输出管的漏极为输出端;

27.第二电容,一端电性连接于共源输出管的栅极,另一端电性连接于接地端,以及

28.第三电容,一端电性连接于共源输出管的栅极,另一端电性连接于所述第二共栅放大管的源极。

29.在本发明一实施例中,共源输出管的栅极到输出端的增益为:

30.a

vef

=-g

m24

/g

m11

;

31.其中,a

vef

为共源输出管的栅极到输出端的增益,g

m24

为共源输出管的跨导,g

m11

为第一共栅放大管的跨导。

32.在本发明一实施例中,共源输出管的栅极到第三电容与所述第二共栅放大管的源极连接点的增益为:

33.a

vec

=-(g

m24

/g

m11

)*(g

m11

/g

m22

)=-g

m24

/g

m22

;

34.其中,a

vec

为共源输出管的栅极到第三电容与所述第二共栅放大管的源极连接点的增益,g

m24

为共源输出管的跨导,g

m11

为第一共栅放大管的跨导,g

m22

为第二共栅放大管的跨导。

35.在本发明一实施例中,所述反馈单元环路的开环增益为:

36.a

open

=-(g

m24

/g

m11

)*(g

m11

/g

m22

)*g

m22r019

=-g

m24r019

;

37.其中,a

open

为所述反馈单元环路的开环增益,g

m24

为共源输出管的跨导,g

m11

为第一共栅放大管的跨导,g

m22

为第二共栅放大管的跨导,r

019

为连接所述第二共栅放大管的漏极和供电电压端的晶体管的小信号输出电阻。

38.在本发明一实施例中,所述线性稳压模组还包括栅端偏置电压单元,所述栅端偏置电压单元组成所述第二共栅放大管的端偏置电压产生电路。

39.在本发明一实施例中,所述栅端偏置电压单元包括:

40.第一偏置电压产生晶体管,所述第一偏置电压产生晶体管的栅极电性连接于所述第二共栅放大管的栅极,且所述第一偏置电压产生晶体管的栅源电压等于所述第二共栅放

大管的栅源电压;以及

41.第二偏置电压产生晶体管,所述第二偏置电压产生晶体管的栅极和漏极电性连接于所述第一偏置电压产生晶体管的源极,所述第二偏置电压产生晶体管的源极电性连接于所述电压钳位晶体管的源极,且所述第二偏置电压产生晶体管的栅源电压等于所述电压钳位晶体管的栅源电压。

42.在本发明一实施例中,所述线性稳压模组还包括:

43.两个晶体管,所述晶体管两个的漏极电性连接于供电电压端,源极电性连接于接地端;

44.第四电阻,电性连接于所述两个晶体管的栅极之间;以及

45.第四电容,一端电性连接于第四电阻的一端,另一端电性连接于输出端。

46.本发明还提供一种片上系统,包括如上所述的一种线性稳压模组。

47.综上所述,本发明提供的一种线性稳压模组及片上系统,包括依据基准偏置电压,并通过调节串联的电阻的大小,获取第一输出电压的电压输出单元,将线性稳压模组输出端的输出电压钳位至第一输出电压的电压钳位单元;以及依据所述输出端的负载,快速动态调整反馈环路的反馈单元,可提高负载电流范围和负载电容范围,可适应大的负载电流范围和负载电容范围,可快速响应负载电流的瞬态变化,且输出精度受工艺偏差、电源纹波、温度变化的影响很小。

附图说明

48.为了更清楚地说明本发明实施例的技术方案,下面将对实施例描述所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

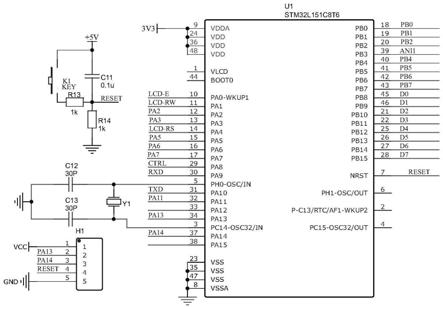

49.图1是本发明中一种片上系统的结构框图。

50.图2是本发明中一种线性稳压模组的线路图。

51.附图标记说明:

52.101微处理器模块;102存储器模块;103外部通讯接口模块;104电源管理模块;c1第一电容;c2第二电容;c3第三电容;c4第四电容;c5第五电容;c6第六电容;m1第一晶体管;m2第二晶体管;m3第三晶体管;m4第四晶体管;m5第五晶体管;m6第六晶体管;m7电压钳位晶体管;m8第八晶体管;m9第九晶体管;m10第十晶体管;m11第十一晶体管;m12第十二晶体管;m13第十三晶体管;m14第十四晶体管;m15第十五晶体管;m16第十六晶体管;m17第十七晶体管;m18第十八晶体管;m19第十九晶体管;m20第二十晶体管;m21第二十一晶体管;m22第二十二晶体管;m23第二十三晶体管;m24第二十四晶体管;m25第二十五晶体管;r1第一电阻;r2第二电阻;r3第三电阻;r4第四电阻;基准电流源iref;vcc供电电压端;gnd接地端;v

ref

基准偏置电压;vout输出端的输出电压。

具体实施方式

53.为了便于理解本技术,下面将参照相关附图对本技术进行更全面的描述。附图中给出了本技术的较佳实施方式。但是,本技术可以以许多不同的形式来实现,并不限于本文

所描述的实施方式。相反地,提供这些实施方式的目的是使对本技术的公开内容理解的更加透彻全面。

54.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施方式的目的,不是旨在于限制本技术。

55.在本发明的描述中,需要理解的是,术语中“中心”、“上”、“下”、“前”、“后”、“左”、“右”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或组件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性。

56.请参阅图1所示,在电子产品中,芯片已经成为不可缺少的核心元件,特别是随着集成电路制造工艺越来越先进,片上系统(system on chip,soc)在尽可能有限的芯片面积集成了更复杂的功能。所述片上系统包括微处理器模块101、嵌入式的存储器模块102、外部通讯接口模块103以及电源管理模块104。因便携类电子产品大多使用锂电池作为其外围电源供电,且锂电池电压的范围在2.6v-3.6v内,不能直接给低压模块直接供电,则需要在电源管理模块104中设置多个低压差线性稳压模组将锂电池的输出电压转换为低电压,为芯片内的多个模块供电。在本实施例中,电源管理模块104中包括微处理器模块101供电的线性稳压模组ldo1,为存储器模块102供电的线性稳压模组ldo2,为外部通讯接口模块103供电的线性稳压模组ldo3,且所述线性稳压模组例如为无片外电容的低压差线性稳压模组。

57.很多低压差线性稳压模组的输出端需要有一个微法级别的外挂电容,来应对负载电流进行的动态响应,但这会增加芯片引脚数量,进而导致芯片的集成度下降,且会增加芯片外围成本。部分无片外电容的低压差线性稳压模组对负载电流的快速瞬态响应较差,且适应的负载电流和负载电容的范围较小。本发明提供一种线性稳压模组,具有宽负载适应范围,可适应较大的负载电流和负载电容范围,且对快速瞬态变化的负载电流响应较良好,输出精度受工艺偏差、电源纹波以及温度变化的影响很小。

58.请参阅图2所示,在本发明一实施例中,所述线性稳压模组包括电压输出单元、电压钳位单元、反馈单元以及栅端偏置电压单元。电压输出单元可依据基准偏置电压,并通过调节串联的电阻的大小,获取第一输出电压,电压钳位单元可将线性稳压模组输出端的输出电压钳位至第一输出电压,反馈单元可依据输出端的负载,快速动态调整反馈环路,栅端偏置电压单元可使得输出端的输出电压更加准确的钳位至第一输出电压。

59.请参阅图2所示,在本发明一实施例中,电压输出单元依据提供的基准偏置电压v

ref

,并通过调节串联的电阻,获取第一输出电压,即图2中a点位的电压。具体的,电压输出单元包括第一晶体管m1、第二晶体管m2、第三晶体管m3、第四晶体管m4、第五晶体管m5和第六晶体管m6,以及第一电阻r1、第二电阻r2、第三电阻r3和第一电容c1。其中,在本实施例中,第二晶体管m2、第三晶体管m3、第四晶体管m4、第五晶体管m5和第六晶体管m6组成误差放大器,以降低调节误差,提高控制系统的灵敏度。且在本实施例中,第一晶体管m1、第二晶体管m2和第三晶体管m3为n型mos管,第四晶体管m4、第五晶体管m5和第六晶体管m6为p型mos管。

60.具体的,请参阅图2所示,在本发明一实施例中,第一晶体管m1的源极电性连接于

供电电压端vcc,漏极为第一输出电压的输出端。第二晶体管m2和第三晶体管m3的源极电性连接于供电电压端vcc,第二晶体管m2和第三晶体管m3的栅极相互连接,且第二晶体管m2的栅极电性连接于第二晶体管m2的漏极。第二晶体管m2的漏极还电性连接于第四mos的漏极,第三晶体管m3的漏极电性连接于第五晶体管m5的漏极。第四晶体管m4的源极和第五晶体管m5的源极电性连接,且第四晶体管m4的源极和第五晶体管m5的源极通过第六晶体管m6电性连接于接地端gnd。更具体的,第四晶体管m4的源极和第五晶体管m5的源极电性连接于第六晶体管m6的漏极,第六晶体管m6的源极电性连接于接地端gnd。在本实施例中,第四晶体管m4的栅极电性连接于分压电阻,相当于误差放大器的负向输入端电性连接于分压电阻。第五晶体管m5的栅极电性连接于基准偏置电压v

ref

,相当于误差放大器的正向输入端电性连接于基准偏置电压v

ref

。其中,基准偏置电压v

ref

例如由带隙基准模块提供,不会受到工艺偏差、电源纹波和温度变化的影响。因而a点位的第一输出电压的精度不受工艺偏差、电源纹波和温度变化的影响。

61.请参阅图2所示,在本发明一实施例中,第一晶体管m1的栅极电性连接于第三晶体管m3的漏极与第五晶体管m5的漏极连接处,相当于第一晶体管m1的栅极电性连接于误差放大器的输出端。分压电阻包括第一电阻r1和第二电阻r2,第一电阻r1与第二电阻r2串联,且第一电阻r1的一端电性连接于第一晶体管m1的漏极,即第一输出电压的输出端,第二电阻r2电性连接于接地端gnd,第四晶体管m4的栅极电性连接于第一电阻r1和第二电阻r2的连接处。其中,第一电阻r1和第二电阻r2可以由多个电阻串联而成。可通过调节第一电阻r1和第二电阻r2的大小,可调节第一输出电压的大小。且在本技术中,第一输出电压的大小为:

[0062]va

=v

ref

×

(1 r1/r2);

[0063]

其中,va为第一输出电压,v

ref

为基准偏置电压,r1为第一电阻r1,r2为第二电阻r2。

[0064]

请参阅图2所示,在本发明一实施例中,在第一晶体管m1的栅极和漏极之间,还设置有第一电容c1和第三电阻r3。第一电容c1和第三电阻r3串联,第一电容c1的一端电性连接于第一晶体管m1的漏极,第三电阻r3的另一端电性连接于第一晶体管m1的栅极。串联在第一晶体管m1的栅极和漏极之间的第一电容c1和第三电阻r3可补偿电压输出单元中反馈环路的相位裕度,以保证电压输出单元的稳定性。

[0065]

请参阅图2所示,在本发明一实施例中,电压钳位单元包括多个晶体管,可将输出端的输出电压vout钳位至第一输出电压。在本技术中,电压钳位单元包括第七晶体管m7(电压钳位晶体管)、第八晶体管m8、第十一晶体管m11(第一共栅放大管)和第十二晶体管m12。其中,第八晶体管m8、第十二晶体管m12与第九晶体管m9、第十晶体管m10、第六晶体管m6构成电流镜结构,将流经第七晶体管m7和第十一晶体管m11的电流限定为相同大小,使得第十一晶体管m11的栅源极电压等于第七晶体管m7的栅源极电压,进而将输出端的输出电压vout钳位至第一输出电压。在本实施例中,第七晶体管m7和第十一晶体管m11为n型mos管,第八晶体管m8、第九晶体管m9、第十晶体管m10和第十二晶体管m12为p型mos管。

[0066]

具体的,请参阅图2所示,在本发明一实施例中,第七晶体管m7的源极电性连接于a点位,漏极电性连接于第八晶体管m8的漏极,栅极电性连接于第十一晶体管m11的栅极,且第七晶体管m7的栅极和漏极电性连接。第八晶体管m8的源极电性连接于接地端gnd,栅极电性连接于第六晶体管m6的栅极。第十一晶体管m11的源极电性连接于输出端,漏极电性连接于第十二晶体管m12的漏极,栅极电性连接于第七晶体管m7的栅极。第十二晶体管m12的源

极电性连接于接地端gnd,栅极电性连接于第六晶体管m6的栅极。第九晶体管m9的源极和第十晶体管m10的源极电性连接于接地端gnd,第九晶体管m9的栅极和第十晶体管m10的栅极连接连接,且第九晶体管m9栅极和源极电性连接,且第九晶体管m9的漏极通过第十三晶体管m13电性连接于供电电压端vcc,第十晶体管m10的漏极通过第十四晶体管m14和第十五晶体管m15电性连接于供电电压端vcc。则第八晶体管m8、第九晶体管m9、第十晶体管m10和第十二晶体管m12与第六晶体管m6构成电流镜。

[0067]

请参阅图2所示,在本发明一实施例中,所述线性稳压模组还设置有基准电流单元,可用于调整电路中的电流大小。基准电流单元例如包括基准电流源iref、第十六晶体管m16、第十七晶体管m17、第十八晶体管m18和第十九晶体管m19。其中,第十六晶体管m16、第十七晶体管m17、第十八晶体管m18和第十九晶体管m1为n型mos管,第十三晶体管m13和第十四晶体管m14也为n型mos管。

[0068]

请参阅图2所示,在本发明一实施例中,基准电流源iref与第十六晶体管m16串联,且第十六晶体管m16的源极电性连接于供电电压端vcc,漏极电性连接于栅极和基准电流源iref的一端,基准电流源iref的另一端电性连接于接地端gnd。第十七晶体管m17的源极电性连接于供电电压端vcc,漏极通过第二十晶体管m20电性连接于接地端gnd,第十七晶体管m17的栅极电性连接于第十六晶体管m16的栅极和第十三晶体管m13的栅极,使得第十六晶体管m16、第十七晶体管m17和第十三晶体管m13构成电流镜。第十八晶体管m18的源极电性连接于供电电压端vcc,漏极通过第二十一晶体管m21电性连接于接地端gnd,栅极电性连接于漏极。第十九晶体管m19的源极电性连接于供电电压端vcc,漏极通过第二十二晶体管m22电性连接于第十一晶体管m11和第十二晶体管m12的连接处,第十九晶体管m19的栅极电性连接于第十八晶体管m18的栅极和第十四晶体管m14的栅极,使得第十八晶体管m18、第十九晶体管m19和第十四晶体管m14构成电流镜。

[0069]

请参阅图2所示,在本发明一实施例中,将第十二晶体管m12的宽长比定义为wl

m12

,将第八晶体管m8的宽长比定义为wl

m8

,将wl

m12

:wl

m8

设置为10:1,则第八晶体管m8的漏端电流i8的关系为i

12

:i8=10:1。将第八晶体管m8的漏端电流i8设置为i,则第十二晶体管m12的漏端电流i

12

为10i,与第八晶体管m8只有一条通路的第七晶体管m7的漏端电流i7也为i。可通过基准电流单元将流经第十九晶体管m19的漏端电流i

19

设置为i,则与第十九晶体管m19只有一条通路的第二十二晶体管m22的漏端电流i

22

也为i。第二十二晶体管m22的漏端电流i

22

和第十一晶体管m11的漏端电流i

11

之和等于第十二晶体管m12的漏端电流i

12

,则第十一晶体管m11的漏端电流为9i。将第十一晶体管m11的宽长比定义为wl

m11

,第七晶体管的宽长比定义为wl

m7

,则wl

m11

:wl

m7

=9:1。此时,第十一晶体管m11的栅源电压v

gs11

等于第七晶体管的栅源电压v

gs7

,可将输出端的输出电压vout钳位到a点位的第一输出端电压。

[0070]

请参阅图2所示,在本发明一实施例中,为方便描述将第七晶体管m7和第八晶体管m8的连接处定义为b点位,将第十一晶体管m11和第十二晶体管m12的连接点处定义为c点位。

[0071]

请参阅图2所示,在本发明一实施例中,所述反馈单元包括第十一晶体管m11、第二十二晶体管m22、第二十四晶体管m24、第二电容c2和第三电容c3。其中,第二十二晶体管m22为p型mos管,第二十四晶体管m24为n型mos管。第二十二晶体管m22的源极电性连接于第十一晶体管m11的漏极,即c点位,漏极电性连接于第十九晶体管m19的漏极和第二十四晶体管

m24的栅极,栅极电性连接于第十五晶体管m15的栅极。第二十四晶体管m24的源极电性连接于供电电压端vcc,漏极为输出端。在本实施例中,将第二十四晶体管m24的栅极定义为e点位,将第二十四晶体管m24的漏极定义为f点位。第二电容c2的一端电性连接于e点位,另一端电性连接于接地端gnd,作为反馈单元的补偿电容。第三电容c3的一端电性连接于e点位,另一端电性连接于c点位,作为反馈单元的补偿电容,且为反馈单元的密勒补偿电容。

[0072]

请参阅图2所示,在本实施例中,第二十四晶体管m24作为共源输出管,为负载提供电流,第十一晶体管m11和第二十二晶体管m22作为共栅放大管,第十一晶体管m11例如定义为第一共栅放大管,第二十二晶体管m22例如定义为第二共栅放大管。则c点位、f点位和e点位的小信号输出电阻分别为:

[0073]

rc=r

012

‖g

m22-1

(1 r

019

/r

022

)‖g

m11r011r024

=g

m22-1

。

[0074]

其中,rc为c点位的小信号输出电阻rc,r

012

为第十二晶体管m12的小信号输出电阻,g

m22

为第二十二晶体管m22的跨导,r

019

为第十九晶体管m19的小信号输出电阻,r

022

为第二十二晶体管m22的小信号输出电阻,g

m11

为第十一晶体管m11的跨导,r

011

为第十一晶体管m11的小信号输出电阻,r

024

为第二十四晶体管m24的小信号输出电阻。

[0075]

rf=r

024

‖(g

m11-1

(1 (r

012

‖g

m22-1

(1 r

019

/r

022

))/r

011

))=g

m22-1

。

[0076]

其中,rf为f点位的小信号输出电阻,r

024

为第二十四晶体管m24的小信号输出电阻,g

m11

为第十一晶体管m11的跨导,r

012

为第十二晶体管m12的小信号输出电阻,g

m22

为第二十二晶体管m22的跨导,r

019

为第十九晶体管m19的小信号输出电阻,r

022

为第二十二晶体管m22的小信号输出电阻,r

011

为第十一晶体管m11的小信号输出电阻。

[0077]

re=r

019

‖g

m22r022

(r

012

‖g

m11r011r024

)=r

019

。

[0078]

即c点位的小信号输出电阻rc约等于第二十二晶体管m22的跨导的倒数g

m22-1

,输出节点f点位的小信号输出电阻rf约等于第十一晶体管m11的跨导的倒数g

m15-1

,主极点节点e点位的小信号输出电阻re约等于第十九晶体管m19的小信号输出电阻r

019

。

[0079]

请参阅图2所示,在本实施例中,节点e作为主极点,位于环路内部,不在输出节点,所以可以适应比较大范围的负载电容,最小可以为0。节点c和节点f作为次极点。且节点e到节点f的增益为:

[0080]avef

=-g

m24

/g

m11

。

[0081]

其中,g

m24

为共源输出管的跨导,g

m11

为第一共栅放大管的跨导。

[0082]

节点e到节点c的增益为:

[0083]avec

=-(g

m24

/g

m11

)*(g

m11

/g

m22

)=-g

m24

/g

m22

。

[0084]

其中,g

m24

为共源输出管的跨导,g

m11

为第一共栅放大管的跨导,g

m22

为第二共栅放大管的跨导。

[0085]

环路的开环增益为:

[0086]aopen

=-(g

m24

/g

m11

)*(g

m11

/g

m22

)*g

m22r019

=-g

m24r019

。

[0087]

其中,g

m24

为共源输出管的跨导,g

m11

为第一共栅放大管的跨导,g

m22

为第二共栅放大管的跨导,r

019

为连接所述第二共栅放大管的漏极和供电电压端的晶体管的小信号输出电阻,即第十九晶体管的的小信号输出电阻。

[0088]

在本实施例中,因为g

m11

》》g

m22

,所以a

vef

》》a

vec

。本发明提供的无片外电容的低压差线性稳压模组可以适应比较宽的负载电流范围,最小可以到0,最大可以到几十毫安。当负

载电流很大时,g

m24

会比较大,所以a

vec

也会比较大,此时密勒补偿电容第三电容c3可以起到很好的环路相位裕度补偿效果。当负载电流较小时,g

m24

会比较小,所以a

vec

也会比较小,此时密勒补偿电容第三电容c3无法起到良好的环路相位裕度补偿效果,但是由于g

m24

比较小,同样会导致环路开环增益a

open

比较小,此时第二电容c2就可以满足环路相位裕度的补偿要求。通过第二电容c2和密勒补偿电容第三电容c3的相互配合,可以满足从很小负载电流到很大负载电流范围的环路相位裕度要求。

[0089]

请参阅图2所示,在本发明一实施例中,在第二十晶体管m20和第二十一晶体管m21之间还设置有第四电容c4和第四电阻r4。其中,第二十晶体管m20和第二十一晶体管m21为p型mos管。且第四电阻r4的一端电性连接于第二十晶体管m20的栅极,另一端电性连接于第二十一晶体管m21的栅极。第四电阻r4的一端电性连接于第二十一晶体管m21的栅极,另一端电性连接于输出端。第四电容c4和第四电阻r4形成左半平面零点zero

lhp

,且左半平面零点为:

[0090]

zero

lhp

=-g

m24

/(10g

m21

c4r4 g

m11

c4r4)=-1/c4r4。

[0091]

其中,g

m24

为第二十四晶体管m24的跨导,g

m21

为第二十一晶体管m21的跨导,g

m11

为第十一晶体管m11的跨导,c4为第四电容c4的容值,r4为第四电阻r4的阻值。

[0092]

请参阅图2所示,当负载电流发生快速瞬态变化,无片外电容的低压差线性稳压模组可以迅速响应改变输出管第二十四晶体管m24的输出电流,避免无片外电容的低压差线性稳压模组输出电压出现大的纹波。当负载电流快速升高时,输出电压vout会被拉低,导致第十一晶体管m11的电流减小,导致c点位的电压vc下降,导致第二十二晶体管m22的电流增大,进而导致输出管第二十四晶体管m24的栅端电压被拉低,输出电流变大,避免输出电压vout进一步降低。当负载电流快速降低时,输出电压vout会被抬高,导致第十一晶体管m11的电流增大,导致c点位的电压vc升高,导致第二十二晶体管m22的电流减小,进而导致输出管第二十四晶体管m24的栅端电压被抬高,输出电流变小,避免输出电压vout进一步升高。进而可实现反馈环路的快速动态调整。

[0093]

请参阅图2所示,在本发明一实施例中,为保证输出端的输出电压vout的输出更加准确,需保证b点位和c点位的电压在不同工艺偏差、电源纹波以及温度变化下保持一致,则设置有栅端偏置电压单元,形成第二十二晶体管m22的栅端偏置电压产生电路。

[0094]

请参阅图2所示,在本发明一实施例中,栅端偏置电压单元包括第十晶体管m10、第十四晶体管m14、第十五晶体管m15和第二十三晶体管m23。其中,第十晶体管m10和第十五晶体管m15为p型mos管,第十四晶体管m14和第二十三晶体管m23为n型mos管,与第十晶体管m10形成电流镜的第九晶体管m9也为p型mos管。可将第十五晶体管m15定义为第一偏置电压产生晶体管,第二十三晶体管m23定义为第二偏置电压产生晶体管。其中第十四晶体管m14、第十五晶体管m15和第十晶体管m10串接,并连接在供电电压端vcc和接地端gnd之间,第二十三晶体管m23的一端电性连接于a点位,另一端电性连接于第十五晶体管m15和第十晶体管m10的连接点。具体的,第十四晶体管m14的源极电性连接于供电电压端vcc,漏极电性连接于第十五晶体管m15的漏极,栅极电性连接于第十九晶体管m19的栅极。第十五晶体管m15的漏极与栅极连接,且电性连接于第二十二晶体管m22的栅极。第十五晶体管m15的源极电性连接于电性连接于第十晶体管m10的漏极,第十晶体管m10的源极电性连接于接地端gnd。第二十三晶体管m23的源极电性连接于a点位,漏极与栅极连接,并电性连接于第十五晶体

管m15的栅极。在本实施例中,为方便描述,将第二十三晶体管m23的漏极、栅极与第十五晶体管m15的栅极的连接点定义为d点位。

[0095]

请参阅图2所示,在本发明一实施例中,将第二十三晶体管m23的宽长比定义为wl

m23

,将wl

m23

:wl

m7

设置为1:1。将第十五晶体管m15的宽长比定义为wl

m15

,将第二十二晶体管m22的宽长比定义为wl

m22

,且将wl

m15

:wl

m22

设置为1:1。将第十四晶体管m14的漏端电流i

14

与第八晶体管m8的漏端电流i8设置为i

14

=i8=i,则第十五晶体管m15的漏端电流i

15

=i

14

=i。将第十晶体管m10的漏端电流i

10

设置为i

10

=2i,则第二十三晶体管m23的漏端电流i

23

=i

10-i

15

=2i-i=i。且第七晶体管m7的漏端电流i7与第八晶体管m8的漏端电流i8的关系为i7=i8=i,则第二十二晶体管m22的宽长比wl

m22

等于第十五晶体管m15的宽长比wl

m15

,第二十二晶体管m22的漏端电流i

22

等于第十五晶体管m15的漏端电流i

15

。第二十三晶体管m23的宽长比wl

m23

等于第七晶体管m7的宽长比wl

m7

,第二十三晶体管m23的漏端电流i

23

等于第七晶体管m7的漏端电流i7。则第二十二晶体管m22的栅源电压v

gs22

等于第十五晶体管m15的栅源电压v

gs15

,第二十三晶体管m23的栅源电压v

gs23

等于第七晶体管m7的栅源电压v

gs7

。则b点位的电压vb和c点位的电压vc的差值为:

[0096]vb-vc=v

b-vd v

d-vc=v

gs7-v

gs23

v

gs22-v

gs15

=0。

[0097]

即可保证b点位的电压vb等于c点位的电压vc,使得b点位和c点位的电压在不同工艺偏差、电源纹波以及温度变化下保持一致。

[0098]

请参阅图2所示,在本发明一实施例中,在输出端和接地端gnd之间还设置有第五电容c5和第二十五晶体管,以响应负载的变化。其中,第二十五晶体管为p型mos管,第二十五晶体管的漏极电性连接于输出端,源极电性连接于接地端gnd,栅极电性连接于第六晶体管的栅极。在第七晶体管的栅极和供电电压端vcc之间还设置有第六电容c6。

[0099]

请参阅图2所示,本技术提供的线性稳压模组示例中,供电电压端的电压为3v,输出端的输出电压为1.6v,可适应0-100pf负载电容,可提供0-20ma输出电流,直流输出精度为

±

20mv,对于负载电流发生10ma,20ns的台阶瞬态变化,输出电压纹波小于

±

70mv。需要说明的是,本技术中每个电气元件的规格选择,可依据供电电压端的电压以及输出端的电压灵活设置。

[0100]

综上所述,本发明提供的所述线性稳压模组可适应大的负载电流和负载电容范围、能迅速响应负载电流的快速瞬态变化、输出精度受工艺偏差、电源纹波以及温度变化变化影响很小,可解决现有的无片外电容的低压差线性稳压模组适应负载范围小,对负载电流快速瞬态变化响应差的问题。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。