1.本发明公开了一种故障分析用的半导体试片的制备方法,且特别是关于一种利用材料黏着度差异以制备失效分析用的半导体试片的方法。

背景技术:

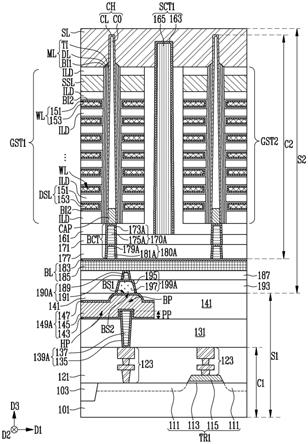

2.已知故障分析用的半导体试片的制备方法,通常必须逐层去层(delayer),以提供故障分析用的半导体试片。如图1a~1b所示的已知一种故障分析用的半导体试片的制备方法,其步骤包括首先提供一如图1a所示的半导体样品10,前述半导体样品10包括一半导体组件100、一连接前述半导体组件100的金属接触层180、一第一介电层170覆盖前述半导体组件100及前述金属接触层180、一导线层185,形成于前述第一介电层170上,并且连接前述金属接触层180,以电性连接前述半导体组件100,以及一第二介电层200,覆盖前述导线层185上,前述半导体组件100例如包括一半导体基板110、一闸极120、一闸极氧化层130、一源极140及一汲极160。然后,如图1b所示般,使用人工研磨并搭配化学蚀刻液去除前述第二介电层200及前述导线层185,使金属接触层180部分裸露,以利缺陷处的寻找或后续的故障分析。如图1a~1b所示的已知一种故障分析用的半导体试片的制备方法,由于使用人工研磨并搭配化学蚀刻液去除前述第二介电层200及前述导线层185,对于尺寸较大的半导体样品而言,由于介电层较厚,较不会在使用人工研磨并搭配化学蚀刻液去除前述第二介电层200的过程中使半导体组件100受到损害。然而,随着半导体制程尺寸逐渐缩小化,介电层的厚度越来越小,使用人工研磨并搭配化学蚀刻液以进行去层处理时,可能会使半导体样品10内的半导体组件100受到损害,如图1b所示因为蚀刻液在研磨过程中经由故障点渗漏而造成第一介电层170被蚀刻出露出闸极120表面或汲极160表面的缺陷通道190、195,或者造成金属接触层180被蚀刻破坏,导致无法完成故障分析用的半导体试片的制备。

3.有鉴于此,一种不会损害半导体样品内的半导体组件的故障分析用的半导体试片的制备方法乃目前半导体业界所殷切期盼。

技术实现要素:

4.本发明公开一种故障分析用的半导体试片的制备方法,其特征在于,包括以下步骤:提供一半导体样品,前述半导体样品包括一半导体组件、一金属接触层、一第一介电层、一导线层以及一第二介电层,其中前述金属接触层连接前述半导体组件,前述第一介电层覆盖前述半导体组件及前述金属接触层,前述导线层是形成于前述第一介电层上,且藉由连接前述金属接触层以电性连接前述半导体组件,且前述第二介电层是覆盖于前述导线层上;对前述半导体样品施一研磨处理,以邻近前述金属接触层与前述导线层间的界面为研磨终点,逐渐研磨去除前述第二介电层及前述导线层;形成一黏着层于研磨处理过的前述半导体样品表面,前述黏着层对前述第一介电层的附着力大于前述黏着层对前述金属接触层的附着力;以及固化前述黏着层后,剥离前述黏着层,使部分前述第一介电层连同前述黏着层一起被剥除,并使部分前述金属接触层裸露出来。

5.前述的故障分析用的半导体试片的制备方法,其中前述第一、第二介电层为相同或相异介电材料所构成。

6.前述的故障分析用的半导体试片的制备方法,其中前述第一、第二介电层为相同介电材料所构成,且前述介电材料主要为氧化硅。

7.前述的故障分析用的半导体试片的制备方法,其中前述研磨处理步骤为人工研磨或机械研磨。

8.前述的故障分析用的半导体试片的制备方法,其中前述黏着层为胶层、胶带或蜡层。

9.前述的故障分析用的半导体试片的制备方法,其中前述胶层或胶带包含一非挥发性且非液态的黏着材料。

10.前述的故障分析用的半导体试片的制备方法,其中前述非挥发性且非液态的黏着材料为硅胶。

11.前述的故障分析用的半导体试片的制备方法,其中前述黏着层的厚度介于50~100微米。

12.前述的故障分析用的半导体试片的制备方法,其中前述黏着层的固化步骤为常温固化、加热固化或照光固化。

附图说明

13.图1a~1b所绘示的剖面制程示意图为已知一种故障分析用的半导体样品的制备方法。

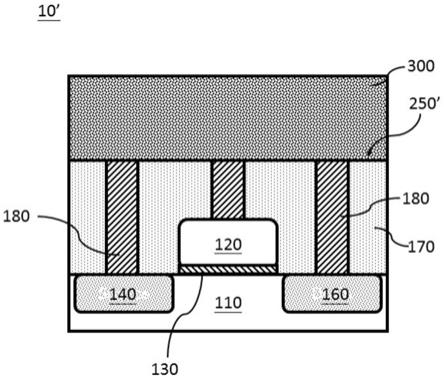

14.图2a~2d所绘示的剖面制程示意图为为根据本发明实施例所揭示的一种故障分析用的半导体样品的制备方法。

15.其中,附图中符号的简单说明如下:

16.10半导体样品

17.10’研磨处理过的半导体样品

18.20故障分析用的半导体试片

19.100半导体组件

20.110半导体基板

21.120闸极

22.130闸极氧化层

23.140源极

24.160汲极

25.170第一介电层

26.180金属接触层

27.185导线层

28.190、195缺陷通道

29.200第二介电层

30.250金属接触层与导线层间的界面

31.250’研磨处理过的半导体样品10’的表面

32.300黏着层

具体实施方式

33.为了使本发明公开内容更加详尽与完备,下文针对了本发明的实施态样与具体实施例提出了说明性的描述;但这并非实施或运用本发明具体实施例的唯一形式。以下所揭露的各实施例,在有益的情形下可相互组合或取代,也可在一实施例中附加其它的实施例,而无须进一步的记载或说明。

34.在以下描述中,将详细叙述许多特定细节以使读者能够充分理解以下的实施例。然而,可在无此等特定细节的情况下实践本发明的实施例。在其他情况下,为简化图式,熟知的结构与装置仅示意性地绘示于图中。

35.实施例

36.请参阅图2a~2d,其所绘示的剖面制程示意图为为根据本发明实施例所揭示的一种故障分析用的半导体样品的制备方法。

37.首先,如图2a所示,提供一半导体样品,前述半导体样品包括一半导体样品10,前述半导体样品10包括一半导体组件100、一金属接触层180、一第一介电层170、一导线层185以及一第二介电层200,其中前述金属接触层180连接前述半导体组件100,前述第一介电层170覆盖前述半导体组件100及前述金属接触层180,前述导线层185是形成于前述第一介电层170上,且藉由连接前述金属接触层180以电性连接前述半导体组件100,且前述第二介电层200是覆盖于前述导线层185上,前述半导体组件100例如但不限于包括一半导体基板110、一闸极120、一闸极氧化层130、一源极140及一汲极160。其中,在根据本发明此实施例中,前述第一、第二介电层170、200为相同介电材料所构成,例如但不限于氧化硅,其它常见的半导体介电材料也可适用作为第一、第二介电层170、200。此外,在根据本发明的其它实施例中,前述第一、第二介电层170、200也可为其它相异介电材料所构成。

38.其次,如图2b所示,对前述半导体样品10施一研磨处理,以邻近前述金属接触层180与前述导线层185间的界面250为研磨终点,逐渐研磨去除前述第二介电层200及前述导线层185,形成一研磨处理过的半导体样品10’的表面250’。根据本发明实施例,前述研磨处理步骤可利用人工研磨或机械研磨。

39.接着,如图2c所示,形成一黏着层300于研磨处理过的半导体样品10’的表面250’上,前述黏着层300对前述第一介电层170的附着力大于前述黏着层300对前述金属接触层180的附着力。其中,根据本发明实施例,前述黏着层300可为胶层、胶带或蜡层,且前述胶层或前述胶带包含一非挥发性且非液态的黏着材料,例如但不限于硅胶,其它具有对前述第一介电层170的附着力大于前述黏着层300对前述金属接触层180的附着力特性的黏着材料也可适用于本发明。此外,根据本发明实施例,前述黏着层300的厚度例如但不限于介于50~100微米。

40.然后,如图2d所示,固化前述黏着层300后,剥离前述黏着层300,使部分前述第一介电层170连同前述黏着层300一起被剥除,并使部分前述金属接触层180部分裸露出来,完成一故障分析用的半导体试片20的制备。根据本发明实施例,前述固化步骤可为常温固化、加热固化或照光固化。

41.综上所述,根据本发明所揭示的故障分析用的半导体试片的制备方法,藉由使用

一种非发性、非液态且对介电材质具有较高黏着特性而对导线材料具有较低黏着特性的黏着材料所构成的黏着层,可大面积、高均匀度的选择性移除介电材料部分厚度,并完整保留金属接触材料,且不会与半导体样品表面产生化学反应或甚至破坏欲分析的结构,且可藉由选用不同的黏着层材料,控制与介电层的黏着度,进而可以控制移除介电层的厚度,故可制备出一种适用于尺寸缩小化的故障分析用半导体试片。

42.虽然本发明已以实施例公开如上,然其并非用以限定本发明,任何熟习此技艺者,在不脱离本发明的精神和范围内,当可作各种的更动与润饰,因此本发明的保护范围当视后附的权利要求书所界定者为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。