1.本发明涉及一种封装结构及其制造方法,尤其涉及一种具有多个芯片的封装结构及其制造方法。

背景技术:

2.为了使得电子产品能达到轻薄短小的设计,半导体封装技术亦跟着日益进展,以发展出符合小体积、重量轻、高密度以及在市场上具有高竞争力等要求的产品。

3.而在具有多个芯片的芯片封装结构中,如何提升芯片与芯片之间信号传输质量或效率,实已成目前亟欲解决的课题。

技术实现要素:

4.本发明是针对一种芯片封装结构及芯片封装结构的制造方法,其具有较佳的信号传输质量或效率。

5.根据本发明的实施例,封装结构包括第一芯片、第二芯片、介电体、导电端子、第一线路层以及第一图案化绝缘层。第一芯片具有第一主动面。第二芯片具有第二主动面。第二芯片以其第二主动面面向第一主动面的方式设置于第一芯片上。介电体覆盖第一芯片。导电端子位于介电体上且相对于第二芯片。第一线路层包括第一线路部分以及第二线路部分。第一线路部分贯穿介电体。第一芯片经由第一线路部分电性连接于导电端子。第二线路部分嵌入介电体。第二芯片经由第二线路部分电性连接于第一芯片。第一图案化绝缘层覆盖线路层且嵌入介电体。

6.根据本发明的实施例,封装结构的制造方法包括以下步骤:提供载板;设置第一芯片于载板上;形成介电体于载板上,以覆盖第一芯片;形成第一线路层于载板上,且第一线路层包括第一线路部分以及第二线路部分,其中第一线路部分贯穿介电体,且第二线路部分嵌入介电体;形成第一图案化绝缘层于载板上,以覆盖线路层且嵌入介电体;设置第二芯片于第一芯片上,第二芯片的第二主动面面向第一芯片的第一主动面,且使第二芯片经由第二线路部分电性连接于第一芯片;以及移除载板,以于相对于第二芯片的介电体上形成导电端子,且使第一芯片经由第一线路部分电性连接于导电端子。

7.基于上述,本发明的芯片封装结构及芯片封装结构的制造方法可以具有较佳的信号传输质量或效率。

附图说明

8.图1a至图1e是依照本发明的第一实施例的一种封装结构的部分制造方法的部分剖视示意图;

9.图1f是依照本发明的第一实施例的一种封装结构的剖视示意图;

10.图1g是依照本发明的第一实施例的一种封装结构的部分剖视示意图;

11.图2是依照本发明的第二实施例的一种封装结构的剖视示意图;

12.图3是依照本发明的第三实施例的一种封装结构的剖视示意图。

13.附图标记说明

14.100、200、300:封装结构;

15.110:第一芯片;

16.110a:第一主动面;

17.110b:第一背面;

18.110c:第一侧面;

19.120:第二芯片;

20.120a:第二主动面;

21.120b:第二背面;

22.120c:第二侧面;

23.111、121:基材;

24.112、122:芯片连接垫;

25.113、123:芯片绝缘层;

26.124:芯片保护层;

27.125:芯片端子;

28.125s:籽晶层;

29.125p:镀覆层;

30.125r:导电连接层;

31.130:重布线路层;

32.131、133:导电层;

33.132、134:绝缘层;

34.134d:开口;

35.140:介电体;

36.140d、140e:介电开口;

37.140a:介电顶面;

38.140b:介电底面;

39.150:第一线路层;

40.150a:导电顶面;

41.150b:导电底面;

42.150c:导电侧面;

43.151:第一线路部分;

44.152:第二线路部分;

45.151s、152s、153s:籽晶层;

46.151p、152p、153p:镀覆层;

47.160:第一图案化绝缘层;

48.160d:绝缘开口;

49.178:导电连接件;

50.179:导电端子;

51.f1、f2:界面;

52.184:黏着层;

53.181:填充层;

54.282、382:模封体;

55.383:热界面材料;

56.384:散热件;

57.92:离型层;

58.91:载板。

具体实施方式

59.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

60.本文所使用的方向用语(例如,上、下、右、左、前、后、顶部、底部)仅作为参看所绘附图使用且不意欲暗示绝对定向。另外,为求清楚表示,于附图中可能省略示出了部分的膜层或构件。

61.除非另有限制,否则术语“设置(disposed)”、“连接(connected)”、“接触(contacted)”和其他在本文中的类似用语是广义上使用的并且涵盖直接和间接设置、连接、接触和其他类似用语。类似地,术语“面向(facing、faces)”和其在本文中的类似用语是广义上使用的并且涵盖直接和间接面向。因此,附图和描述应被视为在本质上是说明性而非限制性的。

62.除非另有明确说明,否则本文所述任何方法绝不意欲被解释为要求按特定顺序执行其步骤。

63.参照本实施例的附图以更全面地阐述本发明。然而,本发明亦可以各种不同的形式体现,而不应限于本文中所述的实施例。附图中的层或区域的厚度、尺寸或大小会为了清楚起见而放大。相同或相似的参考号码表示相同或相似的组件,以下段落将不再一一赘述。

64.图1a至图1e是依照本发明的第一实施例的一种封装结构的部分制造方法的部分剖视示意图。

65.请参照图1a,提供载板91。本发明对于载板91并无特别的限制,只要载板91可以适于承载形成于其上膜层或设置于其上的组件即可。

66.在本实施例中,载板91上可以具有离型层92,但本发明不限于此。离型层92例如是光热转换(light to heat conversion;lthc)黏着层或其他类似的膜层。

67.请继续参照图1a,在本实施例中,可以于载板91上形成重布线路层130。重布线路层130可以包括导电层131、133以及绝缘层132、134。最顶的绝缘层134(即,重布线路层130中最远离载板91的绝缘层;可以被称为:第二图案化绝缘层)可以具有多个开口134d,且开口134d可以暴露出最顶的导电层133(即,重布线路层130中最远离载板91的导电层;可以被称为:第二线路层)。重布线路层130可以经由一般常用的半导体工艺(如:沉积工艺、微影工艺和/或蚀刻工艺)形成,故于此不加以赘述。

68.请继续参照图1a,于载板91上设置第一芯片110。在本实施例中,第一芯片110可以被设置于重布线路层130上,但本发明不限于此。

69.在本实施例中,第一芯片110可以包括基材111、多个芯片连接垫112(可以被称为:第一芯片连接垫)以及芯片绝缘层113(可以被称为:第一芯片绝缘层)。基材111的一侧具有组件区(未示出),而组件区所位于的表面可以被称为第一主动面110a。相对于第一主动面110a的表面可以被称为第一背面110b。连接于第一主动面110a及第一背面110b之间的表面可以被称为第一侧面110c。芯片连接垫112可以位于第一主动面110a上。芯片绝缘层113可以覆盖芯片连接垫112,且芯片绝缘层113暴露出芯片连接垫112的一部分。在一般芯片设计中,组件区内的组件(如:第一芯片110的组件区内的组件)可以经由对应的后段金属内连(back end of line interconnect;beol interconnect)电性连接于对应的芯片连接垫(die pad;如:第一芯片110的部分芯片连接垫112)。

70.在本实施例中,芯片连接垫112例如为铝垫、铜垫或其他适宜的芯片连接垫,但本发明不限于此。

71.在一实施例中,第一芯片110的第一背面110b上可以具有黏着层184,但本发明不限于此。黏着层184可以包括芯片黏着膜(die attach film;daf),但本发明不限于此。

72.请参照图1a至图1b,于载板91上形成介电体140。介电体140可以覆盖第一芯片110。举例而言,介电体140可以覆盖第一芯片110的第一主动面110a及第一侧面110c。介电体140可以具有暴露出芯片连接垫112的第二介电开口140e。在一实施例中,介电体140可以经由涂布法或其他适宜的工艺形成,但本发明不限于此。

73.在本实施例中,介电体140可以被形成于重布线路层130上,但本发明不限于此。介电体140可以具有暴露出最顶的导电层134的第一介电开口140d。举例而言,可以将光敏介电材(photoimageable dielectric material;pid material)涂布于重布线路层130上。然后,可以经由光聚合(photopolymerization)和/或烘烤(baking)的方式固化部分的光敏介电材。并且,于固化部分的光敏介电材之后,经由湿清洗(wet clean)或其他适宜的方式以移除未被固化的其余光敏介电材。如此一来,可以经由上述的方式而形成具有第一介电开口140d及第二介电开口140e的介电体140。

74.在一实施例中,介电体140的形成方式可以依据其性质而加以调整,于本发明并不加以限制。

75.请参照图1b至图1c,于载板91上形成第一线路层150。第一线路层150可以覆盖介电体140,且第一线路层150可以填入介电体140的第一介电开口140d(标示于图1b)及第二介电开口140e(标示于图1b)。

76.在本实施例中,第一线路层150可以经由溅镀工艺、微影工艺、电镀工艺和/或蚀刻工艺形成,但本发明不限于此。举例而言,可以经由溅镀工艺于介电体140的表面上形成籽晶层(seed layer)。然后,可以经由微影工艺于籽晶层上形成图案化光阻层。然后,可以在经由电镀工艺以在图案化光阻层所暴露出的部分籽晶层上形成镀覆层。然后,可以经由蚀刻工艺移除图案化光阻层及未被镀覆层覆盖于其上的另一部分籽晶层。图案化的籽晶层151s、152s、153s(标示于图1g)及位于其上的图案化的镀覆层151p、152p、153p(标示于图1g)可以构成图案化的第一线路层150。

77.在本实施例中,第一线路层150可以包括第一线路部分151。第一线路部分151可以位于介电体140的第一介电开口140d(标示于图1b)内。位于第一介电开口140d内的部分第一线路部分151可以共形覆盖(conformally covered)第一介电开口140d的底部及侧壁。

78.在本实施例中,第一线路部分151可以完全填入绝缘层134的开口134d(标示于图1b)。第一线路部分151可以直接接触重布线路层130中最顶的导电层133。举例而言,属于第一线路部分151的图案化籽晶层(标示于图1g)可以直接接触部分的导电层133。

79.在本实施例中,第一线路部分151与导电层133是经由不同的步骤所形成。如此一来,相接触的第一线路部分151与导电层133之间可以具有界面(interface)f1(标示于图1g)。举例而言,属于第一线路部分151的部分图案化籽晶层151s(标示于图1g)与导电层133之间可以具有界面f1。

80.在本实施例中,第一线路层150可以包括第二线路部分152。第二线路部分152可以位于介电体140的第二介电开口140e(标示于图1b)内,且第二线路部分152可以完全填入第二介电开口140e。第二线路部分152可以直接接触第一芯片110的芯片连接垫112。举例而言,属于第二线路部分152的图案化籽晶层152s可以直接接触第一芯片110的芯片连接垫112。

81.请参照图1c至图1d,于载板91上形成第一图案化绝缘层160。第一图案化绝缘层160的材料可以包含无机材料、有机材料、其他适宜的绝缘材料或上述的堆栈,与本发明并不加以限制。在一实施例中,第一图案化绝缘层160的形成方式可以依据其性质而加以调整,于本发明并不加以限制。

82.在本实施例中,第一图案化绝缘层160可以覆盖第一线路层150。第一图案化绝缘层160可以具有多个绝缘开口160d,以暴露出部分的第一线路层150。举例而言,绝缘开口160d可以暴露出部分的第二线路部分152。

83.在本实施例中,第一图案化绝缘层160可以接触介电体140。举例而言,第一图案化绝缘层160可以直接接触介电体140的部分介电顶面140a(即,第一图案化绝缘层160最远离载板91或重布线路层130的表面)。

84.在本实施例中,第一图案化绝缘层160与介电体140是经由不同的步骤所形成。如此一来,相接触的第一图案化绝缘层160与介电体140之间可以具有界面f2(标示于图1g)。

85.在本实施例中,部分的第一图案化绝缘层160可以填入介电体140的第二介电开口140e(标示于图1b)。如此一来,可以降低位于第二介电开口140e内的第一线路部分151剥离(peeling)的可能。并且,在形成第一线路层150时,可以降低镀覆的厚度,而可以提升封装结构的制造效率。

86.请参照图1d至图1e,在形成第一图案化绝缘层160之后,可以将第二芯片120于第一芯片110上。第二芯片120可以经由导电连接件178电性连接第一芯片110。

87.在本实施例中,第二芯片120可以包括基材121、多个芯片连接垫122(可以被称为:第二芯片连接垫)、芯片绝缘层123(可以被称为:第二芯片绝缘层)、芯片保护层124以及多个芯片端子125。基材121的一侧具有组件区(未示出),而组件区所位于的表面可以被称为第二主动面120a。相对于第二主动面120a的表面可以被称为第二背面120b。连接于第二主动面120a及第二背面120b之间的表面可以被称为第二侧面120c。芯片连接垫122可以位于第二主动面120a上。芯片绝缘层123可以覆盖芯片连接垫122,芯片保护层124可以覆盖芯片绝缘层123,且芯片绝缘层123及芯片保护层124可以暴露出芯片连接垫122的一部分。在一般芯片设计中,组件区内的组件(如:第二芯片120的组件区内的组件)可以经由对应的后段金属内联机(back end of line interconnect;beol interconnect)电性连接于对应的连

接垫(如:第二芯片120的部分芯片连接垫122)。芯片端子125可以包括籽晶层125s(标示于图1g)、镀覆层125p(标示于图1g)以及导电连接层125r(标示于图1g),但本发明不限于此。在一实施例中,芯片端子125的籽晶层125s可以直接接触芯片连接垫122,且镀覆层125p可以位于籽晶层125s与导电连接层125r之间,但本发明不限于此。芯片连接垫122可以经由对应的芯片端子125电性连接于对应的导电连接件178。

88.在一实施例中,导电连接件178可以是焊球(solder ball)、导电凸块(conductive bump)或具有其他形式或形状的导电连接件178。导电连接件178可以经由置球(ball placement)、回焊(reflow)和/或其他适宜的工艺来形成。

89.在本实施例中,第二芯片120与第一图案化绝缘层160之间可以形成填充层181。填充层181可以包括毛细底部填胶(capillary underfill;cuf)或其他适宜的底胶(underfill),但本发明不限于此。

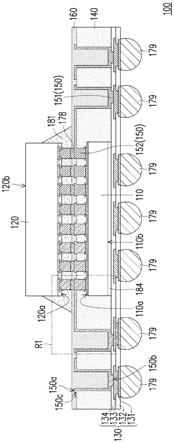

90.请继续参照图1d至图1e,在本实施例中,在移除载板91之后,可以形成多个导电端子179。导电端子179可以是导电柱(conductive pillar)、焊球(solder ball)、导电凸块(conductive bump)或具有其他形式或形状的导电端子179。导电端子179可以经由电镀、沉积、置球(ball placement)、回焊(reflow)和/或其他适宜的工艺来形成。导电端子179可以经由重布线路层130中对应的线路电性连接于第一线路层150中对应的第一线路部分151。

91.请参照图1e,在本实施例中,可以经由单一化工艺(singulation process),以至少切穿重布线路层130、介电体140以及第一图案化绝缘层160。单一化工艺例如可以包括切割工艺(dicing process/cutting process),但本发明不限于此。

92.值得注意的是,在进行单一化工艺之后,相似的组件符号将用于单一化后的组件。举例而言,第一芯片110(如图1d所示)于单一化后可以为第一芯片110(如图1e所示),重布线路层130(如图1d所示)于单一化后可以为重布线路层130(如图1e所示),介电体140(如图1d所示)于单一化后可以为介电体140(如图1e所示),第一图案化绝缘层160(如图1d所示)于单一化后可以为第一图案化绝缘层160(如图1e所示),诸如此类。其他单一化后的组件将依循上述相同的组件符号规则,于此不加以赘述或特别示出。

93.值得注意的是,本发明并未限定设置第二芯片120、形成多个导电端子179以及单一化工艺(若有)的顺序。举例而言,可以在设置第二芯片120之后形成多个导电端子179,然后进行单一化工艺。又举例而言,可以在设置第二芯片120之后进行单一化工艺,然后形成多个导电端子179。

94.图1f是依照本发明的第一实施例的一种封装结构的剖视示意图。图1g是依照本发明的第一实施例的一种封装结构的部分剖视示意图。图1g可以是对应于图1f中区域r1的放大图。请参照图1f及图1g,经过上述步骤后即可大致上完成本实施例的封装结构100的制作。

95.封装结构100包括第一芯片110、第二芯片120、介电体140、导电端子179以及第一线路层150。第二芯片120以第二主动面120a面向第一主动面110a的方式设置于第一芯片110上。介电体140覆盖第一芯片110。导电端子179位于介电体140上且相对于第二芯片120。第一线路层150包括第一线路部分151以及第二线路部分152。第一线路部分151贯穿介电体140。第一芯片110经由第一线路部分151电性连接于导电端子179。第二线路部分152嵌入介电体140。第二芯片120经由第二线路部分152电性连接于第一芯片110。第一图案化绝缘层

160覆盖第一线路层150且嵌入介电体140。

96.在本实施例中,第一线路层150可以具有导电顶面150a、导电底面150b及导电侧面150c。导电顶面150a可以是第一线路层150中最远离重布线路层130的表面。导电底面150b可以是第一线路层150中最接近重布线路层130的表面。导电侧面150c可以是连接导电顶面150a及导电底面150b的表面。第一图案化绝缘层160可以覆盖第一线路层150的部分导电顶面150a及部分导电侧面150c。如此一来,可以降低位于第一线路层150剥离(peeling)的可能。

97.在本实施例中,导电顶面150a的位置(泛指自其延伸的虚拟面)可以介于介电顶面140a的位置(泛指自其延伸的虚拟面)与介电底面140b的位置(泛指自其延伸的虚拟面)之间,且介电顶面140a的位置(泛指自其延伸的虚拟面)可以介于导电顶面150a的位置(泛指自其延伸的虚拟面)与导电底面150b的位置(泛指自其延伸的虚拟面)之间。也就是说,第一线路层150的导电底面150b与介电体140的介电底面140b(即,介电体140最接近重布线路层130的表面)不共面,且第一线路层150的导电顶面150a与介电体140的介电顶面140a不共面。

98.在本实施例中,第一芯片110与第二芯片120之间的信号传输距离基本上相同于第一芯片110与第二芯片120之间的物理距离。举例而言,第一芯片110与第二芯片120之间的信号可以经由对应的导电件(如:对应的导电连接件178及对应的第二线路部分152)传输,且第一芯片110的芯片连接垫112与第二芯片120的芯片端子125之间的距离基本上等于前述的导电件的高度或厚度(如:对应的导电连接件178的高度及对应的第二线路部分152的厚度)。如此一来,可能可以提升第一芯片110与第二芯片120之间信号传输的质量及效率。

99.一般而言,在多个导电结构所构成的导体中,沿着导体传输的信号会因为多个导电结构之间的不连续(如:可能因材质或晶格的不同而具有接口或阻抗不匹配)而会有对应的反射信号。这种现象可以被称为回波损耗(return loss)。因此,相较于以一般重布线路的方式进行芯片间的信号传输,经由对应的导电连接件178及对应的第二线路部分152可能可以提升第一芯片110与第二芯片120之间信号传输的质量及效率。

100.在一实施例中,第一芯片110及第二芯片120可以是具有相同或不同功能(function)的晶粒(die)、封装后芯片(packaged chip)、堆栈式的芯片封装件(stacked chip package)或是特殊应用集成电路(application-specific integrated circuit;asic),但本发明不限于此。

101.在一实施例中,第一芯片110及第二芯片120之间可以是异质的(heterogeneous)芯片。举例而言,第一芯片110及第二芯片120的其中之一可以是动态随机存取内存芯片(dynamic random access memory,dram)、静态随机存取内存芯片(static random access memory,sram)或高带宽内存(high bandwidth memory,hbm)芯片,第一芯片110及第二芯片120的其中另一可以是特殊应用集成电路芯片(application-specific integrated circuit,asic)、应用处理器(application processor,ap)、系统芯片(system on chip,soc)或其他类似的高效能运算(high performance computing,hpc)芯片,但本发明不限于此。

102.图2是依照本发明的第二实施例的一种封装结构的剖视示意图。第二实施例的封装结构200与第一实施例的封装结构100相似,其类似的构件以相同的标号表示,且具有类

似的功能、材质或形成方式,并省略描述。

103.请参照图2,封装结构200可以包括第一芯片110、第二芯片120、介电体140、导电端子179、第一线路层150以及模封体282。模封体282覆盖第二芯片120。举例而言,模封体282可以覆盖第二芯片120的第二侧面120c。在一实施例中,模封体282的材质可以包括环氧树脂(epoxy resin)或其他适宜的模塑化合物(molding compound),但本发明不限于此。模封体282例如是经由模塑工艺(molding process)所形成,但本发明不限于此。

104.在本实施例中,模封体282还可以覆盖第二芯片120的第二背面120b,但本发明不限于此。

105.图3是依照本发明的第三实施例的一种封装结构的剖视示意图。第三实施例的封装结构300与第二实施例的封装结构200相似,其类似的构件以相同的标号表示,且具有类似的功能、材质或形成方式,并省略描述。

106.请参照图3,封装结构300可以包括第一芯片110、第二芯片120、介电体140、导电端子179、第一线路层150、模封体382以及散热件384。模封体382可以暴露出第二芯片120的第二背面120b。散热件384可以热耦接于第二芯片120。

107.在本实施例中,第二芯片120的第二背面120b与散热件384之间可以具有热界面材料(thermal interface material;tim)383,但本发明不限于此。

108.在一实施例中,第二芯片120的第二背面120b可以直接接触散热件384,但本发明不限于此。

109.在一实施例中,类似于散热件384的散热件可以具有鳍片(fins),但本发明不限于此。

110.综上所述,本发明的芯片封装结构及芯片封装结构的制造方法可以具有较佳的信号传输质量或效率。

111.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。