包括被配置作为用于器件的基座平面的阻焊层的封装件

1.优先权要求

2.本专利申请要求于2019年10月1日提交的题为“package comprising a solder resist layer configured as a seating plane for a device”的申请号16/590,299的优先权,其被转让给本技术的受让人并在此通过引用明确并入本文。

技术领域

3.各种特征涉及包括器件的封装件,但更具体地涉及包括被配置作为用于器件的基座平面的阻焊层的封装件。

背景技术:

4.图1图示了包括衬底102、管芯104和包封层160的封装件100。管芯104通过多个焊料互连件140而耦合到衬底102的第一表面,焊料互连件140可以包括凸块和柱。衬底102包括多个介电层120和多个互连件122。介电层120的每一层包括图案化金属层。衬底102包括第一阻焊层124、第二阻焊层126和多个焊料互连件130。包封层160包封管芯104。存在改进封装件的性能的持续需要。

技术实现要素:

5.各种特征涉及包括器件的封装件,但是更具体地涉及包括被配置作为用于器件的基座平面的阻焊层的封装件。

6.一个示例提供了一种封装件,该封装件包括:衬底,具有第一表面;阻焊层,被耦合到衬底的第一表面;器件,该器件位于阻焊层上方,使得器件的一部分接触阻焊层;以及包封层,该包封层位于阻焊层上方,使得包封层对该器件进行包封。

7.另一个示例提供了一种装置,该装置包括:衬底,具有第一表面;用于提供被耦合到衬底的第一表面的水平支撑的部件;器件,该器件位于用于提供水平支撑的部件上方,使得该器件的一部分接触用于提供水平支撑的部件;以及用于包封的部件,该用于包封的部件位于用于提供水平支撑的部件上方,使得用于包封的部件对该器件进行包封。

8.另一个示例提供了一种用于制造封装件的方法。该方法提供了包括第一表面的衬底。该方法在衬底的第一表面上方形成阻焊层。该方法将器件耦合到衬底,使得器件位于阻焊层上方并接触阻焊层。该方法在阻焊层上方形成包封层,使得包封层对该器件进行包封。

附图说明

9.当结合附图进行以下所阐述的详细描述时,各种特征、性质和优点将变得明显,其中相同的参考符号自始至终对应地标识。

10.图1图示了包括管芯和衬底的器件的轮廓图。

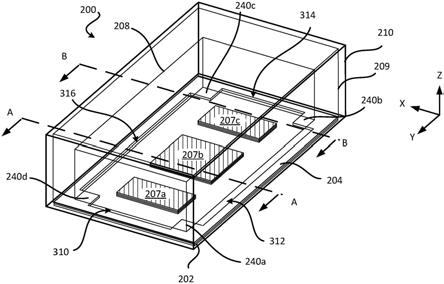

11.图2图示了包括被配置作为用于器件的基座平面的阻焊层的封装件的组装图。

12.图3图示了包括被配置作为用于器件的基座平面的阻焊层的封装件的视图。

13.图4图示了包括被配置作为用于器件的基座平面的阻焊层的封装件的aa截面的轮廓图。

14.图5图示了包括被配置作为用于器件的基座平面的阻焊层的封装件的bb截面的轮廓图。

15.图6图示了包括被配置作为用于器件的基座平面的阻焊层的封装件的平面图。

16.图7图示了被配置作为用于器件的基座平面的阻焊层的示例性图案的平面图。

17.图8图示了被配置作为用于器件的基座平面的阻焊层的另一个示例性图案的平面图。

18.图9图示了被配置作为用于器件的基座平面的阻焊层的另一个示例性图案的平面图。

19.图10图示了被配置作为用于器件的基座平面的阻焊层的另一个示例性图案的平面图。

20.图11图示了被配置作为用于器件的基座平面的阻焊层的另一个示例性图案的平面图。

21.图12图示了被配置作为用于器件的基座平面的阻焊层的另一个示例性图案的平面图。

22.图13图示了包括被配置作为用于器件的基座平面的阻焊层的封装件的平面图。

23.图14(包括图14a至图14d)图示了用于制造包括被配置作为用于器件的基座平面的阻焊层的封装件的示例性顺序。

24.图15图示了用于制造封装件的方法的示例性流程图,该封装件包括被配置作为用于器件的基座平面的阻焊层。

25.图16图示了可以对管芯、集成器件、集成无源器件(ipd)、无源组件、封装件和/或本文中所描述的器件封装件进行集成的各种电子设备。

具体实施方式

26.在以下描述中,给出了具体细节以提供对本公开的各个方面的透彻理解。然而,本领域普通技术人员将理解,可以在没有这些具体细节的情况下实践这些方面。例如,可以在框图中示出电路以避免在不必要的细节中模糊各方面。在其他情形中,可能未详细示出众所周知的电路、结构和技术以免模糊本公开的各方面。

27.本公开描述了一种封装件,该封装件包括:衬底,具有第一表面;阻焊层,被耦合到衬底的第一表面;以及器件,该器件位于阻焊层上方,使得器件的一部分接触阻焊层。该封装件还包括包封层,该包封层位于阻焊层上方,使得包封层对该器件进行包封。阻焊层被配置作为用于器件的基座平面。阻焊层提供了有助于使器件(相对于衬底)的倾斜减小、最小化和/或消除的层,这可以帮助器件执行得更好。例如,该器件可以是对倾斜敏感的射频(rf)器件。因此,使rf器件相对于衬底的倾斜减小、最小化和/或消除有助于提高rf器件的性能。器件和/或器件的部分可以位于阻焊层上方,使得器件的面向衬底的表面大致平行于衬底的第一表面。阻焊层包括至少一个凹部。该器件位于阻焊层上方,使得该器件的至少一个角接触该至少一个凹部。

28.包括被配置作为用于器件的基座平面的阻焊层的示例性封装件

29.图2图示了包括阻焊层的封装件200的组装,阻焊层被配置作为用于器件的基座平面。封装件200包括衬底202、阻焊层204、衬底互连件205、焊料互连件206、器件互连件207和器件208。封装件200可以包括射频(rf)器件封装。

30.衬底202可以是任何类型的衬底,诸如层压衬底。衬底202可以包括硅和/或玻璃。衬底202可以包括一个或多个介电层。衬底202可以包括多个互连件。

31.阻焊层204被耦合到衬底202的表面(例如,第一表面)。阻焊层204包括允许阻焊层204被配置作为用于器件208的基座平面的图案和/或开口。如将在下面进一步描述的,当器件208的至少一部分被定位在(例如,搁置在、放置在)阻焊层204上方时,阻焊层204被配置为作为用于器件208的水平支撑,使得器件208的表面(例如,面向衬底202的表面、底表面、有源表面)平行于(或尽可能平行于)衬底202的表面。阻焊层204可以是用于提供水平支撑的部件。

32.衬底互连件205(例如205a-205c)、焊料互连件206(例如206a-206c)和器件互连件207(例如207a-207c)被配置为在衬底202和器件208之间提供一个或多个电路径。例如,衬底互连件205a、焊料互连件206a和器件互连件207a可以被配置为在衬底202和器件208之间针对接地提供一个或多个电路径。衬底互连件205b、焊料互连件206b和器件互连件207b可以被配置为在衬底202和器件208之间针对输入/输出(i/o)信号提供一个或多个电路径。衬底互连件205c、焊料互连件206c、并且器件互连件207c可以被配置为在衬底202和器件208之间针对电力提供一个或多个电路径。然而,不同的实现可以使用不同的互连件配置和/或布置来在衬底202和器件208之间提供接地、电力和/或i/o信号。

33.衬底互连件205可以被耦合到衬底202的第一表面。衬底互连件205可以包括一个或多个导电层(例如,金属,铜)。在一些实现中,衬底互连件205可以被认为是衬底202的部分。焊料互连件206可以被耦合到衬底互连件205。器件互连件207可以被耦合到焊料互连件206。器件互连件207可以包括一个或多个导电层(例如,金属,铜)。在一些实现中,器件互连件207可以被认为是器件208的部分。

34.器件208被耦合到阻焊层204和器件互连件207。器件208位于衬底202和阻焊层204上方,使得器件208的至少一部分接触(例如,直接接触)阻焊层204。在这种配置中,器件208的部分可以被定位(例如,搁置)在阻焊层204上方。例如,器件208的一个或多个角可以搁置在阻焊层204的部分上并且/或接触阻焊层204的部分。因此,阻焊层204的一个或多个部分可以被配置作为用于器件208的基座平面。

35.阻焊层204提供了有助于使器件208(相对于衬底202)的倾斜(例如,沿长度和/或宽度的倾斜)减小、最小化和/或消除的层,这可以帮助器件208执行得更好。例如,器件208可以是对倾斜敏感的射频(rf)器件。因此,使rf器件相对于衬底202的倾斜减少、最小化和/或消除有助于提高rf器件的性能。器件208可以位于阻焊层204上方,使得器件208的面向衬底202的表面大致平行于衬底202的第一表面。阻焊层204包括至少一个凹部(例如,240a-240d)。器件208可以位于阻焊层204上方,使得器件208的至少一个角接触至少一个凹部(例如,240a-240d)。

36.器件208可以包括射频(rf)器件、管芯、集成器件、无源器件、滤波器、电容器、电感器、天线、发射器、接收器和/或它们的组合。器件208可以是组件和/或器件的组装。

37.如以下将在图3中进一步描述的那样,封装件200可以包括包封层209和屏蔽件

210。包封层209可以包括模具、树脂和/或环氧树脂。包封层209可以是用于包封的部件。屏蔽件210可以是电磁干扰(emi)屏蔽件。屏蔽件210可以是用于屏蔽的部件(例如,用于emi屏蔽的部件)。屏蔽件210可以被配置为耦合到接地。

38.图3图示了封装件200的另一视图。封装件200包括衬底202、阻焊层204、衬底互连件205、焊料互连件206、器件互连件207、器件208、包封层209和屏蔽件210。要注意的是,阻焊层204可以被认为是衬底202的部分。

39.如上所述,阻焊层204包括凹部(例如,第一凹部240a、第二凹部240b、第三凹部240c、第四凹部240d)。阻焊层204被设置在衬底202上方。器件208被耦合到衬底202的第一表面,使得器件208的部分接触阻焊层204。例如,(i)器件208的第一角可以搁置在阻焊层204的第一凹部240a上和/或接触阻焊层204的第一凹部240a,(ii)器件208的第二角可以搁置在阻焊层204的第二凹部240b上和/或接触阻焊层204的第二凹部240b,(iii)器件208的第三角可以搁置在阻焊层204的第三凹部240c上和/或接触阻焊层204的第三凹部240c,和/或(iv)器件208的第四角可以搁置在阻焊层204的第四凹部240d上和/或接触阻焊层204的第四凹部240d。阻焊层204(特别是凹部(例如,240a-240d))被配置作为用于提供水平支撑的部件,这有助于防止器件208过度倾斜。在一些实现中,使用阻焊层204作为用于器件208的基座平面有助于器件208的表面在平行于衬底202的第一表面的2度内或更少。因此,例如,阻焊层205可以帮助防止器件208从衬底202倾斜多于2度。

40.图3图示了器件208位于衬底202和阻焊层204上方,使得器件208的表面与阻焊层204的表面之间存在至少一个间隙。例如,图3图示了器件208的横向表面(例如,侧表面)与阻焊层204的表面(例如,横向表面)之间的第一间隙310、第二间隙312、第三间隙314和第四间隙316。如将在下文进一步描述的,一个或多个间隙(例如,310、312、314、316)可以被配置为允许包封层209形成在器件208和衬底202之间(例如,在还没有被互连件和阻焊层204占据的空间中)。

41.图3图示了包封层209在衬底202和阻焊层204上方被形成,使得包封层209对器件208进行包封。例如,包封层209可以位于阻焊层204上方,使得包封层209对器件208进行包封。包封层209可以被形成并位于间隙(例如,310、312、314、316)中且围绕间隙(例如,310、312、314、316)。包封层209可以被形成并且位于衬底202与器件208的表面(例如,底表面)之间。在一些实现中,包封层209可以通过一个或多个间隙(例如,310、312、314、316)而被提供在器件208和衬底202之间。在一些实现中,包封层209被提供以使得器件208与衬底202之间的空间基本上没有空隙(例如,气隙)。基本上没有空隙可能意味着空隙表示器件208与衬底202之间的空间的百分之五(5%)或更少。这是可能的,因为包封层209能够通过一个或多个间隙进入并安置在衬底202和器件208之间未被占据的空间中。当器件208包括对不同材料敏感的rf组件时,使衬底202与器件208之间的空隙减小、最小化和/或消除可能很重要。包封层209和空隙具有不同的性质,这可能影响器件208的性能。例如,器件208的靠近空隙的部分可能会执行得与器件208的靠近包封层209的另一部分不同。为了提供一致地执行的器件208,确保使衬底202与器件208之间的空隙减小、最小化和/或消除可能很重要。在一些实现中,在衬底202和器件208之间的空间中存在百分之五(5%)或更少的空隙。衬底202与器件208之间的阻焊层204和互连件(例如,205、206、207)不应被视为空隙。

42.屏蔽件210可以被形成在包封层209的表面、阻焊层204的侧表面和/或衬底202的

侧表面上方。屏蔽件210可以是电磁干扰(emi)屏蔽件。屏蔽件210可以是用于屏蔽的部件(例如,用于emi屏蔽的部件)。屏蔽件210可以被配置为法拉第笼(faraday cage)。屏蔽件210可以包括导电材料(例如金属)。屏蔽件210可以被耦合到接地。屏蔽件210可以被图案化。

43.图4图示了跨封装件200的aa截面的轮廓图。如图4中所示,器件208位于衬底202和阻焊层204上方,使得阻焊层204被配置作为用于器件208的基座平面。如图4中所示,器件208位于阻焊层204上方,使得器件208的一部分接触阻焊层204。在该示例中,器件208的第一角接触阻焊层204的第一凹部240a,并且器件208的第二角接触第四凹部240d。这种配置允许器件208尽可能地平行于衬底202。例如,这种配置允许器件208的表面(例如,底表面、顶表面)尽可能地平行于衬底202的表面。在一些实现中,器件208和/或器件208的表面在平行于衬底202和/或衬底202的表面的2度内。器件208相对于衬底202的倾斜角可以大致为2度或更小。

44.图5图示了跨封装件200的bb截面的轮廓图。如图5中所示,器件208位于衬底202上方。器件208通过互连件(205、206、207)被电耦合到衬底。器件208位于衬底202上方,使得在器件208与阻焊层204之间存在至少一个间隙(例如,第二间隙312、第四间隙316)。(多个)间隙被配置为允许包封层209被形成在器件208下方并且在器件208和衬底202之间。(多个)间隙可以具有至少15微米(μm)的宽度。在一些实现中,(多个)间隙(例如,310、312、314、316)可以具有在大约15至60微米(μm)范围内的宽度。

45.图4和图5图示了在包封层209的表面(例如,外表面)、阻焊层204的侧表面和/或衬底202的侧表面上方形成的屏蔽件210。屏蔽件210可以被图案化。

46.图6图示了器件208可以如何被定位在衬底202和阻焊层204上方的平面图。如图6中所示,在一个示例中,器件208可以被定位在衬底202和阻焊层204上方,使得(i)器件208的第一角可以搁置在阻焊层204的第一凹部240a上和/或接触阻焊层204的第一凹部240a,(ii)器件208的第二角可以搁置在阻焊层204的第二凹部240b上和/或接触阻焊层204的第二凹部240b,(iii)器件208的第三角可以搁置在阻焊层204的第三凹部240c上和/或接触阻焊层204的第三凹部240c,和/或(iv)器件208的第四角可以搁置在阻焊层204的第四凹部240d上和/或接触阻焊层204的第四凹部240d。此外,器件208可以被定位在衬底202和阻焊层204上方,使得存在第一间隙310、第二间隙312、第三间隙314和第四间隙316以供包封层209进入并安置在器件208和衬底202之间。第一间隙310、第二间隙312、第三间隙314和/或第四间隙316可以被填充有包封层209。

47.使用被配置作为基座平面的阻焊层提供了若干技术优势,诸如(i)使器件相对于衬底的倾斜或过度倾斜减小、最小化和/或消除,(ii)使衬底与器件之间的空隙或过多空隙减少、最小化和/或消除,(iii)使由于倾斜引起的器件高度的变化减小、最小化和/或消除,(iv)使衬底与器件之间的包封层中的不一致性减小、最小化和/或消除,和/或(v)使器件性能的变化减小、最小化和/或消除。

48.图2-图6图示了图案化的阻焊层204的示例。然而,不同的实现可以使用具有不同图案和/或开口的阻焊层。图7-图12图示了具有不同图案和/或开口的各种阻焊层,其可以利用封装件200或本公开中描述的任何封装件来实现。图7-图12还图示了器件208如何可以接触和/或搁置在各种阻焊层上方。

49.图7图示了包括第一凹部240a、第二凹部740a、第三凹部740b和第四凹部240d的阻焊层704。第二凹部740a和第三凹部740b可以具有与第一凹部240a和第四凹部240d不同的尺寸。

50.图8图示了包括第一凹部840a、第二凹部840b、第三凹部840c和第四凹部840d的阻焊层804。第一凹部840a、第二凹部840b、第三凹部840c和第四凹部840d可以具有弯曲形状和/或弧形形状。凹部的尺寸可以相同或不同。

51.图9图示了包括第一凹部240a、第四凹部240d和第一部分940a的阻焊层904。器件208的一个或多个部分可以接触第一凹部240a、第四凹部240d和/或第一部分940a。图10图示了包括第一部分940a和第二部分1040a的阻焊层1004。器件208的一个或多个部分可以接触第一部分940a和/或第二部分1040a。

52.图11图示了阻焊层1104,阻焊层1104包括第一岛1140a(例如,阻焊岛)、第二岛1140b(例如,阻焊岛)、第三岛1140c和第四岛1140d。器件208的一个或多个部分可以接触第一岛1140a、第二岛1140b、第三岛1140c和/或第四岛1140d。

53.图12图示了包括第一岛1240a和第二岛1240b的阻焊层1204。第一岛1240a和第二岛1240b具有矩形形状。器件208的一个或多个部分可以接触第一岛1240a和/或第二岛1240b。

54.应注意,不同的实现可以使用包括凹部、平面和/或岛的不同组合的阻焊层。此外,凹部、平面和/或岛的位置可以变化。凹部、平面和/或岛的数目也可以变化。凹部、平面和/或岛的尺寸和/或形状可以变化。

55.图2-图6图示了包括器件208的封装件200。应注意,封装件200可以包括若干组件,诸如其他器件、管芯、集成器件、电容器和/或电感器。图13图示了包括若干器件1308、电容器1318、阻焊层204和器件208的封装件1300。封装件1300可以包括封装件300的相似或相同的组件。器件1308可以包括管芯和/或集成器件。器件208被定位在阻焊层204上方,使得器件208的部分位于凹部(例如,240a-240d)上方。封装件1300的阻焊层204可以被配置作为用于器件208的基座平面。

56.已经描述了包括被配置作为用于器件的基座平面的阻焊层的各种封装件,现在将在下面描述用于制造包括被配置作为用于器件的基座平面的阻焊层的封装件的顺序。

57.用于制造包括被配置作为用于器件的基座平面的阻焊层的封装件的示例性顺序

58.图14(包括图14a-图14d)图示了用于提供或制造包括阻焊层的封装件的示例性顺序,该阻焊层被配置作为用于器件的基座平面。在一些实现中,图14a-图14d的顺序可以被用来提供或制造图3的封装件200或本公开中描述的任何封装件。

59.应该注意的是,图14a-图14d的顺序可以对一个或多个阶段进行组合,以便简化和/或阐明用于提供或制造包括阻焊层的封装件的顺序,该阻焊层被配置作为用于器件的基座平面。在一些实现中,可以改变或修改过程的顺序。在一些实现中,可以取代或替换一个或多个过程而不背离本公开的精神。然而,不同的实现可以以不同的方式制造封装件。

60.阶段1,如图14a中所示,图示了衬底202被提供之后的状态。衬底202可以包括一个或多个介电层和多个互连件。衬底202可以包括硅。可以制造衬底202。在一些实现中,制造衬底202可以包括使用半增材工艺(semi additive process,sap)和/或修改的半增材工艺(modified semi additive process,msap)。

61.阶段2图示了阻焊层204被设置(例如,形成)在衬底202上方之后的状态。阻焊层204可以被配置为作为用于器件(例如,208)的基座平面进行操作。阻焊层204包括凹部(例如,240a-240d)。不同的实现可以使用具有不同图案和/或开口的阻焊层,诸如图7至图12中描述的阻焊层。阻焊层可以包括凹部、平面和/或岛。

62.阶段3,如图14b中所示,图示了衬底互连件205被设置(例如,形成)在衬底202上方之后的状态。可以使用电镀工艺来形成衬底互连件205。在一些实现中,衬底互连件205可以在阻焊层204被形成衬底202上方之前被设置。在一些实现中,当衬底202在阶段1被提供时,衬底202可以包括衬底互连件205。

63.阶段4图示了焊料互连件206被设置(例如,形成)在衬底互连件205上方之后的状态。可以使用电镀工艺来在衬底互连件205上方形成焊料互连件206。

64.阶段5图示了器件互连件207被设置(例如,形成)在焊料互连件206上方之后的状态。可以使用电镀工艺来在焊料互连件206上方形成器件互连件207。在一些实现中,器件互连件207可以被认为是器件208的部分。在这种情形中,当器件208被耦合到衬底202和阻焊层204时,器件互连件207可以被耦合到焊料互连件206。

65.阶段6,如图14c中所示,图示了器件208被耦合到衬底202和阻焊层204的状态。器件208可以通过拾取和放置工艺来耦合。器件208可以被配置为电耦合到器件互连件207、焊料互连件206和衬底互连件205。器件208被定位在衬底202和阻焊层204上方,使得(i)器件208的第一角可以搁置在阻焊层204的第一凹部240a上和/或接触阻焊层204的第一凹部240a,(ii)器件208的第二角可以搁置在阻焊层204的第二凹部240b上和/或接触阻焊层204的第二凹部240b,(iii)器件208的第三角可以搁置在阻焊层204的第三凹部240c上和/或接触阻焊层204的第三凹部240c,和/或(iv)器件208的第四角可以搁置在阻焊层204的第四凹部240d上和/或接触阻焊层204的第四凹部240d。

66.如阶段6所示,阻焊层204的凹部被配置作为用于器件208的基座平面,有助于使器件208相对于衬底202的倾斜减小、最小化和/或消除。

67.此外,器件208可以被定位在衬底202和阻焊层204上方,使得在器件208的表面与阻焊层204的表面之间存在第一间隙310、第二间隙312、第三间隙314和第四间隙316。如下文将进一步描述的,间隙(例如,210、312、314、316)可以被用来允许包封层在器件208下方行进,从而使器件208与衬底202之间的空隙减小、最小化和/或消除。

68.器件208可以包括射频(rf)器件、管芯、集成器件、无源器件、滤波器、电容器、电感器、天线、发射器、接收器和/或它们的组合。器件208可以是组件和/或器件的组装。

69.阶段7图示了包封层209被形成在衬底202、阻焊层204和器件208上方之后的状态。包封层209被形成以使得包封层209对器件208进行包封。此外,包封层209可以被形成并位于间隙(例如,310、312、314、316)中以及在衬底202和器件208之间。不同的实现可以不同地提供和形成包封层209。一些实现可以使用压缩和传递模塑工艺(compression and transfer molding process)、片状模塑工艺(sheet molding process)或液体模塑工艺(liquid molding process)来提供和形成包封层209。阶段7可以图示包括被配置作为用于器件的基座平面的阻焊层的封装件200的示例。

70.阶段8,如图14d中所示,图示了屏蔽件210被形成在包封层209上方之后的状态。屏蔽件210可以是emi屏蔽。屏蔽件210可以包括一种或多种导电材料(例如金属)。屏蔽件210

可以在阻焊层204的侧表面和/或衬底202的侧表面上方被形成。可以使用电镀工艺和/或溅射工艺来形成屏蔽件210。屏蔽件210可以是被图案化的屏蔽件。屏蔽件210可以被形成,使得屏蔽件210被配置为耦合到接地。阶段8可以图示包括被配置作为用于器件的基座平面的阻焊层的封装件200的示例。

71.用于制造包括被配置作为用于器件的基座平面的阻焊层的封装件的方法的示例性流程图

72.在一些实现中,制造包括被配置作为用于器件的基座平面的阻焊层的封装件包括若干过程。图15图示了用于提供或制造封装件的方法1500的示例性流程图,该封装件包括被配置作为用于器件的基座平面的阻焊层。图15的方法1500可以被用来提供或制造本公开中描述的图3的封装件200。然而,方法1500可以被用来提供或制造本公开中描述的任何封装件。

73.应该注意的是,图15的顺序可以对一个或多个过程进行组合,以便简化和/或阐明用于提供或制造封装件的方法,该封装件包括被配置作为用于器件的基座平面的阻焊层。在一些实现中,过程的顺序可以被改变或修改。在一些实现中,可以取代或替换一个或多个过程而不背离本公开的精神。然而,不同的实现可以以不同的方式制造封装件。

74.该方法提供(在1505处)衬底(例如,202)。衬底202可以包括一个或多个介电层和多个互连件。衬底202可以包括第一表面和第二表面。可以制造衬底202。在一些实现中,制造衬底202可以包括使用半增材工艺(sap)和/或修改的半增材工艺(msap)。

75.该方法在衬底(例如,202)的第一表面上方形成(在1510处)阻焊层(例如,204)。阻焊层的图案和/或开口可以随着不同的实现而变化。图14a的阶段2图示了被设置(例如,形成)在衬底202上方的阻焊层204的示例。阻焊层204可以被配置为作为用于器件(例如,208)的基座平面进行操作。阻焊层204包括凹部(例如,240a-240d)。不同的实现可以使用具有不同图案和/或开口的阻焊层,诸如图7-图12中描述的阻焊层。阻焊层可以包括凹部、平面、岛和/或它们的组合。

76.该方法在衬底202上方形成(在1515处)衬底互连件(例如,205)。图14b的阶段3图示了被设置(例如,形成)在衬底202上方的衬底互连件205的示例。可以使用电镀工艺来形成衬底互连件205。在一些实现中,衬底互连件205可以在阻焊层204被形成衬底202上方之前被设置。在一些实现中,当衬底202在图14a的阶段1被提供时,衬底202可以包括衬底互连件205。

77.该方法在衬底互连件205上方形成(在1520处)焊料互连件(例如,206)。图14b的阶段4图示了被设置(例如,形成)在衬底互连件205上方的焊料互连件206的示例。可以使用电镀工艺来在衬底互连件205上方形成焊料互连件206。

78.该方法在焊料互连件206上方形成(在1525处)器件互连件(例如,207)。图14b的阶段5图示了被设置(例如,形成)在焊料互连件206上方的器件互连件207的示例。可以使用电镀工艺来在焊料互连件206上方形成器件互连件207。在一些实现中,器件互连件207可以被认为是器件208的部分。在这种情形中,当器件208被耦合到衬底202和阻焊层204时,器件互连件207可以被耦合到焊料互连件206。

79.该方法将器件(例如,208)耦合(在1530处)到衬底,使得器件的至少一部分位于阻焊层上方并接触阻焊层。图14c的阶段6图示了被耦合到衬底202和阻焊层204的器件208的

示例。器件208可以通过拾取和放置工艺来耦合到衬底。

80.器件208可以被配置为电耦合到器件互连件207、焊料互连件206和衬底互连件205。器件208被定位在衬底202和阻焊层204上方,使得(i)器件208的第一角可以搁置在阻焊层204的第一凹部240a上和/或接触阻焊层204的第一凹部240a,(ii)器件208的第二角可以搁置在阻焊层204的第二凹部240b上和/或接触焊料的第二凹部240b阻焊层204,(iii)器件208的第三角可以搁置在阻焊层204的第三凹部240c上和/或接触阻焊层204的第三凹部240c,和/或(iv)器件208的第四角可以搁置在阻焊层204的第四凹部240d上和/或接触阻焊层204的第四凹部240d。

81.阻焊层204的凹部被配置作为用于器件208的基座平面,从而使器件208相对于衬底202的倾斜减小、最小化和/或消除。

82.器件208可以被定位在衬底202和阻焊层204上方,使得在器件208的表面和阻焊层204的表面之间存在第一间隙310、第二间隙312、第三间隙314和第四间隙316。

83.器件208可以包括射频(rf)器件、管芯、集成器件、无源器件、滤波器、电容器、电感器、天线、发射器、接收器和/或它们的组合。器件208可以是组件和/或器件的组装。

84.该方法在阻焊层204和/或衬底202上方形成(在1535处)包封层(例如,209),使得包封层对器件208进行包封。如图14c中所示的阶段7图示了在衬底202、阻焊层204和器件208上方形成的包封层209的示例。包封层209被形成,使得包封层209对器件208进行包封。此外,包封层209可以被形成并位于间隙(例如,310、312、314、316)中以及在衬底202和器件208之间。间隙(例如,210、312、314、316)可以被用来允许包封层在器件208下方行进,从而使器件208与衬底202之间的空隙减小、最小化和/或消除。不同的实现可以提供和形成包封层209。一些实现可以使用压缩和传递模塑工艺、片状模塑工艺或液体模塑工艺来提供和形成包封层209。

85.该方法在包封层(例如,209)的表面上方形成(在1540处)屏蔽件(例如,210)。图14d的阶段8图示了被形成在包封层209上方的屏蔽件210的示例。屏蔽件210可以是emi屏蔽。屏蔽件210可以包括一种或多种导电材料(例如金属)。屏蔽件210可以在阻焊层204的侧表面和/或衬底202的侧表面上方被形成。可以使用电镀工艺和/或溅射工艺来形成屏蔽件210。屏蔽件210可以是被图案化的屏蔽件。屏蔽件210可以被形成,使得屏蔽件210被配置为耦合到接地。

86.示例性电子设备

87.图16图示了可以与上述器件、集成器件、集成电路(ic)封装、集成电路(ic)器件、半导体器件、集成电路、管芯、中介件、封装件、层叠封装(pop)、系统级封装(sip)或片上系统(soc)中的任一集成的各种电子设备。例如,移动电话设备1602、膝上型计算机设备1604、固定位置终端设备1606、可穿戴设备16016或自动车辆1610可以包括如本文中所描述的设备1600。例如,设备1600可以是本文中所描述的任何器件和/或封装件。图16中所图示的电子设备1602、1604、1606和16016以及车辆1610仅是示例性的。其他电子设备也可以以设备1600为特征,包括但不限于设备(例如,电子设备)的组合,包括:移动设备、手持个人通信系统(pcs)单元、诸如个人数字助理之类的便携式数据单元、支持全球定位系统(gps)的设备、导航设备、机顶盒、音乐播放器、视频播放器、娱乐单元、固定位置数据单元(诸如抄表设备)、通信设备、智能电话、平板计算机、计算机、可穿戴设备(例如手表、眼镜)、物联网(iot)

设备、服务器、路由器、在自动车辆(例如,自动驾驶汽车)中实现的电子设备、或存储或检索数据或计算机指令的任何其他设备、或它们的任何组合。

88.在图2-图13、图14a-图14d和/或图15-图16中图示的一个或多个组件、过程、特征和/或功能可以被重新布置和/或组合成单个组件、过程、特征或功能或被体现在若干组件、过程或功能中。在不背离本公开的情况下,还可以添加额外的元件、组件、过程和/或功能。还应注意,图2-图13、图14a-图14d和/或图15-图16及其在本公开中的对应描述不限于管芯和/或ic。在一些实现中,图2-图13、图14a-图14d和/或图15-图16及其对应的描述可以被用来制造、创建、提供和/或生产器件和/或集成器件。在一些实现中,器件可以包括管芯、集成器件、集成无源器件(ipd)、管芯封装、集成电路(ic)器件、器件封装、集成电路(ic)封装、晶片、半导体器件、层叠封装(pop)器件、散热器件和/或中介层。

89.词语“示例性”在本文中被用来意指“用作示例、实例或说明”。在本文中被描述为“示例性”的任何实现或方面不必被解释为比本公开的其他方面更优选或有利。同样,术语“方面”并不要求本公开的所有方面都包括所讨论的特征、优点或操作模式。在本文中使用的术语“耦合”是指两个对象之间的直接或间接耦合。例如,如果对象a与对象b物理接触,而对象b与对象c接触,则对象a和c仍可被视为彼此耦合——即使它们没有彼此直接物理接触。术语“包封”意指对象可以部分包封或完全包封另一对象。还应注意,如在本技术中在一个组件位于另一个组件上方的上下文中使用的术语“上方”可以被用来意指在另一个组件上和/或在另一个组件中(例如,在组件的表面上或嵌入在组件中)的组件。因此,例如,在第二组件上方的第一组件可能意指:(1)第一组件在第二组件上方,但不直接接触第二组件,(2)第一组件在第二组件上(例如,在第二组件的表面上),和/或(3)第一组件在(例如,嵌入在)第二组件中。本公开中使用的术语“大约

‘

x值

’”

或“大致x值”意指“x值”的10%以内。例如,大约1或大致1的值将意指0.9

–

1.1范围内的值。

90.在一些实现中,互连件是器件或封装件的元件或组件,其允许或促进两个点、元件和/或组件之间的电连接。在一些实现中,互连件可以包括迹线、通孔、焊盘、柱、再分布金属层和/或凸块下金属化(ubm)层。互连件可以包括一个或多个金属组件(例如,种子层 金属层)。在一些实现中,互连件是可以被配置来为信号(例如,数据信号、接地或电源)提供电路径的导电材料。互连件可以是电路的一部分。互连件可以包括一个以上的元件或组件。互连件可以由一个或多个互连件定义。不同的实现可以使用相似或不同的工艺来形成互连件。在一些实现中,化学气相沉积(cvd)工艺和/或物理气相沉积(pvd)工艺用于形成互连件。例如,可以使用溅射工艺、喷涂和/或电镀工艺来形成互连件。形成和/或安置包封层的工艺可以包括使用压缩和传递模塑工艺、片材模塑工艺或液体模塑工艺。

91.此外,应注意,在本文中包含的各种公开可以被描述为被描绘为流程图、流程图表、结构图表或框图的过程。尽管流程图可以将操作描述为顺序过程,但是许多操作可以并行或同时执行。此外,可以重新布置操作的顺序。一个过程在其操作完成时终止。

92.在不背离本公开的情况下,本文描述的本公开的各种特征可以在不同的系统中被实现。应当注意,本公开的上述方面仅仅是示例并且不应被解释为限制本公开。本公开的各方面的描述旨在是说明性的,而不旨在限制权利要求的范围。如此,本教导可以容易地被应用于其他类型的装置,并且许多替代、修改和变化对于本领域技术人员来说将是显而易见的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。