1.本发明实施例涉及用于核心装置在安全操作区中操作的虚设装置及其制造方法。

背景技术:

2.本公开大体上涉及半导体装置及其制造方法。具体来说,本公开涉及包含使核心装置能够在安全操作区(soa)中操作的虚设装置的半导体装置及其制造方法。

3.在半导体电路领域中,核心装置表示在较低电压(例如,约0.75伏特(v))下操作的装置。替代地,输入/输出(io)装置表示在较高电压(例如,约1.2v)下操作的装置。一般来说,io装置通常具有较厚氧化物结构且因此具有较佳soa。然而,io装置通常在操作速度、驱动能力等方面具有较低性能。另一方面,核心装置通常在操作速度及驱动能力方面具有较佳性能,但可能无法在与io装置相同的操作电压下操作。因此,核心装置的应用受到限制。

4.随着技术进步,对半导体装置的操作速度的要求愈来愈高。出于这个原因,已进行关于核心装置在与io装置相同的电压下操作的研究。

技术实现要素:

5.根据本发明的一实施例,一种半导体装置包括:核心晶体管,其具有经配置以接收第一电压的漏极;及第一虚设装置,其连接到所述核心晶体管的所述漏极,所述第一虚设装置具有第一虚设晶体管及第二虚设晶体管,其中所述第一虚设晶体管的栅极及源极彼此连接,所述第二虚设晶体管的漏极连接到所述第一虚设晶体管的所述源极,且所述第二虚设晶体管的栅极连接到所述核心晶体管的所述漏极。

6.根据本发明的一实施例,一种半导体装置包括:衬底;连续作用区域,其在所述衬底上;核心晶体管,其具有经配置以接收第一电压的漏极;及虚设装置,其连接到所述核心晶体管的所述漏极,所述虚设装置具有第一虚设晶体管及第二虚设晶体管,其中所述第二虚设晶体管的漏极连接到所述第一虚设晶体管的所述源极,且所述第二虚设晶体管的源极邻近于所述连续作用区域的边缘放置。

7.根据本发明的一实施例,一种用于制造半导体装置的方法包括:形成具有经配置以接收io电压范围内的第一电压的漏极的第一核心晶体管;形成具有第一虚设晶体管及第二虚设晶体管的虚设装置;将所述第二虚设晶体管的漏极连接到所述第一虚设晶体管的源极;及将所述第一虚设晶体管的栅极连接到所述第一核心晶体管的栅极。

附图说明

8.当结合附图阅读时,从以下详细描述更佳地理解本公开的实施例的方面。应注意,根据行业中的标准实践,各种结构不按比例绘制。事实上,为清晰论述,各种结构的尺寸可任意增加或减小。

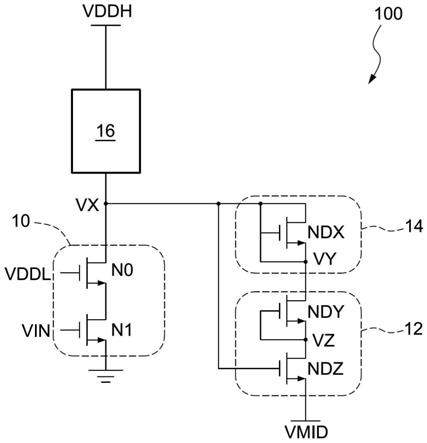

9.图1a说明根据本公开的一些实施例的半导体装置的示意图。

10.图1b说明根据本公开的一些实施例的半导体装置的示意图。

11.图2a说明根据本公开的一些实施例的半导体装置的示意图。

12.图2b说明根据本公开的一些实施例的半导体装置的示意图。

13.图3a说明根据本公开的一些实施例的半导体装置的示意图。

14.图3b说明根据本公开的一些实施例的半导体装置的示意图。

15.图4a说明根据本公开的一些实施例的半导体装置的示意图。

16.图4b说明根据本公开的一些实施例的半导体装置的示意图。

17.图5a、图5b、图5c及图5d各自说明核心装置的布局图案,其中可应用根据本公开的一些实施例的虚设装置。

18.图6a说明根据本公开的一些实施例的半导体装置的布局图案。

19.图6b说明根据本公开的一些实施例的半导体装置的布局图案。

20.图7a说明根据本公开的一些实施例的半导体装置的布局图案。

21.图7b说明根据本公开的一些实施例的半导体装置的布局图案。

22.图8a说明根据本公开的一些实施例的半导体装置的示意图。

23.图8b说明根据本公开的一些实施例的半导体装置的示意图。

24.图9a说明根据本公开的一些实施例的半导体装置的布局图案。

25.图9b说明根据本公开的一些实施例的半导体装置的布局图案。

26.图10说明根据本公开的一些比较实施例的半导体装置的布局图案。

27.图11说明根据本公开的一些实施例的包含用于制造半导体装置的操作的流程图。

具体实施方式

28.以下揭露提供用于实施所提供主题的不同构件的许多不同实施例或实例。在下文描述元件及布置的特定实例以简化本公开。当然,这些仅是实例且不意在是限制性。例如,在以下描述中,在第二构件上方或上形成第一构件可包含其中第一构件及第二构件形成为直接接触的实施例,且还可包含其中额外构件可形成在第一构件与第二构件之间使得第一构件及第二构件可不直接接触的实施例。另外,本公开可在各种实例中重复参考数字及/或字母。这个重复是出于简单及清晰的目的且本身并不指示所论述的各种实施例及/或构形之间的关系。

29.此外,为便于描述,例如“在

…

下面”、“在

…

下方”、“下”、“在

…

上面”、“在

…

上方”、“上”、“在

…

上”等的空间相对术语可在本文中用于描述一个元件或构件与图中说明的另一(些)元件或构件的关系。空间相对术语意在涵盖除在图中描绘的定向以外的使用或操作中的装置的不同定向。设备可以其它方式定向(旋转90度或按其它定向)且因此可同样解释本文中使用的空间相对描述符。

30.如本文中使用,尽管例如“第一”、“第二”及“第三”的术语描述各种元件、组件、区、层及/或区段,然这些元件、组件、区、层及/或区段不应被这些术语限制。这些术语仅可用于将一个元件、组件、区、层或区段彼此区分。例如“第一”、“第二”及“第三”的术语当在本文中使用时并不暗示序列或顺序,除非由上下文明确指示。

31.尽管阐述本公开的广泛范围的数值范围及参数是近似值,但尽可能精确地报告在特定实例中阐述的数值。然而,任何数值固有地含有必然由相应测试测量中发现的标准偏差所引起的某些误差。而且,如本文中使用,术语“基本上”、“近似”及“约”通常表示在可由

所属领域的一般技术人员所预期的值或范围内。替代地,术语“基本上”、“近似”及“约”表示在由所属领域的一般技术人员考虑时在平均值的可接受标准误差内。所属领域的一般技术人员可理解,可接受标准误差可根据不同技术而变化。除了在操作/工作实例中之外,或除非另外明确指定,否则全部数值范围、量、值及百分比(例如针对材料数量、持续时间、温度、操作条件、量的比率及本文中揭示的其类似物的数值范围、量、值及百分比)应被理解为在全部例子中由术语“基本上”、“近似”或“约”修饰。因此,除非相反地指示,否则本公开及所附权利要求书中阐述的数值参数是可视需要变化的近似值。至少,每一数值参数应至少依据所报告的有效数字的数字且通过应用普通舍入技术来解释。本文中可将范围表达为从一个端点到另一端点或在两个端点之间。除非另外指定,否则本文中揭示的全部范围均包含端点。

32.本公开中揭示的技术提供数种解决方案以使施加有io装置的电压范围的核心装置能够在soa中操作。

33.图1a说明根据本公开的一些实施例的半导体装置的示意图。

34.图1a展示装置100。装置100可为电装置。装置100可为半导体装置。装置100可为集成电路(ic)系统。装置100包含核心装置10、虚设装置12、虚设装置14及电路16。

35.核心装置10电连接在电路16与接地(gnd)之间。电路16经配置以接收供应电压vddh。电路16电连接到节点vx。虚设装置12电连接到节点vx。虚设装置12电连接在核心装置10与参考电压vmid之间。虚设装置14电连接到节点vx。虚设装置14电连接到虚设装置12。

36.核心装置10包含晶体管n0及晶体管n1。晶体管n0可被称为核心晶体管。晶体管n1可被称为核心晶体管。晶体管n0可为n沟道mosfet。晶体管n1可为n沟道mosfet。

37.核心装置表示在低于io装置的电压的电压下操作的装置。在一些实施例中,核心装置可在例如约0.75v下操作,而io装置可在例如约1.2v下操作。本公开中提及的核心晶体管可为构成核心装置的一部分的晶体管。核心晶体管可经施加有较低电压,例如约0.75v,而io装置的晶体管可经施加有较高电压,例如约1.2v。

38.晶体管n0的源极电连接到晶体管n1的漏极。晶体管n0的漏极在节点vx处电连接到电路16。晶体管n0的栅极经配置以接收参考电压vddl。晶体管n1的源极电连接到接地(gnd)。晶体管n1的栅极经配置以接收输入电压vin。

39.虚设装置12包含晶体管ndy及晶体管ndz。晶体管ndy可为n沟道mosfet。晶体管ndz可为n沟道mosfet。晶体管ndy的源极在节点vz处电连接到晶体管ndz的漏极。晶体管ndy的源极连接到晶体管ndy的栅极。晶体管ndz的栅极电连接到节点vx。晶体管ndz的源极经配置以接收参考电压vmid。

40.在一些实施例中,晶体管ndy及晶体管n0可为不同类型的晶体管。在一些实施例中,晶体管ndy及晶体管n0可包含不同类型的阈值电压。在一些实施例中,晶体管ndy可包含标准阈值电压,而晶体管n0可包含超低泄漏阈值电压,或反之亦然。

41.在一些实施例中,晶体管ndy及晶体管ndz可为不同类型的晶体管。在一些实施例中,晶体管ndy及晶体管ndz可包含不同类型的阈值电压。在一些实施例中,晶体管ndy可包含标准阈值电压,而晶体管ndz可包含超低泄漏阈值电压,或反之亦然。

42.虚设装置14包含晶体管ndx。晶体管ndx可为n沟道mosfet。晶体管ndx的栅极、源极及漏极连接在一起。晶体管ndx的栅极、源极及漏极电连接到节点vx。晶体管ndx的栅极、源

极及漏极在节点vy处电连接到晶体管ndy的漏极。

43.针对半导体装置(例如bjt、mosfet、晶闸管或igbt),安全操作区(soa)被称为装置可预期在其上操作而不会自损的电压及电流条件。在一些实施例中,针对mosfet,安全操作区(soa)可为其中晶体管的电压vgs、vds及vgd不超过预定电压的条件。在一些实施例中,安全操作区(soa)可为其中晶体管的电压vgs、vds及vgd低于0.96v的条件。

44.将如下般描述装置100的操作。在一些实施例中,供应电压vddh可为约1.2v。在一些实施例中,参考电压vddl可为约0.75v。在一些实施例中,参考电压vmid可为约0.75v。在一些实施例中,晶体管n1的输入电压vin的范围可为约从0v到0.75v。在一些实施例中,参考电压vddl可相同于参考电压vmid。在一些实施例中,参考电压vddl可不同于参考电压vmid。晶体管n1的输入电压vin可控制晶体管n1接通或关断。

45.在其中晶体管n1接通的条件下,由晶体管n1驱动的电流将拉低节点vx处的电压,且因此晶体管ndz将关断。同时,晶体管ndy由于在晶体管ndy的栅极与源极之间不存在电压差而关断,且晶体管ndx由于相同原因而关断。由于晶体管ndx、ndy及ndz全部关断,当晶体管n1接通时,虚设装置12及虚设装置14将仅消耗非常有限的电流,例如泄漏电流。另外,晶体管n0、n1、ndx、ndy、ndz将全部在soa中。

46.当晶体管n1接通时,施加到晶体管n1的栅极的电压可为0.75v。针对晶体管n0,可将约0.75v的参考电压vddl施加到晶体管n0的栅极,且由于其固有的源极跟随电路操作,晶体管n0的源极处的电压将跟踪电压vddl。即,晶体管n0的源极处的电压将不超过电压vddl。因此,晶体管n1的vgs、vds及vgd将全部低于预定电压,例如0.96v。另外,晶体管n0的vgs、vds及vgd将全部低于预定电压,例如0.96v。

47.在其中晶体管n1关断的条件下,节点vx处的电压将被上拉到几乎相同于供应电压vddh。此时,晶体管ndz将接通且接着将参考电压vmid传递到晶体管ndy的栅极/源极。由于晶体管ndy的vgs为零,晶体管ndy关断。由于晶体管ndy的vgs为零,晶体管ndx关断。晶体管ndy及晶体管ndz两者将在soa中。另外,晶体管n0、n1及ndx将全部在soa中。

48.当晶体管n1关断时,施加到晶体管n1的栅极的电压可为0v。针对晶体管n0,可将约0.75v的参考电压vddl施加到晶体管n0的栅极,且由于其固有的源极跟随电路操作,晶体管n0的源极处的电压将跟踪电压vddl。即,晶体管n0的源极处的电压将不超过电压vddl。因此,晶体管n1的vgs、vds及vgd将全部低于预定电压,例如0.96v。另外,晶体管n0的vgs、vds及vgd将全部低于预定电压,例如0.96v。

49.应注意,当晶体管n1关断时,节点vx将被上拉到供应电压vddh(例如,1.2v)。即,在装置100的操作期间,核心装置10可经施加有io电压范围内的电压。在一些实施例中,本公开中提及的io电压可大于或等于约1.2v。在一些实施例中,本公开中提及的io电压可大于或等于约1.8v。如在先前段落中论述,虚设装置12的配置使核心装置10的晶体管n0及n1能够在soa中操作。另外,虚设装置12及虚设装置14中的全部晶体管将在soa中操作。

50.针对包含n沟道mosfet的虚设装置12及14,参考电压vmid可由以下方程定义:

51.vx(max)

–

vmid《vgs/vds/vgd的soa限制(方程1)

52.vx(max)表示节点vx处的电压的最大值。例如,如果施加到装置100的供应电压vddh为1.2v,那么vx(max)为1.2v。

53.图1b说明根据本公开的一些实施例的半导体装置的示意图。

54.图1b展示装置100'。装置100'可为电装置。装置100'可为半导体装置。装置100'可为集成电路(ic)系统。装置100'包含核心装置10'、虚设装置12'、虚设装置14'及电路16。

55.核心装置10'电连接在电路16与供应电压vddh之间。电路16电连接在核心装置10'与接地(gnd)之间。核心装置10'及电路16在节点vx处电连接。虚设装置12'电连接到节点vx。虚设装置12'电连接在核心装置10'与参考电压vmid之间。虚设装置14'电连接到节点vx。虚设装置14'电连接到虚设装置12'。

56.核心装置10'包含晶体管p0及晶体管p1。晶体管p0可被称为核心晶体管。晶体管p1可被称为核心晶体管。晶体管p0可为p沟道mosfet。晶体管n1可为p沟道mosfet。本公开中提及的核心晶体管可为构成核心装置的一部分的晶体管。

57.晶体管p0的源极电连接到晶体管p1的漏极。晶体管p0的漏极在节点vx处电连接到电路16。晶体管p0的栅极经配置以接收参考电压vssh。晶体管p1的源极电连接到供应电压vddh。晶体管p1的栅极经配置以接收输入电压vhin。

58.虚设装置12'包含晶体管pdy及晶体管pdz。晶体管pdy可为p沟道mosfet。晶体管pdz可为p沟道mosfet。晶体管pdy的源极电连接到晶体管pdz的漏极。晶体管pdy的源极连接到晶体管pdy的栅极。晶体管pdz的栅极电连接到节点vx。晶体管pdz的源极经配置以接收参考电压vmid。

59.在一些实施例中,晶体管pdy及晶体管p0可为不同类型的晶体管。在一些实施例中,晶体管pdy及晶体管p0可包含不同类型的阈值电压。在一些实施例中,晶体管pdy可包含标准阈值电压,而晶体管p0可包含超低泄漏阈值电压,或反之亦然。

60.在一些实施例中,晶体管pdy及晶体管pdz可为不同类型的晶体管。在一些实施例中,晶体管pdy及晶体管pdz可包含不同类型的阈值电压。在一些实施例中,晶体管pdy可包含标准阈值电压,而晶体管pdz可包含超低泄漏阈值电压,或反之亦然。

61.虚设装置14'包含晶体管pdx。晶体管pdx可为p沟道mosfet。晶体管pdx的栅极、源极及漏极连接在一起。晶体管pdx的栅极、源极及漏极电连接到节点vx。

62.装置100'的操作与装置100的操作类似。在一些实施例中,供应电压vddh可为约1.2v。在一些实施例中,参考电压vssh可为约0.45v。在一些实施例中,参考电压vmid可为约0.45v。在一些实施例中,参考电压vssh可不同于参考电压vmid。在一些实施例中,晶体管p1的输入电压vhin的范围可为从约0.45v到1.2v。晶体管p1的输入电压vhin可控制晶体管p1接通或关断。

63.在其中晶体管p1接通的条件下,由晶体管p1驱动的电流将上拉节点vx处的电压,且因此晶体管pdz将关断。同时,晶体管pdy由于在晶体管pdy的栅极与源极之间不存在电压差而关断,且晶体管pdx由于相同原因而关断。由于晶体管pdx、pdy及pdz全部关断,当晶体管p1接通时,虚设装置12'及虚设装置14'将仅消耗非常有限的电流,例如泄漏电流。另外,由于晶体管p0、p1、pdx、pdy、pdz的vgs、vds及vgd将全部低于预定电压(例如,0.96v),因此晶体管p0、p1、pdx、pdy、pdz将全部在soa中。

64.在其中晶体管p1关断的条件下,节点vx处的电压将被拉低到几乎相同于接地(gnd)。此时,晶体管pdz将接通且接着将参考电压vmid传递到晶体管pdy的栅极/源极。由于晶体管ndy的vgs为零,晶体管pdy关断。由于晶体管ndy的vgs为零,晶体管pdx关断。另外,由于晶体管p0、p1、pdx、pdy及pdz的vgs、vds及vgd将全部低于预定电压(例如,0.96v),因此晶

体管p0、p1、pdx、pdy及pdz将全部在soa中。

65.应注意,当晶体管p1接通时,节点vx将被上拉到供应电压vddh(例如,1.2v)。即,在装置100'的操作期间,核心装置10'可经施加有io电压范围内的电压。如先前段落中论述,虚设装置12'的配置使核心装置10'的晶体管p0及p1能够在soa中操作。另外,虚设装置12'及虚设装置14'中的全部晶体管将在soa中操作。

66.针对包含p沟道mosfet的虚设装置12'及14',参考电压vmid可由以下方程定义:

67.vmid《vgs/vds/vgd的soa限制(方程2)

68.图2a说明根据本公开的一些实施例的半导体装置的示意图。

69.图2a展示装置110。装置110可为电装置。装置110可为半导体装置。装置110可为集成电路(ic)系统。装置110包含核心装置20、虚设装置22、虚设装置24及电路16。

70.核心装置20电连接在电路16与接地(gnd)之间。电路16经配置以接收供应电压vddh。电路16电连接到节点vx。虚设装置24电连接到节点vx。虚设装置24电连接到虚设装置22。虚设装置22电连接在虚设装置24与参考电压vmid之间。

71.核心装置20包含晶体管n0及晶体管n1。晶体管n0可被称为核心晶体管。晶体管n1可被称为核心晶体管。晶体管n0可为n沟道mosfet。晶体管n1可为n沟道mosfet。本公开中提及的核心晶体管可为构成核心装置的一部分的晶体管。

72.晶体管n0的源极电连接到晶体管n1的漏极。晶体管n0的漏极在节点vx处电连接到电路16。晶体管n0的栅极经配置以接收参考电压vddl。晶体管n1的源极电连接到接地(gnd)。晶体管n1的栅极经配置以接收输入电压vin。

73.虚设装置22包含晶体管ndy及晶体管ndz。晶体管ndy可为n沟道mosfet。晶体管ndz可为n沟道mosfet。晶体管ndy的源极电连接到晶体管ndz的漏极。晶体管ndy的源极连接到晶体管ndy的栅极。晶体管ndz的栅极电连接到晶体管ndz的源极。晶体管ndz的源极经配置以接收参考电压vmid。

74.虚设装置24包含晶体管ndx。晶体管ndx可为n沟道mosfet。晶体管ndx的栅极、源极及漏极连接在一起。晶体管ndx的栅极、源极及漏极电连接到节点vx。晶体管ndx的栅极、源极及漏极电连接到晶体管ndy的漏极。

75.将如下般描述装置110的操作。在一些实施例中,供应电压vddh可为约1.2v。在一些实施例中,参考电压vddl可为约0.75v。在一些实施例中,参考电压vmid可为约0.75v。在一些实施例中,参考电压vddl可相同于参考电压vmid。在一些实施例中,参考电压vddl可不同于参考电压vmid。在一些实施例中,晶体管n1的输入电压vin的范围可为从约0v到0.75v。晶体管n1的输入电压vin可控制晶体管n1接通或关断。

76.在其中晶体管n1接通的条件下,由晶体管n1驱动的电流将拉低节点vx处的电压。同时,晶体管ndx、ndy及ndz将全部处于关断状态,这是因为它们的栅极与源极之间不存在电压差。由于晶体管ndx、ndy及ndz全部关断,当晶体管n1接通时,虚设装置22及虚设装置24将仅消耗非常有限的电流,例如泄漏电流。另外,晶体管n0、n1、ndx、ndy、ndz将全部在soa中。

77.在其中晶体管n1关断的条件下,节点vx处的电压将被上拉到几乎相同于供应电压vddh。此时,晶体管ndx、ndy及ndz将全部处于关断状态,这是因为它们的栅极与源极之间不存在电压差。晶体管ndy及晶体管ndz两者将在soa中。另外,晶体管n0、n1及ndx将全部在soa

中。

78.针对包含n沟道mosfet的虚设装置22及24,参考电压vmid可由方程1定义。

79.图2b说明根据本公开的一些实施例的半导体装置的示意图。

80.图2b展示装置110'。装置110'可为电装置。装置110'可为半导体装置。装置110'可为集成电路(ic)系统。装置110'包含核心装置20'、虚设装置22'、虚设装置24'及电路16。

81.核心装置20'电连接在电路16与供应电压vddh之间。电路16电连接在核心装置20'与接地(gnd)之间。核心装置20'及电路16在节点vx处电连接。虚设装置24'电连接到节点vx。虚设装置24'电连接到虚设装置22'。虚设装置22'电连接在核心装置20'与参考电压vmid之间。

82.核心装置20'包含晶体管p0及晶体管p1。晶体管p0可被称为核心晶体管。晶体管p1可被称为核心晶体管。晶体管p0可为p沟道mosfet。晶体管n1可为p沟道mosfet。本公开中提及的核心晶体管可为构成核心装置的一部分的晶体管。

83.晶体管p0的源极电连接到晶体管p1的漏极。晶体管p0的漏极在节点vx处电连接到电路16。晶体管p0的栅极经配置以接收参考电压vssh。晶体管p1的源极电连接到供应电压vddh。晶体管p1的栅极经配置以接收输入电压vhin。

84.虚设装置22'包含晶体管pdy及晶体管pdz。晶体管pdy可为p沟道mosfet。晶体管pdz可为p沟道mosfet。晶体管pdy的源极电连接到晶体管pdz的漏极。晶体管pdy的源极连接到晶体管pdy的栅极。晶体管pdz的源极连接到晶体管pdz的栅极。晶体管pdz的源极经配置以接收参考电压vmid。

85.虚设装置24'包含晶体管pdx。晶体管pdx可为p沟道mosfet。晶体管pdx的栅极、源极及漏极连接在一起。晶体管pdx的栅极、源极及漏极电连接到节点vx。

86.装置110'的操作与装置110的操作类似。在一些实施例中,供应电压vddh可为约1.2v。在一些实施例中,参考电压vssh可为约0.45v。在一些实施例中,参考电压vmid可为约0.45v。在一些实施例中,参考电压vssh可不同于参考电压vmid。在一些实施例中,晶体管p1的输入电压vhin的范围可为从约0.45v到1.2v。晶体管p1的输入电压vhin可控制晶体管p1接通或关断。

87.在其中晶体管p1接通的条件下,由晶体管p1驱动的电流将上拉节点vx处的电压。同时,晶体管pdx、pdy及pdz将全部处于关断状态,这是因为它们的栅极与源极之间不存在电压差。由于晶体管pdx、pdy及pdz全部关断,当晶体管p1接通时,虚设装置22'及虚设装置24'将仅消耗非常有限的电流,例如泄漏电流。另外,由于晶体管p0、p1、pdx、pdy、pdz的vgs、vds及vgd将全部低于预定电压(例如,0.96v),因此晶体管p0、p1、pdx、pdy、pdz将全部在soa中。

88.在其中晶体管p1关断的条件下,节点vx处的电压将被拉低到几乎相同于接地(gnd)。此时,晶体管pdx、pdy及pdz将全部处于关断状态,这是因为它们的栅极与源极之间不存在电压差。晶体管pdy及晶体管pdz两者将在soa中。另外,晶体管p0、p1及pdx将全部在soa中。

89.针对包含p沟道mosfet的虚设装置22'及24',参考电压vmid可由方程2定义。

90.图3a说明根据本公开的一些实施例的半导体装置的示意图。

91.图3a展示装置120。装置120可为电装置。装置120可为半导体装置。装置120可为集

成电路(ic)系统。装置120包含核心装置30、虚设装置32、虚设装置34及电路16。虚设装置32包含虚设电路32a及32b。

92.核心装置30电连接在电路16与接地(gnd)之间。电路16经配置以接收供应电压vddh。电路16电连接到节点vx。虚设装置32电连接到节点vx。虚设装置32电连接在核心装置30与参考电压vmid之间。虚设装置34电连接到节点vx。虚设装置34电连接到虚设装置32。

93.虚设电路32a电连接在虚设装置34与虚设电路32b之间。虚设电路32b电连接到虚设装置34。虚设电路32b电连接在参考电压vmid与节点vx之间。

94.核心装置30包含晶体管n0及晶体管n1。晶体管n0可被称为核心晶体管。晶体管n1可被称为核心晶体管。晶体管n0可为n沟道mosfet。晶体管n1可为n沟道mosfet。本公开中提及的核心晶体管可为构成核心装置的一部分的晶体管。

95.晶体管n0的源极电连接到晶体管n1的漏极。晶体管n0的漏极在节点vx处电连接到电路16。晶体管n0的栅极经配置以接收参考电压vddl。晶体管n1的源极电连接到接地(gnd)。晶体管n1的栅极经配置以接收输入电压vin。

96.虚设电路32a包含多个晶体管ndy1、ndy2、ndy3、

…

及ndyn。数字“n”是正整数。晶体管ndy1、ndy2、ndy3、

…

及ndyn中的每一者可为n沟道mosfet。

97.晶体管ndy1的源极及栅极连接在一起。晶体管ndy1的源极电连接到晶体管ndy2的漏极。晶体管ndy2、ndy3、

…

及ndyn全部包含与晶体管ndy1相同的配置。晶体管ndyn的源极电连接到虚设电路32b。晶体管ndyn的源极电连接到晶体管ndz1的漏极。

98.虚设电路32b包含多个晶体管ndz1、ndz2、ndz3、

…

及ndzn。数字“n”是正整数。晶体管ndz1、ndz2、ndz3、

…

及ndzn中的每一者可为n沟道mosfet。晶体管ndz1的源极电连接到晶体管ndz2的漏极。晶体管ndz2、ndz3、

…

及ndzn全部包含与晶体管ndz1相同的配置。晶体管ndz1、ndz2、ndz3、

…

及ndzn的栅极全部连接到节点vx。晶体管ndz1、ndz2、ndz3、

…

及ndzn可串联连接,其中共享它们的栅极。

99.虚设装置34包含晶体管ndx。晶体管ndx可为n沟道mosfet。晶体管ndx的栅极、源极及漏极连接在一起。晶体管ndx的栅极、源极及漏极电连接到节点vx。

100.装置120的操作与装置100的操作类似。在一些实施例中,供应电压vddh可为约1.2v。在一些实施例中,参考电压vddl可为约0.75v。在一些实施例中,参考电压vmid可为约0.75v。在一些实施例中,参考电压vddl可相同于参考电压vmid。在一些实施例中,参考电压vddl可不同于参考电压vmid。在一些实施例中,晶体管n1的输入电压vin的范围可为从约0v到0.75v。晶体管n1的输入电压vin可控制晶体管n1接通或关断。

101.在其中晶体管n1接通的条件下,由晶体管n1驱动的电流将拉低节点vx处的电压。同时,晶体管ndx、ndy1到ndyn及ndz1到ndzn将全部处于关断状态,这是因为它们的栅极与源极之间不存在电压差。因此,当晶体管n1接通时,虚设装置32及虚设装置34将仅消耗非常有限的电流,例如泄漏电流。另外,核心装置30、虚设装置32及虚设装置34的全部晶体管将在soa中。

102.应注意,串联连接的晶体管ndy1、ndy2、ndy3、

…

及ndyn将促进泄漏电流的减少,串联连接的晶体管ndz1、ndz2、ndz3、

…

及ndzn也将促进泄漏电流的减少。因此,与图1a中展示的虚设装置12相比,图3a的虚设装置32将展现较小泄漏电流。

103.在其中晶体管n1关断的条件下,节点vx处的电压将被上拉到几乎相同于供应电压

vddh。此时,晶体管ndx、ndy1到ndyn及ndz1到ndzn将全部处于关断状态,这是因为它们的栅极与源极之间不存在电压差。另外,核心装置30、虚设装置32及虚设装置34的全部晶体管将在soa中。

104.针对包含n沟道mosfet的虚设装置32及34,参考电压vmid可由方程1定义。

105.图3b说明根据本公开的一些实施例的半导体装置的示意图。

106.图3b展示装置120'。装置120'可为电装置。装置120'可为半导体装置。装置120'可为集成电路(ic)系统。装置120'包含核心装置30'、虚设装置32'、虚设装置34'及电路16'。虚设装置32'包含虚设电路32a'及32b'。

107.核心装置30'电连接在电路16与供应电压vddh之间。电路16电连接在接地(gnd)与节点vx之间。虚设装置32'电连接到节点vx。虚设装置32'电连接在核心装置30与参考电压vmid之间。虚设装置34'电连接到节点vx。虚设装置34'电连接到虚设装置32'。

108.虚设电路32a'电连接在虚设装置34'与虚设电路32b'之间。虚设电路32b'电连接到虚设装置34'。虚设电路32b'电连接在参考电压vmid与节点vx之间。

109.核心装置30'包含晶体管p0及晶体管p1。晶体管p0可被称为核心晶体管。晶体管p1可被称为核心晶体管。晶体管p0可为p沟道mosfet。晶体管p1可为p沟道mosfet。本公开中提及的核心晶体管可为构成核心装置的一部分的晶体管。

110.晶体管p0的源极电连接到晶体管p1的漏极。晶体管p0的漏极在节点vx处电连接到电路16。晶体管p0的栅极经配置以接收参考电压vssh。晶体管p1的源极电连接到供应电压vddh。晶体管p1的栅极经配置以接收输入电压vhin。

111.虚设电路32a'包含多个晶体管pdy1、pdy2、pdy3、

…

及pdyn。数字“n”是正整数。晶体管pdy1、pdy2、pdy3、

…

及pdyn中的每一者可为p沟道mosfet。

112.晶体管pdy1的源极及栅极连接在一起。晶体管pdy1的源极电连接到晶体管pdy2的漏极。晶体管pdy2、pdy3、

…

及pdyn全部包含与晶体管pdy1相同的配置。晶体管pdyn的源极电连接到虚设电路32b'。晶体管pdyn的源极电连接到晶体管pdz1的漏极。

113.虚设电路32b'包含多个晶体管pdz1、pdz2、pdz3、

…

及pdzn。数字“n”是正整数。晶体管pdz1、pdz2、pdz3、

…

及pdzn中的每一者可为p沟道mosfet。晶体管pdz1的源极电连接到晶体管pdz2的漏极。晶体管pdz2、pdz3、

…

及pdzn全部包含与晶体管pdz1相同的配置。晶体管pdz1、pdz2、pdz3、

…

及pdzn的栅极全部连接到节点vx。晶体管pdz1、pdz2、pdz3、

…

及pdzn可串联连接,其中共享它们的栅极。

114.虚设装置34'包含晶体管pdx。晶体管pdx可为p沟道mosfet。晶体管pdx的栅极、源极及漏极连接在一起。晶体管pdx的栅极、源极及漏极电连接到节点vx。

115.装置120'的操作与装置100'的操作类似。在一些实施例中,供应电压vddh可为约1.2v。在一些实施例中,参考电压vssh可为约0.45v。在一些实施例中,参考电压vmid可为约0.45v。在一些实施例中,参考电压vssh可不同于参考电压vmid。在一些实施例中,晶体管p1的输入电压vhin的范围可为从约0.45v到1.2v。晶体管p1的输入电压vhin可控制晶体管p1接通或关断。

116.在其中晶体管p1接通的条件下,由晶体管p1驱动的电流将上拉节点vx处的电压。同时,晶体管pdx、pdy1到pdyn及pdz1到pdzn将全部处于关断状态,这是因为它们的栅极与源极之间不存在电压差。因此,当晶体管p1接通时,虚设装置32'及虚设装置34'将仅消耗非

常有限的电流,例如泄漏电流。另外,核心装置30'、虚设装置32'及虚设装置34'的全部晶体管将在soa中。

117.应注意,串联连接的晶体管pdy1、pdy2、pdy3、

…

及pdyn将促进泄漏电流的减少,串联连接的晶体管pdz1、pdz2、pdz3、

…

及pdzn也将促进泄漏电流的减少。因此,与图1b中展示的虚设装置12'相比,图3b的虚设装置32'将展现较小泄漏电流。

118.在其中晶体管p1关断的条件下,节点vx处的电压将被拉低到几乎相同于接地(gnd)。此时,晶体管pdx、pdy1到pdyn及pdz1到pdzn将全部处于关断状态,这是因为它们的栅极与源极之间不存在电压差。另外,核心装置30'、虚设装置32'及虚设装置34'的全部晶体管将在soa中。

119.针对包含p沟道mosfet的虚设装置32'及34',参考电压vmid可由方程2定义。

120.图4a说明根据本公开的一些实施例的半导体装置的示意图。

121.图4a展示装置130。装置130可为电装置。装置130可为半导体装置。装置130可为集成电路(ic)系统。装置130包含核心装置40、虚设装置42、虚设装置44及电路16。虚设装置42包含虚设电路42a及42b。

122.核心装置40电连接在电路16与接地(gnd)之间。电路16经配置以接收供应电压vddh。电路16电连接到节点vx。虚设装置42电连接到节点vx。虚设装置42电连接在核心装置40与参考电压vmid之间。虚设装置44电连接到节点vx。虚设装置44电连接到虚设装置42。

123.虚设电路42a电连接在虚设装置44与虚设电路42b之间。虚设电路42b电连接到虚设装置44。虚设电路42b电连接在参考电压vmid与节点vx之间。

124.核心装置40包含晶体管n0及晶体管n1。晶体管n0可被称为核心晶体管。晶体管n1可被称为核心晶体管。晶体管n0可为n沟道mosfet。晶体管n1可为n沟道mosfet。本公开中提及的核心晶体管可为构成核心装置的一部分的晶体管。

125.晶体管n0的源极电连接到晶体管n1的漏极。晶体管n0的漏极在节点vx处电连接到电路16。晶体管n0的栅极经配置以接收参考电压vddl。晶体管n1的源极电连接到接地(gnd)。晶体管n1的栅极经配置以接收输入电压vin。

126.虚设电路42a包含多个晶体管ndy1、ndy2、ndy3、

…

及ndyn。数字“n”是正整数。晶体管ndy1、ndy2、ndy3、

…

及ndyn中的每一者可为n沟道mosfet。

127.晶体管ndy1的源极电连接到晶体管ndy2的漏极,且晶体管ndy2的源极电连接到晶体管ndy3的漏极,依此类推。晶体管ndy1、ndy2、ndy3、

…

及ndyn的栅极连接在一起。晶体管ndy1、ndy2、ndy3、

…

及ndyn可串联连接,其中共享它们的栅极。晶体管ndyn的源极及栅极连接在一起。晶体管ndyn的源极电连接到虚设电路42b。晶体管ndyn的源极电连接到晶体管ndz1的漏极。

128.虚设电路42b包含多个晶体管ndz1、ndz2、ndz3、

…

及ndzn。数字“n”是正整数。晶体管ndz1、ndz2、ndz3、

…

及ndzn中的每一者可为n沟道mosfet。晶体管ndz1的源极电连接到晶体管ndz2的漏极,且晶体管ndz2的源极电连接到晶体管ndz3的漏极,依此类推。晶体管ndz1、ndz2、ndz3、

…

及ndzn的栅极全部连接到节点vx。晶体管ndz1、ndz2、ndz3、

…

及ndzn可串联连接,其中共享它们的栅极。

129.虚设装置34包含晶体管ndx。晶体管ndx可为n沟道mosfet。晶体管ndx的栅极、源极及漏极连接在一起。晶体管ndx的栅极、源极及漏极电连接到节点vx。

130.装置130的操作与装置100的操作类似。在一些实施例中,供应电压vddh可为约1.2v。在一些实施例中,参考电压vddl可为约0.75v。在一些实施例中,参考电压vmid可为约0.75v。在一些实施例中,参考电压vddl可相同于参考电压vmid。在一些实施例中,参考电压vddl可不同于参考电压vmid。在一些实施例中,晶体管n1的输入电压vin的范围可为从约0v到0.75v。晶体管n1的输入电压vin可控制晶体管n1接通或关断。

131.在其中晶体管n1接通的条件下,由晶体管n1驱动的电流将拉低节点vx处的电压。同时,晶体管ndx、ndy1到ndyn及ndz1到ndzn将全部处于关断状态,这是因为它们的栅极与源极之间不存在电压差。因此,当晶体管n1接通时,虚设装置42及虚设装置44将仅消耗非常有限的电流,例如泄漏电流。另外,核心装置40、虚设装置42及虚设装置44的全部晶体管将在soa中。

132.应注意,串联连接的晶体管ndy1、ndy2、ndy3、

…

及ndyn将促进泄漏电流的减少,串联连接的晶体管ndz1、ndz2、ndz3、

…

及ndzn也将促进泄漏电流的减少。因此,与图1a中展示的虚设装置12相比,图4a的虚设装置42将展现较小泄漏电流。

133.在其中晶体管n1关断的条件下,节点vx处的电压将被上拉到几乎相同于供应电压vddh。此时,晶体管ndx、ndy1到ndyn及ndz1到ndzn将全部处于关断状态,这是因为它们的栅极与源极之间不存在电压差。另外,核心装置40、虚设装置42及虚设装置44的全部晶体管将在soa中。

134.针对包含n沟道mosfet的虚设装置42及44,参考电压vmid可由方程1定义。

135.图4b说明根据本公开的一些实施例的半导体装置的示意图。

136.图4b展示装置130'。装置130'可为电装置。装置130'可为半导体装置。装置130'可为集成电路(ic)系统。装置130'包含核心装置40'、虚设装置42'、虚设装置44'及电路16'。虚设装置42'包含虚设电路42a'及42b'。

137.核心装置40'电连接在电路16与供应电压vddh之间。电路16电连接在接地(gnd)与节点vx之间。虚设装置42'电连接到节点vx。虚设装置42'电连接在核心装置40与参考电压vmid之间。虚设装置44'电连接到节点vx。虚设装置44'电连接到虚设装置42'。

138.虚设电路42a'电连接在虚设装置44'与虚设电路42b'之间。虚设电路42b'电连接到虚设装置44'。虚设电路42b'电连接在参考电压vmid与节点vx之间。

139.核心装置40'包含晶体管p0及晶体管p1。晶体管p0可被称为核心晶体管。晶体管p1可被称为核心晶体管。晶体管p0可为p沟道mosfet。晶体管p1可为p沟道mosfet。本公开中提及的核心晶体管可为构成核心装置的一部分的晶体管。

140.晶体管p0的源极电连接到晶体管p1的漏极。晶体管p0的漏极在节点vx处电连接到电路16。晶体管p0的栅极经配置以接收参考电压vssh。晶体管p1的源极电连接到供应电压vddh。晶体管p1的栅极经配置以接收输入电压vhin。

141.虚设电路42a'包含多个晶体管pdy1、pdy2、pdy3、

…

及pdyn。数字“n”是正整数。晶体管pdy1、pdy2、pdy3、

…

及pdyn中的每一者可为p沟道mosfet。

142.晶体管pdy1的源极及栅极连接在一起。晶体管pdy1的源极电连接到晶体管pdy2的漏极,且晶体管pdy2的源极电连接到晶体管pdy3的漏极,依此类推。晶体管pdy1、pdy2、pdy3、

…

及pdyn可串联连接,其中共享它们的栅极。晶体管pdyn的源极电连接到虚设电路42b'。晶体管pdyn的源极电连接到晶体管pdz1的漏极。晶体管pdyn的源极及栅极连接在一

起。

143.虚设电路42b'包含多个晶体管pdz1、pdz2、pdz3、

…

及pdzn。数字“n”是正整数。晶体管pdz1、pdz2、pdz3、

…

及pdzn中的每一者可为p沟道mosfet。晶体管pdz1的源极电连接到晶体管pdz2的漏极。晶体管pdz2、pdz3、

…

及pdzn全部包含与晶体管pdz1相同的配置。晶体管pdz1、pdz2、pdz3、

…

及pdzn的栅极全部连接到节点vx。晶体管pdz1、pdz2、pdz3、

…

及pdzn可串联连接,其中共享它们的栅极。

144.虚设装置44'包含晶体管pdx。晶体管pdx可为p沟道mosfet。晶体管pdx的栅极、源极及漏极连接在一起。晶体管pdx的栅极、源极及漏极电连接到节点vx。

145.装置130'的操作与装置100'的操作类似。在一些实施例中,供应电压vddh可为约1.2v。在一些实施例中,参考电压vssh可为约0.45v。在一些实施例中,参考电压vmid可为约0.45v。在一些实施例中,参考电压vssh可不同于参考电压vmid。在一些实施例中,晶体管p1的输入电压vhin的范围可为从约0.45v到1.2v。晶体管p1的输入电压vhin可控制晶体管p1接通或关断。

146.在其中晶体管p1接通的条件下,由晶体管p1驱动的电流将上拉节点vx处的电压。同时,晶体管pdx、pdy1到pdyn及pdz1到pdzn将全部处于关断状态,这是因为它们的栅极与源极之间不存在电压差。因此,当晶体管p1接通时,虚设装置42'及虚设装置44'将仅消耗非常有限的电流,例如泄漏电流。另外,核心装置40'、虚设装置42'及虚设装置44'的全部晶体管将在soa中。

147.应注意,串联连接的晶体管pdy1、pdy2、pdy3、

…

及pdyn将促进泄漏电流的减少,串联连接的晶体管pdz1、pdz2、pdz3、

…

及pdzn也将促进泄漏电流的减少。因此,与图1b中展示的虚设装置12'相比,图4b的虚设装置42'将展现较小泄漏电流。

148.在其中晶体管p1关断的条件下,节点vx处的电压将被拉低到几乎相同于接地(gnd)。此时,晶体管pdx、pdy1到pdyn及pdz1到pdzn将全部处于关断状态,这是因为它们的栅极与源极之间不存在电压差。另外,核心装置40'、虚设装置42'及虚设装置44'的全部晶体管将在soa中。

149.针对包含p沟道mosfet的虚设装置42'及44',参考电压vmid可由方程2定义。

150.根据图1a、图1b、图2a、图2b、图3a、图3b、图4a及图4b描述的虚设装置可广泛应用于潜在地在io电压范围内操作的核心装置。如图1a、图1b、图2a、图2b、图3a、图3b、图4a及图4b中展示的电路结构/配置可广泛应用于潜在地在io电压范围内操作的核心装置。

151.下文表1展示根据本公开的一些实施例的虚设装置可应用于的各种条件。可分别在图5a、图5b、图5c及图5d中说明条件1、2、3及4的布局图案。

152.[0153][0154]

表1

[0155]

图5a、图5b、图5c及图5d各自说明核心装置的布局图案,其中可应用根据本公开的一些实施例的虚设装置。

[0156]

图5a展示核心晶体管n0及n1的布局150。布局150包含作用区域150a。作用区域150a可被称为连续作用区域。核心晶体管n1可包含偶数指状物。即,核心晶体管n1可包含偶数个栅极n1_g。核心晶体管n0可包含偶数指状物。即,核心晶体管n0可包含偶数个栅极n0_g。

[0157]

图5a中展示的区域150d表示其中虚设装置可定位于布局150上的区域。

[0158]

核心晶体管n0的漏极(d)在节点vx处连接到虚设装置(即,区域150d)。再次参考图1a,节点vx可经施加有io电压范围内的电压(例如,1.2v)。因此,虚设装置的端部(即,区域150d)连接到io电压范围内的电压(例如,1.2v)。针对其中虚设装置的端部连接到io电压的布局,可应用如图1a、图1b、图2a、图2b、图3a、图3b、图4a及图4b中展示的电路结构/配置,以便使核心装置及虚设装置在soa中工作。

[0159]

图5b展示核心晶体管n0及n1的布局152。布局152包含作用区域152a。作用区域152a可被称为连续作用区域。核心晶体管n1可包含奇数指状物。即,核心晶体管n1可包含偶数个栅极n1_g。核心晶体管n0可包含奇数指状物。即,核心晶体管n0可包含奇数个栅极n0_g。

[0160]

图5b中展示的区域152d表示其中虚设装置可定位于布局152上的区域。

[0161]

核心晶体管n0的漏极(d)在节点vx处连接到虚设装置(即,区域152d)。再次参考图1a,节点vx可经施加有io电压范围内的电压(例如,1.2v)。因此,虚设装置的端部(即,区域152d)连接到io电压范围内的电压(例如,1.2v)。针对其中虚设装置的端部连接到io电压的布局,可应用如图1a、图1b、图2a、图2b、图3a、图3b、图4a及图4b中展示的电路结构/配置,以便使核心装置及虚设装置在soa中工作。

[0162]

图5c展示核心晶体管n0及n1的布局154。布局152包含作用区域154a。作用区域154a可被称为连续作用区域。核心晶体管n1可包含偶数指状物。即,核心晶体管n1可包含偶数个栅极n1_g。核心晶体管n0可包含奇数指状物。即,核心晶体管n0可包含奇数个栅极n0_g。

[0163]

图5c中展示的区域154d表示其中虚设装置可定位于布局154上的区域。

[0164]

核心晶体管n0的漏极(d)在节点vx处连接到虚设装置(即,区域154d)。再次参考图1a,节点vx可经施加有io电压范围内的电压(例如,1.2v)。因此,虚设装置的端部(即,区域154d)连接到io电压范围内的电压(例如,1.2v)。针对其中虚设装置的端部连接到io电压的布局,可应用如图1a、图1b、图2a、图2b、图3a、图3b、图4a及图4b中展示的电路结构/配置,以便使核心装置及虚设装置在soa中工作。

[0165]

图5d展示核心晶体管n0及n1的布局156。布局156包含作用区域156a。作用区域156a可被称为连续作用区域。核心晶体管n1可包含奇数指状物。即,核心晶体管n1可包含奇

数个栅极n1_g。核心晶体管n0可包含奇数指状物。即,核心晶体管n0可包含奇数个栅极n0_g。

[0166]

图5d中展示的区域156d表示其中虚设装置可定位于布局156上的区域。

[0167]

核心晶体管n0的漏极(d)在节点vx处连接到虚设装置(即,区域156d)。再次参考图1a,节点vx可经施加有io电压范围内的电压(例如,1.2v)。因此,虚设装置的端部(即,区域156d)连接到io电压范围内的电压(例如,1.2v)。针对其中虚设装置的端部连接到io电压的布局,可应用如图1a、图1b、图2a、图2b、图3a、图3b、图4a及图4b中展示的电路结构/配置,以便使核心装置及虚设装置在soa中工作。

[0168]

图6a说明根据本公开的一些实施例的半导体装置的布局图案。

[0169]

图6a展示布局160。布局160可为对应于图1a的装置100的布局。布局160包含衬底160s及作用区域160a。作用区域160a可被称为连续作用区域。在布局160中,核心晶体管n0包含三个指状物(即,栅极n0_g),且核心晶体管n1包含三个指状物(即,栅极n1_g)。虚设装置14的晶体管ndx可包含多个指状物(即,栅极ndx_g)。虚设装置12的晶体管ndy及ndz可各自包含单个指状物(即,栅极ndy_g及ndz_g)。

[0170]

应注意,核心晶体管n0及n1中的指状物的数目与晶体管ndx、ndy及ndz中的指状物的数目可根据不同设计/目的进行调整/修改,且不限于图6a中展示的数目。

[0171]

核心晶体管n0的漏极(d)将连接到节点vx(参考图1a)。如先前论述,在装置100的操作期间,节点vx可被上拉到供应电压vddh(即,io电压范围内的电压)。因此,如果核心晶体管n0的漏极(d)安置在作用区域160a的端部处,那么在装置100的操作期间可观察到衬底160s与作用区域160a之间的电过应力(electrical overstress,eos),且接着核心晶体管n0可能无法在soa中工作。

[0172]

为了避免衬底160s与作用区域160a之间的电过应力,虚设装置12及14可在布局160中邻近于核心晶体管n0放置。参考图6a中展示的虚设装置12,晶体管ndz的源极(s)放置在作用区域160a的边缘160ae附近。

[0173]

再次参考图1a,晶体管ndz的源极(s)经配置以接收参考电压vmid,且晶体管ndz的栅极(即,ndz_g)连接到节点vx。在其中根据先前论述的方程1选择参考电压vmid的条件下,布局160中展示的晶体管ndz、ndy、ndx、n0及n1全部可在soa中工作。

[0174]

参考核心晶体管n1的源极(s)进行比较,核心晶体管n1的源极电连接到接地(gnd),且因此如果核心晶体管n1的源极(s)安置在作用区域160a的端部处,那么将不会观察到衬底160s与作用区域160a之间的电过应力。因此,关于已知技术的虚设装置160_dmy可邻近于核心晶体管n1安置。

[0175]

图6b说明根据本公开的一些实施例的半导体装置的布局图案。图6b展示布局160'。布局160'可为对应于图1a的装置100的布局。布局160'与图6a的布局160类似,例外之处是布局160'进一步包含金属层及导电通路。

[0176]

布局160'展示如图1a中提出的电路结构的安置及路由可以简洁方式完成。参考布局160'中的晶体管ndy,晶体管ndy的栅极ndy_g可通过导电通路ndy_v1、金属层160_m1及导电通路ndy_v2电连接到晶体管ndy的源极。晶体管ndy的源极可通过金属层160_m2电连接到节点vz(再次参考图1a)。

[0177]

参考布局160'中的晶体管ndx,晶体管ndx的漏极及源极可通过金属层160_m3与导

电通路ndx_v1、ndx_v2、ndx_v3及ndx_v4电连接在一起。晶体管ndx的栅极ndx_g可通过导电通路ndx_v5、ndx_v6、ndx_v7、ndx_v8、金属层160_m4、金属层160_m5与导电通路ndx_v9及ndx_v10电连接到晶体管ndx的漏极及源极。晶体管ndx的栅极、源极及漏极可电连接到节点vx(再次参考图1a)。

[0178]

图7a说明根据本公开的一些实施例的半导体装置的布局图案。

[0179]

图7a展示布局180。布局180可为对应于图1a的装置100的布局。布局180包含衬底180s及作用区域180a。

[0180]

作用区域180a可被称为连续作用区域。在布局180中,核心晶体管n0包含两个指状物(即,栅极n0_g),且核心晶体管n1包含两个指状物(即,栅极n1_g)。虚设装置14的晶体管ndx可包含多个指状物(即,栅极ndx_g)。虚设装置12的晶体管ndy及ndz可各自包含两个指状物(即,栅极ndy_g及ndz_g)。

[0181]

与图6a中展示的布局160相比,在布局180中,虚设装置12可放置在布局180的两侧(即,最左侧及最右侧)上。另外,虚设装置14可放置在布局180的两侧(即,最左侧及最右侧)上。虚设装置12可放置在晶体管n0的两侧上,且虚设装置14可放置在晶体管n0的两侧上。

[0182]

应注意,核心晶体管n0及n1中的指状物的数目与晶体管ndx、ndy及ndz中的指状物的数目可根据不同设计/目的进行调整/修改,且不限于图7a中展示的数目。

[0183]

核心晶体管n0的漏极(d)将连接到节点vx(参考图1a)。如先前论述,在装置100的操作期间,节点vx可被上拉到供应电压vddh(即,io电压范围内的电压)。因此,如果核心晶体管n0的漏极(d)安置在作用区域180a的端部处,那么在装置100的操作期间可观察到衬底180s与作用区域180a之间的电过应力,且接着核心晶体管n0可能无法在soa中工作。

[0184]

为了避免衬底180s与作用区域180a之间的电过应力,虚设装置12及14可在布局180中邻近于核心晶体管n0放置。参考图7a中展示的虚设装置12,晶体管ndz的源极(s)放置在作用区域180a的边缘180ae附近。

[0185]

再次参考图1a,晶体管ndz的源极(s)经配置以接收参考电压vmid,且晶体管ndz的栅极(即,ndz_g)连接到节点vx。在其中根据先前论述的方程1选择参考电压vmid的条件下,布局180中展示的晶体管ndz、ndy、ndx、n0及n1全部可在soa中工作。

[0186]

图7b说明根据本公开的一些实施例的半导体装置的布局图案。图7b展示布局180'。布局180'可为对应于图1a的装置100的布局。布局180'与图7a的布局180类似,例外之处是布局180'进一步包含金属层及导电通路。

[0187]

布局180'展示如图1a中提出的电路结构的安置及路由可以简洁方式完成。布局180'的晶体管n0、n1、ndx、ndy及ndz的配置可以与根据图6b描述的方式类似的方式来理解。

[0188]

图8a说明根据本公开的一些实施例的半导体装置的示意图。

[0189]

图8a展示装置200。装置200可为电装置。装置200可为半导体装置。装置200可为集成电路(ic)系统。装置200包含核心装置80、虚设装置82及电路16。

[0190]

核心装置80电连接在电路16与供应电压vddh之间。电路16电连接到接地(gnd)。电路16电连接到节点vx。虚设装置82电连接到节点vx。虚设装置82电连接到核心装置80。虚设装置82电连接到供应电压vddh。

[0191]

核心装置80包含晶体管pa及晶体管pb。晶体管pa可被称为核心晶体管。晶体管pb可被称为核心晶体管。晶体管pa可为p沟道mosfet。晶体管pb可为p沟道mosfet。本公开中提

及的核心晶体管可为构成核心装置的一部分的晶体管。

[0192]

晶体管pb的源极电连接到晶体管pa的漏极。晶体管pb的漏极在节点vx处电连接到电路16。晶体管pb的栅极经配置以接收参考电压vssh。晶体管pa的源极电连接到供应电压vddh。晶体管pa的栅极经配置以接收输入电压vhin。

[0193]

虚设装置82包含晶体管pd1及晶体管pd2。晶体管pd1可为p沟道mosfet。晶体管pd2可为p沟道mosfet。晶体管pd2的源极电连接到晶体管pd1的漏极。晶体管pd1的源极电连接到晶体管pd1的栅极。晶体管pd1的源极与栅极经配置以接收供应电压vddh。

[0194]

晶体管pd2的漏极电连接到节点vx。晶体管pd2的栅极电连接到晶体管pb的栅极。即,虚设装置82将使用与核心装置80相同的偏压,且因此可避免电过应力。

[0195]

将如下般描述装置200的操作。在一些实施例中,供应电压vddh可为约1.8v。在一些实施例中,参考电压vssh可为约0.85v。在一些实施例中,晶体管pa的输入电压vhin的范围可为约从1.1v到1.8v。晶体管pa的输入电压vhin可控制晶体管pa接通或关断。

[0196]

当晶体管pa关断时,施加到晶体管pa的栅极的电压可为1.8v,且节点vx处的电压将为约相同于0v。施加到晶体管pb的栅极的参考电压vssh可为0.85v。晶体管pd1将由于其vgs等于零而关断。同时,晶体管pd1及pd2两者将在soa中工作。

[0197]

当晶体管pa接通时,施加到晶体管pa的栅极的电压可为1.1v,且节点vx处的电压将被上拉到约1.8v。施加到晶体管pb的栅极的参考电压vssh可为0.85v。晶体管pd1将由于其vgs等于零而关断。同时,晶体管pd1及pd2两者将在soa中工作。

[0198]

图8b说明根据本公开的一些实施例的半导体装置的示意图。

[0199]

图8a展示装置220。装置220可为电装置。装置220可为半导体装置。装置220可为集成电路(ic)系统。装置220包含核心装置90、虚设装置92及电路16。

[0200]

核心装置90电连接在电路16与供应电压vddh之间。电路16电连接到接地(gnd)。电路16电连接到节点vx。虚设装置92电连接到节点vx。虚设装置92电连接到核心装置90。

[0201]

核心装置90包含晶体管pa及晶体管pb。晶体管pa可被称为核心晶体管。晶体管pb可被称为核心晶体管。晶体管pa可为p沟道mosfet。晶体管pb可为p沟道mosfet。本公开中提及的核心晶体管可为构成核心装置的一部分的晶体管。

[0202]

晶体管pb的源极电连接到晶体管pa的漏极。晶体管pb的漏极在节点vx处电连接到电路16。晶体管pb的栅极经配置以接收参考电压vssh。晶体管pa的源极电连接到供应电压vddh。晶体管pa的栅极经配置以接收输入电压vhin。

[0203]

虚设装置92包含晶体管pd1、pd2及pd3。晶体管pd1可为p沟道mosfet。晶体管pd2可为p沟道mosfet。晶体管pd3可为p沟道mosfet。

[0204]

晶体管pd2的源极电连接到晶体管pd1的漏极。晶体管pd1的源极电连接到晶体管pd1的栅极。晶体管pd1的源极及栅极连接在一起且电连接到晶体管pa的栅极。晶体管pd1的源极与栅极经配置以接收输入电压vhin。

[0205]

晶体管pd2的漏极电连接到晶体管pd3的源极。晶体管pd2的栅极电连接到晶体管pb的栅极,且经配置以接收参考电压vssh。即,虚设装置92将使用与核心装置90相同的偏压,且因此可避免电过应力。晶体管pd3的漏极及栅极连接在一起。晶体管pd3的漏极电连接到节点vx。

[0206]

将如下般描述装置220的操作。在一些实施例中,供应电压vddh可为约1.8v。在一

些实施例中,参考电压vssh可为约0.85v。在一些实施例中,晶体管pa的输入电压vhin的范围可为约从1.1v到1.8v。晶体管pa的输入电压vhin可控制晶体管pa接通或关断。

[0207]

当晶体管pa关断时,施加到晶体管pa的栅极的电压可为1.8v,且节点vx处的电压将为约相同于0v。施加到晶体管pb的栅极的参考电压vssh可为0.85v。晶体管pd1及pd2将由于它们的vgs等于零而关断。同时,晶体管pd1、pd2及pd3将全部在soa中工作。

[0208]

当晶体管pa接通时,施加到晶体管pa的栅极的电压可为1.1v,且节点vx处的电压将被上拉到约1.8v。施加到晶体管pb的栅极的参考电压vssh可为0.85v。晶体管pd1及pd2将由于它们的vgs等于零而关断。同时,晶体管pd1、pd2及pd3将全部在soa中工作。

[0209]

图9a说明根据本公开的一些实施例的半导体装置的布局图案。

[0210]

图9a展示布局240。布局240可为对应于图8a的装置200的布局。布局240包含阱区域240w及作用区域240a。在一些实施例中,阱区域240w可为n型阱。在一些实施例中,作用区域240a可经掺杂有p型杂质。尽管图9a中未描绘,然应理解,阱区域240w及作用区域240a可放置在衬底上。

[0211]

晶体管pd1的栅极经配置以接收供应电压vddh。晶体管pd2的栅极经配置以接收参考电压vssh。晶体管pb的栅极经配置以接收参考电压vssh。晶体管pa的栅极经配置以接收输入电压vhin。阱区域240w电连接到供应电压vddh。

[0212]

晶体管pd1的源极(s)邻近于作用区域240a的边缘240ae1放置,且电连接到供应电压vddh。晶体管pa的源极(s)邻近于作用区域240a的边缘240ae2放置,且电连接到供应电压vddh。

[0213]

参考布局240上的晶体管pd1及pa,由于晶体管pd1的源极(s)、晶体管pa的源极(s)及阱区域240w全部电连接到供应电压vddh,因此在作用区域240a与阱区域240w之间不存在电压差。因此,不会观察到作用区域240a与阱区域240w之间的电过应力,且布局240的全部晶体管pd1、pd2、pa及pb可在soa中工作。

[0214]

图9b说明根据本公开的一些实施例的半导体装置的布局图案。

[0215]

图9b展示布局260。布局260可为对应于图8b的装置220的布局。布局260包含阱区域260w及作用区域260a。在一些实施例中,阱区域260w可为n型阱。在一些实施例中,作用区域260a可经掺杂有p型杂质。尽管图9b中未描绘,然应理解,阱区域260w及作用区域260a可放置在衬底上。

[0216]

晶体管pd1的栅极经配置以接收输入电压vhin,其范围可为从1.1v到1.8v。晶体管pd2的栅极经配置以接收参考电压vssh。晶体管pb的栅极经配置以接收参考电压vssh。

[0217]

晶体管pa的栅极经配置以接收输入电压vhin。阱区域260w电连接到供应电压vddh。晶体管pd1的源极(s)邻近于作用区域260a的边缘260ae1放置,且电连接到输入电压vhin。晶体管pa的源极(s)邻近于作用区域260a的边缘260ae2放置,且电连接到供应电压vddh。

[0218]

参考布局260上的晶体管pa,由于晶体管pa的源极(s)及阱区域260w两者电连接到供应电压vddh,因此在作用区域260a与阱区域260w之间不存在电压差。另外,参考布局260上的晶体管pd1,晶体管pd1的源极(s)电连接到输入电压vhin,其范围可为从1.1v到1.8v,且阱区域260w电连接到供应电压vddh,其可为1.8v。因此,不会观察到作用区域260a与阱区260w之间的电过应力,且布局260的全部晶体管pd1、pd2、pd3、pa及pb可在soa中工作。

[0219]

图10说明根据本公开的一些比较实施例的半导体装置的布局图案。

[0220]

图10展示布局300。布局300包含衬底300s及作用区域300a。核心晶体管n0'放置在布局300的中间,而两个虚设晶体管nd1及nd2放置在核心晶体管n0'的两侧上。作用区域300a的边缘300ae附近的核心晶体管n0'的漏极(d)可经施加有io电压范围内的电压(例如,1.2v)。虚设晶体管nd1及nd2根据现有技术来配置。将虚设晶体管nd1作为实例,虚设晶体管nd1的栅极nd1_g、漏极及源极全部连接到接地(gnd)。另外,衬底300s将连接到接地(gnd)。

[0221]

因此,由于核心晶体管n0'的漏极(d)可经施加有io电压范围内的电压(例如,1.2v),因此可观察到衬底300s与作用区域300a之间的电过应力。因此,针对在io电压范围内操作的核心晶体管,根据现有技术配置的虚设晶体管是不适用的。

[0222]

图11说明根据本公开的一些实施例的包含用于制造半导体装置的操作的流程图。

[0223]

图11包含用于制造半导体装置的操作1102、1104、1106、1108、1110、1112、1114及1116。在操作1102中,形成衬底。在操作1102中形成的衬底可包含例如但不限于硅(si)、掺杂si、碳化硅(sic)、硅化锗(sige)、砷化镓(gaas)或其它半导体材料。在操作1102中形成的衬底可包含例如但不限于蓝宝石、绝缘体上硅(soi)或其它合适材料。在一些实施例中,在操作1102中形成的衬底可包含硅材料。在一些实施例中,在操作1102中形成的衬底可为硅衬底。

[0224]

在操作1104中,可在衬底上形成作用区域。在操作1104中形成的作用区域可对应于图9a的作用区域240a或图9b的作用区域260a。

[0225]

在操作1106中,形成具有经配置以接收io电压范围内的第一电压的漏极的第一核心晶体管。在操作1106中形成的第一核心晶体管可对应于图8a的核心晶体管pb或图8b的核心晶体管pb。图8a的核心晶体管pb具有经配置以接收节点vx处的电压的漏极,所述电压在io电压范围内。图8b的核心晶体管pb具有经配置以接收节点vx处的电压的漏极,所述电压在io电压范围内。

[0226]

在操作1108中,形成具有邻近于作用区域的边缘的源极的第二核心晶体管。在操作1108中形成的第二核心晶体管可对应于图8a的核心晶体管pa或图8b的核心晶体管pa。参考图9a,核心晶体管pa的源极(s)邻近于作用区域240a的边缘240ae2放置。类似地,参考图9b,核心晶体管pa的源极(s)邻近于作用区域260a的边缘260ae2放置。

[0227]

在操作1110中,形成具有第一虚设晶体管及第二虚设晶体管的虚设装置。在操作1110中形成的第一虚设晶体管可对应于图8a或图8b的虚设晶体管pd2。在操作1110中形成的第二虚设晶体管可对应于图8a或图8b的虚设晶体管pd1。

[0228]

在操作1112中,将第二虚设晶体管的漏极连接到第一虚设晶体管的源极。参考图8a或图8b,虚设晶体管pd1的漏极连接到虚设晶体管pd2的源极。

[0229]

在操作1114中,将第一虚设晶体管的栅极连接到第一核心晶体管的栅极。参考图8a或图8b,虚设晶体管pd2的栅极连接到核心晶体管pb的栅极。

[0230]

在操作1116中,将第二虚设晶体管的源极连接到第二虚设晶体管的漏极。参考图8a或图8b,虚设晶体管pd1的源极连接到虚设晶体管pd1的漏极。

[0231]

本公开的一些实施例提供一种半导体装置。所述半导体装置包括:核心晶体管,其具有经配置以接收第一电压的漏极;及第一虚设装置,其连接到所述核心晶体管的所述漏极,所述第一虚设装置具有第一虚设晶体管及第二虚设晶体管。其中所述第一虚设晶体管

的栅极及源极彼此连接。其中所述第二虚设晶体管的漏极连接到所述第一虚设晶体管的所述源极。其中所述第二虚设晶体管的栅极连接到所述核心晶体管的所述漏极。

[0232]

本公开的一些实施例提供一种半导体装置。所述半导体装置包括:衬底;连续作用区域,其在所述衬底上;及核心晶体管,其具有经配置以接收第一电压的漏极。所述半导体装置进一步包括连接到所述核心晶体管的所述漏极的虚设装置,所述虚设装置具有第一虚设晶体管及第二虚设晶体管。其中所述第二虚设晶体管的漏极连接到所述第一虚设晶体管的所述源极,且其中所述第二虚设晶体管的源极邻近于所述连续作用区域的边缘放置。

[0233]

本公开的一些实施例提供一种用于制造半导体装置的方法。所述方法包括形成具有经配置以接收io电压范围内的第一电压的漏极的第一核心晶体管。所述方法包括形成具有第一虚设晶体管及第二虚设晶体管的虚设装置。所述方法包括将所述第二虚设晶体管的漏极连接到所述第一虚设晶体管的源极。所述方法进一步包括将所述第一虚设晶体管的栅极连接到所述第一核心晶体管的栅极。

[0234]

前文概述若干实施例的结构,使得所属领域的技术人员可更佳地理解本公开的方面。所属领域的技术人员应了解,其可容易地使用本公开作为设计或修改用于实行本文中介绍的实施例的相同目的及/或达成相同优点的其它过程及结构的基础。所属领域的技术人员还应认识到,此类等效构造不脱离本公开的精神及范围,且其可在不脱离本公开的精神及范围的情况下在本文中进行各种改变、替换及更改。

[0235]

符号说明

[0236]

10:核心装置

[0237]

10':核心装置

[0238]

12:虚设装置

[0239]

12':虚设装置

[0240]

14:虚设装置

[0241]

14':虚设装置

[0242]

16:电路

[0243]

20:核心装置

[0244]

20':核心装置

[0245]

22:虚设装置

[0246]

22':虚设装置

[0247]

24:虚设装置

[0248]

24':虚设装置

[0249]

30:核心装置

[0250]

30':核心装置

[0251]

32:虚设装置

[0252]

32':虚设装置

[0253]

32a:虚设电路

[0254]

32a':虚设电路

[0255]

32b:虚设电路

[0256]

32b':虚设电路

[0257]

34:虚设装置

[0258]

34':虚设装置

[0259]

40:核心装置

[0260]

40':核心装置

[0261]

42:虚设装置

[0262]

42':虚设装置

[0263]

42a:虚设电路

[0264]

42a':虚设电路

[0265]

42b:虚设电路

[0266]

42b':虚设电路

[0267]

44:虚设装置

[0268]

44':虚设装置

[0269]

80:核心装置

[0270]

82:虚设装置

[0271]

90:核心装置

[0272]

92:虚设装置

[0273]

100:装置

[0274]

100':装置

[0275]

110:装置

[0276]

110':装置

[0277]

120:装置

[0278]

120':装置

[0279]

130:装置

[0280]

130':装置

[0281]

150:布局

[0282]

150a:作用区域

[0283]

150d:区域

[0284]

152:布局

[0285]

152a:作用区域

[0286]

152d:区域

[0287]

154:布局

[0288]

154a:作用区域

[0289]

154d:区域

[0290]

156:布局

[0291]

156a:作用区域

[0292]

156d:区域

[0293]

160:布局

[0294]

160':布局

[0295]

160a:作用区域

[0296]

160ae:边缘

[0297]

160_dmy:虚设装置

[0298]

160_m1到160_m5:金属层

[0299]

160s:衬底

[0300]

180:布局

[0301]

180':布局

[0302]

180a:作用区域

[0303]

180ae:边缘

[0304]

180s:衬底

[0305]

200:装置

[0306]

220:装置

[0307]

240:布局

[0308]

240a:作用区域

[0309]

240ae1:边缘

[0310]

240ae2:边缘

[0311]

240w:阱区域

[0312]

260:布局

[0313]

260a:作用区域

[0314]

260ae1:边缘

[0315]

260ae2:边缘

[0316]

260w:阱区域

[0317]

300:布局

[0318]

300a:作用区域

[0319]

300ae:边缘

[0320]

300s:衬底

[0321]

1102:操作

[0322]

1104:操作

[0323]

1106:操作

[0324]

1108:操作

[0325]

1110:操作

[0326]

1112:操作

[0327]

1114:操作

[0328]

1116:操作

[0329]

gnd:接地

[0330]

n0:晶体管

[0331]

n0':晶体管

[0332]

n0_g:栅极

[0333]

n1:晶体管

[0334]

n1_g:栅极

[0335]

nd1:虚设晶体管

[0336]

nd1_g:栅极

[0337]

nd2:虚设晶体管

[0338]

ndx:晶体管

[0339]

ndx_g:栅极

[0340]

ndx_v1到ndx_v10:导电通路

[0341]

ndy:晶体管

[0342]

ndy1到ndyn:晶体管

[0343]

ndy_g:栅极

[0344]

ndy_v1:导电通路

[0345]

ndy_v2:导电通路

[0346]

ndz:晶体管

[0347]

ndz1到ndzn:晶体管

[0348]

ndz_g:栅极

[0349]

p0:晶体管

[0350]

p1:晶体管

[0351]

pa:晶体管

[0352]

pb:晶体管

[0353]

pd1:晶体管

[0354]

pd2:晶体管

[0355]

pd3:晶体管

[0356]

pdx:晶体管

[0357]

pdy:晶体管

[0358]

pdy1到pdyn:晶体管

[0359]

pdz:晶体管

[0360]

pdz1到pdzn:晶体管

[0361]

vddh:供应电压

[0362]

vddl:参考电压

[0363]

vhin:输入电压

[0364]

vin:输入电压

[0365]

vmid:参考电压

[0366]

vssh:参考电压

[0367]

vx:节点

[0368]

vy:节点

[0369]

vz:节点。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。