1.本发明涉及半导体集成电路的制造领域,特别是涉及一种铜填充凹槽结构。本发明还涉及一种铜填充凹槽结构的制造方法。

背景技术:

2.随着后段(beol)铜互连的关键尺寸(cd)越来越小,沟槽(trench)和通孔(via)开口的填孔的难度越来越大,现说明如下:

3.如图1所示,是现有第一种铜填充凹槽结构的制造方法形成的铜填充凹槽结构的结构示意图;现有第一种铜填充凹槽结构的制造方法采用了物理气相沉积(pvd)tan ta 铜籽晶层(cu seed)工艺,包括如下步骤:

4.在介质层如层间膜101上形成凹槽102,所述凹槽102为铜互连线中的铜连线对应的沟槽或者为通孔对应的通孔开口。

5.之后,采用pvd工艺形成tan层103和ta层104并由tan层103和ta层104叠加形成阻挡层。

6.之后,形成铜籽晶层105。由于铜籽晶层105的台阶覆盖能力较差,容易在所述凹槽102的顶部产生封口效应,也即在所述凹槽102的顶部的铜籽晶层105的厚度较厚,使得所述凹槽102的顶部的宽度d101变得较小。

7.之后,采用电镀工艺(ecp)形成铜电镀膜106。由于,所述凹槽102顶部的宽度d101较小,使得铜电镀膜106的形成难度增加。现有第一种方法并不能适用于14nm以下技术节点的凹槽填充,这是因为,14nm工艺节点的半导体器件对应的铜互连线中的铜连线的关键尺寸约为32nm,长完所述铜籽晶层105后,所述凹槽102的顶部的宽度d101太小,无法满足ecp工艺要求。而若通过减少所述铜籽晶层105的厚度来增加宽度d101,则所述凹槽102的侧面上的铜无法形成连续结构。

8.如图2所示,是现有第二种铜填充凹槽结构的制造方法形成的铜填充凹槽结构的结构示意图;为了克服上面描述的现有第一种铜填充凹槽结构的制造方法不能再14nm以下技术节点的缺陷,所以14nm技术节点的工艺中引入了化学气相沉积(cvd)钴(co)金属工艺,用金属钴层替代了ta层金属,即采用pvd tan cvd co cu seed工艺,现有第二种铜填充凹槽结构的制造方法包括如下步骤:

9.在介质层如层间膜102上形成凹槽202,所述凹槽202为铜互连线中的铜连线对应的沟槽或者为通孔对应的通孔开口。

10.之后,采用pvd工艺形成tan层203。

11.之后,采用cvd工艺形成钴层204。

12.之后,形成铜籽晶层205。由于铜籽晶层205的台阶覆盖能力较差,采用铜籽晶层205后,依然容易在所述凹槽202的顶部产生封口效应,也即在所述凹槽202的顶部的铜籽晶层205的厚度较厚,使得所述凹槽102的顶部的宽度d201同样会很小。

13.之后,采用电镀工艺(ecp)形成铜电镀膜206。

14.钴层204主要的作用是改善cu的黏附性能,防止cu在较薄的厚度下出现团聚效应,保证了cu在很薄的厚度下仍保持铜在凹槽202的侧面是连续的。也即采用钴层204,能减少铜籽晶层205的厚度,由于图2的铜籽晶层205的厚度小于图1中的铜籽晶层105的厚度,故在凹槽202的顶部开口宽度和凹槽102的顶部开口宽度相同的条件下,形成铜籽晶层后,图2中的宽度d201会大于图1中的宽度d101,故现有第二种铜填充凹槽结构的制造方法能应用于14nm技术节点的工艺中,但是现有第一种铜填充凹槽结构的制造方法则不能应用于14nm技术节点的工艺中。

15.现有第二种铜填充凹槽结构的制造方法虽然在引入co衬垫层(liner)即钴层204后,需要的铜籽晶层205的厚度可以得到有效的降低,但铜籽晶层205对于凹槽202顶部开口缩小带来的贡献仍然是非常大的,14nm技术节点时,开口缩小达到7.9nm。

技术实现要素:

16.本发明要解决的技术问题是提供一种铜填充凹槽结构,铜层不含铜籽晶层,完全由铜电镀膜组成,从而能提高在凹槽中填充铜的能力,有利于铜填充凹槽结构的缩小,特别适用于作为14nm工艺节点以下的铜连线和通孔。为此,本发明还公开了一种铜填充凹槽结构的制造方法。

17.为解决上述技术问题,本发明提供的铜填充凹槽结构包括:

18.凹槽,形成于第一介质层中。

19.在所述凹槽的底部表面和侧面形成有阻挡层。

20.在所述阻挡层的表面形成钴层,在所述钴层的表面形成有钌层。

21.铜层将形成有所述阻挡层、所述钴层和所述钌层的所述凹槽完全填充并形成铜填充凹槽结构。

22.所述铜层完全由铜电镀膜组成。

23.由所述钴层和所述钌层叠加形成所述铜层的辅助成核膜层。

24.所述辅助成核膜层使所述铜层具有由所述铜电镀膜和所述钌层直接接触的结构,使所述铜电镀膜的填充区域为所述辅助成核膜层所围区域。

25.进一步的改进是,所述凹槽为沟槽,所述铜填充凹槽结构为铜互连线。

26.或者,所述凹槽为通孔的开口,所述铜填充凹槽结构为通孔。

27.进一步的改进是,所述第一介质层为层间膜。

28.进一步的改进是,所述阻挡层为tan层或者为tin层。

29.进一步的改进是,所述钴层的厚度为

30.进一步的改进是,所述钌层的厚度为

31.进一步的改进是,所述层间膜形成于半导体衬底上,所述半导体衬底上形成有半导体器件,所述铜互连线形成所述半导体器件的电极引出结构。

32.进一步的改进是,所述半导体器件的工艺节点为14nm以下。

33.为解决上述技术问题,本发明提供的铜填充凹槽结构的制造方法包括如下步骤:

34.步骤一、在第一介质层中形成凹槽。

35.步骤二、在所述凹槽的底部表面和侧面形成阻挡层。

36.步骤三、在所述阻挡层的表面形成钴层。

37.步骤四、在所述钴层的表面形成有钌层。

38.由所述钴层和所述钌层叠加形成所述铜层的辅助成核膜层。

39.步骤五、直接进行铜电镀工艺在所述辅助成核膜层上形成完全由铜电镀膜组成铜层,铜层将形成有所述阻挡层、所述钴层和所述钌层的所述凹槽完全填充并形成铜填充凹槽结构。

40.进一步的改进是,所述凹槽为沟槽,所述铜填充凹槽结构为铜互连线。

41.或者,所述凹槽为通孔的开口,所述铜填充凹槽结构为通孔。

42.进一步的改进是,所述第一介质层为层间膜。

43.进一步的改进是,所述阻挡层为tan层或者为tin层。

44.进一步的改进是,所述钴层的厚度为

45.进一步的改进是,所述钌层的厚度为

46.进一步的改进是,所述层间膜形成于半导体衬底上,所述半导体衬底上形成有半导体器件,所述铜互连线形成所述半导体器件的电极引出结构。

47.进一步的改进是,所述半导体器件的工艺节点为14nm以下。

48.本发明铜填充凹槽结构中在铜电镀膜之前采用了由钴层和钌层叠加而成的铜层的辅助成核膜层,钌层由于具有较低的电化学势能,能够直接在钌层上进行电镀铜,而且钌的氧化物即ruox导电性好,故钌即使在酸性的ecp溶液中被氧化,也不会影响铜填充凹槽结构的导电性能。但是,单独采用钌层形成铜层时可靠性较差,故不能单独采用钌层来作为铜电镀膜的辅助成核膜层。

49.另外,和钌层有助于铜成核一样,钴层也有助于铜成核,也即钴层和钌层都有助于铜成核,但是co与酸性的ecp溶液不兼容,且易溶解,而且co的氧化物也不导电,这使得单独采用钴层形成铜层时会使整个铜填充凹槽结构的导电性能较差,故不能单独采用钴层来作为铜电镀膜的辅助成核膜层。

50.本发明通过钴层和钌层相结合且是将钌层设置在钴层和铜层之间,能够克服单独设置钌层和单独设置钴层时不能作为铜电镀膜的辅助成核膜层的缺陷,最后能在不采用铜籽晶层的条件下得到可靠性良好的铜电镀膜,这样就能够克服采用铜籽晶层所带来的容易造成凹槽开口变小从而不利于铜电镀膜填充的缺陷,从而能提高在凹槽中填充铜的能力,能提高铜填充凹槽的工艺窗口并同时保持优越的可靠性,有利于铜填充凹槽结构的缩小,特别适用于作为14nm工艺节点以下的铜连线和通孔。

附图说明

51.下面结合附图与具体实施方式对本发明作进一步详细的说明:

52.图1是现有第一种铜填充凹槽结构的制造方法形成的铜填充凹槽结构的结构示意图;

53.图2是现有第二种铜填充凹槽结构的制造方法形成的铜填充凹槽结构的结构示意图;

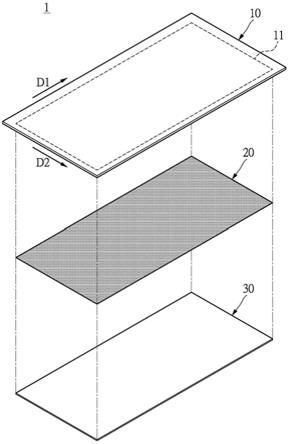

54.图3是本发明实施例铜填充凹槽结构的结构示意图;

55.图4是本发明实施例铜填充凹槽结构的制造方法的流程图。

具体实施方式

56.如图3所示,是本发明实施例铜填充凹槽结构的结构示意图;本发明实施例铜填充凹槽结构包括:

57.凹槽2,形成于第一介质层1中。

58.在所述凹槽2的底部表面和侧面形成有阻挡层3。

59.本发明实施例中,所述阻挡层3为tan层,在其他实施例中,所述阻挡层3也能为tin层。

60.在所述阻挡层3的表面形成钴层4,在所述钴层4的表面形成有钌层5。

61.铜层6将形成有所述阻挡层3、所述钴层4和所述钌层5的所述凹槽2完全填充并形成铜填充凹槽结构。

62.所述铜层6完全由铜电镀膜组成。

63.由所述钴层4和所述钌层5叠加形成所述铜层6的辅助成核膜层。

64.所述辅助成核膜层使所述铜层6具有由所述铜电镀膜和所述钌层5直接接触的结构,使所述铜电镀膜的填充区域为所述辅助成核膜层所围区域。由图3所示可知,在所述铜层6中并不具有铜籽晶层,从而能克服铜籽晶层所带来的封口效应并避免由于铜籽晶层的封口效应使得所述凹槽2的顶部开口的减少,从而能使所述凹槽2的顶部开口的宽度d1保持较大值,从而有利于所述铜层6的铜电镀膜的填充,能提高填充工艺窗口和填充质量。

65.本发明实施例中,所述第一介质层1为层间膜。

66.所述层间膜形成于半导体衬底上,所述半导体衬底上形成有半导体器件,所述铜互连线形成所述半导体器件的电极引出结构。

67.所述半导体器件的工艺节点为14nm以下。

68.所述凹槽2为沟槽,所述铜填充凹槽结构为铜互连线。

69.或者,所述凹槽2为通孔的开口,所述铜填充凹槽结构为通孔。

70.所述钴层4的厚度为

71.所述钌层5的厚度为

72.本发明实施例铜填充凹槽结构中在铜电镀膜之前采用了由钴层4和钌层5叠加而成的铜层6的辅助成核膜层,钌层5由于具有较低的电化学势能,能够直接在钌层5上进行电镀铜,而且钌的氧化物即ruox导电性好,故钌即使在酸性的ecp溶液中被氧化,也不会影响铜填充凹槽结构的导电性能。但是,单独采用钌层5形成铜层6时可靠性较差,故不能单独采用钌层5来作为铜电镀膜的辅助成核膜层。

73.另外,和钌层5有助于铜成核一样,钴层4也有助于铜成核,也即钴层4和钌层5都有助于铜成核,但是co与酸性的ecp溶液不兼容,且易溶解,而且co的氧化物也不导电,这使得单独采用钴层4形成铜层6时会使整个铜填充凹槽结构的导电性能较差,故不能单独采用钴层4来作为铜电镀膜的辅助成核膜层。

74.本发明实施例通过钴层4和钌层5相结合且是将钌层5设置在钴层4和铜层6之间,能够克服单独设置钌层5和单独设置钴层4时不能作为铜电镀膜的辅助成核膜层的缺陷,最后能在不采用铜籽晶层的条件下得到可靠性良好的铜电镀膜,这样就能够克服采用铜籽晶层所带来的容易造成凹槽2开口变小从而不利于铜电镀膜填充的缺陷,从而能提高在凹槽2中填充铜的能力,能提高铜填充凹槽2的工艺窗口并同时保持优越的可靠性,有利于铜填充

凹槽结构的缩小,特别适用于作为14nm工艺节点以下的铜连线和通孔。

75.如图4所示,是本发明实施例铜填充凹槽结构的制造方法的流程图,本发明实施例铜填充凹槽结构的制造方法形成的铜填充凹槽结构请参考图3所示,本发明实施例铜填充凹槽结构的制造方法包括如下步骤:

76.步骤一、在第一介质层1中形成凹槽2。

77.步骤二、在所述凹槽2的底部表面和侧面形成阻挡层3。

78.本发明实施例中,所述阻挡层3为tan层,在其他实施例中,所述阻挡层3也能为tin层。

79.步骤三、在所述阻挡层3的表面形成钴层4。

80.步骤四、在所述钴层4的表面形成有钌层5。

81.由所述钴层4和所述钌层5叠加形成所述铜层6的辅助成核膜层。

82.步骤五、直接进行铜电镀工艺在所述辅助成核膜层上形成完全由铜电镀膜组成铜层6,铜层6将形成有所述阻挡层3、所述钴层4和所述钌层5的所述凹槽2完全填充并形成铜填充凹槽结构。

83.本发明实施例方法中,所述第一介质层1为层间膜。

84.所述层间膜形成于半导体衬底上,所述半导体衬底上形成有半导体器件,所述铜互连线形成所述半导体器件的电极引出结构。

85.所述半导体器件的工艺节点为14nm以下。

86.所述凹槽2为沟槽,所述铜填充凹槽结构为铜互连线。

87.或者,所述凹槽2为通孔的开口,所述铜填充凹槽结构为通孔。

88.所述钴层4的厚度为

89.所述钌层5的厚度为

90.和现有第一种铜填充凹槽结构的制造方法以及现有第二种铜填充凹槽结构的制造方法相比可知,本发明实施例铜填充凹槽结构的制造方法采用了tan co ru工艺,本发明实施例方法由于现有第一种方法和现有第二种方法的理由为:

91.co和ru均有助于cu的成核,但co与酸性的ecp浴(bath)不兼容,且易溶解,而且co的氧化物也不导电,所以本发明实施例方法把钴层4处于钌层5的下层。而钌层5的电化学势能低,甚至可以进行无电镀膜(electroless deposited,eld)方式镀铜,且钌层5的氧化物(ruox)导电性能也很好,所以本发明实施例方法的最上层为钌层5。但由于钌层5的可靠性能即金属的电迁移(electromigration,em)较差,而co又能显著提高可靠性能(em)。所以这也是co金属存在的原因。

92.最后使得,本发明实施例方法能增大14nm以下技术节点的铜填充凹槽的工艺窗口(cu gapfill window),适合更小尺寸的后段铜互连技术。同时保持优越的em能性

93.以上通过具体实施方式对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。