1.本发明涉及压电元件及其制造方法。

背景技术:

2.作为公开了压电元件的结构的文献,有日本特开2009-302661号公报(专利文献1)。专利文献1所记载的压电元件包括硅基板、压电体膜以及导电体膜。压电体膜由压电体例如氮化铝(aln)形成,设于硅基板上。导电体膜由导电材料形成,设于压电体膜上。导电体膜配置于压电体膜上和压电体膜间,与硅层的n型区域和压电体膜接触。aln膜通过反应性磁控溅射法成膜,通过使用氯类气体的rie(reactive ion etching)构成图案而形成。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2009-302661号公报

技术实现要素:

6.发明要解决的问题

7.在以往的压电装置中,在使压电体层和电极层(下部电极)相互层叠之后,从与电极层侧相反的那一侧通过蚀刻形成贯通压电体层的贯通孔。电极层中的面向上述贯通孔的部分在上述贯通孔的形成的同时被蚀刻。因此,在以往的压电装置中,在上述电极层中的面向上述贯通孔的部分中,实际上不可避免地产生凹部,并且存在电极层的结晶性紊乱这样的问题。并且,位于贯通孔内的连接电极与电极层中的结晶性紊乱的上述的部分接合,因此电极层与连接电极的接合部处的电连接变得不充分,有时产生断路不良。

8.本发明是鉴于上述问题点而完成的,其目的在于,提供一种能够抑制电极层与连接电极的接合部处的断路不良的产生的压电元件。

9.用于解决问题的方案

10.基于本发明的第1技术方案的压电元件包括压电体层、第1电极层、第2电极层以及连接电极。压电体层具有第1面、第2面以及贯通孔。第2面与第1面相对。贯通孔从第1面贯通到第2面。第1电极层设于第1面上。第2电极层位于压电体层的第2面侧。第2电极层至少局部隔着压电体层而与第1电极层相对。第2电极层具有连接面。连接面在第2电极层中的不与第1电极层相对的区域中面向贯通孔。连接电极设于连接面上。连接面与第2电极层的压电体层侧的面中的连接面以外的部分的位置的差为5nm以下。

11.基于本发明的第2技术方案的压电元件包括压电体层、第1电极层、第2电极层以及连接电极。压电体层具有第1面、第2面以及贯通孔。第2面与第1面相对。贯通孔从第1面贯通到第2面。第1电极层设于第1面上。第2电极层位于压电体层的第2面侧。第2电极层至少局部隔着压电体层而与第1电极层相对。第2电极层具有连接面。连接面在第2电极层中的不与第1电极层相对的区域中面向贯通孔。连接电极设于连接面上。贯通孔随着从第1面朝向第2面而扩大。

12.基于本发明的技术方案的压电元件的制造方法包括在压电体基板中形成凹部的工序、形成压电体层的工序、配置第2电极层的工序以及层叠第1电极层的工序。压电体基板具有第1主面和与第1主面相对的第2主面。在压电体基板中形成凹部的工序中,利用蚀刻法在第2主面侧形成上述凹部。在形成压电体层的工序中,通过在从第1主面侧磨削压电体基板之后进行抛光,从而使第1面暴露,并且,去除凹部的底部而形成由凹部的内表面形成的贯通孔。压电体层具有第1面、第2面以及贯通孔。第2面与第1面相对。贯通孔从第1面贯通到第2面。在配置第2电极层的工序中,在压电体层的第2面侧,以至少局部面向贯通孔的方式配置第2电极层。在层叠第1电极层的工序中,在压电体层的第1面侧,以至少局部隔着压电体层而与第2电极层相对的方式层叠第1电极层。

13.发明的效果

14.根据本发明,能够抑制电极层与连接电极的接合部处的断路不良的产生。

附图说明

15.图1是表示本发明的实施方式1的压电元件的概略俯视图。

16.图2是从

ⅱ‑ⅱ

线箭头方向观察图1的压电元件而得到的剖视图。

17.图3是表示在本发明的实施方式1的压电元件的制造方法中在压电体基板形成凹部的状态的剖视图。

18.图4是在本发明的实施方式1的压电元件的制造方法中准备包含第2电极层的层叠基板的剖视图。

19.图5是表示在本发明的实施方式1的压电元件的制造方法中使压电体基板接合于包含第2电极层的层叠基板的状态的剖视图。

20.图6是表示在本发明的实施方式1的压电元件的制造方法中切削压电体基板而形成压电体层的状态的剖视图。

21.图7是表示在本发明的实施方式1的压电元件的制造方法中设置第1电极层的状态的剖视图。

22.图8是表示在本发明的实施方式1的压电元件的制造方法中设置连接电极的状态的剖视图。

23.图9是表示在本发明的实施方式2的压电元件的制造方法中在第2电极层上设置连接电极的状态的剖视图。

24.图10是表示在本发明的实施方式2的压电元件的制造方法中使压电体基板接合于包含第2电极层的层叠基板的状态的剖视图。

25.图11是表示在本发明的实施方式2的压电元件的制造方法中切削压电体基板而形成压电体层的状态的剖视图。

26.图12是表示在本发明的实施方式2的压电元件的制造方法中设置第1电极层的状态的剖视图。

27.图13是表示本发明的实施方式3的压电元件的剖视图。

28.图14是表示在本发明的实施方式3的压电元件的制造方法中在贯通孔填充连接电极的状态的剖视图。

29.图15是表示本发明的实施方式4的压电元件的剖视图。

30.图16是表示在本发明的实施方式4的压电元件的制造方法中使接合层层叠于压电体基板的状态的剖视图。

31.图17是表示在本发明的实施方式4的压电元件的制造方法中接合层由多个层形成的情况的即将使第2接合层接合于第1接合层之前的状态的剖视图。

32.图18是表示在本发明的实施方式4的压电元件的制造方法中使压电体基板上的接合层接合于包含第2电极层的层叠基板的状态的剖视图。

33.图19是表示在本发明的实施方式4的压电元件的制造方法中切削压电体基板而形成压电体层的状态的剖视图。

34.图20是表示在本发明的实施方式4的压电元件的制造方法中设置第1电极层的状态的剖视图。

35.图21是表示在本发明的实施方式4的压电元件的制造方法中设置连接电极的状态的剖视图。

36.图22是表示本发明的实施方式5的压电元件的剖视图。

37.图23是表示本发明的实施方式6的压电元件的剖视图。

38.图24是表示在本发明的实施方式6的压电元件的制造方法中在层叠基板上设置第2电极层的状态的剖视图。

39.图25是表示在本发明的实施方式6的压电元件的制造方法中使压电体基板接合于设于层叠基板上的第2电极层的状态的剖视图。

40.图26是表示在本发明的实施方式6的压电元件的制造方法中切削压电体基板而形成压电体层的状态的剖视图。

41.图27是表示在本发明的实施方式6的压电元件的制造方法中设置第1电极层的状态的剖视图。

42.图28是表示在本发明的实施方式6的压电元件的制造方法中设置连接电极的状态的剖视图。

43.图29是表示本发明的实施方式7所示的压电元件的剖视图。

44.图30是表示本发明的实施方式8所示的压电元件的剖视图。

45.图31是表示在本发明的实施方式8的压电元件的制造方法中接合层由多个层形成的情况的即将使第2接合层接合于第1接合层之前的状态的剖视图。

46.图32是表示在本发明的实施方式8的压电元件的制造方法中使压电体基板上的接合层接合于设于层叠基板上的第2电极层的状态的剖视图。

47.图33是表示在本发明的实施方式8的压电元件的制造方法中切削压电体基板而形成压电体层的状态的剖视图。

48.图34是表示在本发明的实施方式8的压电元件的制造方法中设置第1电极层的状态的剖视图。

49.图35是表示在本发明的实施方式8的压电元件的制造方法中设置连接电极的状态的剖视图。

50.图36是表示本发明的实施方式9的压电元件的剖视图。

具体实施方式

51.以下,参照附图,说明本发明的各实施方式的压电元件。在以下的实施方式的说明中,对图中的相同或相当的部分标注相同的附图标记,不重复其说明。

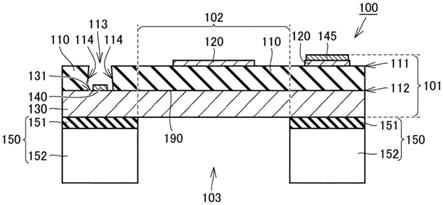

52.(实施方式1)

53.图1是表示本发明的实施方式1的压电元件的概略俯视图。图2是从

ⅱ‑ⅱ

线箭头方向观察图1的压电元件而得到的剖视图。

54.如图1和图2所示,本发明的实施方式1的压电元件100包括压电体层110、第1电极层120、第2电极层130、连接电极140、外侧连接电极145以及基部150。

55.如图2所示,压电体层110具有第1面111、第2面112以及贯通孔113。第2面112位于与第1面111相反的那一侧,与第1面111相对。贯通孔113从第1面111贯通到第2面112。贯通孔113随着从第1面111朝向第2面112而扩大。具体而言,贯通孔113从第1面111朝向第2面112连续地扩大。

56.在本实施方式中,压电体层110由碱金属铌酸盐类的化合物或碱金属钽酸盐类的化合物构成。在本实施方式中,上述碱金属铌酸盐类的化合物或上述碱金属钽酸盐类的化合物所含有的碱金属由锂、铷以及铯中的至少一者形成。压电体层110例如由铌酸锂(linbo3)或钽酸锂(litao3)构成。在本实施方式中,压电体层110由单晶形成。

57.第1电极层120设于压电体层110的第1面111上。密合层位于第1电极层120与压电体层110之间。第1电极层120例如由al或pt等金属构成。上述密合层例如由ti或nicr构成。

58.第2电极层130位于压电体层110的第2面112侧。第2电极层130至少局部隔着压电体层110而与第1电极层120相对。在本实施方式中,第2电极层130仅隔着压电体层110和后述的第2电极层130的自然氧化膜层而与第1电极层120相对。即,第2电极层130与压电体层110的第2面112连接。

59.第2电极层130面向贯通孔113。第2电极层130具有连接面131。第2电极层130中的连接面131在不与第1电极层120相对的区域中面向贯通孔113。连接面131的位置与第2电极层130的压电体层110侧的面中的连接面131以外的部分的位置的与第1面111垂直的方向上的差为5nm以下。换言之,在将第2电极层130的压电体层110侧的面中的连接面131以外的部分作为基准面时,连接面131在从第1面111朝向第2面112的方向上位于相对于该基准面而言5nm以下的范围。另外,在本实施方式中,以上述基准面与连接面131相互分离的方式在第2电极层130的压电体层110侧的面形成有台阶。在本实施方式中,由该基准面和连接面131形成的台阶的与第1面111垂直的方向上的高度的尺寸为5nm以下。上述的差、连接面131相对于基准面的位置和高度的尺寸能够通过使用透射式电子显微镜(tem:transmission electron microscope)直接观察将压电元件100相对于第1面111垂直地剖切时的截面来确认。

60.第2电极层130的压电体层110侧的连接面131以外的部分被自然氧化膜层覆盖。第2电极层130的连接面131也可以被自然氧化膜层覆盖,但在后述的与连接电极140的接合部处,优选去除上述自然氧化膜层。在本实施方式中,位于连接面131上的自然氧化膜层被去除。

61.第2电极层130含有硅作为主要成分。在本实施方式中,第2电极层130含有单晶硅作为主要成分。更具体而言,第2电极层130由掺杂有降低第2电极层130的电阻率的元素的

单晶硅构成。第2电极层130例如掺杂有硼(b)、铝(al)、镓(ga)、磷(p)、砷(as)或锑(sb)等元素。在本实施方式中,优选构成第2电极层130的材料的电阻率较低,具体而言,优选20mω

·

cm以下。此外,在本实施方式中,由cf4气体进行的反应性离子蚀刻(rie)中的构成第2电极层130的材料的蚀刻速率比构成压电体层110的材料的蚀刻速率大。具体而言,构成第2电极层130的材料的上述蚀刻速率是构成压电体层110的材料的蚀刻速率的1.5倍以上。

62.在本实施方式中,第2电极层130含有硅作为主要成分,因此上述自然氧化膜层是氧化硅。在本实施方式中,自然氧化膜的厚度约为1nm以上且2nm以下。

63.在本实施方式中,第2电极层130与压电体层110之间的界面190由通过表面活化接合或原子扩散接合而形成的界面接合部构成。

64.在本实施方式中,压电体层110由单晶形成,第2电极层130含有单晶硅作为主要成分,因此压电元件100的电机转换效率良好。

65.如图2所示,连接电极140设于第2电极层130中的面向贯通孔113的连接面131上。在本实施方式中,连接电极140位于与贯通孔113的内表面114分开的位置。连接电极140例如由au构成。也可以是,在连接电极140与第2电极层130之间形成有密合层。该密合层例如由ti或nicr构成。

66.如图2所示,在本实施方式中,层叠体101至少包含压电体层110、第1电极层120以及第2电极层130。另外,层叠体101还包含连接电极140和外侧连接电极145。基部150支承该层叠体101。

67.如图2所示,基部150位于层叠体101的第2电极层130侧。如图1所示,基部150以在从层叠体101的层叠方向观察时沿着层叠体101的基部150侧的面的周缘的方式形成为环状。

68.如图2所示,在本实施方式中,基部150包含氧化硅层151和基部主体152。氧化硅层151与第2电极层130接触。基部主体152在氧化硅层151的与第2电极层130侧相反的那一侧与氧化硅层151接触。在本实施方式中,构成基部主体152的材料没有特别限定,基部主体152由单晶硅形成。

69.如图2所示,开口103在从层叠体101的层叠方向观察时位于基部150的内侧。开口103的端缘在从上述层叠方向观察时具有圆形状的外形,沿着上述层叠方向延伸,但开口103的外形的形状没有特别限定。

70.如图1和图2所示,在本实施方式中,在层叠体101形成有膜片部102。膜片部102在从层叠方向观察时与开口103重叠,不与基部150重叠。

71.本实施方式的压电元件100通过向图2所示的外侧连接电极145与连接电极140之间施加电压来向图2所示的第1电极层120与第2电极层130之间施加电压。由此,以位于第1电极层120与第2电极层130之间的压电体层110变形的方式驱动。由此,膜片部102能够在层叠体101的层叠方向上大幅弯曲振动。

72.以下,说明本发明的实施方式1的压电元件的制造方法。基于本发明的实施方式的压电元件100的制造方法至少包括在压电体基板110s中形成凹部113s的工序、形成压电体层110的工序、配置第2电极层130的工序以及层叠第1电极层120的工序。此外,以下的图3~图8所示的各状态以与图2相同的剖视进行图示。

73.图3是表示在本发明的实施方式1的压电元件的制造方法中在压电体基板形成凹

部的状态的剖视图。

74.如图3所示,压电体基板110s具有第1主面111s和位于与第1主面111s相反的那一侧的第2主面112s。第2主面112s与第1主面111s相对。在压电体基板110s中形成凹部113s的工序中,利用蚀刻法在第2主面112s侧形成凹部113s。用于形成凹部113s的蚀刻法既可以是干蚀刻,也可以是湿蚀刻。如后述那样,凹部113s的深度适当调整为能够由凹部113s形成贯通孔113的深度即可。

75.图4是在本发明的实施方式1的压电元件的制造方法中准备包含第2电极层的层叠基板的剖视图。如图4所示,准备包含第2电极层130和基部150的层叠基板104s。在本实施方式中,层叠基板104s是soi(silicon on insulator)基板。

76.图5是表示在本发明的实施方式1的压电元件的制造方法中使压电体基板接合于包含第2电极层的层叠基板的状态的剖视图。如图5所示,在本实施方式中,当在压电体基板110s形成凹部113s之后,使第2电极层130接合于压电体基板110s。另外,在本实施方式中,通过表面活化接合或原子扩散接合而使压电体基板110s接合于层叠基板104s。这样,在本实施方式中,能够将使用基板所包含的层作为电极层,因此不需要在基板上进一步层叠电极层的工序。

77.图6是表示在本发明的实施方式1的压电元件的制造方法中切削压电体基板而形成压电体层的状态的剖视图。如图6所示,在形成压电体层110的工序中,在例如利用磨床从第1主面111s侧磨削压电体基板110s而使其变薄之后,利用cmp(chemical mechanical polishing)等进行抛光而使其平坦,从而使第1面111暴露,并且,去除凹部113s的底部而形成由凹部113s的内表面114形成的贯通孔113。

78.这样,在本实施方式的压电元件100的制造方法中,在压电体层110的第2面112侧,以至少局部面向贯通孔113的方式配置第2电极层130。

79.另外,也可以通过预先向压电体基板110s的第2主面112s侧注入离子来形成剥离层。通过在使压电体基板110s接合于第2电极层130之前预先形成该剥离层,能够在接合后剥离该剥离层而形成压电体层110。

80.图7是表示在本发明的实施方式1的压电元件的制造方法中设置第1电极层的状态的剖视图。

81.这样,在层叠第1电极层120的工序中,在压电体层110的第1面111侧,以至少局部隔着压电体层110而与第2电极层130相对的方式层叠第1电极层120。第1电极层120使用蒸镀剥离法等而形成为具有期望的图案。

82.图8是表示在本发明的实施方式1的压电元件的制造方法中设置连接电极的状态的剖视图。如图8所示,使用蒸镀剥离法等而形成连接电极140和外侧连接电极145。在本实施方式中,在形成连接电极140之前,利用湿蚀刻等蚀刻法去除连接面131处的第2电极层130的自然氧化膜层。通过自然氧化膜层的去除,由于自然氧化膜层的厚度约为1nm以上且2nm以下,因此连接面131与第2电极层130的压电体层110侧的面中的连接面131以外的部分的位置的与第1面111垂直的方向上的差为5nm以下。在利用蚀刻法去除的层的厚度为5nm以下这样的非常薄的情况下,连接面131处的接触电阻不会由于连接面131的改性等而显著变高。即,在本实施方式中,通过上述的自然氧化膜层的去除,在图8中虽未图示,但在第2电极层130的压电体层110侧的面处成为连接面131凹陷的凹面形状。

83.最后,通过深反应离子蚀刻(deep rie),从基部150的与第2电极层130侧相反的那一侧形成本实施方式的压电元件100的开口103。此外,在本实施方式中,为了形成开口103而对氧化硅层151进行蚀刻,但也可以不对氧化硅层151进行蚀刻,也可以是,对氧化硅层151的层叠基板104s的层叠方向上的局部进行蚀刻。

84.通过上述的工序,制造如图1和图2所示那样的本发明的实施方式1的压电元件100。

85.如上述那样,在本发明的实施方式1的压电元件100中,第2电极层130具有连接面131。连接面131在第2电极层130中的不与第1电极层120相对的区域中面向贯通孔113。连接电极140设于第2电极层130中的面向贯通孔113的连接面131上。连接面131与第2电极层130的压电体层110侧的面中的连接面131以外的部分的位置的差为5nm以下。

86.由此,在本实施方式中,连接面131不受用于形成贯通孔113的蚀刻的影响而上述位置的差为5nm以下,从而能够抑制第2电极层130的连接面131的结晶性紊乱的情况。进而,能够抑制第2电极层130的连接面131与连接电极140的接合部处的断路不良的产生。

87.贯通孔113随着从第1面111朝向第2面112而扩大。

88.由此,能够减小第2电极层130与连接电极140的接合部的电阻率。即,对于贯通孔113,使第2面112侧的端部的截面面积比第1面111侧的端部的截面面积大,因此能够扩大第2电极层130与连接电极140的连接面积,减小第2电极层130与连接电极140的接触电阻。

89.特别是,在利用剥离法形成连接电极140的情况下,连接电极140的形成变得容易,因此难以产生连接电极140与第2电极层130的连接不良,压电元件100的成品率提高。

90.贯通孔113从第1面111面向第2面112连续地扩大。

91.由此,与将贯通孔113的内表面形成为台阶状的情况相比,能够减少贯通孔113的形成工序。

92.连接电极140位于与贯通孔113的内表面114分开的位置。

93.由此,连接电极140不与由容易产生应力集中的贯通孔113的内表面114和第1面111构成的角部接触,因此能够抑制在连接电极140产生裂纹的情况。

94.由cf4气体进行的反应性离子蚀刻中的构成第2电极层130的材料的蚀刻速率比构成压电体层110的材料的蚀刻速率大。

95.在本实施方式中,即使在具有如上述那样的蚀刻速率的差而导致第2电极层130比压电体层110容易被蚀刻的情况下,上述位置的差也成为5nm以下,连接面131也处于不受由用于形成贯通孔113的蚀刻造成的影响的状态。因此,能够抑制第2电极层130的连接面131的结晶性紊乱的情况。进而,能够抑制第2电极层130的连接面131与连接电极140的断路不良的产生。

96.压电体层110由碱金属铌酸盐类的化合物或碱金属钽酸盐类的化合物构成。上述碱金属铌酸盐类的化合物或上述碱金属钽酸盐类的化合物所含有的碱金属由锂、铷以及铯中的至少一者形成。第2电极层130含有硅作为主要成分。

97.由此,能够使压电体层110的介电常数比较低。另外,压电体层110的电阻变高,因此相对于含有硅作为主要成分的第2电极层130而言向压电体层110施加的电压变大,能够提高压电元件100的驱动效率。

98.压电体层110由铌酸锂构成。由此,与压电体层110由其他碱金属铌酸盐类的化合

物或碱金属钽酸盐类的化合物构成的情况相比,能够提高压电体层110的压电常数,因此能够提高压电元件100的装置特性。

99.压电体层110由钽酸锂构成。由此,与压电体层110由其他碱金属铌酸盐类的化合物或碱金属钽酸盐类的化合物构成的情况相比,压电体层110的介电常数变低,因此压电体层110的电阻变高,压电元件100的驱动效率提高,能够提高压电元件100的装置特性。

100.第2电极层130含有单晶硅作为主要成分。由此,压电体层110与第2电极层130的接合强度提高,能够提高压电体层110的电机转换效率。

101.压电元件100还包括基部150,该基部150支承至少包含第1电极层120、压电体层110以及第2电极层130的层叠体101。基部150位于层叠体101的第2电极层130侧,并且,以在从层叠体101的层叠方向观察时沿着层叠体101的基部150侧的面的周缘的方式形成为环状。

102.由此,能够将压电体层110的驱动转换为膜片部102的弯曲振动,提高压电元件100的装置特性。

103.基部150包含与第2电极层130接触的氧化硅层。第2电极层130由掺杂有降低第2电极层130的电阻率的元素的单晶硅构成。

104.由此,能够使用层叠基板将第2电极层130和基部150同时连接于压电体层110,并且,能够提高第2电极层130的电流效率。

105.基于本发明的实施方式的压电元件100的制造方法包括在压电体基板110s中形成凹部113s的工序、形成压电体层110的工序、配置第2电极层130的工序以及层叠第1电极层120的工序。压电体基板110s具有第1主面111s和与第1主面111s相对的第2主面112s。在压电体基板110s中形成凹部113s的工序中,利用蚀刻法在第2主面112s侧形成上述凹部113s。在形成压电体层110的工序中,通过在从第1主面111s侧磨削压电体基板110s之后进行抛光,从而使第1面111暴露,并且,去除凹部113s的底部而形成由凹部113s的内表面114形成的贯通孔113。在配置第2电极层130的工序中,在压电体层110的第2面112侧,以至少局部面向贯通孔113的方式配置第2电极层130。在层叠第1电极层120的工序中,在压电体层110的第1面111侧,以至少局部隔着压电体层110而与第2电极层130相对的方式层叠第1电极层120。

106.这样,与贯通孔113对应的凹部113s在将第2电极层130配置于压电体基板110s之前利用蚀刻法形成,因此在贯通孔113形成时第2电极层130未被蚀刻。由此,能够抑制第2电极层130的连接面131的结晶性紊乱的情况,抑制第2电极层130的连接面131与连接电极140的接合部处的电阻率的上升,进而,抑制第2电极层130的断路不良的产生。

107.而且,如上述那样,在本实施方式的压电元件100中,由cf4气体进行的反应性离子蚀刻中的构成第2电极层130的材料的蚀刻速率比构成压电体层110的材料的蚀刻速率大。因此,假若在将第2电极层130配置于压电体基板110s之后利用蚀刻法形成贯通孔113,则对第2电极层130进行过蚀刻。由于该过蚀刻,第2电极层130的表面改性或厚度变小,从而在上述接合部处电阻率上升。然而,在本实施方式中,如上述那样形成贯通孔113,因此在贯通孔113形成时不会对第2电极层130进行过蚀刻。因此,在本实施方式中,能够在抑制上述接合部处的电阻率的上升的同时采用蚀刻速率比构成压电体层110的材料的蚀刻速率大的材料作为构成第2电极层130的材料。

108.另外,贯通孔113由在压电体基板110s从第2主面112s侧利用蚀刻法形成的凹部113s的内表面114形成,因此能够使贯通孔113形成为随着从第1面111朝向第2面112而扩大那样的形状。由此,能够扩大第2电极层130与连接电极140的连接面积,减小第2电极层130与连接电极140的接合部处的接触电阻。

109.(实施方式2)

110.以下,说明本发明的实施方式2的压电元件。本发明的实施方式2的压电元件的构造与本发明的实施方式1的压电元件100的构造相同,但本发明的实施方式2的压电元件的制造方法与本发明的实施方式1的压电元件100的制造方法不同。由此,对本发明的实施方式2的压电元件仅说明制造方法,对与本发明的实施方式1的压电元件100的制造方法同样的结构不重复说明。

111.图9是表示在本发明的实施方式2的压电元件的制造方法中在第2电极层上设置连接电极的状态的剖视图。如图9所示,在本发明的实施方式2的压电元件的制造方法中,在将第2电极层130配置于压电体层110的第2面112侧之前,在第2电极层130上形成连接电极140。连接电极140能够利用蒸镀法、溅射法或镀敷法等方法形成。

112.图10是表示在本发明的实施方式2的压电元件的制造方法中使压电体基板接合于包含第2电极层的层叠基板的状态的剖视图。如图10所示,使形成有凹部113s的压电体基板110s与第2电极层130接合。此时,以凹部113s的内表面114与连接电极140相互不接触的方式使压电体基板110s与第2电极层130接合。在本实施方式中,优选的是,在形成连接电极140之前,利用蚀刻等去除第2电极层130整体的自然氧化膜。

113.图11是表示在本发明的实施方式2的压电元件的制造方法中切削压电体基板而形成压电体层的状态的剖视图。如图11所示,与本发明的实施方式1的压电元件100的制造方法同样地形成压电体层110。

114.图12是表示在本发明的实施方式2的压电元件的制造方法中设置第1电极层的状态的剖视图。如图12所示,利用与本发明的实施方式1的压电元件100的制造方法同样的方法,层叠第1电极层120。最后,利用与本发明的实施方式1的压电元件100的制造方法同样的方法,形成开口103。

115.通过上述的工序,能够制造与图1和图2所示的本发明的实施方式1的压电元件100同样的压电元件。

116.(实施方式3)

117.以下,说明本发明的实施方式3的压电元件。本发明的实施方式3的压电元件主要在连接电极的结构上与本发明的实施方式1的压电元件100不同。由此,对与本发明的实施方式1的压电元件100同样的结构不重复说明。

118.图13是表示本发明的实施方式3的压电元件的剖视图。如图13所示,在本发明的实施方式3的压电元件300中,贯通孔113被连接电极340填充。由此,能够提高连接电极340的相对于第2电极层130的剥离强度,能够提高压电元件300的可靠性。另外,在通过倒装接合来安装压电元件300时,能够以在从与第1面111垂直的方向观察时与贯通孔113重叠的方式设置钎焊凸块360,因此能够使压电元件300小型化。

119.另外,在本实施方式中,贯通孔113随着从第1面111朝向第2面而扩大,因此能够进一步抑制填充于贯通孔113的连接电极340朝向比第1面111靠外侧的位置剥离。

120.接着,说明本发明的实施方式3的压电元件300的制造方法。在本发明的实施方式3的压电元件300的制造方法中,如图7所示,与本发明的实施方式1的压电元件的制造方法同样地形成贯通孔113。

121.图14是表示在本发明的实施方式3的压电元件的制造方法中在贯通孔填充连接电极的状态的剖视图。如图14所示,形成连接电极340和外侧连接电极145。在本实施方式中,连接电极340使用镀敷法形成。由此,贯通孔113被连接电极340填充。连接电极340和外侧连接电极145既可以同时形成,也可以在形成连接电极340和外侧连接电极145中的一者之后形成另一者。

122.最后,利用与本发明的实施方式1的压电元件100的制造方法同样的方法,形成开口103。通过上述的工序,能够制造图13所示的本发明的实施方式3的压电元件300。

123.(实施方式4)

124.以下,说明本发明的实施方式4的压电元件。本发明的实施方式4的压电元件主要在还包括接合层这一点上与本发明的实施方式1的压电元件100不同。由此,对与本发明的实施方式1的压电元件100同样的结构不重复说明。

125.图15是表示本发明的实施方式4的压电元件的剖视图。如图15所示,在本发明的实施方式4的压电元件400中,接合层470位于第2电极层130的压电体层110侧的连接面131以外的部分与压电体层110之间。由此,压电体层110与第2电极层130的接合强度提高。

126.在本实施方式中,接合层470还位于贯通孔113的内表面114上。由此,贯通孔113的内表面114的耐环境性提高。

127.在本实施方式中,接合层470由氧化硅(sio2)形成。由此,能够在考虑接合层470的介电常数的同时在第2电极层130与压电体层110之间设置适当的厚度的接合层470。接合层470也可以含有金属。

128.此外,接合层470也可以由多个层构成,该多个层也可以具有金属层。在接合层470由多个层构成的情况下,接合层470中的与第2电极层130接触的部分也可以由第2电极层130的自然氧化膜层构成。上述自然氧化膜层例如由sio2形成。

129.以下,说明本发明的实施方式4的压电元件的制造方法。在本发明的实施方式4的压电元件的制造方法中,首先,如图3所示,与本发明的实施方式1的压电元件的制造方法同样地在压电体基板110s形成凹部113s。

130.图16是表示在本发明的实施方式4的压电元件的制造方法中使接合层层叠于压电体基板的状态的剖视图。如图16所示,利用cvd(chemical vapor deposition)法或pvd(physical vapor deposition)法等,在压电体基板的第2主面112s上和凹部113s的内表面114和底面层叠接合层470。

131.此外,在接合层470由多个层构成,接合层470中的与第2电极层130接触的部分由第2电极层130的自然氧化膜层构成的情况下,在利用层叠上述接合层470的方法层叠第1接合层之后,使作为自然氧化膜层的第2接合层接合于第1接合层即可。图17是表示在本发明的实施方式4的压电元件的制造方法中接合层由多个层形成的情况的即将使第2接合层接合于第1接合层之前的状态的剖视图。如图17所示,使作为第2电极层130的自然氧化膜层的第2接合层472接合于层叠的第1接合层471。此外,在使第1接合层471与第2接合层472接合的情况下,通过预先去除层叠基板104s中的第2电极层130的面向压电体基板110s的凹部

113s的部分的自然氧化膜层,从而避免第2接合层472面向凹部113s。

132.图18是表示在本发明的实施方式4的压电元件的制造方法中使压电体基板上的接合层接合于包含第2电极层的层叠基板的状态的剖视图。如图18所示,通过表面活化接合或原子扩散接合,使第2电极层130与压电体基板110s借助接合层470而相互接合。此外,如图16所示,在接合层470包含第1接合层471和第2接合层472的情况下,使第2电极层130与压电体基板110s借助第1接合层471和第2接合层472而相互接合。

133.图19是表示在本发明的实施方式4的压电元件的制造方法中切削压电体基板而形成压电体层的状态的剖视图。如图19所示,在凹部113s中,层叠有接合层470的底部与接合层470一起被去除。

134.图20是表示在本发明的实施方式4的压电元件的制造方法中设置第1电极层的状态的剖视图。如图20所示,在压电体层110的第1面111侧层叠第1电极层120。

135.图21是表示在本发明的实施方式4的压电元件的制造方法中设置连接电极的状态的剖视图。如图21所示,与本发明的实施方式1的压电元件100同样地形成连接电极140和外侧连接电极145。并且,最后,通过形成开口103,制造图15所示的本发明的实施方式4的压电元件400。

136.(实施方式5)

137.以下,说明本发明的实施方式5的压电元件。本发明的实施方式5的压电元件主要在连接电极的结构上与本发明的实施方式4的压电元件400不同。由此,对与本发明的实施方式4的压电元件400同样的结构不重复说明。

138.图22是表示本发明的实施方式5的压电元件的剖视图。在本发明的实施方式5的压电元件500中,与本发明的实施方式3的压电元件300同样,贯通孔113被连接电极340填充。由此,能够提高连接电极340的相对于第2电极层130的剥离强度。

139.(实施方式6)

140.以下,说明本发明的实施方式6的压电元件。本发明的实施方式6的压电元件主要在第2电极层与层叠基板分开地设置这一点上与本发明的实施方式1的压电元件100不同。由此,对与本发明的实施方式1的压电元件100同样的结构不重复说明。

141.图23是表示本发明的实施方式6的压电元件的剖视图。如图23所示,在本发明的实施方式6的压电元件600中,压电体层110由铌酸锂构成。第2电极层630由金属材料构成。第2电极层630例如由al或pt构成。

142.在本实施方式中,即使当在压电体层110使用蚀刻速率比第2电极层630所使用的金属材料的蚀刻速率低的铌酸锂的情况下,在贯通孔113的形成时第2电极层630也不被蚀刻。由此,能够抑制第2电极层630的结晶性的紊乱,抑制产生由在连接面131中的连接电极140与第2电极层630的接合部处电连接变得不充分引起的断路不良的情况。

143.在本实施方式中,硅层680位于第2电极层630的与压电体层110侧相反的那一侧的面上。由此,硅层680也与第2电极层630一起作为电极层发挥功能,因此电流效率提高。

144.这样,在本实施方式中,层叠体101还包含硅层680。基部150位于层叠体101的硅层680侧。

145.以下,说明本发明的实施方式6的压电元件的制造方法。图24是表示在本发明的实施方式6的压电元件的制造方法中在层叠基板上设置第2电极层的状态的剖视图。如图24所

示,在本实施方式中,层叠基板104s包含硅层680和基部150。并且,利用cvd法或pvd法等,在层叠基板104s的硅层680上设置第2电极层630。

146.图25是表示在本发明的实施方式6的压电元件的制造方法中使压电体基板接合于设于层叠基板上的第2电极层的状态的剖视图。如图25所示,通过表面活化接合或原子扩散接合,在第2电极层630上接合图3所示的形成有凹部113s的压电体基板110s。

147.图26是表示在本发明的实施方式6的压电元件的制造方法中切削压电体基板而形成压电体层的状态的剖视图。如图26所示,与本发明的实施方式1的压电元件100的制造方法同样,在例如利用磨床磨削压电体基板110s而使其变薄之后,利用cmp等进行抛光而使其平坦,形成压电体层110。这样,在本实施方式中,与贯通孔113对应的凹部113s在将第2电极层630配置于压电体基板110s之前利用蚀刻法形成,因此在贯通孔113形成时第2电极层630未被蚀刻。由此,能够抑制第2电极层630的连接面131紊乱的情况,抑制第2电极层630的连接面131与连接电极140的接合部处的电阻率的上升,进而,能够抑制第2电极层630的断路不良的产生。

148.而且,如上述那样,在本实施方式的压电元件600中,在压电体层110由铌酸锂构成,并且,构成第2电极层630的金属材料的蚀刻速率比铌酸锂的蚀刻速率大的情况下,假若在将第2电极层630配置于压电体基板110s之后利用蚀刻法形成贯通孔113,则对第2电极层630进行过蚀刻。由于该过蚀刻,第2电极层630的表面改性或厚度变小,从而上述接合部处的电阻率上升。然而,在本实施方式中,如上述那样形成贯通孔113,因此在贯通孔113形成时不会对第2电极层630进行过蚀刻。因此,在本实施方式中,能够在抑制上述接合部处的电阻率的上升的同时采用蚀刻速率比铌酸锂的蚀刻速率大的金属材料作为第2电极层630。

149.图27是表示在本发明的实施方式6的压电元件的制造方法中设置第1电极层的状态的剖视图。如图27所示,与本发明的实施方式1的压电元件100的制造方法同样地设置第1电极层120。

150.图28是表示在本发明的实施方式6的压电元件的制造方法中设置连接电极的状态的剖视图。如图28所示,形成连接电极140和外侧连接电极145。在本实施方式中,连接面131也可以被自然氧化膜覆盖,但在与连接电极140的接合部处,优选去除上述自然氧化膜。在本实施方式中,优选的是,在形成连接电极140之前,利用蚀刻等去除连接面131整体的自然氧化膜层。并且,通过最后形成开口103,从而制造图23所示的本发明的实施方式6的压电元件600。

151.(实施方式7)

152.以下,说明本发明的实施方式7的压电元件。本发明的实施方式7的压电元件主要在连接电极的结构上与本发明的实施方式6的压电元件600不同。由此,对与本发明的实施方式6的压电元件600同样的结构不重复说明。

153.图29是表示本发明的实施方式7所示的压电元件的剖视图。在本发明的实施方式7的压电元件700中,与本发明的实施方式3的压电元件300同样,贯通孔113被连接电极340填充。由此,能够提高连接电极340的相对于第2电极层630的剥离强度。

154.(实施方式8)

155.以下,说明本发明的实施方式8的压电元件。本发明的实施方式8的压电元件主要在第2电极层与层叠基板分开地设置这一点上且主要在连接电极的结构上与本发明的实施

方式4的压电元件400不同。由此,对与本发明的实施方式4的压电元件400同样的结构不重复说明。

156.图30是表示本发明的实施方式8所示的压电元件的剖视图。如图30所示,在本发明的实施方式8的压电元件800中,与本发明的实施方式6的压电元件600同样,第2电极层630由金属材料构成,硅层680位于第2电极层630的与压电体层110侧相反的那一侧的面上。在本实施方式中也是,通过接合层470位于由金属材料构成的第2电极层630与压电体层110之间,压电体层110与第2电极层630的接合强度提高。

157.以下,说明本发明的实施方式8的压电元件的制造方法。首先,如图16所示,与本发明的实施方式4的压电元件400的制造方法同样,在形成有凹部113s的压电体基板110s上形成接合层470。并且,如图24所示,与本发明的实施方式6的压电元件600的制造方法同样,在层叠基板104s的硅层680上设置第2电极层630。

158.在此,与本发明的实施方式4的压电元件400的制造方法同样,接合层470由氧化硅(sio2)形成。接合层470也可以由多个层构成。该多个层也可以具有金属层。在接合层470由多个层构成的情况下,也可以是,接合层470中的与第2电极层630接触的部分由第2电极层630的自然氧化膜层构成。图31是表示在本发明的实施方式8的压电元件的制造方法中接合层由多个层形成的情况的即将使第2接合层接合于第1接合层之前的状态的剖视图。是表示在本发明的实施方式8的压电元件的制造方法中,在接合层由多个层形成的情况下,即将使第2接合层接合于第1接合层之前的状态的图。如图31所示,使第2接合层472接合于层叠的第1接合层471。此外,在使第1接合层471与第2接合层472接合的情况下,通过预先去除第2电极层630的面向压电体基板110s的凹部113s的部分的第2接合层472,从而避免第2接合层472面向凹部113s。

159.图32是表示在本发明的实施方式8的压电元件的制造方法中使压电体基板上的接合层接合于设于层叠基板上的第2电极层的状态的剖视图。如图32所示,通过表面活化接合或原子扩散接合,使第2电极层630与压电体基板110s借助接合层470而相互接合。此外,如图31所示,在接合层470包含第1接合层471和第2接合层472的情况下,使第2电极层630与压电体基板110s借助第1接合层471和第2接合层472而相互接合。

160.图33是表示在本发明的实施方式8的压电元件的制造方法中切削压电体基板而形成压电体层的状态的剖视图。如图33所示,在凹部113s中,接合有接合层470的底部与接合层470一起被去除。

161.图34是表示在本发明的实施方式8的压电元件的制造方法中设置第1电极层的状态的剖视图。如图34所示,在压电体层110的第1面111侧层叠第1电极层120。

162.图35是表示在本发明的实施方式8的压电元件的制造方法中设置连接电极的状态的剖视图。如图35所示,与本发明的实施方式1的压电元件100同样地形成连接电极140和外侧连接电极145。并且,最后,通过形成开口103,制造图35所示的本发明的实施方式8的压电元件800。

163.(实施方式9)

164.以下,说明本发明的实施方式9的压电元件。本发明的实施方式9的压电元件主要在连接电极的结构上与本发明的实施方式8的压电元件800不同。由此,对与本发明的实施方式8的压电元件800同样的结构不重复说明。

165.图36是表示本发明的实施方式9的压电元件的剖视图。在本发明的实施方式9的压电元件900中,与本发明的实施方式3的压电元件300同样,贯通孔113被连接电极340填充。由此,能够提高连接电极340的相对于第2电极层630的剥离强度。

166.在上述的实施方式的说明中,也可以将能够组合的结构相互组合。

167.应该认为本次公开的实施方式在所有的方面为例示而并非限制。本发明的范围由权利要求书表示而不由上述的说明表示,意图包含在与权利要求书等同的含义和范围内的所有的变更。

168.附图标记说明

169.100、300、400、500、600、700、800、900、压电元件;101、层叠体;102、膜片部;103、开口;104s、层叠基板;110、压电体层;110s、压电体基板;111、第1面;111s、第1主面;112、第2面;112s、第2主面;113、贯通孔;113s、凹部;114、内表面;120、第1电极层;130、630、第2电极层;131、连接面;140、340、连接电极;145、外侧连接电极;150、基部;151、氧化硅层;152、基部主体;190、界面;360、钎焊凸块;470、接合层;471、第1接合层;472、第2接合层;680、硅层。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。