1.本发明涉及一种判别电平自适应的高精度输入信号接收电路,属于集成电路技术领域。

背景技术:

2.在智能电网、移动通信以及新能源汽车等新兴产业的牵引下,电力电子应用系统要求进一步提高系统的效率、小型化和增加功能,特别要求系统装备在尺寸、质量、功率和效率之间的权衡,比如服务器电源管理、电池充电器和太阳能电场的微逆变器。新一代电力电子整机系统对其内部高压集成电路(hvic)的可靠性、速度、智能化提出了更高的需求,从而进一步提高整机可靠性,并降低整机系统设计复杂度。功率集成电路(power integrated circuit)作为系统信号处理部分和执行部分的桥梁,将功率器件与控制电路、外围接口电路及保护电路等集成在一起。功率集成技术就是需要在有限的芯片面积上实现高低压兼容、高性能、高效率与高可靠性。功率集成技术范畴包括用于制备功率集成电路的所有制造技术。

3.驱动芯片的输入控制信号为cpu控制器输出的pwm方波信号,通常为标准的数字逻辑电平。为了提高驱动电路对输入信号的兼容性,以及滤除输入信号中可能存在的噪声,在驱动电路的输入端,驱动芯片必须设置接口电路,对输入信号进行预处理。数字电路发展的早期,绝大多数数字器件都采用ttl和cmos数字逻辑标准,其中逻辑高电平为5v。近几年,在功耗低、体积小的便携式设备和高速通信设备应用需求驱动下,产生了许多针对不同应用的低压、高速的数字逻辑标准,例如lvttl、lvcmos、hstl、sstl、lvpecl等,逻辑高电平电压不断降低。

4.图1示出了一种现有的基本输入接口电路结构,包括输入esd(静电放电)保护电路和电平判别电路。接口电路不仅要完成信号的传输,还要完成对芯片内部的电路的esd保护,防止由于esd造成对电路内部的冲击而损毁电路。常用于集成电路设计的esd保护的电路有:横向scr、反向并联二极管、齐纳钳位和cdm钳位电路等。电平判别电路用于识别外部输入电平是逻辑“0”还是“1”,由于外部信号存在很大干扰,电平判别电路必须具备足够的抗干扰噪声容限。具体电路实现通常包括2种形式,一种为schmitt触发器,一种为迟滞比较器。根据驱动芯片驱动对象和输入逻辑信号的速度不同,schmitt触发器和迟滞比较器的实现电路存在很大差异。

5.一般理想的电平判别波形如图2上半部分所示,当输入信号高于判别电平时,输出信号为高电平;当输入信号低于判别电平,输出信号为低电平。但由于存在电源电压波动、衬底噪声以及共模尖峰干扰等影响,会使输入信号产生严重的尖峰噪声,导致实际的判别波形如图2下半部分所示,输入信号的高低电平判别输出会出现一定的信号误差,误差宽度足够宽时后续的滤波电路将难以滤除,形成数据错误。

6.为克服现有技术中各种噪声的影响,目前有采用差分比较判别技术对共模干扰引起的误差进行抑制,其电路框图如图3所示。输入信号vin同时进入正端电平判别电路(上)

和负端电平判别电路(下),分别与正端参考电平vrp和负端参考电平vrn进行比较,此时接收电路的逻辑电平的判别阈值vt=vrp-vrn。如果输入信号vin大于vrp,由于vrp大于vrn,则正端电平判别电路的电平判别输出口dinp和负端电平判别电路的电平判别输出口dinn的输出均为高电平;如果输入信号vin小于vrn,由于vrp大于vrn,则正端电平判别电路的电平判别输出口dinp和负端电平判别电路的电平判别输出口dinn的输出均为低电平。如果电源电压vdd因为干扰而产生一定幅度的尖峰抖动,由于正端参考电平vrp和负端参考电平vrn为内部基准电压,其波动会被参考电压产生电路共模抑制,仅产生很小的波动,此时正端电平判别电路的电平判别输出口dinp和负端电平判别电路的电平判别输出口dinn的输出仅会产生非常微小的尖峰误差。由于逻辑电平的判别阈值vt=vrp-vrn具有非常高的共模抑制比,判别阈值vt不受电源共模干扰影响,因此逻辑信号dinp和dinn经过rs触发器电路滤波,便可以得到不受共模干扰的输出数据dinh。各信号的波形关系如图4所示。

7.虽然采用上述差分比较判别技术可以对共模干扰引起的噪声进行有效抑制,但是采用了两个判别电路,器件电路增多了,功耗也相应增大。

技术实现要素:

8.本发明的目的是克服现有技术中存在的不足,针对输入信号接收电路中判别电路的抗干扰噪声容限问题,提供一种判别电平自适应的高精度输入信号接收电路。

9.本发明提供的高精度输入信号接收电路包括偏置和滤波模块、判别电平自适应产生模块、比较器模块和输出整形模块;所述偏置和滤波模块的输入端连接已通过esd保护的输入信号,经过偏置和滤波模块滤波的输出信号vin1连接比较器模块的第一信号输入端,偏置和滤波模块还向比较器模块提供两个偏置电压vb1和vb3;比较器模块的输出信号vout1连接输出整形模块的输入端;输出整形模块的数据输出端vout为整体电路的数据输出端,输出整形模块同时还向判别电平自适应产生模块输出3路控制信号vc1、vc2、vc3,其中vc1和vc2互为反相信号,vc1和vc3互为反相信号;所述判别电平自适应产生模块根据控制信号vc1、vc2、vc3产生判别电平vr,连接到比较器模块的第二信号输入端,判别电平自适应产生模块还向偏置和滤波模块提供两个偏置电压vb4和vb2;判别电平vr由输出整形模块所反馈的控制信号vc1、vc2、vc3的电平决定,通过控制信号vc1、vc2、vc3反馈产生了随信号vin1波动的判别电平vr,在判别的过程中提高了电路的抗干扰噪声容限。

10.当信号vin1为高电平时,判别电平vr为较低电平,当信号vin1为低电平时,判别电平vr为较高电平。

11.具体的,所述偏置和滤波模块包括:pmos管m11、pmos管m12、pmos管m15、pmos管m16、pmos管m17、pmos管m19、nmos管m13、nmos管m14、nmos管m18、nmos管m120、nmos管m121、nmos管m122、电阻r11、电阻r12、电阻r13、电容c11和电容c12;其中,pmos管m11和pmos管m12的栅极相连,并连接nmos管m13的漏极和pmos管m11的漏极;nmos管m13的栅极连接偏置电压vb3输出节点,pmos管m12的漏极连接nmos管m14的漏极、nmos管m14栅极、nmos管m18的栅极和nmos管m120的栅极;nmos管m14的源极连接pnos管m15的源极,pnos管m15的栅极连接偏置电压vb2;pmos管m16和pmos管m17的栅极相连,并连接到pmos管m16的漏极和nmos管m18的漏极;pmos管m17的漏极和pmos管m19的源极相连,并作为偏置电压vb1输出节点;pmos管m19的栅极连接偏置电压vb2,nmos管m18的源极和pmos管m19的漏极连接,并经过电阻r11连接电

容c11一端;nmos管m120的源极连接nmos管m122的漏极,nmos管m121和nmos管m122的栅极相连,并连接到nmos管m121的漏极和偏置电压vb3输出节点,nmos管m121的漏极经过电阻r13连接偏置电压vb4;nmos管m120的漏极经过电阻r12连接电容c12一端;电容c12另一端和电容c11另一端相连并作为偏置和滤波模块的信号vin1的输出节点;输入信号vin通过esd保护电路连接到电容c11和电容c12的连接节点上;pmos管m11、pmos管m12、pmos管m16和pmos管m17的源极同时连接电源电压vdd;nmos管m13的源极、pmos管m15的漏极、nmos管m121和nmos管m122的源极同时连接到地电压gnd。

12.所述偏置和滤波模块中,电阻r11、电容c11、电阻r12、电容c12构成上下对称的滤波电路,使输入信号vin尖峰变小;pmos管m11和pmos管m12、nmos管m14和nmos管m18、pmos管m16和pmos管m17、nmos管m121和nmos管m122构成镜像电流源,向比较器模块提供一种正常偏置电压vb3和一种动态偏置电压vb1;每当信号vin1发生变化时,vb1信号会跳动,提供一个迅速变大的偏置电压,然后恢复稳定。

13.具体的,所述判别电平自适应产生模块包括:pmos管m21、pmos管m22、pmos管m24、nmos管m23、nmos管m25、电阻r21、电阻r22、电阻r23和电阻r24;其中,pmos管m21的栅极接复位信号vn,pmos管m21的源极接电源电压vdd,pmos管m21的漏极接电阻r21的上端,同时作为偏置电压vb4的输出节点;电阻r21下端接电阻r22上端,并连接pmos管m22的漏极和nmos管m23的源极;nmos管m23的栅极连接控制信号vc2;电阻r22下端连接电阻r23上端,并连接pmos管m24的漏极和nmos管m25的源极,pmos管m24的栅极连接控制信号vc3;pmos管m22的栅极和nmos管m25的栅极共同连接控制信号vc1;pmos管m22的源极、nmos管m23的漏极、pmos管m24的源极和nmos管m25漏极连接,并作为判别电平vr的输出节点;电阻r23下端连接电阻r24上端,同时作为偏置电压vb2的输出节点,电阻r24下端连接到地电压gnd。

14.具体的,所述比较器模块包括:pmos管m31、pmos管m32、pmos管m36、pmos管m37、nmos管m33、nmos管m34、nmos管m35、nmos管m38、nmos管m39、nmos管m310、nmos管m311、nmos管m312;其中,pmos管m31的源极、pmos管m32的源极、pmos管m36的源极和pmos管m37的源极同时连接电源电压vdd,pmos管m31和pmos管m32的栅极相连,并同时连接到pmos管m31的漏极、nmos管m33的漏极和nmos管m310的漏极,nmos管m310的栅极连接偏置电压vb3;nmos管m33的源极和nmos管m34的源极相连,并且连接到nmos管m312的漏极和nmos管m35的漏极,nmos管m33的栅极作为比较器模块第一信号输入端,连接偏置和滤波模块的输出信号vin1;nmos管m34的栅极作为比较器模块第二信号输入端,连接判别电平自适应产生模块输出的判别电平vr,nmos管m35的栅极连接偏置电压vb3;pmos管m36和pmos管m37的栅极相连,同时连接nmos管m34的漏极和pmos管m36的漏极;nmos管m38和nmos管m39的栅极相连,同时连接nmos管m38的漏极和pmos管m32的漏极;pmos管m37的漏极和nmos管m39的漏极相连,并作为比较器模块的输出节点,输出信号vout1;nmos管m311的栅极、nmos管m311的漏极和nmos管m312的栅极相连,并连接偏置电压vb1;nmos管m310的源极、nmos管m35的源极、nmos管m38的源极、nmos管m39的源极、nmos管m311的源极和nmos管m312的源极同时连接到地电压gnd。

15.所述比较器模块中,pmos管m31、pmos管m32、pmos管m36、pmos管m37、nmos管m33、nmos管m34、nmos管m35、nmos管m38和nmos管m39构成一个两级推挽输出结构的运算放大器,以最大程度提供宽摆幅输出;nmos管m311和nmos管m312构成镜像电流源。

16.具体的,所述输出整形模块包括:pmos管m41、pmos管m43、pmos管m45、pmos管m47、

nmos管m42、nmos管m44、nmos管m46、nmos管m48;其中,pmos管m41的栅极和nmos管m42的栅极相连接,连接比较器模块的输出信号vout1;pmos管m41的漏极、nmos管m42的漏极、pmos管m43的栅极、pmos管m45的栅极、nmos管m44的栅极和nmos管m46的栅极相连,同时作为控制信号vc1的输出节点;pmos管m43的漏极、nmos管m44的漏极、pmos管m47的栅极相连,同时作为控制信号vc2的输出节点;pmos管m45的漏极、nmos管m46的漏极、nmos管m48的栅极相连,同时作为控制信号vc3的输出节点;pmos管m47的漏极和nmos管m48的漏极相连,输出信号vout;pmos管m41的源极、pmos管m43的源极、pmos管m45的源极、pmos管m47的源极同时连接电源电压vdd;nmos管m42的源极、nmos管m44的源极、nmos管m46的源极、nmos管m48的源极同时连接到地电压gnd。

17.所述输出整形模块中,pmos管m41和nmos管m42、pmos管m43和nmos管m44、pmos管m45和nmos管m46、pmos管m47和nmos管m48构成4对反相器。

18.本发明的优点是:所提供的高精度输入信号接收电路,采用判别电平自适应技术,判别电平值由输出控制信号反馈决定,提高了电路进行电平判别的抗干扰噪声容限;同时比较器模块采用动态偏置,瞬间电流增大,提高响应速度;本发明可以广泛应用于各类输入信号接收电路中。

附图说明

19.图1为现有技术中一种典型输入信号接收电路结构图。

20.图2为理想的输入信号判别电平波形图和一种典型的输入信号干扰波形图。

21.图3为现有技术中一种高精度输入信号接收电路结构图。

22.图4为图3中各信号波形图。

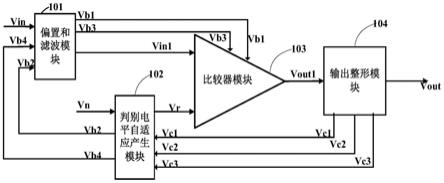

23.图5为本发明的判别电平自适应的高精度输入信号接收电路结构框图。

24.图6为本发明的输入信号判别电平的波形示意图。

25.图7为本发明偏置和滤波模块电路的实施例。

26.图8为本发明动态偏置电压的波形示意图。

27.图9为本发明判别电平自适应产生模块电路的实施例。

28.图10为本发明比较器模块电路的实施例。

29.图11(a)为图10中nmos管m312栅电流。

30.图11(b)为图10中nmos管m312漏电流。

31.图12为本发明输出整形模块电路的实施例。

具体实施方式

32.下面结合附图和实施例对本发明进行进一步详细的说明。

33.如图5所示,本发明的判别电平自适应的高精度输入信号接收电路结构上包括:偏置和滤波模块101、判别电平自适应产生模块102、比较器模块103和输出整形模块104。偏置和滤波模块101的输入端接的是已通过esd保护的输入信号,偏置和滤波模块101的输出信号vin1连接比较器模块103的第一信号输入端;判别电平自适应产生模块102根据输出整形模块104提供的三个控制信号vc1、vc2、vc3产生了判别电平vr,判别电平vr连接到比较器模块103的第二信号输入端,判别电平自适应产生模块102还向偏置和滤波模块101提供偏置

电压vb4和vb2;偏置和滤波模块101向比较器模块103提供两个偏置电压vb1和vb3;比较器模块103的输出信号vout1连接输出整形模块104的输入端;除了产生三个反馈控制信号vc1、vc2、vc3,输出整形模块104的数据输出端vout作为整个输入信号接收电路的数据输出端口。

34.本发明为克服现有技术中尖峰干扰和噪声的影响,采用判别电平自适应技术,通过输出整形模块104输出控制信号vc1、vc2、vc3反馈产生了随vin1波动的判别电平vr,如图6所示,当输入信号vin1为高电平时,vr为较低电平,当输入信号vin1为低电平时,vr为较高电平,在判别的过程中有效提高了电路的抗干扰噪声容限。同时,在比较器模块103中采用动态偏置电压vb1,瞬间电流增大了,提高了响应速度。

35.如图7所示,右侧虚线框为本发明所述的偏置和滤波模块101的一种实现方式。该电路包括pmos管m11、pmos管m12、pmos管m15、pmos管m16、pmos管m17、pmos管m19、nmos管m13、nmos管m14、nmos管m18、nmos管m120、nmos管m121、nmos管m122、电阻r11、电阻r12、电阻r13、电容c11和电容c12。

36.其中,输入信号vin通过esd保护电路(图7左侧虚线框中电路),连接到偏置和滤波模块101中电容c11和电容c12的连接节点上,并作为信号vin1的输出节点;pmos管m11、pmos管m12、pmos管m16和pmos管m17的源极同时连接电源电压vdd;pmos管m11和pmos管m12的栅极相连,并连接nmos管m13的漏极和pmos管m11的漏极;nmos管m13的栅极连接到偏置电压vb3输出节点,pmos管m12的漏极连接nmos管m14的漏极,并且连接到nmos管m14栅极、nmos管m18的栅极和nmos管m120的栅极;nmos管m14的源极连接pnos管m15的源极,pnos管m15的栅极连接偏置电压vb2;pmos管m16和pmos管m17的栅极相连,并连接到pmos管m16的漏极和nmos管m18的漏极;pmos管m17的漏极和pmos管m19的源极相连,并作为偏置电压vb1的输出节点;pmos管m19的栅极连接偏置电压vb2,nmos管m18的源极和pmos管m19的漏极连接,同时连接电阻r11的上端,电阻r11的下端连接电容c11的一端;电容c11的另一端连接电容c12的一端,该节点作为信号vin1的输出节点;电容c12的另一端连接电阻r12的上端,电阻r12的下端连接到nmos管m120的漏极;nmos管m120的源极连接nmos管m122的漏极,nmos管m121和nmos管m122的栅极相连,并连接到nmos管m121的漏极,同时连接到偏置电压vb3输出节点,nmos管m121的漏极连接电阻r13的一端,电阻r13的另一端连接偏置电压vb4;nmos管m13的源极、pmos管m15的漏极、nmos管m121和nmos管m122的源极同时连接到地电压gnd。

37.图7给出的实施例中,电阻r11、电容c11、电阻r12、电容c12构成上下对称的滤波电路,使输入信号vin尖峰变小;pmos管m11和pmos管m12、nmos管m14和nmos管m18、pmos管m16和pmos管m17、nmos管m121和nmos管m122构成镜像电流源,同时向比较器模块103提供了一种正常偏置电压vb3和一种动态偏置电压vb1。图8给出了信号vin1和vb1的波形示意图,图中横坐标为时间,单位微秒μs,纵坐标为电压,单位伏特(v),信号vin1和vb1的波形如图所示,当信号vin1变化(上升或下降)时,vb1信号会跳动,提供一个迅速变大的偏置电压,然后恢复稳定。

38.图9为本发明所述的判别电平自适应产生模块102的一种实现方式。该电路包括pmos管m21、pmos管m22、pmos管m24、nmos管m23、nmos管m25、电阻r21、电阻r22、电阻r23和电阻r24。

39.其中,pmos管m21的栅极接复位信号vn,pmos管m21的源极接电源电压vdd,pmos管

m21的漏极接电阻r21的上端,同时作为偏置电压vb4的输出节点;电阻r21的下端接电阻r22的上端,同时连接pmos管m22的漏极和nmos管m23的源极;nmos管m23的栅极连接控制信号vc2;电阻r22的下端连接电阻r23的上端,同时连接pmos管m24的漏极和nmos管m25的源极,pmos管m24的栅极连接控制信号vc3;pmos管m22的栅极和nmos管m25的栅极相连,连接控制信号vc1;pmos管m22的源极、nmos管m23的漏极、pmos管m24的源极和nmos管m25漏极连接,并作为判别电平vr的输出节点;电阻r23的下端连接电阻r24的上端,同时作为偏置电压vb2的输出节点,电阻r24的下端连接到地电压gnd。

40.图9给出的实施例中,当复位信号vn为低电平时,pmos管m21导通,电路正常工作。pmos管m22和nmos管m23构成传输门,连接输出整形模块104输出的控制信号vc1和vc2,vc1和vc2互为反相信号;pmos管m24和nmos管m25构成传输门,连接控制信号输出整形模块104输出的控制信号vc1和vc3,vc1和vc3互为反相信号;当vc1为高电平时,pmos管m24和nmos管m25构成的传输门导通,输出判别电平vr=vrl;当vc1为低电平时,pmos管m22和nmos管m23构成的传输门导通,输出判别电平vr=vrh。根据电阻分压,就可以得到上位参考电平vrh大小为vdd*(r23 r24)/(r21 r23 r24 r22),下位参考电平vrp大小为vdd*(r23 r24 r22)/(r21 r23 r24 r22)。通过设置电阻比例,即可精确设定上位参考电平vrh和下位参考电平vrl的大小,从而可以最大限度的提高电路进行电平判别的抗干扰噪声容限。

41.图10为本发明所述的比较器模块103的一种实现方式。该电路包括pmos管m31、pmos管m32、pmos管m36、pmos管m37、nmos管m33、nmos管m34、nmos管m35、nmos管m38、nmos管m39、nmos管m310、nmos管m311和nmos管m312。

42.其中,pmos管m31的源极、pmos管m32的源极、pmos管m36的源极和pmos管m37的源极同时连接电源电压vdd,pmos管m31和pmos管m32的栅极相连,并同时连接到pmos管m31的漏极、nmos管m33的漏极和nmos管m310的漏极,nmos管m310的栅极连接偏置电压vb3;nmos管m33的源极和nmos管m34的源极相连,并且连接到nmos管m312的漏极和nmos管m35的漏极,同时nmos管m33的栅极作为比较器模块103信号输入端,连接信号vin1;nmos管m34的栅极作为判别电平信号vr的输入端,nmos管m35的栅极连接偏置电压vb3;pmos管m36和pmos管m37的栅极相连,同时连接nmos管m34和pmos管m36的漏极;nmos管m38和nmos管m39的栅极相连,同时连接nmos管m38和pmos管m32的漏极;pmos管m37的漏极和nmos管m39的漏极相连,同时作为比较器模块103的输出节点vout1;nmos管m311的栅极和nmos管m312的栅极相连,并且连接nmos管m311的漏极,同时连接偏置信号vb1;nmos管m310的源极、nmos管m35的源极、nmos管m38的源极、nmos管m39的源极、nmos管m311和nmos管m312同时连接到地电压gnd。

43.图10给出的实施例中,pmos管m31、pmos管m32、pmos管m36、pmos管m37、nmos管m33、nmos管m34、nmos管m35、nmos管m38和nmos管m39构成一个两级推挽输出结构的运算放大器,以最大程度提供宽摆幅输出;nmos管m311和nmos管m312构成镜像电流源,偏置和滤波模块101提供动态偏置电压vb1。其中,nmos管m312的栅极电流和漏极电流波形如图11(a)和图11(b)所示,每当输入信号在翻转的瞬间,动态偏置电压vb1会首先出现一个快速跳变的过程,紧接着m312的栅极电流和漏极电流会出现一个迅速增大的峰值,瞬间提高了响应速度。当输入电压平稳时,迅速恢复正常工作状态。

44.图12为本发明所述的输出整形模块104的一种实现方式。该电路包括pmos管m41、pmos管m43、pmos管m45、pmos管m47、nmos管m42、nmos管m44、nmos管m46、nmos管m48。

45.其中,pmos管m41的栅极和nmos管m42的栅极相连接,同时连接到信号vout1;pmos管m41的漏极和nmos管m42的漏极相连接,并且连接pmos管m43的栅极、pmos管m45的栅极、nmos管m44的栅极和nmos管m46的栅极,同时作为控制信号vc1的输出节点;pmos管m43的漏极和nmos管m44的漏极连接,并连接pmos管m47的栅极,同时作为控制信号vc2的输出节点;pmos管m45的漏极和nmos管m46的漏极连接,并连接nmos管m48的栅极,同时作为控制信号vc3的输出节点;pmos管m47的漏极和nmos管m48的漏极,同时作为输出整形模块104的输出节点输出vout;pmos管m41的源极、pmos管m43的源极、pmos管m45的源极、pmos管m47的源极同时连接电源电压vdd;nmos管m42的源极、nmos管m44的源极、nmos管m46的源极、nmos管m48的源极同时连接到地电压gnd。

46.图12给出的实施例中,pmos管m41和nmos管m42、pmos管m43和nmos管m44、pmos管m45和nmos管m46、pmos管m47和nmos管m48构成4对反相器,整体构成了一个输出整形电路,同时在电路内部各节点可以抽出3路控制信号,其中vc1和vc2互为反相信号;vc1和vc3互为反相信号。

47.以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。