一种验证ldo芯片性能的夹具

技术领域

1.本实用新型涉及一种验证ldo芯片性能的夹具,用于验证ldo芯片满载时带载的能力。主要用于研发阶段验证ldo芯片能否正常工作的能力。

背景技术:

2.为了保证ldo芯片能正常工作,就需要验证满载状态下的工作能力,而一般ldo都是用于实际样机中使用,实际样机对ldo抽载电流的能力有限,并不能验证在ldo满载状态下的能力,使用该夹具就能验证ldo芯片满载时带载的能力。

技术实现要素:

3.本实用新型的目的在于针对上述现有技术的不足,提供一种验证ldo芯片性能的夹具,观察ldo芯片满载时带载的能力,成本低、操作方便。

4.为解决上述问题,本实用新型所采取的技术方案是:

5.一种验证ldo芯片性能的夹具,包括pcb板,所述pcb板上设有ldo芯片管脚座子、电阻r1、电阻r2、电阻r3、电容c1、电容c2和三极管q1,所述ldo芯片管脚座子有三个管脚,1脚并联连接电阻r1和电阻r2,电阻r2的另一端接地,电阻r1的另一端连接2脚,2脚连接电阻r3的一端,电阻r3的另一端连接三极管q1的集电极,电容c2的一端接地,另一端接三极管q1的集电极,三极管q1的发射极连接外部电子负载,三极管q1的基极接外部电路,3脚接电压输入源vin,电容c1的一端接地,另一端与3脚相连。

6.更进一步的技术方案是,所述电压输入源vin的电压为12v,所述电阻r1的阻值为120欧姆,所述电阻r2的阻值为200欧姆,所述电阻r3的阻值为0欧姆,所述电容c1的容值为0.1uf,所述电容c2的容值为0.1uf。

7.采用上述技术方案所产生的有益效果在于:实现起来容易,能够验证满载状态下的工作能力。成本低廉,极具性价比。

附图说明

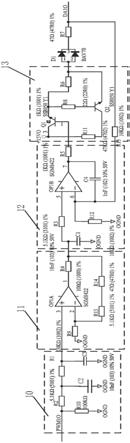

8.图1是本实用新型的示意图。

具体实施方式

9.下面结合附图和实施例对本实用新型的实施方式作进一步详细描述。以下实施例用于说明本实用新型,但不能用来限制本实用新型的范围。

10.在本实用新型的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

11.如图1所示,公开了一种验证ldo芯片性能的夹具,用于验证ldo芯片满载时带载的能力,包括pcb板,所述pcb板上设有ldo芯片管脚座子、电阻r1、电阻r2、电阻r3、电容c1、电容c2和三极管q1,所述ldo芯片管脚座子有三个管脚,1脚并联连接电阻r1和电阻r2,电阻r2的另一端接地,电阻r1的另一端连接2脚,2脚连接电阻r3的一端,电阻r3的另一端连接三极管q1的集电极,电容c2的一端接地,另一端接三极管q1的集电极,三极管q1的发射极连接外部电子负载,三极管q1的基极接外部电路,3脚接电压输入源vin,电容c1的一端接地,另一端与3脚相连。

12.其中,所述电压输入源vin的电压为12v,所述电阻r1的阻值为120欧姆,所述电阻r2的阻值为200欧姆,所述电阻r3的阻值为0欧姆,所述电容c1的容值为0.1uf,所述电容c2的容值为0.1uf。

13.工作原理:1、电压输入源vin用于给ldo芯片管脚座子供电管脚端使用,供电电压为12v。2、ldo芯片管脚座子有3个管脚,用于将待测试ldo芯片焊接在上面,当前使用zilltek公司的ztp1117芯片作为验证,管脚对应如下:1脚为ldo芯片adj管脚,为可调整管脚,有两个用处,首先作为参考电压点,提供1.25v的参考电压,其次作为电流调整,能提供35ua的电流输出,电阻r1和电阻r2为分压电阻,电阻r1为120欧姆,电阻r2为200欧姆,2脚为ldo芯片输出管脚,提供输出电压和电流,电阻r3为0欧姆电阻,此处用于测试使用,即需要进行电流测试时将0欧姆电阻取下换成导线串接进去,电容c2为输出电压滤波电容,容值0.1uf,3脚为ldo芯片电源输入管脚,通过电容c1串接到地,电容c1为0.1uf,作为电源输入滤波电容。3、三极管q1发射极通过导线连接到外部电子负载上,集电极和电阻r3相连接,基级由外部电路控制高电平或者低电平,此处三极管q1作为开关使用,当外部输入高电平时,三极管导通,此时电子负载会抽载电流,当外部输入低电平时,三极管断开,此时ldo输出和电子负载断开。

14.当使用该夹具进行验证时,先将待测试ldo芯片焊接在ldo芯片管脚座子上,当前使用zilltek公司的ztp1117芯片作为验证,首先给vin输入12v电压,此时三极管q1处于断开状态,ldo芯片处于空载状态,能正常输出3.3v电压,此时调节电子负载为1a,并将三极管q1打开,处于导通状态,此时电子负载会抽载1a电流,如此时用万用表测试ldo芯片输出电压为3.3v,说明工作正常,再次将电子负载调节至1.1a,并将三极管q1打开,处于导通状态,此时电子负载会抽载1.1a电流,如此时用万用表测试ldo芯片输出电压为3.3v,说明工作正常,最后将电子负载调节至1.2a,并将三极管q1打开,处于导通状态,此时电子负载会抽载1.2a电流,如此时用万用表测试ldo芯片输出电压为0v,说明工作不正常,记录此时电流值,即说明满载带载能力为1.1a。此方案实现简单,且节约成本,夹具成本只有几十块钱,也方便操作。

15.最后应说明的是:以上实施例仅用以说明本实用新型的技术方案,而非对其限制;尽管参照前述实施例对本实用新型进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本实用新型实施例技术方案的精神和范围。

技术特征:

1.一种验证ldo芯片性能的夹具,其特征在于:包括pcb板,所述pcb板上设有ldo芯片管脚座子、电阻r1、电阻r2、电阻r3、电容c1、电容c2和三极管q1,所述ldo芯片管脚座子有三个管脚,1脚并联连接电阻r1和电阻r2,电阻r2的另一端接地,电阻r1的另一端连接2脚,2脚连接电阻r3的一端,电阻r3的另一端连接三极管q1的集电极,电容c2的一端接地,另一端接三极管q1的集电极,三极管q1的发射极连接外部电子负载,三极管q1的基极接外部电路,3脚接电压输入源vin,电容c1的一端接地,另一端与3脚相连。2.根据权利要求1所述的一种验证ldo芯片性能的夹具,其特征在于:所述电压输入源vin的电压为12v,所述电阻r1的阻值为120欧姆,所述电阻r2的阻值为200欧姆,所述电阻r3的阻值为0欧姆,所述电容c1的容值为0.1uf,所述电容c2的容值为0.1uf。

技术总结

本实用新型公开了一种验证LDO芯片性能的夹具,包括PCB板,所述PCB板上设有LDO芯片管脚座子、电阻R1、电阻R2、电阻R3、电容C1、电容C2和三极管Q1,所述LDO芯片管脚座子有三个管脚,1脚并联连接电阻R1和电阻R2,电阻R2的另一端接地,电阻R1的另一端连接2脚,2脚连接电阻R3的一端,电阻R3的另一端连接三极管Q1的集电极,电容C2的一端接地,另一端接三极管Q1的集电极,三极管Q1的发射极连接外部电子负载,三极管Q1的基极接外部电路,3脚接电压输入源VIN,电容C1的一端接地,另一端与3脚相连。实现起来容易,能够验证满载状态下的工作能力。成本低廉,极具性价比。极具性价比。极具性价比。

技术研发人员:陈晨

受保护的技术使用者:太仓市同维电子有限公司

技术研发日:2021.10.27

技术公布日:2022/4/15

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。