1.本技术属于计算机调试技术领域,尤其涉及一种多余度多处理器断点同步停止方法。

背景技术:

2.为了提高控制系统的容错能力,控制计算机通常采用多余度冗余配置。为了提高控制系统的计算能力,单个控制计算机可采用多处理器配置。控制系统的多余度控制计算机的多处理器之间需要建立同步机制,以满足同步控制需要。

3.与此同时,多余度多处理器的同步调试能力也不可或缺,即一个处理器因调试断点停止运行,本余度控制计算机的其他处理器和其他余度控制计算机的处理器也要同步停止运行,以保存整个控制系统的调试现场。

4.由于不同处理器之间代码逻辑存在差异,存在无法通过设置相同的调试断点使所有处理器均停止运行的场景,因此需要一种多余度多处理器断点的同步停止技术。

技术实现要素:

5.针对上述技术问题,本技术提供了一种多余度多处理器断点同步停止方法,所述方法包括:

6.第一处理器的软件断点命中,发送停止信号,并进入待命状态;其中,所述软件断点是调试上位机设置的;

7.第二处理器接收所述停止信号,并处于待命状态;其中,所述停止信号用于使得所述处理器处于待命状态;所述第一计算机包括第一处理器和第二处理器。

8.优选地,所述方法还包括:

9.调试连接器接收所述停止信号,转发给第二计算机;

10.第二计算机接收所述停止信号,转发给第三处理器和第四处理器;其中,所述第二计算机包括第三处理器和第四处理器;

11.所述第三处理器和第四处理器接收所述停止信号,并处于待命状态;其中,所述第一计算机和所述第二计算机不同。

12.优选地,所述方法还包括:

13.调试连接器接收所述停止信号,转发给第三计算机;

14.第三计算机接收所述停止信号,转发给第五处理器和第六处理器;其中,所述第三计算机包括第五处理器和第六处理器;

15.所述第五处理器和第六处理器接收所述停止信号,并处于待命状态;其中,所述第一计算机和所述第三计算机不同。

16.优选地,所述调试连接器分别与所述第一计算机、所述第二计算机和所述第三计算机连接。

17.优选地,所述调试连接器还与所述调试上位机连接。

18.优选地,所述方法还包括:

19.调试上位机发送调试指令,所述调试连接器接收所述调试指令,并转发给所述第一处理器、第二处理器、第三处理器、第四处理器、第五处理器和第六处理器。

20.优选地,所述第一处理器与所述第二处理器连接;所述第三处理器与所述第四处理器连接;所述第五处理器与所述第六处理器连接。

21.优选地,所述调试上位机通过调试总线与所述调试连接器连接;所述停止信号的数据线连接在处理器的外部中断引脚。

22.本发明的有益效果:

23.本技术提供的一种多余度多处理器同步调试机制,在一个处理器因断点命中停止运行的同时,也可以触发本余度的其他处理器和其它余度的处理器同步停止运行。

附图说明

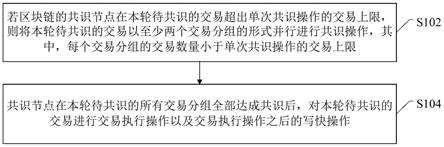

24.图1为本技术实施例提供的系统连接框图;

25.图2为本技术实施例提供的调试连接器硬线连接框图;

26.图3为本技术实施例提供的控制计算机连接框图。

具体实施方式

27.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

28.请参阅图1-3,本技术提供的技术解决方案:系统包含一台调试上位机,一个调试连接器和多余度冗余配置控制计算机(假设余度数为n)。调试上位机用来发送调试指令(如设置断点,读写变量等),调试连接器负责调试上位机与n个余度控制计算机之间的调试信号连接,每个余度的控制计算机包含多个处理器(假设处理器个数为m)。

29.2)外部连接关系:调试上位机与n余度控制计算机的m个处理器之间通过调试总线连接,调试上位机与调试连接器通过1条调试总线连接,由调试连接器负责将调试数据中转至n个余度控制计算机的m个处理器。调试连接器和控制计算机之间采用硬线连接,每个余度的控制计算机有一个sbo_out_from_x(sbo:stop by other)输出信号和一个sbo_in_to_x输入信号与调试连接器连接。

30.3)调试连接器内部连接关系:来自n-1个余度控制计算机的sbo_out_from_*信号(不包含sbo_out_from_x信号),经过或逻辑综合后,生成sbo_out_to_x信号。

31.4)控制计算机内部连接关系:余度x控制计算机的每个处理器均有3个信号:sbo_out输出信号,sbo_in输入信号和sbo_in_local输入信号。m个处理器的sbo_out信号经过或逻辑综合后,输出为sbo_out_from_x信号。来自调试连接器的sbo_in_to_x输入信号,分别连接至m个处理器的sbo_in输入信号。任意一个处理器的sbo_out输出信号,连接至其他m-1个处理器的sbo_in_loacal输入信号。

32.6)信号流描述:通过调试上位机,设置余度x控制计算机任一处理器中软件的调试断点,软件调试断点命中,进入异常处理程序,立即发出sbo信号后,轮循等待来自调试上位

机的调试指令。在本控制计算机内部,通过sbo_out信号,输出至其他m-1个处理器的sbo_in_local。在本控制计算机外部,通过sbo_out_from_x信号送至调试连接器,在调试连接器内部,经过或逻辑综合后,送至其他余度控制计算机的sbo_in_to_*(*代表除余度x外的其他余度)。其他余度控制计算机接收到sbo_in_to_*信号后,分别送至本余度控制计算机m个处理器的sbo_in信号。

33.7)处理器的sbo_in输入信号和sbo_in_local输入信号,经过或逻辑综合后,与本处理器的外部中断引脚相连,信号到来会触发外部中断,软件进入中断处理程序,轮循等待来自调试上位机的调试指令。

34.本发明通过一个stop by other软硬件综合设计,任一处理器停止运行,发出sbo信号,可触发整个控制系统的其他所有处理器停止运行,从而完整保存了整个控制系统的同步运行现场快照,解决了多余度多处理器的同步调试问题。

35.需要说明的是,第一计算机是余度a计算机,第二计算机是余度b计算机,第三计算机是余度c计算机。第一处理器是余度a计算机的cpu1,第二处理器是余度a计算机的cpu2,第三处理器是余度b计算机的cpu1,第四处理器是余度b计算机的cpu2,第五处理器是余度c计算机的cpu1,第六处理器是余度c计算机的cpu2。

36.以图1-图3所示的示例,详细说明具体的实施方式。

37.1)控制系统的控制计算机采用三余度控制,包含余度a、余度b和余度c。

38.2)每个余度的控制计算机采用双处理器配置,包含cpu1和cpu2。

39.3)调试上位机通过调试总线,设置余度a控制计算机cpu1中软件的调试断点,调试断点命中,软件进入异常处理程序,立即对外发出sbo信号,之后进入轮循等待状态,等待调试上位机的调试指令。

40.4)余度a控制计算机cpu2停止运行:sbo信号发送至余度a控制计算机cpu2的sbo_in_local信号,触发外部中断,软件进行中断处理程序,进入轮循等待状态,等待调试上位机的调试指令。

41.5)余度b控制计算机cpu1/2停止运行:sbo信号在余度a控制计算机内部经过或逻辑处理后,综合为sbo_out_from_a信号,送入调试连接器。在调试连接器内部,sbo_out_from_a经过或逻辑后,综合为sbo_in_to_b信号送入余度b控制计算机。sbo_in_to_b信号在余度b控制计算机,一分为二,分别进入cpu1和cpu2的sbo_in输入信号。sbo_in信号会触发cpu1和cpu2的外部中断,软件进入中断处理程序,进入轮循等待状态,等待调试上位机的调试指令。

42.6)余度c控制计算机cpu1/2停止运行:sbo信号在余度a控制计算机内部经过或逻辑处理后,综合为sbo_out_from_a信号,送入调试连接器。在调试连接器内部,sbo_out_from_a经过或逻辑后,综合为sbo_in_to_c信号送入余度c控制计算机。sbo_in_to_c信号在余度c控制计算机,一分为二,分别进入cpu1和cpu2的sbo_in输入信号。sbo_in信号会触发cpu1和cpu2的外部中断,软件进入中断处理程序,进入轮循等待状态,等待调试上位机的调试指令。

43.7)至此,余度a控制计算机cpu1软件断点停止运行,已同步停止余度a控制计算机的cpu2,余度b/c控制计算机的cpu1/2中软件都停止运行。整个控制系统的所有处理器软件,均进入轮循等待状态,等待来自调试上位机的调试指令。整个控制系统的软件同步运行

现场得以保存。

44.8)调试上位机可以读写控制系统任一处理器中软件的变量,开展需要的调试工作。

45.以上所述,仅为本发明的具体实施例,对本发明进行详细描述,未详尽部分为常规技术。但本发明的保护范围不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。本发明的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。