1.本发明实施例涉及锁存电路技术,尤其涉及一种故障信号锁存电路。

背景技术:

2.故障硬件锁存电路是在系统出现故障时,对故障信号进行检测并保持的电路,其可以避免因输入的低电平故障信号的消失而导致故障无法被检测到、或故障信号在高低电平之间频繁跳变使得系统的故障状态频繁切换而导致系统进入紊乱的状态。

3.现有技术中,故障锁存电路会利用与门和或门完成故障锁存的方法,具备故障清除功能,但由于采用两种不同的门电路,实际使用中需要至少两个芯片完成功能,增加了系统的复杂度与成本。

技术实现要素:

4.本发明提供了一种故障信号锁存电路,以实现结构简单、成本低廉、稳定可靠、易于实现的设计。

5.本发明实施例提供了一种故障信号锁存电路,该故障信号锁存电路包括:故障信号端、复位信号端、锁存故障信号端、逻辑元件、反馈电阻及二极管;

6.所述故障信号端,用于接收故障信号;所述复位信号端,用于接收复位信号;所述锁存故障信号端,用于输出锁存故障信号;

7.所述故障信号端与所述逻辑元件的第一输入端电连接;所述复位信号端与所述二极管的第一端电连接;所述二极管的第二端与所述逻辑元件的第二输入端电连接;所述逻辑元件的输出端与所述锁存故障信号端电连接;

8.所述逻辑元件的输出端与所述反馈电阻的第一端电连接,所述反馈电阻的第二端与所述二极管的第二端电连接。

9.可选的,所述逻辑元件包括与门模块;

10.所述与门模块的第一输入端与所述故障信号端电连接;所述与门模块的第二输入端与所述反馈电阻的第二端电连接;所述与门模块的输出端与所述锁存故障信号端电连接。

11.可选的,所述二极管包括第一单向二极管;

12.所述第一单向二极管的输出端与所述与门模块的第二输入端电连接;所述第一单向二极管的输入端与所述复位信号端电连接。

13.可选的,所述逻辑元件包括或门模块;

14.所述或门模块的第一输入端与所述故障信号端电连接;所述或门模块的第二输入端与所述反馈电阻的第二端电连接;所述或门模块的输出端与所述锁存故障信号端电连接。

15.可选的,所述二极管包括第二单向二极管;

16.所述第二单向二极管的输出端与所述或门模块的第二输入端电连接;所述第二单

向二极管的输入端与所述复位信号端电连接。

17.可选的,所述反馈电阻的电阻r取值范围满足:103ω≤r≤105ω。

18.可选的,所述逻辑元件还包括至少一个第三输入端;

19.至少一个所述第三输入端均与所述故障信号端电连接。

20.可选的,所述逻辑元件包括第一逻辑单元、第二逻辑单元、第三逻辑单元...及第n逻辑单元;

21.所述第一逻辑单元的第一输入端与所述复位信号端电连接;所述第一逻辑单元的第二输入端为所述逻辑元件的第一输入端;

22.所述第一逻辑单元的输出端与所述第二逻辑单元的第二输入端电连接,所述第二逻辑单元的第一输入端为所述逻辑元件的第二输入端;

23.所述第二逻辑单元的输出端与所述第三逻辑单元的第二输入端电连接,所述第三逻辑单元的第一输入端与所述逻辑元件的第三输入端;

24.…

25.所述第三逻辑单元的输出端与所述第n锁存单元的第二输入端电连接,所述第n逻辑单元的第一输入端为所述逻辑元件的第n输入端;

26.其中,n大于等于3。

27.本发明实施例,通过故障信号端与逻辑元件的第一输入端电连接;复位信号端与二极管的第一端电连接;二极管的第二端与逻辑元件的第二输入端电连接;逻辑元件的输出端与锁存故障信号端电连接;逻辑元件的输出端与反馈电阻的第一端电连接,反馈电阻的第二端与二极管的第二端电连接,实现了对故障信号进行检测并保持的效果,同时实现了结构简单、成本低廉、稳定可靠的锁存电路的设计。

附图说明

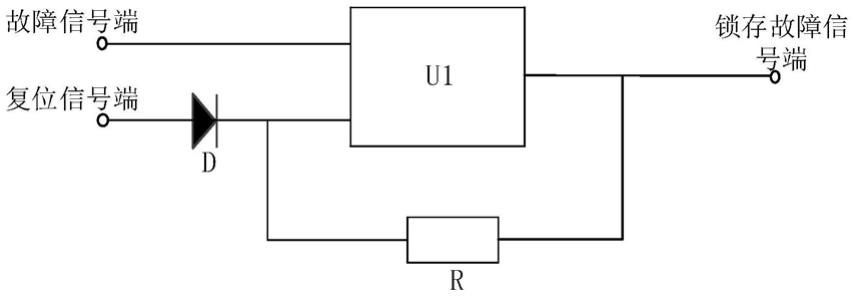

28.图1是本发明实施例提供的一种故障信号锁存电路的结构示意图;

29.图2是本发明实施例提供的另一种故障信号锁存电路的结构示意图;

30.图3是本发明实施例提供的另一种故障信号锁存电路结构示意图;

31.图4是本发明实施例提供的又一种故障信号锁存电路的结构示意图;

32.图5是本发明实施例提供的又一种故障信号锁存电路的结构示意图。

具体实施方式

33.下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

34.图1是本发明实施例提供的一种故障信号锁存电路的结构示意图,如图1所示,该故障信号锁存电路包括故障信号端、复位信号端、锁存故障信号端、逻辑元件u1、反馈电阻r及二极管d;故障信号端,用于接收故障信号;复位信号端,用于接收复位信号;锁存故障信号端,用于输出锁存故障信号;故障信号端与逻辑元件u1的第一输入端电连接;复位信号端与二极管d的第一端电连接;二极管d的第二端与逻辑元件u1的第二输入端电连接;逻辑元件u1的输出端与锁存故障信号端电连接;逻辑元件u1的输出端与反馈电阻r的第一端电连

接,反馈电阻r的第二端与二极管d的第二端电连接。

35.其中,实际中故障信号端可以接收来自系统输出的故障信号;单片机可以用来检测锁存故障信号端输出的锁存故障信号,并通过复位信号端提供复位信号;逻辑元件u1可以包括与门或者或门。本技术方案通过逻辑元件u1和反馈电阻r共同完成对故障信号锁存的功能,且二极管d提供复位信号的通道,通过二极管d、逻辑元件u1以及反馈电阻r完成对故障信号的消除的功能;如此实现了故障信号锁存电路对高电平有效、低电平有效的故障信号的保持和检测;同时实现了锁存电路结构简单、成本低廉、稳定可靠、易于实现的设计。

36.可选的,图2是本发明实施例提供的另一种故障信号锁存电路的结构示意图,如图2所示,逻辑元件u1包括与门模块01;与门模块01的第一输入端与故障信号端电连接;与门模块01的第二输入端与反馈电阻r的第二端电连接;与门模块01的输出端与锁存故障信号端电连接。

37.可选的,如图2所示,二极管d包括第一单向二极管d1;第一单向二极管d1的输出端与与门模块01的第二输入端电连接;第一单向二极管d1的输入端与复位信号端电连接。

38.其中,当系统上电完成初始化操作后,由于初始化过程中信号的不稳定,故障信号端为低电平信号,复位信号端为低电平信号,与门模块01的输出端输出锁存故障信号为低电平,系统处于故障状态;此时,即使故障信号端由低电平信号跳变到高电平信号,由于与门模块01输出端的低电平信号会通过反馈电阻r反馈到与门模块01的第二输入端,与门模块01的第二输入端为低电平信号,则与门模块01的输出端会锁存低电平的故障信号;

39.为了消除系统的故障状态,故障信号端输出无故障的高电平状态,单片机通过复位信号端输出高电平信号,第一单向二极管d1导通,则与门模块01输出端输出高电平信号,与门模块01的输出端由低电平的故障信号变化为高电平信号,锁存电路完成复位的功能;

40.正常工作下,复位信号端输出低电平信号,第一二极管d1反向截止,与门模块01的输出端的高电平信号通过反馈电阻r反馈到与门模块01的第二输入端,维持第二输入端的高电平状态;

41.当系统发生故障时,故障信号端由高电平信号跳变到低电平信号,与门模块01输出端由高电平信号变为低电平信号,与门模块01输出端的低电平信号通过反馈电阻r反馈到与门模块01的第二输入端上,使得第二输入端为低电平信号,此时即使故障信号由低电平信号跳变到高电平信号,与门模块01的输出端输出锁存故障信号均为低电平,达到对低电平有效的故障信号的锁存。

42.可选的,反馈电阻r的电阻取值范围满足:103ω≤r≤105ω。

43.其中,若反馈电阻r选择阻值太小,通过反馈电阻r的电流较大,容易超过单片机驱动能力,从而将反馈电阻r与二极管d输出端相连的一端的电压拉低,若反馈电阻r选择阻值太大,会导致逻辑元件u1输出端的信号无法反馈至逻辑元件u1的第二输入端,起不到反馈信号的能力;如此选择反馈电阻r取值范围在:103ω≤r≤105ω之内,可避免了锁存电路无法复位的问题,也保证反馈电阻一定的反馈信号能力。

44.可选的,图3是本发明实施例提供的另一种故障信号锁存电路结构示意图,如图3所示,逻辑元件u1包括或门模块02;或门模块02的第一输入端与故障信号端电连接;或门模块02的第二输入端与反馈电阻r的第二端电连接;或门模块02的输出端与锁存故障信号端电连接。

45.可选的,如图3所示,二极管d包括第二单向二极管d2;第二单向二极管d2的输出端与或门模块02的第二输入端电连接;第二单向二极管d2的输入端与复位信号端电连接。

46.其中,当系统上电完成初始化操作后,由于初始化过程中信号的不稳定,故障信号端为低电平信号,复位信号端为低电平信号,或门模块02的输出端输出锁存故障信号为低电平信号;

47.当故障信号端由低电平跳变到高电平信号,系统处于故障状态,或门模块02输出端的电平由低电平跳变到高电平,与门模块02输出端的高电平信号会通过反馈电阻r反馈到或门模块02的第二输入端,或门模块02的第二输入端为高电平信号,即使故障信号端由高电平变为低电平信号,或门模块02的输出端会锁存在高电平的故障信号,达到对高电平有效的故障信号的锁存。

48.为了消除系统的故障状态,故障信号端输出无故障的低电平状态,单片机通过复位信号端输出低电平信号,第二二极管d2导通,则或门模块02输出端输出低电平信号,或门模块02的输出端由高电平的故障信号变化为低电平信号,锁存电路完成复位的功能;

49.正常工作下,复位信号端输出高电平信号,第二二极管d2反向截止,或门模块02的输出端的低电平信号通过反馈电阻r反馈到或门模块02的第二输入端,维持第二输入端的低电平状态;

50.当系统再次发生故障时,故障信号端由低电平信号跳变到高电平信号,或门模块02输出端由低电平变为高电平,或门模块02输出端的高电平通过反馈电阻r反馈到或门模块02的第二输入端上,使得第二输入端为高电平信号,此时即使故障信号由高电平跳变到低电平信号,或门模块02的输出端输出锁存故障信号均为高电平信号,达到对高电平有效的故障信号的锁存。

51.可选的,图4是本发明实施例提供的又一种故障信号锁存电路的结构示意图,如图4所示,逻辑元件u1还包括至少一个第三输入端;至少一个第三输入端均与故障信号端电连接。

52.其中,逻辑元件u1中还包括多个第三输入端,各第三输入端均与故障信号端电连接,故障信号端输出不同的故障信号,如此通过逻辑元件u1和反馈电阻r可实现对多个故障信号的锁存;以及通过逻辑元件u1、反馈电阻r和二极管d实现对多个故障信号的消除。

53.可选的,图5是本发明实施例提供的又一种故障信号锁存电路的结构示意图,如图5所示,逻辑元件u1包括第一逻辑单元u11、第二逻辑单元u12、第三逻辑单元u13...及第n逻辑单元u1n;

54.第一逻辑单元u11的第一输入端与复位信号端电连接;第一逻辑单元u11的第二输入端为逻辑元件u1的第一输入端;

55.第一逻辑单元u11的输出端与第二逻辑单元u12的第二输入端电连接,第二逻辑单元u12的第一输入端为逻辑元件u1的第二输入端;

56.第二逻辑单元u12的输出端与第三逻辑单元u13的第二输入端电连接,第三逻辑单元u13的第一输入端与逻辑元件u1的第三输入端;

57.…

58.第三逻辑单元u13的输出端与第n锁存单元u1n的第二输入端电连接,第n逻辑单元u1n的第一输入端为逻辑元件u1的第n输入端;

59.其中,n大于等于3。

60.其中,通过多个逻辑单元级联的方式,实现对多个故障信号的输入,从而实现对多个故障信号的锁存功能以及多个故障信号的故障消除功能;可以理解的是,逻辑元件u1内部各逻辑单元还可以通过其他级联的方式实现对多个故障信号的输入,本实施例对多个逻辑单元级联的方式不作具体的限定。

61.注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。