高速多模cmos时钟分频器

技术领域

1.提供了一种对输入信号的频率进行分频的电子电路。

背景技术:

2.时钟分频器用于将输入信号的频率转换为输出信号的降低频率。输入信号的频率与输出信号的频率之比为分频因子。时钟分频器广泛用于锁相环。

3.在锁相环中,生成的时钟需要被分频以与参考时钟进行比较。众所周知,将整个时钟分频器分为几个级,其中第一级具有最高速度,因此设计起来最困难。

4.时钟分频器的瓶颈是在器件老化或退化的情况下,考虑到工艺电压和温度(pvt)变化,它们在提供稳定分频比时可操作的最大速度。

5.图1是根据现有技术的3分频cmos逻辑电路的示例100的简化示意图。该电路由串联连接的四个门控反相器110、120、130、140组成。第二门控反相器120和第四门控反相器140的输出连接到(与非门)nand门150的输入152、154,并且其输出156连接到第一门控反相器110的输入。每个门控反相器都具有互补的控制信号输入。作为一个示例,第一门控反相器110包括第一互补输入112和第二互补输入114。这些输入中的每一个都由非对称时钟驱动器160驱动。非对称时钟驱动器160提供高于50%的占空比时钟,使得门控反相器内的每个pmos晶体管和nmos晶体管在超过50%的时钟周期内导通。这是为了提高最大操作速度。在任何情况下,最大速度都受到通过nand门150的传播延迟的限制。为了加速nand门150,可以通过增加其大小来增加其驱动强度,但这会增加节点div3_stage4 170尤其是div3_stage2172上的负载,这反过来又会成为速度瓶颈。如果必须使用单个分频器电路来提供多个分频比,由于需要更多的组合逻辑和门控反相器的该电路的复杂性,则可实现的最大速度将进一步降低。

技术实现要素:

6.提供了一种电子电路。

7.电子电路可以是高速cmos逻辑电路或者可以适合于此。

8.电子电路可以是时钟分频器。

9.电子电路可以包括环形振荡器。环形振荡器可以包括多个门控反相器。门控反相器中的至少一个可以被配置为在两个互补输入处接收振荡信号和控制信号。电子电路可以被配置为被部分地门控,使得分频比可以是可选择的。

10.环形振荡器可以包括至少三个门控反相器。至少三个门控反相器可以串联连接布置。每个门控反相器的输出可以被应用到环形振荡器的后续门控反相器的输入。

11.控制信号可以包括第一信号和第二信号。第一信号和第二信号可以彼此相反。

12.控制信号的占空比可以大于0.5。

13.至少一个门控反相器可以被部分地门控,使得其根据输入信号的逻辑状态输出逻辑高或逻辑低。输出信号可以通过在pmos或nmos上应用部分门控而是可选择的。

14.电子电路可以包括互连。

15.门控反相器可以具有总线保持器。

16.电子电路可以是三模时钟分频器。

17.至少1比3、4和5的分频比可以是可选择的。

18.在另一方面中,提供了一种时钟分频器。时钟分频器可以包括随后彼此耦合的多个门控反相器。门控反相器中的至少一个可以被配置为接收振荡信号和控制信号。时钟分频器可以被配置为使得分频比是基于控制信号可选择的。

19.根据又一方面,提供了一种电子电路。电子电路可以包括环形振荡器。环形振荡器可以包括多个门控反相器。门控反相器中的至少一个可以被配置为在附加输入处接收振荡信号和至少一个辅助信号。电子电路可以包括多个互连。电子电路可以提供基于至少一个辅助信号可选择的分频比。

附图说明

20.本技术的其他方面和特性将从以下参照附图对优选示例的描述中得出,其中:

21.图1是根据现有技术用作3分频时钟分频器的cmos逻辑电路的示例的简化示意图;

22.图2是用作多模时钟分频器的时钟分频器的示例的简化示意图;

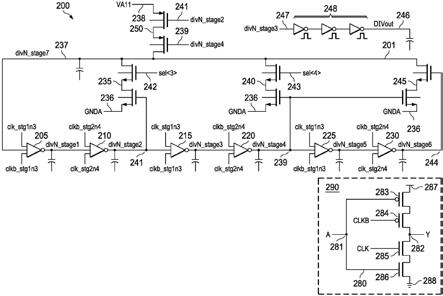

23.图3是根据一个示例的时钟分频器的过程信号的简化示意图;

24.图4是时钟分频器的另一示例的简化示意图,该时钟分频器是改进的多模时钟分频器;

25.图5是门控反相器的简化示意图;以及

26.图6是根据一个示例的时钟分频器的过程信号的简化示意图。

具体实施方式

27.图2是被配置为时钟分频器200的电子电路的简化示意图示例。时钟分频器200包括第一至第六门控反相器205、210、215、220、225、230。第一至第六门控反相器205、210、215、220、225、230以串联连接布置并且是环形振荡器201的部分。时钟分频器200还具有一定的组合逻辑以获得所需的分频因子3、4和5。

28.在虚线框290内部更详细地示出了门控反相器280的示例。门控反相器280包括用于控制其操作状态的附加输入。

29.门控反相器280包括两个p-金属氧化物半导体(pmos)晶体管283、284和两个n-金属氧化物半导体(nmos)晶体管285、286。第一pmos 283的漏极耦合到第二pmos 284的源极。第一nmos 285的源极耦合到第二nmos 286的漏极。在pmos 283、284对和nmos 285、286对之间,布置了提供输出信号y的节点282。这意味着,在第二pmos 284的漏极和第一nmos 285的漏极之间的节点282处提供输出信号y。

30.输入信号a耦合到门控反相器280的第一pmos 283和第二nmos 286的栅极。控制信号包括第一信号clk和第二信号clkb。第一信号clk耦合到第一nmos 285的栅极。第二信号clkb耦合到第二pmos 284的栅极。第二信号clkb与第一信号clk相反。这意味着,如果clk为逻辑“高”,则clkb为逻辑“低”。

31.如果第一信号clk为低并且第二信号clkb为高,则供应有第一信号clk和第二信号

clkb的门控反相器280可以处于高阻抗配置中。同样,如果第一信号clk为高并且第二信号clkb为低,则门控反相器280可以处于反相器配置中。在反相器配置中,如果输入信号a为低,则门控反相器280可以输出高,反之亦然。如果clk保持低,则门控反相器280可以输出始终为高。在这种配置中,预计clkb改换(toggle),并且输入信号a改换或保持低。要求clkb和输入信号a二者在特定时间一起变低。如果clkb保持高,则门控反相器280可以输出始终为低。在这种配置中,预计clk改换,并且输入信号a改换或保持高。要求clkb和输入信号a二者在特定时间一起变高。

32.电源电压287耦合到第一pmos 283的源极。第二nmos 286的源极耦合到地288。时钟分频器200的第二、第四和第六门控反相器210、220、230类似于门控反相器280。除了与门控反相器280相比第一信号clk和第二信号clkb交换之外,第一、第三和第五门控反相器205、215、225类似于门控反相器280。

33.时钟分频器200包括多个互连235、240、245、250。第一互连235布置在地236和节点divn_stage7 237之间。第二互连240布置在地236和节点divn_stage7 237之间。第三互连245布置在地236和节点divn_stage7 237之间。第四互连250布置在电源电压va11 238和节点divn_stage7 237之间。

34.互连235、240、245、250都包括两个pmos的串联连接。第二至第四互连240、245、250的一个pmos的栅极耦合到节点divn_stage4 239,并且因此在这些互连之间共享。此外,第一互连235的栅极耦合到节点divn_stage2241。节点divn_stage2 241也耦合到第四互连250的第二栅极。

35.选择信号sel《3》242耦合到第一互连235的第二栅极。选择信号sel《4》243耦合到第二互连240的第二栅极。第三互连245的第二栅极耦合到节点divn_stage6 244。

36.在已经应用额外的反相器248用于稳定、缓冲和/或运行时间调整之后,时钟分频器200的divout 246被提供在节点divn_stage3 247处。

37.时钟分频器200的功能原理依赖于互连235、240、245、250。第一互连235创建一个周期(1t)的divout高时间(意味着在状态逻辑“高”中的divout)。第二互连240创建两个周期(2t)divout高时间。第三互连245创建三个周期(3t)的divout高时间。第四互连250创建两个周期(2t)的divout低时间(意味着在状态逻辑“低”中的divout)。

38.选择信号sel《3》242和sel《4》243可以用于在divout 246处在不同分频比之间切换。由于第一到第三互连235、240、245共享相同的pmos(上拉),因此负载降低,使得divout 246低时间对于所有分频比都相等,即divout 246低时间对于选择信号sel《3》242和sel《4》243的所有配置为2t。这导致时钟分频器200提供不同的分频比。时钟分频器200是三模的,使得通过选择信号242、243提供三个不同的分频比/3、/4和/5。控制信号因此可以用于有效地修改时钟分频器200的操作状态,使得分频比可以不同。时钟分频器200适用于大量使用情况。时钟分频器200可以在宽范围的输入时钟频率下操作。几mhz到ghz。时钟分频器200的最大操作速度可以非常高,接近10ghz。

39.根据另一方面,门控反相器205、210、215、220、225、230的占空比可能会失真。这意味着可以应用大于0.5的占空比,使得提供更多的“导通”时间。这可以通过利用具有不对称上拉(pmos)和下拉(nmos)强度的附加反相器缓冲时钟信号,即第一信号clk和第二信号clkb来实现。这导致时钟分频器200的最大速度(采样时间、时钟分频器200可操作的最大频

率)的进一步增加。

40.图3示出了时钟分频器200的过程信号300的示意图。在x轴上示出了以ns为单位的时间。y轴示出了在“高”和“低”之间切换的相应信号的幅度。

41.clk_stgln3 312和clkb_stgln3 314是用于门控时钟分频器200的门控反相器205、210、215、220、225、230的时钟信号和反相时钟信号。图3中的时钟信号频率为10ghz。

42.divn_stagel至divn_stage7 320是如前所述的时钟分频器200的门控反相器205、210、215、220、225、230的输出信号。

43.sel《4》322是用于在时钟分频器200的不同分频比div-3、div-4和div-5之间进行选择的选择信号之一。因此,门控反相器的输出信号,即信号divn_stage1到divn_stage7 320对应于不同时间点处的sel《4》322的切换而在div-3、div-4和div-5之间变化。divout 324示出了新鲜硅模拟的分频输出,并且divout 326示出了老化10年后的分频输出。它们基于sel《3》,尤其是sel《4》322的状态提供逻辑“高”和逻辑“低”之间的不同比率,使得时钟分频器200提供不同的分频比。从时钟分频器200的divout 324和“老化”的divout 326的比较可以明显看出,即使在老化10年后,时钟分频器200也为/3的分频比提供稳定的输出信号。这意味着对于/3的比率,输出信号divout326与“新鲜”divout 324基本相同(在可忽略的容差范围内)。然而,对于剩余的分频比/4和/5,divout 326与“新鲜”divout 324不同。这意味着考虑到这种器件的所有(物理上有意义的)工艺电压和温度(pvt)变化,时钟分频器200还不能够完全在10年的模拟寿命内在预定义的容差范围内(根据工业需要)在10ghz输入时钟频率下提供恒定的分频比。

44.图4示出了被配置为时钟分频器400的改进的高速cmos逻辑电路。即使在非常高的输入时钟速率下,该高速分频器400也可以将输入时钟信号分频到1/3、1/4和1/5。因此,它是一种高速多模分频器。

45.时钟分频器400包括第一至第七门控反相器410、415、420、425、430、435、440。时钟分频器400的门控反相器410、415、420、425、430、435、440与参照时钟分频器200详细解释的类型相似。时钟分频器400包括在节点divn_stage2 416和节点divn_stage2b 470之间以反向布置的附加反相器460,节点divn_stage2b 470本身耦合到第一门控反相器410的输入。

46.时钟分频器400还包括nand2 445,其中nand2 445的第一输入耦合到节点divn_stage4 426。nand2 445的第二输入耦合到控制信号clkb_stgln3427。nand2 445的输出耦合到第一门控反相器410的pmos控制输入。

47.此外,时钟分频器400包括nand3 450,其中第一输入耦合到节点divn_stage5 431。nand3 450的第二输入耦合到节点divn_stage7 441,节点divn_stage7 441本身耦合到第七门控反相器440的输出。nand3 450的第三输入耦合到控制信号clk_stg2n4 442。nand3 450的输出耦合到第二门控反相器415的pmos控制输入。

48.基于时钟信号clk和反相时钟信号clkb以及选择信号sel《3》481和sel《4》482提供控制信号480。同样,基于选择信号sel《3》481和sel《4》482,时钟分频器400的不同分频比是可选择的。

49.在通过附加的反相器491、492、493应用运行时间调整、稳定和/或缓冲之后,在节点divn_stage2b 470处提供时钟分频器400的divout 495。

50.nand2 445创建两个周期(2t)的divout 495高时间。附加的反相器460创建一个周

期(1t)的divout 495低时间。节点divn_stage5 431创建两个周期(2t)的divout 495低时间。节点divn_stage7 441创建三个周期(3t)的divout 495低时间。由于nand2 445由时钟分频器400的不同模数共享,因此不同的分频比具有两个周期(2t)的divout 495高时间。

51.此外,将时钟门控到门控反相器的pmos上拉可以用于在任意数量的周期内增加其输出的低时间。

52.时钟分频器400提供不同的模数(分频比),这些模数通过仅门控耦合到门控反相器430(“半锁存器”)或门控反相器440中的nmos的时钟信号clk(第一控制信号)是可选择的。这意味着门控反相器430或门控反相器440作为反相时钟信号clkb(第二控制信号)被部分地门控(半门控),并且引入的输入信号通过pmos将输出拉到已知状态。

53.换言之,只有门控反相器的pmos和nmos(上拉或下拉)时钟之一被门控。因此,由于仅门控反相器的一侧被门控,因此功耗较低,因为门控时钟需要较低的驱动强度。如果仅对nmos进行门控,则功耗甚至可以进一步降低,因为对于相等的驱动强度,pmos尺寸至少是nmos的两倍。通过半门控,与pmos和nmos都被门控的场景相比,电路非常简单且紧凑。根据另一方面,如果两者都被门控,则门控反相器将是具有未定义输出的“三态”。通过仅门控例如nmos,pmos将定期将输出上拉到已知状态,因为进入门控反相器的数据会上下改换。换句话说,基于进入门控反相器的数据来限定输出信号。

54.对于时钟分频器400,与时钟分频器200的情况中不同,三个不同的模数(分频比)是通过门控时钟而不是对数据使用组合逻辑来选择的。时钟可以被“开环”缓冲,这允许打破速度现状(breaking out of the speed box),即这允许时钟分频器400可操作的最大速度甚至高于时钟分频器200可操作的最大速度。

55.本文描述的时钟分频器200、400可以被配置用于高频,例如频率高于100mhz,优选高于1ghz,更优选接近或者甚至高于10ghz或射频。时钟分频器200、400可以适合用于模数转换器(adc)或锁相环(pll)。

56.时钟分频器200、400可以被配置为在基础产品的生命周期(超过十年)内鲁棒地工作。由于其鲁棒性,时钟分频器200、400可以被配置为在存在器件老化或退化的情况下针对所有(物理上有意义的)工艺电压和温度(pvt)变化提供预定义的规范。特别地,时钟分频器400可以被配置为在存在器件老化或退化的情况下针对所有(物理上有意义的)pvt变化,在65nm拓扑中在大于10ghz的频率下操作。

57.在一个示例用例中,电子电路可以实现为pll中的时钟分频器200、400。pll生成的时钟可能需要被分频以与参考时钟进行比较。为了提供减速,整个时钟分频器可以分为几个级,其中第一级可能具有最高速度(该级可操作的操作频率)并且最难设计。对于pll的特定用例,第一级(前置分频器)的时钟分频器可能需要为三模,从而提供/3、/4和/5的可选择分频比。表示示例时钟分频器200、400的本电子电路可以被配置为达到这些要求。

58.然而,电子电路是通用的,并且因此不限于在adc或pll中实施。

59.图5是包括总线保持器的门控反相器的简化示意图。

60.在框510中,门控反相器根据门控级表示来示出。在框530中,门控反相器根据晶体管表示来示出。

61.在框510中,节点512之后示出了包括第一反相器516和第二反相器518的环形配置。在节点514处提供的输出信号y。

62.在框530中,根据晶体管表示示出了第一反相器516和第二反相器518。第一反相器516和第二反相器518中的每一个都包括pmos 536、540和nmos538、542。

63.在任何情况下,第一反相器516和第二反相器518提供电容效应。因此,可以在门控反相器的输出514、534不下降或改变其值的情况下停止时钟。因此,避免了撬棒电流(crow-bar currents)。

64.时钟分频器200和时钟分频器400的所有门控反相器都包括总线保持器。然而,一般而言,总线保持器对于时钟分频器200、400是可选的而不是强制性的。

65.图6是根据时钟分频器400的示例的过程信号600的简化示意图。图6的原理布局对应于图3示出了时钟分频器200的过程信号300。因此这些图的比较提供了对时钟分频器200、400的两个示例的性能的量度。同样,在x轴上示出了以ns为单位的时间。y轴示出了在“高”和“低”之间切换的相应信号的幅度。

66.clk_stgln3 612和clkb_stgln3 614是用于对门控反相器进行门控的时钟信号和反相时钟信号。图6中的时钟信号频率为11ghz。

67.divn_stagel到divn_stage7 620是时钟分频器400的门控反相器410、415、420、425、430、435、440的输出信号。

68.sel《4》622是用于在时钟分频器400的不同分频比div-3、div-4和div-5之间进行选择的选择信号之一。因此,门控反相器的输出信号,即信号divn_stagel到divn_stage7 620,对应于在不同时间点处切换sel《4》而在div-3、div-4和div-5之间变化。divout 626示出了新鲜硅模拟的分频输出,并且divout 628示出了老化10年后的分频输出。它们基于sel《3》,尤其是sel《4》622的状态提供在逻辑“高”和逻辑“低”之间的不同比率,使得时钟分频器400提供不同的分频比。

69.从“老化的”divout 628和“新鲜的”divout 626的比较可以明显看出,即使在10年的模拟寿命和所有(物理上有意义的)pvt变化之后,两个信号对于所有分频比/3、/4和/5基本相同。这意味着,通过避免将慢速组合逻辑应用于数据、通过仅对门控反相器进行半门控以及通过根据“开环”时钟缓冲配置来配置时钟分频器400,时钟分频器400实现了最高速度。时钟分频器400在高于11ghz的频率下可操作,并在这些频率下提供恒定的分频比达超过10年的寿命(在可忽略的容差范围内)。因此,即使对于存在器件老化或退化的所有(物理上有意义的)工艺电压和温度(pvt)变化,也在这些频率下提供了分频比。

70.尽管上文已参考特定示例描述了本公开,但本公开不限于这些示例,并且毫无疑问,本领域技术人员将想到在所要求保护的时钟分频器的范围内的进一步替代方案。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。