使用逆crc生成器多项式进行解码的循环冗余校验crc

技术领域

1.本发明的领域涉及循环冗余校验(crc)电路、通信单元和crc的计算方法。本发明的领域适用于但不限于当前和未来几代通信标准的信道编码。

背景技术:

2.已知循环冗余校验(crc)可以用于检测在信息位的序列从源传递到宿时是否已将任何错误引入到信息位的序列中。

3.源端crc计算

4.在源端,对a信息位的序列a=[a0,a

l

,a2,...,a

a-1

]执行crc计算,以便生成l个奇偶校验位的序列p=[p0,p1,p2,...,p

l-1

]。

[0005]

根据crc生成器多项式,作为a的a个信息位的函数生成奇偶校验位的序列p。crc生成器多项式通常在正在实施的通信标准中指定,诸如3gpp新无线电[1]的l=6位crc生成器多项式:g

crc6

(d)=[d6 d5 1]。值得注意的是,通信标准通常指定了规定crc的生成的约束,而没有指定其可以如何实施。更具体地,通信标准通常只指定以系统形式执行计算,使得多项式a0d

a l-1

a1d

a l-2

…

a

a-1dl

p0d

l-1

p1d

l-2

…

p

l-2

d1 p

l-1

当除以crc生成器多项式时,在gf(2)中产生等于“0”的余数。

[0006]

l个奇偶校验位的序列p通常附加到a信息位的序列a的末尾,以产生b=a l个位的crc编码序列

[0007]

b=[b0,b

l

,b2,...,b

b-1

],其中

[0008]bk

=ak,对于k=0,1,2,

…

a-1并且

[0009]bk

=p

k-a

,对于k=a,a 1,a 2,

…

,a l-1。

[0010]

一些通信标准规定,在crc计算之前,a信息位的序列a可以附加到l个1值位的序列的末尾,以生成包括l a个位的扩展的信息位序列:

[0011]a′

=[a

′0,a

′1,a

′2,...,a

′

l a-1

],其中

[0012]a′k=1,对于k=0,1,2,

…

l-1并且

[0013]a′k=a

k-l

,对于k=l,l 1,l 2,

…

,l a-1。

[0014]

在这些情况下,l个奇偶校验位的序列p可以作为扩展的信息位序列a

′

的所有l a个位的函数计算,而不是作为信息位序列a的a个位的函数计算。l个奇偶校验位的序列可以附加到a个信息位的序列a的末尾,以产生crc编码序列:

[0015]

b=a l个位b=[b0,b

l

,b2,...,b

b-1

],如上。

[0016]

在某些情况下,crc编码序列b的位可以在源端进行加扰、交织和/或信道编码。

[0017]

宿端crc计算

[0018]

在宿端,可以执行crc计算以检测b=a l个恢复的crc编码位的序列中的错误,如果存在错误,它将与在源中获得的crc编码位序列b不同。这里,恢复的crc编码位序列可以表示l个恢复的奇偶校验位的序列

附加到a个恢复的信息位的序列的末尾,如果存在错误,它将与在源中获得的奇偶校验位序列p和信息位序列a不同。

[0019]

可以通过执行crc计算来检测错误,以作为的a个恢复的信息位的函数获得l个计算出的奇偶校验位序列如果计算出的奇偶校验位序列与恢复的奇偶校验位序列不同,则已检测到错误。可替代地,可以通过执行crc计算以作为的所有b=a l个恢复的crc编码位的函数获得l个计算出的奇偶校验位的序列来检测错误。在这种情况下,计算出的奇偶校验位序列成为crc的校验子(如理解的那样)。如果该校验子不等于l个0值位的序列,则已检测到错误。请注意,标准通常不指定如何使用crc来检测错误,允许实施者选择此处描述的方法或另一种方法。

[0020]

在源通过将a信息位的序列a附加到l个1值位的序列的末尾来获得扩展的信息位序列a

′

的情况下,在宿中执行相同的扩展操作。更具体地,将a个恢复的信息位的序列附加到l个1值位的序列的末尾,以生成包括l a个位的扩展的恢复的信息位序列:

[0021]

其中

[0022]

对于k=0,1,2,

…

l-1并且

[0023]

对于k=l,l 1,l 2,

…

,l a-1。

[0024]

在这些情况下,l个计算出的奇偶校验位的序列可以作为扩展的恢复的信息位序列的所有l a个位的函数来计算,而不是作为恢复的信息位序列的a个位的函数计算。可替代地,b个恢复的crc编码位的序列可以附加到l个1值位的序列的末尾,以生成包括l b个位的扩展的恢复的crc编码位序列:

[0025]

其中

[0026]

对于k=0,1,2,

…

l-1并且

[0027]

对于k=l,l 1,l 2,

…

,l b-1。

[0028]

在这些情况下,l个计算出的校验子位的序列可以作为扩展的恢复的crc编码位序列的所有l b个位的函数计算,而不是作为恢复的crc编码位序列的b个位的函数计算。

[0029]

在源对crc编码序列b的位执行加扰、交织和/或信道编码的情况下,可以在宿中执行逆解扰、解交织和/或信道解码操作,以获得恢复的crc编码位序列。在源中对crc编码序列b的加扰仅影响其由奇偶校验位序列p提供的位的情况下,宿可以在crc计算后对计算出的奇偶校验位序列应用逆加扰操作,而不是在crc计算之前对恢复的crc编码位序列应用逆加扰操作。

[0030]

使用移位寄存器的crc计算

[0031]

现在参考图1,示出了源电路的l=6位crc生成器多项式g

crc6

(d)=[d6 d5 1]的已知移位寄存器实施方式100。crc生成器多项式可以被解释为线性反馈移位寄存器101,如图1针对[1]的l=6位crc生成器多项式g

crc6

(d)=[d6 d5 1]所举例说明的。

[0032]

该移位寄存器可以用于计算与k个输入位的序列s=[s0,s1,s2,

…

,s

k-1

]103相对应的l个奇偶校验位的序列p=[p0,p1,p2,...,p

l-1

]102,该k个输入位的序列可以由信息位序列a、扩展的信息位的序列a

′

、恢复的信息位序列恢复的crc编码位序列恢复的扩展的信息位序列或恢复的扩展的crc编码位序列提供。图1在104处示出了a=12个信息位的序列如何:

[0033]

a=[0 1 1 0 0 1 1 1 0 1 1 0]可以转换为l=6个奇偶校验位的序列:

[0034]

p=[1 0 0 1 0 1],其中k=a且s=a。这些奇偶校验位可以附加到信息位的序列a的末尾,以获得b=18个crc编码位的序列:

[0035]

b=[0 1 1 0 0 1 1 1 0 1 1 0 1 0 0 1 0 1]。

[0036]

注意,某些应用可以采用crc生成器多项式的逆,这可以通过由l减去其每个指数来获得。例如,l=6位crc生成器多项式g

crc6

(d)=[d6 d5 1]=[d6 d5 d0]的逆由下式给出:g

invcrc6

(d)=[d

l-6

d

l-5

d

l-0

]=[d6 d 1]。

[0037]

逆生成器多项式可以由逆线性反馈移位寄存器201表示,如图2针对l=6位逆crc生成器多项式g

invcrc6

(d)=[d6 d 1]所举例说明的。

[0038]

现在参见图2,示出了源电路的l=6位逆crc生成器多项式g

invcrc6

(d)=[d6 d 1]的已知移位寄存器实施方式200。

[0039]

图2在204处示出了相同的a=12个信息位的序列如何:

[0040]

来自图1的a=[0 1 1 0 0 1 1 1 0 1 1 0]可以转换为l=6个奇偶校验位的序列:

[0041]

p=[1 0 0 1 1 1],其中k=a且s=a。

[0042]

注意,这些奇偶校验位与图1的那些不同,因为逆生成器多项式g

invcrc6

(d)=[d6 d 1]不同于生成器多项式g

crc6

(d)=[d6 d5 1]。

[0043]

使用生成器矩阵的crc计算

[0044]

生成器矩阵可以用于对k个输入位的序列s=[s0,s1,s2,

…

,s

k-1

]执行crc计算,该k个输入位的序列可以由信息位序列a、扩展的信息位的序列a

′

、恢复的信息位序列恢复的crc编码位序列恢复的扩展的信息位序列或恢复的扩展的crc编码位序列提供。更具体地,l个奇偶校验位的序列p=[p0,p1,p2,

…

,p

l-1

]可以根据p=sg作为输入位序列s的函数生成,其中g是crc的k

×

l生成器矩阵,矩阵乘法为在gf(2)中执行。生成器矩阵g的第k行作为在计算k个输入位的序列的crc时产生奇偶校验位序列获得,其中第k位设置为1,并且所有其他位设置为0。例如,在l=6位crc生成器多项式的情况下,g

crc6

(d)=[d6 d5 1]用于计算k=12个输入位的序列的crc,生成器矩阵由下式给出:

[0045][0046]

注意,在从上面的a=12个信息位的示例序列a=[0 1 1 0 0 1 1 1 0 1 1 0]中,第2、3、6、7、8、10和11位设置为1。在这种情况下,l=6个奇偶校验位的序列p=[1 0 0 1 0 1]可以作为该生成器矩阵的第2、3、6、7、8、10和11行的“异或”获得。

[0047]

注意,当生成器矩阵应用于恢复的crc编码位序列以获得校验子时,生成器矩阵表现为奇偶校验矩阵。在从上面的b=18个crc编码位的示例序列b=[0 1 1 0 0 1 1 1 0 1 1 0 1 0 0 1 0 1]中,第2、3、6、7、8、10、11、13、16、18位设置为1。如可以预期的,校验子可以作为k=18个输入位的生成器矩阵的第2、3、6、7、8、10、11、13、16和18行的“异或”获得,该生成器矩阵由下式给出:

[0048][0049]

可以观察到,在对应于特定数量的k

′

个输入位的生成器矩阵g中,最后k行等于对应于k个输入位的生成器矩阵g,其中k≤k

′

。例如,上面k=18的生成器矩阵g的最后12行等于上面k=12的生成器矩阵g。

[0050]

在crc编码序列b的位在源中交织的情况下,宿可以在应用对应的解交织操作以获

得恢复的crc编码位序列之后使用生成器矩阵g执行crc计算。可替代地,生成器矩阵g的行可以被对应地交织并且用于基于恢复的crc编码位序列的交织版本来计算crc。例如,这使得能够在3gpp新无线电[1]的物理下行链路控制信道(pdcch)中的盲解码期间提前终止极性解码[2]。

[0051]

总之,已知crc计算可以以多种方式等效地描述,包括生成器多项式,诸如:g

crc6

(d)=[d6 d5 1];线性反馈移位寄存器,诸如101;或者生成器矩阵g,诸如上面的示例。

[0052]

并行处理可以用于实施具有低延迟的crc计算。这里,一组两个或更多个并行处理器可以在控制器的指导下操作,以一次处理两个或更多个位并计算一组寄存器内的对应的crc位。在一些已知的实施方式中,处理器可以执行位与生成器多项式的二进制表示的乘法[3]。然而,与例如“异或”操作相比,乘法是相对复杂的操作,并且存在对改进的crc方法的需要,例如在使用并行处理时。

技术实现要素:

[0053]

本发明提供了一种使用处理进行低延迟crc计算的方法。特别地,本发明详述了存储器映射并引入了消除对存储器和处理器之间的置换网络的需要的查找表(lut)。在从属权利要求中阐述了本发明的特定实施例。参考下文描述的实施例,本发明的这些和其他方面将变得显而易见并被阐明。

[0054]

在本发明的第一方面中,一种循环冗余校验crc解码器电路包括:输入端,其用于从对输入位序列进行编码的预定义crc生成器多项式接收具有输入位序列的输入流,输入位序列包括信息位和crc位;以及至少一个处理器,其被配置为执行输入位序列的crc解码计算。至少一个处理器被配置为:应用对输入位序列进行编码的预定义crc生成器多项式的逆处理操作以产生数据集;从数据集计算crc校验子;以及确定所述crc校验子是否包含指示crc错误的任何1值位。

[0055]

在可选示例中,crc解码器电路可以包括查找表lut,其可操作地联接到至少一个处理器并且包括多个地址,其中多个地址中的至少一个被配置为存储与输入流的输入位对齐的crc生成器矩阵的一个或多个行。以这种方式,并且由于输入流与crc生成器矩阵的行对齐,可以在没有复杂路由的情况下获得单个奇偶校验位序列,该路由将需要使任何输入位能够与crc生成器矩阵的任何行组合。

[0056]

在可选示例中,至少一个处理器可以被配置为首先通过使用对齐的输入流的一个或多个位掩蔽存储在lut中的crc生成器矩阵的一个或多个行来将lut数据与输入流组合。以这种方式,可以消除对计算的奇偶校验位没有贡献的生成器矩阵的行。

[0057]

在可选示例中,crc解码器电路还可以包括:查找表lut,其可操作地联接到至少两个处理器并且包括多个地址,其中多个地址中的至少一个被配置为存储与输入流的输入位对齐的crc生成器矩阵的两个或更多个行;其中至少两个处理器可以被配置为:首先将lut数据与输入流组合以生成两个或更多个中间奇偶校验位序列;并且其次将两个或更多个中间奇偶校验位序列组合成单个奇偶校验位序列。以这种方式,可以通过使用并行处理来减少完成crc计算所需的步骤的数量。

[0058]

在可选示例中,存储在lut中的crc生成器矩阵的两个或更多个行可以通过零填充与输入位序列对齐。以这种方式,零填充重新定位输入位序列内的位,使得它们与crc生成

器矩阵的对应的行对齐。

[0059]

在可选示例中,与存储在lut中的crc生成器矩阵的两个或更多个行对齐可以包括以下中的一个:至少两个处理器接收提供输入位序列长度的具有零填充的输入流;或者其中输入位序列具有第一长度,并且两个或更多个处理器中的至少一个对输入位序列进行零填充。以这种方式,输入位序列的位可以在p个并行处理器之间均匀分布,从而允许所有并行处理器以相同方式操作且任何处理器都不需要特殊的独立控制。

[0060]

在可选示例中,存储在lut中的crc生成器矩阵中的行的数量等于或超过最大支持输入位序列长度(k

max

)除以一个或多个处理器的数量p。以这种方式,单个lut可以用于启用任何支持的输入位序列长度的crc处理,避免针对不同的输入位序列长度使用不同的crc处理机制的需要。

[0061]

在可选示例中,crc解码器电路还可以包括控制器,该控制器可操作地联接并被配置为控制至少一个处理器和lut。以这种方式,控制器可以协调并行处理器的操作和从lut读取crc生成器矩阵的行。

[0062]

在可选示例中,生成两个或更多个中间奇偶校验位序列包括:进行倍数[k/p]次数据的第一组合,其中k是输入位序列的长度。以这种方式,处理输入序列的k个位所需的步骤的数量除以了并行处理器的数量,从而最小化处理步骤并最大化处理效率。

[0063]

在可选示例中,两个或更多个中间奇偶校验位序列的第二组合被执行倍数[log2(p)]次以生成单个奇偶校验位序列,其中p是两个或更多个并行处理器的数量。以这种方式,处理输入序列的k个位所需的步骤的数量减少到并行处理器的数量的对数,从而最小化处理步骤并最大化处理效率。

[0064]

在可选示例中,生成器矩阵(g)的行中的至少一个行中的l个位可以被填充零值位以将位序列增加到第二长度(l

′

)。以这种方式,可以将长度调整为更便于在常规存储器架构(诸如32位ram)中存储的长度。

[0065]

在本发明的第二方面中,描述了一种包括根据第一方面的crc计算电路的通信单元。

[0066]

在本发明的第三方面中,描述了一种用于循环冗余校验crc的方法。该方法包括从对输入位序列进行编码的预定义crc生成器多项式接收具有输入位序列的输入流该输入位序列包括信息位和crc位;以及执行输入位序列的crc解码计算。该方法还包括:应用对输入位序列进行编码的预定义crc生成器多项式的逆处理操作以产生数据集;从数据集计算crc校验子;以及确定crc校验子是否包含指示crc错误的任何1值位。

附图说明

[0067]

将参考附图仅通过示例的方式描述本发明的进一步细节、方面和实施例。在附图中,相似的附图标记用于标识相似或功能类似的元件。图中的元件是为了简单和清楚而示出的并且不一定按比例绘制。

[0068]

图1示出了源电路的l=6位crc生成器多项式g

crc6

(d)=[d6 d5 1]的已知移位寄存器实施方式,并提供了a=12个信息位的序列a=[0 1 1 0 0 1 1 1 0 1 1 0]可以如何转换为l=6个奇偶校验位的序列p=[1 0 0 1 0 1]的示例,其中k=a且s=a。

[0069]

图2示出了源电路的l=6位逆crc生成器多项式g

invcrc6

(d)=[d6 d 1]的已知移位

寄存器实施方式,并提供了a=12个信息位的序列a=[0 1 1 0 0 1 1 1 0 1 1 0]可以如何转换为l=6个奇偶校验位的序列p=[1 0 0 1 1 1]的示例,其中k=a且s=a。

[0070]

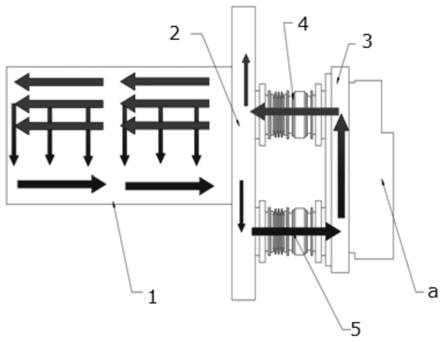

图3示出了对于其中p=4的情况的本发明的示例实施例。

[0071]

图4示出了在本发明的示例实施例中的对应于l=6位crc生成器多项式g

crc6

(d)=[d6 d5 1]的生成器矩阵g在lut中的存储,其中:l

′

=8,k

max

=18且p=4。图4还提供了a=9个信息位的序列a=[1 1 0 1 1 0 0 1 1]可以如何转换为l=6个奇偶校验位的序列p=[0 0 0 1 0 1]的示例,其中:k=a且s=a。

[0072]

图5示出了本发明的示例实施例中的控制器的操作的流程图。

[0073]

图6示出了宿电路的l=6位逆crc生成器多项式g

invcrc6

(d)=[d6 d 1]的移位寄存器实施方式,其用于计算使用源电路的l=6位crc生成器多项式g

crc6

(d)=[d6 d5 1]生成的crc编码位序列的校验子。图6还提供了b=18个crc编码位的序列b=[0 1 1 0 0 1 1 1 0 1 1 0 1 0 0 1 1 1]可以如何转换为l=6个校验子位的序列的示例,其中k=b,s=b且

[0074]

图7示出了在本发明的示例实施例中的对应于l=6位逆crc生成器多项式g

invcrc6

(d)=[d6 d 1]的逆生成器矩阵g

′

在lut中的存储,其中l

′

=8,k

max

=18且p=4。图7还提供了b=15个crc编码位的序列b=[1 1 0 1 1 0 0 1 1 00 0 1 0 1]可以如何转换为l=6个校验子位的序列的示例,其中k=b,s=b且

[0075]

图8示出了根据本发明的一些示例实施例的可以在电子设备或无线通信单元中采用以执行crc计算的典型计算系统。

[0076]

图9示出了本发明的示例实施例中的控制器的操作的流程图,该控制器基于逆生成器矩阵g

′

进行操作。

具体实施方式

[0077]

使用根据第一方面的生成器矩阵的crc计算的并行处理

[0078]

现在参考图3,示出了对于p=4的情况的本发明的示例循环冗余校验crc计算电路300。本发明的第一方面旨在解决使用一组p个并行处理器301对输入位的连续序列有效地执行l位crc计算的挑战。这里,并行处理器的数量采用固定值p,其可以在设计时选择为大于或等于“2”的任何值。相比之下,连续输入位序列s中的位的数量k∈[1,k

max

]可能在运行时变化,其中最大输入位序列长度k

max

可以在正在实施的标准中指定。如图3对于其中p=4的示例所示,并行处理器301由查找表(lut)302、输入流303、寄存器组304和控制器305辅助。在其他示例中,并行处理器301的数量可以变化。

[0079]

在crc计算过程的步骤中,p个处理器301中的多个(并且在一些示例中,每个)能够计算一组l

′

位与掩蔽位的“与”307,并且然后计算所得一组l

′

位与另一组l

′

位的“异或”308,其中l

′

≥l可以选择为便于实施的值,诸如,例如8、16或32位。处理器中的多个还能够在一些步骤期间可选地仅执行这些“与”307和“异或”308操作中的一个或两者都不执行。在一些示例中,每个步骤可以对应于硬件实施方式中的至少一个时钟周期。在一些示例中,每个处理器可以是单指令多数据(simd)处理器中的处理单元。注意,不是使用“与”307操作,而是可以通过使用时钟或电源门控在掩蔽位设置为零时禁用一组l

′

位的传递以替代布置

来实现掩蔽操作。此后,使用输入流303的两个或更多个位来掩蔽存储在lut 302中的crc生成器矩阵的对齐的两个或更多个行并且由此生成两个或更多个中间奇偶校验位序列包括禁用几组位的传递的此类时钟或电源门控技术。

[0080]

本发明的一些示例利用以下观察:在对应于k

max

个输入位的生成器矩阵g中,最后k行等于对应于k个输入位的生成器矩阵g,其中k≤k

max

。因此,可以在图3的相同lut 302的帮助下完成连续crc计算过程,例如,lut 302可以在只读存储器(rom)或随机存取存储器(ram)中实施。这里,在本发明的专用硬件实施方式中可以使用专门配置的rom来存储lut,而在使用通用处理器的实施方式中可以使用ram来存储lut 302。更具体地,该lut 302可以存储对应于最大支持数量的输入位k

max

的生成器矩阵g的k

max

个行。

[0081]

现在参考图4,在本发明的示例实施例中示出了对应于l=6位crc生成器多项式g

crc6

(d)=[d6 d5 1]的生成器矩阵g 400在lut中的存储,其中l

′

=8,k

max

=18且p=4。图4还提供了a=9个信息位的序列a=[1 1 0 1 1 0 0 1 1]可以如何转换为l=6个奇偶校验位的序列p=[0 0 0 1 0 1]的示例,其中k=a且s=a。

[0082]

如图所示,在一些示例中,存储在lut中的生成器矩阵g的每一行中的l个位可以可选地用零值位401填充,以便将其长度增加到l

′

位。例如,在生成器矩阵g的行包括l=24个位的情况下,可以用8个零值位填充它们,以便将它们的长度增加到l

′

=32个位并允许它们存储在32位ram中。在一些示例中,填充位可以被添加到生成器矩阵g的每一行的开头,而在其他示例中它们可以被添加到每一行的末尾。不是对存储在lut中的生成器矩阵g的每一行应用填充,而是设想在替代布置中,可以在已经从lut读取行之后,在其后续处理期间的某个时间点向行添加填充。

[0083]

生成器矩阵g的k

max

个行存储在lut 302中的几组p个行402中。在k

max

不能被p整除的情况下,可以对生成器矩阵g的顶部前置一组附加mod(-k

max

,p)个行403,以便将其行的数量扩展为p的倍数。这些附加行可以包含任何任意位值。来自(扩展的)生成器矩阵的[k

max

/p]个连续组p个行(和它们的填充位)402的每一个可以被连接并存储在lut 302的连续地址中,其中第一组p个行可以被地址0索引。这里,[x]是大于或等于x的最小整数。

[0084]

在替代布置中,生成器矩阵g的每个(填充的)行的位在它们被连接之前可以颠倒。在替代布置中,来自(扩展的)生成器矩阵g的数量[k

max

/p]个连续组p个行402可以存储在lut 302内的其他地址中。图4示出了对于l

′

=8,k

max

=18且p=4的情况,对应于l=6位crc生成器多项式g

crc6

(d)=[d6 d5 1]的生成器矩阵g在lut 302中的存储。

[0085]

还参考图3,图3的输入流303用于提供连续输入位序列s。输入序列s的位由输入流303以与lut 302中的生成器矩阵g的行的布置对齐的方式提供。如下文将详述的,这种对齐避免了对在输入流303、lut 302和处理器301之间复杂路由的需要。更具体地,当输入流303提供它们时,通过将输入位序列s中的k个位布置成几组p个位404来实现对齐。在k不能被p整除的情况下,可以通过将一组mod(-k,p)个零值填充位405前置到输入位序列s以便将其长度扩展到p的倍数来实现对齐。来自(扩展的)输入位序列的数量[k/p]个连续组p个位404可以由输入流303在crc计算过程的连续步骤中提供。注意,在一些布置中,来自输入流提供的(扩展的)输入位序列的[k/p]个连续组p个位(404)可以从ram的连续地址读取,该ram具有至少[k

max

/p]个地址的容量。

[0086]

输入位s的k位序列的crc计算过程在图3的控制器305的指导下使用如图5的流程

图所示的两组步骤完成。可以在第一组[k/p]个步骤期间计算一组p个l个奇偶校验位的中间序列406。然后在第二组[log2(p)]个步骤期间,p个中间奇偶校验位序列406可以组合成期望的l个奇偶校验位的单个序列p=[p0,p1,p2,...,p

l-1

]102。

[0087]

现在参考图5,参考图3和图4的前面的讨论,流程图500示出了根据本发明的示例实施例的控制器的操作。在第一组[k/p]个步骤期间,p个中间奇偶校验位序列406在图3的寄存器组304中累加。该寄存器组304包括p个寄存器,每个寄存器可以存储l

′

个位。控制器305内的计数器c 306在一组[k/p]个步骤511中的第一步骤开始时被初始化501为0值,并且该计数器c 306在此后的多个连续步骤开始时递增502。在多个(例如每个)步骤中,从lut 302的地址([k

max

/p]-[k/p] c)读取503生成器矩阵g的一组p个行402。同时,由输入流303提供504来自(扩展的)输入位序列的具有索引c的一组p个位404。

[0088]

在第一组[k/p]个步骤中的每一个中,由lut 302提供的生成器矩阵g的p个行中的每一个被由输入流303提供的p个输入位中的对应的一个掩蔽505。更具体地,p个处理器301中的每一个通过将生成器矩阵g的对应的行中的l

′

个位中的每一个与对应的输入位进行“与”307来执行这些p个掩蔽操作中的对应的一个。由于输入流303中的p个输入位的布置与lut 302中的生成器矩阵g的p个行之间的对齐,可以有利地执行该掩蔽而不需要输入流303、lut 302和处理器301之间的复杂路由。

[0089]

注意,在[k/p]个步骤的第一步骤中,在该示例中并且当c=0时,输入流303提供的一组p个输入位404在k不是p的倍数的情况下将包括mod(-k,p)个前置零值填充位405。如上所述,这些零值填充位用于实现对齐并用于掩蔽来自从lut 302读取的生成器矩阵g的一组p个行402的对应的mod(-k,p)个行。在这种情况下,这些mod(-k,p)个被掩蔽的行将在生成器矩阵g的最后k个行之前,从而有利地确保只有生成器矩阵g的最后k个行将有机会影响p个中间奇偶校验位序列406。如上所述,存储在lut 302中的生成器矩阵g中的k

max

个行的最后k个行等于对应于k个输入位的生成器矩阵g。以这种方式,即使k不是p的倍数,存储对应于k

max

个输入位的生成器矩阵g的相同lut 302也可以有利地重新用于k的所有值。

[0090]

在第一组[k/p]个步骤中的第一步骤506期间,当c=0时,在该步骤期间获得的生成器矩阵g的p个被掩蔽的行被写入507到寄存器组304,以便初始化p个中间奇偶校验位序列406。在多个后续步骤中,当0《c《[k/p]时,从寄存器组304读取508p个中间奇偶校验位序列406并将其提供给p个处理器301,其中它们与在该步骤中获得的生成器矩阵g的p个被掩蔽的行进行“异或”308 509。然后将结果写回510寄存器组304,以便累加p个中间奇偶校验位序列406。注意,计数器c 306的动作是按升序读取lut 302中的[k/p]个地址,与输入流303以其自然顺序提供几组p个输入位404一致。然而,在其他布置中,输入流303可以以任何顺序提供几组p个输入位404并且可以以对应的顺序读取lut的地址。图4提供了a=9个信息位的序列a=[1 1 0 1 1 0 0 1 1]303可以如何转换为一组p=4个中间奇偶校验位序列406的示例。

[0091]

在第二组[log2(p)]个步骤514期间,寄存器组304用于将p个中间奇偶校验位序列406组合成单个期望奇偶校验位序列102。计数器c 306在一组[log2(p)]个步骤中的第一步骤开始时被初始化512为0值,并且该计数器c 306在此后的连续步骤开始时递增513。在0≤c《[log2(p)]时的多个步骤中,从p个寄存器的组304中的第一p/2c个寄存器读取515一组p/2c个中间奇偶校验位序列。一组p/2c个中间奇偶校验位序列然后被分解成两个子集,每个子

集包括p/2

c 1

个中间奇偶校验位序列。然后将p/2

c 1

个中间奇偶校验位序列的第一子集中的每个中间奇偶校验位序列与来自p/2

c 1

个中间奇偶校验位序列的第二子集的对应的中间奇偶校验位序列进行“异或”308 516。所得一组p/2

c 1

个经“异或”308的中间奇偶校验位序列然后被写入517到p个寄存器的组304中的第一组p/2

c 1

个寄存器。

[0092]

在第二组[log2(p)]个步骤中的最后一个步骤完成后,p个中间奇偶校验位序列将被组合成单个期望奇偶校验位序列,该序列存储在p个寄存器的组304中的第一寄存器中。然后可以通过移除零值填充位从寄存器的l

′

个位中提取518该奇偶校验位序列p=[p0,p1,p2,...,p

l-1

]的l个位。注意,在此处描述的方法中,p个中间奇偶校验位序列被连续组合到寄存器组304中的p个寄存器的第一寄存器中。

[0093]

在替代布置中,p个中间奇偶校验位序列可以连续地组合到寄存器组304中的p个寄存器中的任何寄存器中。例如并且返回参考图4,提供了一组p=4个中间奇偶校验位序列406可以如何组合成l=6个奇偶校验位的序列p=[0 0 0 1 0 1]102的示例,其中k=a且s=a。

[0094]

本发明的第一方面中的使用逆生成器矩阵的校验子计算及其相关联的并行处理

[0095]

现在参考图6,示出了宿电路的l=6位逆crc生成器多项式g

invcrc6

(d)=[d6 d 1]的移位寄存器实施方式600,其用于计算使用源电路的l=6位crc生成器多项式g

crc6

(d)=[d6 d5 1]生成的crc编码位序列的校验子。图6还提供了b=18个crc编码位的序列b=[0 1 1 0 0 1 1 1 0 1 1 0 1 0 0 1 1 1]可以如何转换为l=6个校验子位的序列的示例,其中k=b,s=b且

[0096]

在宿中,可以使用crc生成器多项式的逆来执行恢复的crc编码位序列的校验子的crc计算,即使在源中使用常规crc生成器多项式执行了crc计算。更具体地,可以使用逆crc生成器多项式的移位寄存器表示作为序列中的所有b=a l个恢复的crc编码位的函数来计算l个校验子位的序列然而,当使用逆crc生成器多项式的移位寄存器表示来计算校验子时,必须以颠倒顺序处理序列的b个位。如果该校验子不等于l个0值位的序列,则已检测到错误。这在图6中被示出为l个奇偶校验位102的序列,其中逆crc生成器多项式g

invcrc6

(d)=[d6 d 1]用于计算图1的无错误的b=18位crc编码序列b的l=6位校验子其中:k=b,102并且s=reverse(b)是通过颠倒b 103中的位的顺序而获得的。注意,校验子包括l=6个零值位,确认b是无错误的。

[0097]

可替代地,可以使用逆crc生成器多项式的k

×

l生成器矩阵g来执行b个恢复的crc编码位的序列的l位校验子的crc计算,其中:k=b。这里,该生成器矩阵g中的行的顺序可以颠倒以获得逆生成器矩阵g

′

。这有利地允许以正向顺序而不是颠倒顺序处理序列的b个位。更具体地,可以将校验子计算为:在从上面的b=18个crc编码位的示例序列b=[0 1 1 0 0 1 1 1 0 1 1 0 1 0 0 1 0 1]中,第2、3、6、7、8、10、11、13、16和18位被设置为1。如可以预期的,l=6位校验子可以作为k=18的逆crc生成器多项式g

invcrc6

(d)=[d6 d 1]的k

×

l逆生成器矩阵的第2、3、6、7、8、10、11、13、16和18行的“异

或”获得,该逆生成器矩阵由下式给出:

[0098][0099]

可以观察到,在对应于特定数量k

′

个输入位的逆生成器矩阵g

′

中,前k行等于对应于k个输入位的逆生成器矩阵g

′

,其中k≤k

′

。例如,上面对于k=18的生成器矩阵g

′

的前12行等于对于k=12的逆生成器矩阵g

′

。这与对应于特定数量k

′

个输入位的常规生成器矩阵g形成对比,在常规生成器矩阵g中,是最后k行等于对应于k个输入位的生成器矩阵g,其中k≤k

′

。

[0100]

在本发明的一些示例中,可以利用逆生成器矩阵g

′

的这个属性来适应图3的方案,使得恢复的crc编码位序列在用作输入位序列s时不需要前置零值填充位405。这有利地允许以更方便的格式存储crc编码位序列如果crc校验成功则可以直接输出crc编码位序列如上所述,图3的lut 302存储对应于最大支持数量的输入位k

max

的逆生成器矩阵g

′

的k

max

个行,而图3的输入流303提供输入位序列s的k个位。然而,当k

max

不能被并行处理器的数量p整除时,不是对生成器矩阵的顶部前置一组mod(-k

max

,p)个任意行403,而是将这些附加行703追加到逆生成器矩阵g

′

的底部,如图7所示。

[0101]

现在参考图7,根据本发明的示例实施例示出了对应于l=6位逆crc生成器多项式g

invcrc6

(d)=[d6 d 1]的逆生成器矩阵g

′

700在lut中的存储,其中l

′

=8,k

max

=18且p=4。图7还提供了b=15个crc编码位的序列b=[1 1 0 1 1 0 0 1 1 0 0 0 1 0 1]可以如何转换为l=6个校验子位的序列的示例,其中k=b,s=b且

[0102]

如图7所示,当k不能被并行处理器的数量p整除时,不是将一组mod(-k,p)个零值填充位405前置到输入位序列s的开头,而是将这些附加填充位705追加到输入位序列s的末尾。如上所述,(扩展的)逆生成器矩阵的多个连续组p个行702存储在lut 302的连续地址

中,其中第一组p个行可以分别由地址0索引。同样,在crc计算的连续步骤中,输入流303提供(扩展的)输入位序列的多个连续组p个位704。

[0103]

图7示出了对于l

′

=8,k

max

=18且p=4的情况的对应于l=6位逆crc生成器多项式g

invcrc6

(d)=[d6 d 1]的逆生成器矩阵g

′

在lut 302中的存储。如上所述,计数器c 306在一组[k/p]个步骤中的第一步骤开始时被初始化为0值,并且该计数器c 306在此后的多个(例如,每个)连续步骤开始时递增。然而,不是在每个步骤中从lut 302的地址([k

max

/p]-[k/p] c)读取生成器矩阵的一组p个行402,而是从地址c读取逆生成器矩阵g

′

的一组p个行702。同时,来自(扩展的)输入位序列的具有索引c的一组p个位704由输入流303提供,如上所述。除了这些差异之外,图7的方案的操作也可以如上所述进行。

[0104]

更具体地,操作如图9的流程图所示进行,与图5的不同之处仅在于,用于从lut读取生成器矩阵的一组p个行402的地址的计算903。

[0105]

因此,图7提供了b=15个crc编码位的序列a=[1 1 0 1 1 0 0 1 1 0 0 0 1 0 1]303可以如何转换为一组p=4个中间奇偶校验位序列706(其然后被组合成l=6个校验子位的序列)的示例,其中k=b,s=b且

[0106]

图9示出了本发明的示例实施例中的控制器的操作的流程图,该控制器基于逆生成器矩阵g

′

进行操作。

[0107]

应用

[0108]

现在参考参照图8,示出了根据本发明的一些示例实施例的可用于实施crc计算的典型计算系统800。这种类型的计算系统可以用在无线通信单元中。相关领域的技术人员还将认识到如何使用其他计算机系统或架构来实施本发明。计算系统800可以表示例如台式机、膝上型或笔记本计算机、手持计算设备(pda、手机、掌上电脑等)、大型机、服务器、客户端或者对于给定应用或环境可能期望或适用的任何其他类型的专用或通用计算设备。计算系统800可以包括至少一个处理器,诸如处理器804。可以使用通用或专用处理引擎(诸如,例如微处理器、微控制器或其他控制逻辑)来实施处理器804。在该示例中,处理器804连接到总线802或其他通信介质。在一些示例中,计算系统800可以是包括存储在其中的用于实施crc计算的可执行代码的非暂时性有形计算机程序产品。

[0109]

计算系统800还可以包括主存储器808,诸如随机存取存储器(ram)或其他动态存储器,以用于存储信息和将由处理器804执行的指令。主存储器808还可以用于在要由处理器804执行的指令的执行期间存储临时变量或其他中间信息。计算系统800同样可以包括只读存储器(rom)或联接到总线802以用于存储处理器804的静态信息和指令的其他静态存储设备。

[0110]

计算系统800还可包括信息存储系统810,其可以包括例如介质驱动器812和可移除存储接口820。介质驱动器812可以包括驱动器或支持固定或可移除存储介质的其他机制,诸如硬盘驱动器、软盘驱动器、磁带驱动器、光盘驱动器、压缩盘(cd)或数字视频驱动器(dvd)读或写驱动器(r或rw),或其他可移除或固定介质驱动器。存储介质818可以包括例如硬盘、软盘、磁带、光盘、cd或dvd、或由介质驱动器812读取和写入的其他固定或可移除介质。如这些示例所示,存储介质818可以包括具有存储在其中的特定计算机软件或数据的计算机可读存储介质。

[0111]

在替代实施例中,信息存储系统810可以包括用于允许计算机程序或其他指令或

数据被加载到计算系统800中的其他类似部件。此类部件可以包括例如可移除存储单元822和接口820,诸如程序盒和盒接口、可移除存储器(例如,闪存或其他可移除存储器模块)和存储器插槽,以及允许软件和数据从可移除存储单元818传递到计算系统800的其他可移除存储单元822和接口820。

[0112]

计算系统800还可以包括通信接口824。通信接口824可以用于允许软件和数据在计算系统800和外部设备之间传递。通信接口824的示例可以包括调制解调器、网络接口(诸如以太网或其他nic卡)、通信端口(诸如通用串行总线(usb)端口)、pcmcia插槽和卡等。经由通信接口824传递的软件和数据是信号的形式,该信号可以是电子信号、电磁信号和光学信号或能够被通信接口824接收的其他信号。这些信号经由信道828提供给通信接口824。该信道828可以携带信号并且可以使用无线介质、线或缆线、光纤或其他通信介质来实施。信道的一些示例包括电话线、蜂窝电话链路、rf链路、网络接口、局域网或广域网以及其他通信信道。

[0113]

在本文档中,术语“计算机程序产品”、“计算机可读介质”等通常可以用于指代介质,诸如,例如存储器808、存储设备818或存储单元822。这些和其他形式的计算机可读介质可以存储供处理器804使用以使处理器执行指定操作的至少一个指令。通常被称为“计算机程序代码”(可以以计算机程序或其他分组的形式分组)的此类指令在被执行时使得计算系统800能够执行本发明的实施例的功能。注意,代码可以直接使处理器执行指定操作,被编译以执行指定操作,和/或与其他软件、硬件和/或固件元素(例如,用于执行标准功能的库)组合以执行指定操作。

[0114]

在使用软件实施元素的实施例中,软件可以存储在计算机可读介质中并且使用例如可移除存储驱动器822、驱动器812或通信接口824加载到计算系统800中。控制逻辑(在该示例中,软件指令或计算机程序代码)在由处理器804执行时使处理器804执行如本文所述的本发明的功能。

[0115]

现在参考图9,在本发明的第二方面中并且参考图3和图4的前面的讨论但不必使用并行处理,流程图900示出了图7的根据本发明的示例实施例的控制器的操作。在第一组[k/p]个步骤期间,p个中间奇偶校验位序列706在图3的寄存器组304中累加。该寄存器组304包括p个寄存器,每个寄存器可以存储l

′

个位。控制器305内的计数器c 306在一组[k/p]个步骤911中的第一步骤开始时被初始化901为“0”值,并且该计数器c 306在此后的多个连续步骤开始时递增902。在多个(例如每个)步骤中,从lut 302的地址(c)读取903生成器矩阵g的一组p个行702。同时,由输入流303提供904来自(扩展的)输入位序列的具有索引c的一组p个位704。

[0116]

在第一组[k/p]个步骤中的每一个中,由lut 302提供的生成器矩阵g的p个行中的每一个被由输入流303提供的p个输入位中的对应的一个掩蔽905。更具体地,p个处理器301中的每一个通过将生成器矩阵g的对应的行中的l

′

个位中的每一个与对应的输入位进行“与”307来执行这些p个掩蔽操作中的对应的一个。由于输入流303中的p个输入位的布置与lut 302中的生成器矩阵g的p个行之间的对齐,可以有利地执行该掩蔽而不需要输入流303、lut 302和处理器301之间的复杂路由。

[0117]

注意,在[k/p]个步骤的第一步骤中,在该示例中并且当c=0时,输入流303提供的一组p个输入位704在k不是p的倍数的情况下将包括mod(-k,p)个前置零值填充位705。如上

所述,这些零值填充位用于实现对齐并用于掩蔽来自从lut 302读取的生成器矩阵g的一组p个行702的对应的mod(-k,p)个行。在这种情况下,这些mod(-k,p)个被掩蔽的行将在生成器矩阵g的最后k个行之前,从而有利地确保只有生成器矩阵g的最后k个行将有机会影响p个中间奇偶校验位序列706。如上所述,存储在lut 302中的生成器矩阵g中的k

max

个行的最后k个行等于对应于k个输入位的生成器矩阵g。以这种方式,即使k不是p的倍数,存储对应于k

max

个输入位的生成器矩阵g的相同lut 302也可以有利地重新用于k的所有值。

[0118]

在第一组[k/p]个步骤中的第一步骤906期间,当c=0时,在该步骤期间获得的生成器矩阵g的p个被掩蔽的行被写入907到寄存器组304,以便初始化p个中间奇偶校验位序列706。在多个后续步骤中,当0《c《[k/p]时,从寄存器组304读取908p个中间奇偶校验位序列706并将其提供给p个处理器301,其中它们与在该步骤中获得的生成器矩阵g的p个被掩蔽的行进行“异或”308 909。然后将结果写回910寄存器组304,以便累加p个中间奇偶校验位序列706。注意,计数器c 306的动作是按升序读取lut 302中的[k/p]个地址,与输入流303以其自然顺序提供几组p个输入位704一致。然而,在其他布置中,输入流303可以以任何顺序提供几组p个输入位704并且可以以对应的顺序读取lut的地址。图7提供了b=15个crc编码位的序列a=[1 1 0 1 1 0 0 1 1 0 0 0 1 0 1]303可以如何转换为一组p=4个中间奇偶校验位序列706的示例。

[0119]

在第二组[log2(p)]个步骤914期间,寄存器组304用于将p个中间奇偶校验位序列706组合成单个期望奇偶校验位序列102。计数器c 306在一组[log2(p)]个步骤中的第一步骤开始时被初始化912为0值,并且该计数器c 306在此后的连续步骤开始时递增913。在0≤c《[log2(p)]时的多个步骤中,从p个寄存器的组304中的第一p/2c个寄存器读取915一组p/2c个中间奇偶校验位序列。一组p/2c个中间奇偶校验位序列然后被分解成两个子集,每个子集包括p/2

c 1

个中间奇偶校验位序列。然后将p/2

c 1

个中间奇偶校验位序列的第一子集中的每个中间奇偶校验位序列与来自p/2

c 1

个中间奇偶校验位序列的第二子集的对应的中间奇偶校验位序列进行“异或”308 916。所得一组p/2

c 1

个经“异或”308的中间奇偶校验位序列然后被写入917到p个寄存器的组304中的第一组p/2

c 1

个寄存器。

[0120]

在第二组[log2(p)]个步骤中的最后一个步骤完成后,p个中间奇偶校验位序列将被组合成单个期望奇偶校验位序列,该序列存储在p个寄存器的组304中的第一寄存器中。然后可以通过移除零值填充位从寄存器的l

′

个位中提取918该奇偶校验位序列p=[p0,p1,p2,...,p

l-1

]的l个位。注意,在此处描述的方法中,p个中间奇偶校验位序列被连续组合到寄存器组304中的p个寄存器的第一寄存器中。

[0121]

在替代布置中,p个中间奇偶校验位序列可以连续地组合到寄存器组304中的p个寄存器中的任何寄存器中。例如并且返回参考图7,提供了一组p=4个中间奇偶校验位序列706可以如何组合成l=6个校验子位的序列706可以如何组合成l=6个校验子位的序列的示例,其中k=b,s=b且

[0122]

在前述说明书中,已经参考本发明的实施例的具体示例描述了本发明。然而,很明显,在不脱离所附权利要求中阐述的本发明的范围的情况下,可以在其中进行各种修改和改变,并且权利要求不限于上述特定示例。

[0123]

如本文所讨论的连接可以是适合于例如经由中间设备从或至相应节点、单元或设

备传递信号的任何类型的连接。因此,除非另有暗示或说明,否则连接可以例如是直接连接或间接连接。可以参考单个连接、多个连接、单向连接或双向连接来示出或描述连接。然而,不同的实施例可以改变连接的实施方式。例如,可以使用单独的单向连接而不是双向连接,反之亦然。此外,多个连接可以用串行或以时间复用方式传递多个信号的单个连接代替。同样,携带多个信号的单个连接可以分离成携带这些信号的子集的各种不同连接。因此,存在用于传递信号的多个选项。

[0124]

本领域技术人员将认识到,本文描述的架构仅仅是示例性的,并且实际上可以实施实现相同功能的许多其他架构。

[0125]

实现相同功能的部件的任何布置都被有效地“关联”,使得实现期望功能。因此,本文中组合以实现特定功能的任何两个部件可以被视为彼此“关联”,使得实现期望功能,而与架构或中间部件无关。同样,如此关联的任何两个部件也可以被视为彼此“可操作地连接”或“可操作地联接”以实现期望功能。

[0126]

此外,本领域技术人员将认识到,上述操作之间的界限仅是说明性的。多个操作可以组合成单个操作,单个操作可以分布在附加操作中,并且操作可以在时间上至少部分重叠地执行。此外,替代实施例可以包括特定操作的多个实例,并且在各种其他实施例中可以改变操作的顺序。

[0127]

本文参考集成电路设备来描述本发明,该集成电路设备包括例如被配置为执行crc计算的功能的微处理器。然而,应当理解,本发明不限于此类集成电路设备,并且可以同样地应用于包括任何替代类型的操作功能的集成电路设备。包括替代类型的操作功能的此类集成电路设备的示例可以包括(仅作为示例)专用集成电路(asic)设备、现场可编程门阵列(fpga)设备或与其他部件集成等。此外,因为本发明的所示实施例大部分可以使用本领域技术人员已知的电子部件和电路来实施,因此为了本发明的基本概念的理解和领会,并且为了不混淆或分散本发明的教导,没有以超出被认为必要的程度的任何更大程度来解释细节。可替代地,电路和/或部件示例可以实施为以合适的方式彼此互连的任意数量的单独集成电路或单独设备。

[0128]

此外例如,示例或其部分可以实施为物理电路系统或可转换为物理电路系统的逻辑表示的软或代码表示,诸如以任何适当类型的硬件描述语言。

[0129]

此外,本发明不限于在非可编程硬件中实施的物理设备或单元,而是可以应用于能够通过根据合适的程序代码操作来执行期望crc计算的可编程设备或单元,诸如小型计算机、个人计算机、记事本、个人数字助理、电子游戏、汽车和其他嵌入式系统、手机和各种其他无线设备,这些在本技术中通常称为“计算机系统”。

[0130]

然而,其他修改、变化和替代也是可能的。因此,说明书和附图被认为是说明性的而不是限制性的。

[0131]

在权利要求中,置于括号之间的任何附图标记不应被解释为限制权利要求。词语“包括”不排除权利要求中列出那些之外的其他元素或步骤的存在。此外,如本文所用,术语“一”或“一个”被定义为至少一个而不是一个。此外,在权利要求中使用诸如“至少一个”和“至少一个”的介绍性短语不应被解释为暗示通过不定冠词“一”或“一个”对另一权利要求元素的引入将包含此类引入的权利要求元素的任何特定权利要求限制为仅包含一个此类元素的发明,即使同一权利要求包括介绍性短语“至少一个”或“至少一个”以及不定冠词

(诸如,“一”或“一个”)。这同样适用于定冠词的使用。除非另有说明,否则诸如“第一”和“第二”的术语用于在此类术语所描述的元素之间进行任意区分。因此,这些术语不一定旨在指示此类元素的时间或其他优先级。在相互不同的权利要求中列举某些措施的简单事实不指示这些措施的组合不能用于发挥优势。

[0132]

参考文献

[0133]

[1]“第三代合作伙伴项目;技术规范组无线电接入网络;nr;复用和信道编码(第15版)”,3gpp ts 38.212v15.2.0,2018年6月。(

″

3rd generation partnership project;technical specification group radio access network;nr;multiplexing and channel coding(release 15)

″

,3gpp ts 38.212v15.2.0,june2018.)

[0134]

[2]诺基亚,阿尔卡特朗讯上海贝尔,“rl-1703497极地设计的crc分布详情”,3gpp tsg-ran wg1会议#88,希腊雅典,2017年2月(nokia,alcatel-lucent shanghai bell,

″

rl-1703497details of crc distribution of polar design

″

,3gpp tsg-ran wg1 meeting#88,athens,greece,february 2017)。

[0135]

[3]英特尔,“使用pclmulqdq指令对泛型多项式进行快速crc计算”,2009年12月(intel,

″

fast crc computation for generic polynomials using pclmulqdq instruction

″

,december 2009)。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。