1.本发明涉及半导体装置。

背景技术:

2.在移动体通信、卫星通信等所使用的电子设备中组入有使高频信号的发送接收功能一体化的rf前端模块。rf前端模块具备具有高频放大功能的单片微波集成电路元件(mmic)、控制高频放大电路的控制ic、开关 ic以及双工器等。

3.在下述的专利文献1中公开在mmic之上层叠控制ic而实现了小型化的结构。专利文献1所公开的模块包括搭载在模块基板之上的mmic、和层叠于其上的控制ic。mmic的电极、控制ic的电极以及模块基板上的电极通过引线接合电连接。

4.专利文献1:美国专利申请公开第2015/0303971号说明书

5.高频放大电路例如使用异质结双极晶体管(hbt)。hbt由于在动作中产生集电极损耗而发热。发热所引起的hbt的温度上升向使集电极电流进一步增大的方向进行作用。若满足该正反馈的条件,则导致hbt热失控。为了避免hbt的热失控,限制hbt的输出电力的上限值。

6.为了实现高频放大电路的高输出化,期望使从构成mmic的hbt等半导体元件的散热特性提高。在专利文献1所公开的模块结构中,难以满足近年来的对高频放大电路的高输出化的要求。

技术实现要素:

7.本发明的目的在于提供能够使从半导体元件的散热特性提高的半导体装置。

8.根据本发明的一观点,提供一种半导体装置,具备:

9.第一部件,包括第一电子电路,上述第一电子电路的一部分由配置在表层部的单体半导体系的半导体元件构成;

10.至少一个第一导体突起,设置于上述第一部件的一个面,与上述第一电子电路连接;

11.第二部件,与上述第一部件的设置有上述第一导体突起的面接合,在俯视时比上述第一部件小,包括第二电子电路,上述第二电子电路的一部分由化合物半导体系的半导体元件构成;以及

12.至少一个第二导体突起,设置于上述第二部件,与上述第二电子电路连接,与上述第一导体突起向同一方向突出,

13.上述第二电子电路包括后级放大电路,

14.上述第一电子电路以及上述第二电子电路中的一方包括前级放大电路,由上述前级放大电路放大后的高频信号输入到上述后级放大电路,

15.上述第一电子电路包括:

16.第一开关,使输入到从多个接点中选择的一个接点的高频信号输入到上述前级放

大电路;

17.控制电路,控制上述前级放大电路以及上述后级放大电路的动作;以及

18.第二开关,使从上述后级放大电路输出的高频信号从自多个接点中选择的一个接点输出。

19.在第二部件的半导体元件产生的热通过第二导体突起进行传导并且也传导至第一部件。由于热从第二部件向第二导体突起侧和第一部件侧两个方向传导,所以能够得到从第二部件的散热特性提高这样的优异的效果。一般而言,形成单体半导体系的半导体元件的第一部件的主要材料具有比形成化合物半导体系的半导体元件的第二部件的主要材料高的导热率。因此,从第二部件传导至第一部件的热在比第二部件大的第一部件内扩散。在第一部件内扩散的热散热到外部。因此,能够得到从第二部件的散热特性进一步提高这样的优异的效果。

附图说明

20.图1是搭载有第一实施例的半导体装置的高频模块的示意俯视图。

21.图2a是图1的单点划线2a-2a处的剖视图,图2b是放大了半导体装置及其周边部分的剖视图。

22.图3是放大了第二部件所包括的半导体元件之一的剖视图。

23.图4是第一实施例的半导体装置的剖视图。

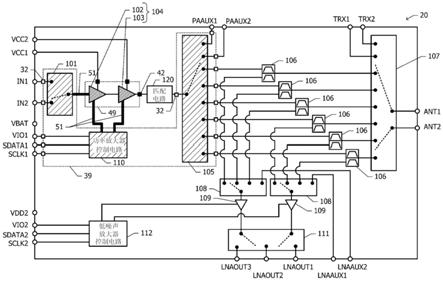

24.图5是表示搭载第一实施例的半导体装置的高频模块的电路构成的框图。

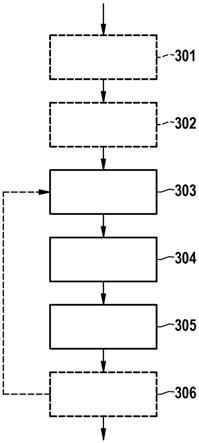

25.图6a~图6f的附图是半导体装置的制造中途阶段的示意剖视图。

26.图7a以及图7b是半导体装置的制造中途阶段的示意剖视图,图7c 是完成后的半导体装置的示意剖视图。

27.图8是将搭载有第一实施例的半导体装置的高频模块安装于母板的状态的剖视图。

28.图9是表示搭载有第一实施例的变形例的半导体装置的高频模块的电路构成的框图。

29.图10是表示搭载有第一实施例的其它的变形例的半导体装置的高频模块的电路构成的框图。

30.图11是表示搭载有第二实施例的半导体装置的高频模块的电路构成的框图。

31.图12是表示搭载有第三实施例的半导体装置的高频模块的电路构成的框图。

32.图13是表示搭载有第四实施例的半导体装置的高频模块的电路构成的框图。

33.图14是表示搭载有第五实施例的半导体装置的高频模块的电路构成的框图。

34.图15是表示搭载有第五实施例的变形例的半导体装置的高频模块的电路构成的框图。

35.图16是表示搭载有第五实施例的其它的变形例的半导体装置的高频模块的电路构成的框图。

36.图17是表示搭载有第五实施例的另外的其它的变形例的半导体装置的高频模块的电路构成的框图。

37.图18是表示第六实施例的半导体装置的电路构成的框图。

38.附图标记说明:20

…

高频模块,21

…

模块基板,22

…

半导体装置,23

…

表面安装部件,24

…

焊盘,25

…

焊料,26

…

接地平面,27

…

连接端子,28

…

导通孔,30

…

第一部件,30l

…

下表面,30u

…

顶面,31

…

衬垫,32

…

第一导体突起,33

…

基板,34

…

多层布线结构,34l

…

内层焊盘,34p

…

衬垫, 34v

…

导通孔,34w

…

布线,35

…

半导体元件,36

…

无源元件,39

…

第一电子电路,40

…

第二部件,41

…

衬垫,42

…

第二导体突起,44

…

半导体薄膜,44a

…

子集电极层,44b

…

元件分离区域,45

…

半导体元件,45b

…

基极层,45bm

…

基极台面,45c

…

集电极层,45e

…

发射极层,45em

…

发射极台面,45p

…

盖层,45t

…

接触层,46

…

发射极电极,46a

…

合金化区域,46b

…

基极电极,46c

…

集电极电极,46e

…

发射极电极,47c

…

集电极布线,47e

…

发射极布线,48a

…

衬垫,48e

…

发射极布线,49

…

第二电子电路,50

…

层间绝缘膜,51

…

部件间连接布线,52

…

保护膜,52a

…

开口,53

…

焊料,80

…

密封材料,81

…

金属膜,83

…

母板,84

…

焊盘,85

…

焊料,91

…

第一导热路径,92

…

第二导热路径,101

…

输入开关(第一开关),102

…

前级放大电路,103

…

后级放大电路,104

…

功率放大器,105

…

发送用的频段选择开关(第二开关),106

…

双工器,107

…

天线开关(第四开关),108

…

接收用的频段选择开关(第五开关),109

…

低噪声放大器, 110

…

功率放大器控制电路,111

…

接收用的输出端子选择开关(第六开关),112

…

低噪声放大器控制电路,115

…

发送接收切换开关(第三开关), 116

…

带通滤波器,120

…

发送侧匹配电路,121

…

接收侧匹配电路,200

…

母基板,201

…

剥离层,202

…

元件形成层,203

…

保护膜,204

…

连结支承体。

具体实施方式

39.[第一实施例]

[0040]

参照图1~图8的附图,对第一实施例的半导体装置进行说明。

[0041]

图1是搭载有第一实施例的半导体装置22的高频模块20的示意俯视图。在模块基板21安装有半导体装置22、低噪声放大器109、天线开关 (第四开关)107、以及其它的多个表面安装部件23。低噪声放大器109、天线开关107由单体半导体系、例如硅系或者锗系的集成电路元件构成。表面安装部件23例如是电感器、电容器、电阻元件等无源部件。半导体装置22包括第一部件30、和与第一部件30的下表面(朝向模块基板21 一方的面)接合的第二部件40。在俯视时,第二部件40比第一部件30 小,包含于第一部件30。例如,第一部件30由单体半导体系构成,第二部件40由化合物半导体构成。

[0042]

图2a是图1的单点划线2a-2a处的剖视图,图2b是放大了半导体装置22及其周边部分的剖视图。此外,图2a示出高频模块20安装于母板83的状态。

[0043]

首先,参照图2b对半导体装置22的构成进行说明。半导体装置22 包括板状的第一部件30、以及与第一部件30接合的膜状的第二部件40。将第一部件30的与厚度方向正交的两个面中的与模块基板21对置的面称为下表面30l,将与下表面朝向相反方向的面称为顶面30u。第二部件40 与第一部件30的下表面30l接合,与第一部件30热耦合。第二部件40 在内部包括多个半导体元件45。多个半导体元件45分别为化合物半导体系的元件,例如是hbt。

[0044]

在第一部件30的下表面30l中的不与第二部件40重叠的区域配置有多个衬垫31。在多个衬垫31之上(与下表面30l朝向同一方向的面)分别配置有第一导体突起32。另外,在第二部件40的与模块基板21对置的面(与第一部件30的下表面30l朝向同一方向的面)配置

有多个衬垫 41。在多个衬垫41各自之上配置有第二导体突起42。设置于第一部件30 的第一导体突起32、和设置于第二部件40的第二导体突起42从第一部件30或者第二部件40朝向同一方向突出。第二导体突起42中的至少一个在俯视时与多个半导体元件45重叠。

[0045]

在模块基板21的上表面配置有多个焊盘24。第一部件30的第一导体突起32以及第二部件40的第二导体突起42分别通过焊料25与模块基板21的焊盘24连接。这样,包括第一部件30以及第二部件40的半导体装置22通过倒装焊接安装于模块基板21。

[0046]

如图2a所示,在模块基板21,除了半导体装置22之外还安装有多个表面安装部件23。在模块基板21的内层配置有至少一层接地平面26。第二部件40的第二导体突起42(图2b)中的俯视时与半导体元件45重叠的导体突起经由焊料25(图2b)、焊盘24(图2b)以及模块基板21 内的导通孔28与接地平面26电连接并且热耦合。

[0047]

在模块基板21的下表面(与安装有半导体装置22的面相反侧的面) 配置有多个连接端子27。至少一个连接端子27经由导通孔28与接地平面26连接。

[0048]

模块基板21的上表面、安装于模块基板21的半导体装置22以及多个表面安装部件23被密封材料80覆盖。将密封材料80的表面中的与第一部件30的顶面朝向同一方向的面称为顶面,将从顶面的边缘到达模块基板21的面称为侧面。密封材料80的侧面与模块基板21的侧面无阶梯差地连续。

[0049]

密封材料80的顶面和侧面、以及模块基板21的侧面被金属膜81覆盖。作为金属膜81,例如能够使用cu、al等,例如能够通过溅射等来成膜。金属膜81在模块基板21的侧面与接地平面26连接。金属膜81作为将由安装于模块基板21的半导体装置22以及多个表面安装部件23构成的电子电路从外界电磁屏蔽的屏蔽膜发挥作用。

[0050]

在母板83的上表面配置有多个焊盘84。通过分别通过焊料85将模块基板21的多个连接端子27与母板83的焊盘84连接,从而高频模块 20安装于母板83。

[0051]

图3是放大了第二部件40所包括的半导体元件45之一的剖视图。第二部件40包括半导体薄膜44、半导体元件45、各种电极以及布线。半导体薄膜44与第一部件30(图2b)接合。图3所示的剖视图相对于图2a 以及图2b所示的剖视图上下反转。在图3的说明中,将相当于图2a以及图2b中下侧的一侧称为上侧。

[0052]

半导体薄膜44由化合物半导体、例如gaas形成,被划分为n型导电性的子集电极层44a和绝缘性的元件分离区域44b。半导体元件45形成在子集电极层44a之上。

[0053]

半导体元件45包括形成在子集电极层44a之上的基极台面45bm、和形成于基极台面45bm的上表面的一部分的区域的发射极台面45em。基极台面45bm包括从子集电极层44a依次层叠的集电极层45c、基极层 45b以及发射极层45e。即,从接近第一部件30(图4)的一侧起依次层叠集电极层45c、基极层45b以及发射极层45e。发射极台面45em包括盖层45p和配置在其上的接触层45t。

[0054]

作为一个例子,集电极层45c由n型gaas形成,基极层45b由p 型gaas形成,发射极层45e由n型ingap形成。盖层45p由n型gaas 形成,接触层45t由n型ingaas形成。由基极台面45bm以及发射极台面45em构成的半导体元件45是hbt。在半导体元件45的动作中,主要在发射极台面45em的正下方的集电极层45c产生发热。

[0055]

在子集电极层44a中的未配置基极台面45bm的区域之上配置有集电极电极46c。在集电极电极46c之上配置有第一层的集电极布线47c。在图3中,对布线层间的层间绝缘膜的

具体结构省略记载。集电极布线 47c经由集电极电极46c以及子集电极层44a与集电极层45c电连接。

[0056]

在发射极层45e中的未配置发射极台面45em的区域之上配置有基极电极46b。基极电极46b经由在厚度方向贯通发射极层45e并到达基极层 45b的合金化区域46a与基极层45b电连接。

[0057]

在发射极台面45em之上配置有发射极电极46e。发射极电极46经由接触层45t以及盖层45p与发射极层45e电连接。位于发射极台面45em 的正下方的发射极层45e实际作为发射极区域发挥作用。

[0058]

在发射极电极46e之上配置有第一层的发射极布线47e,在其上配置有第二层的发射极布线48e。第二层的发射极布线48e经由第一层的发射极布线47e与发射极电极46e电连接。在第二层的发射极布线48e之上配置有至少一个衬垫41(图2b)。该衬垫41与半导体元件45的发射极层 45e电连接。

[0059]

图4是第一实施例的半导体装置22的剖视图。首先,对第一部件30 的构成进行说明。

[0060]

第一部件30包括基板33以及配置在其上(在图4中是朝向下侧的面之上)的多层布线结构34。作为基板33,例如使用绝缘体上硅(soi)基板。此外,也可以使用通常的硅基板等作为基板33。在从基板33观察时,在下表面30l侧配置有多层布线结构34。在基板33的表层部形成有多个硅系的半导体元件35等。通过多个半导体元件35,例如构成cmos电路等。

[0061]

多层布线结构34包括多个布线34w、多个内层焊盘34l、将层间连接的多个导通孔34v、以及配置在下表面侧的多个衬垫34p。在图4中,对多层布线结构34内的多个层间绝缘膜的构成省略记载。在基板33的朝向下方的面或者多层布线结构34的内层配置有多个无源元件36。通过半导体元件35、无源元件36、以及多层布线结构34内的布线34w、导通孔 34v、内层焊盘34l等构成第一电子电路39。即,第一部件30包括第一电子电路39。多个衬垫34p与第一电子电路39连接。

[0062]

在第一部件30的下表面30l的一部分区域接合第二部件40。通过第二部件40所包括的多个半导体元件45构成第二电子电路49。即,第二部件40包括第二电子电路49。第二部件40包括配置在朝向下方的面的发射极布线48e(图3)以及衬垫48a。

[0063]

在第一部件30以及第二部件40之上(图4中下侧)经由层间绝缘膜配置有再布线层。对再布线层与第一部件30以及第二部件40之间的层间绝缘膜的构成省略记载。再布线层包括分别由金属图案构成的多个衬垫 31、衬垫41以及部件间连接布线51。部件间连接布线51将第一部件30 所包括的第一电子电路39与第二部件40所包括的第二电子电路49连接。

[0064]

保护膜52覆盖再布线层所包括的多个衬垫31、衬垫41以及部件间连接布线51。在保护膜52设置有在俯视时分别包含于多个衬垫31以及衬垫41的多个开口52a。在多个衬垫41之上分别配置有第二导体突起42,在多个衬垫31之上分别配置有第一导体突起32。第一导体突起32、第二导体突起42从保护膜52的下表面朝向下方突出。在这些第一导体突起 32、第二导体突起42各自的朝向下方的面放置焊料53。例如,使用cu 作为第一导体突起32以及第二导体突起42。该情况下,第一导体突起32 及其上的焊料53、以及第二导体突起42及其上的焊料53分别被称为cu 柱凸块。

[0065]

图5是表示搭载第一实施例的半导体装置22(图4)的高频模块20 的电路构成的框图。高频模块20包括:输入开关(第一开关)101、功率放大器104、发送用的频段选择开关(第二开关)105、多个双工器106、天线开关(第四开关)107、两个接收用的频段选择开关(第五开关)108、两个低噪声放大器109、功率放大器控制电路110、接收用的输出端子选择开关(第六开关)111、以及低噪声放大器控制电路112。功率放大器 104包括前级放大电路102以及后级放大电路103。该高频模块20具有进行频分复用(fdd)方式的发送接收的功能。功率放大器104可以是一个或者多个。也可以在功率放大器104除了102和103之外还包括pa而成为三级以上的构成。

[0066]

功率放大器104的前级放大电路102以及后级放大电路103包括于第二部件40(图4)的第二电子电路49。输入开关101、频段选择开关105 以及功率放大器控制电路110包括于第一部件30(图4)的第一电子电路 39。其它的功能通过安装于模块基板21(图2a)的电子部件实现。在图 5中,对第一电子电路39所包括的电子部件附加相对较淡的影线,对第二电子电路49所包括的电子部件附加相对较浓的影线。此外,在后述的图9~图18的框图中,也对第一电子电路39所包括的电子部件以及第二电子电路49所包括的电子部件附加相同的影线。

[0067]

接下来,对高频模块20的构成以及功能进行说明。

[0068]

输入开关101的两个输入侧的接点分别经由设置于第一部件30的第一导体突起32(图2b)与模块基板21的高频信号输入端子in1、in2连接。在图5中,以空心的正方形示出第一导体突起32。从两个高频信号输入端子in1、in2输入高频信号。输入开关101从输入侧的两个接点中选择一个接点,使输入到所选择的接点的高频信号输入到前级放大电路 102。对输入开关101与前级放大电路102的输入端口之间的连接使用部件间连接布线51(图4)。在图5中,以相对较粗的实线示出通过部件间连接布线51连接的位置。此外,在后述的图9~图18的框图中,也以相对较粗的实线示出部件间连接布线51。

[0069]

由前级放大电路102放大后的高频信号输入到后级放大电路103。由后级放大电路103放大后的高频信号通过发送侧匹配电路120输入到频段选择开关105的一个输入侧的接点。后级放大电路103的输出端口与发送侧匹配电路120经由设置于第二部件40的第二导体突起42(图2b)连接。在图5中,以涂黑的正方形示出第二导体突起42。发送侧匹配电路120 与频段选择开关105的输入侧的接点经由第一导体突起32连接。频段选择开关105从多个输出侧的接点选择一个接点,并使由后级放大电路103 放大后的高频信号从所选择的接点输出。

[0070]

频段选择开关105的输出侧的多个接点中的两个接点分别经由第一导体突起32(图2b)与辅助输出端子paaux1、paaux2连接。其它的六个接点分别经由第一导体突起32(图2b)与按照各频段准备的多个双工器106的发送用输入端口连接。频段选择开关105具有从按照各频段准备的多个双工器106中选择一个双工器106的功能。

[0071]

天线开关107具有电路侧的多个接点和天线侧的两个接点。天线开关 107的多个电路侧的接点中的两个接点分别与发送信号输入端子trx1、 trx2连接。电路侧的其它的六个接点分别与多个双工器106的输入输出共用端口连接。天线侧的两个接点分别与天线端子ant1、ant2连接。在天线端子ant1、ant2分别连接天线。此外,虽然在实施例中,示出天线端子为两个的情况,但也可以是天线端子为三个以上的构成。

[0072]

天线开关107分别将两个天线侧的接点与从电路侧的多个接点中选择的两个接点连接。在使用一个频段进行通信的情况下,天线开关107将电路侧的一个接点与天线侧的一个接点连接。由功率放大器104放大并通过了对应的频段用的双工器106的高频信号从选择的天线侧的接点所连接的天线发送。

[0073]

两个接收用的频段选择开关108分别具有输入侧的四个接点。两个频段选择开关108各自的输入侧的四个接点中的三个接点分别与双工器106 的接收用输出端口连接。两个频段选择开关108各自的剩余的一个接点分别与辅助输入端子lnaaux1、lnaaux2连接。

[0074]

与两个接收用的频段选择开关108对应地准备两个低噪声放大器 109。两个接收用的频段选择开关108分别使通过了双工器106的接收信号输入到对应的低噪声放大器109。lna的数目可以是一个,也可以为三个以上。

[0075]

输出端子选择开关111的两个电路侧的接点分别与两个低噪声放大器 109的输出端口连接。输出端子选择开关111的三个端子侧的接点分别与接收信号输出端子lnaout1、lnaout2、lnaout3连接。由低噪声放大器109放大后的接收信号从由输出端子选择开关111选择的接收信号输出端子输出。此外,虽然在本实施例中,是接收信号输出端子为三个的构成,但也可以为四个以上。

[0076]

分别从电源端子vcc1、vcc2对前级放大电路102以及后级放大电路103施加电源电压。电源端子vcc1、vcc2经由设置于第二部件40 的第二导体突起42(图2b)与功率放大器104连接。设置于第二部件40 的第二导体突起42中的至少一个与模块基板21的接地平面26(图2a) 连接,但在图5未示出。

[0077]

功率放大器控制电路110经由设置于第一部件30的第一导体突起32 (图2b)与电源端子vio1、控制信号端子sdata1以及时钟端子sclk1 连接。功率放大器控制电路110基于给予到控制信号端子sdata1的控制信号来控制功率放大器104。功率放大器控制电路110与功率放大器104 的连接使用部件间连接布线51(图4)。

[0078]

低噪声放大器控制电路112与电源端子vio2、控制信号端子sdata2 以及时钟端子sclk2连接。低噪声放大器控制电路112基于给予到控制信号端子sdata2的控制信号来控制低噪声放大器109。

[0079]

在模块基板21还设置有电源端子vbat以及漏极电压端子vdd2。从电源端子vbat向功率放大器104的偏置电路以及功率放大器控制电路110供给电源。从漏极电压端子vdd2对安装于模块基板21的低噪声放大器控制电路112、低噪声放大器109等施加电源电压。

[0080]

接下来,参照图6a~图7c的附图,对半导体装置22(图4)的制造方法进行说明。图6a~图7b的附图是半导体装置22的制造中途阶段的示意剖视图,图7c是完成后的半导体装置22的示意剖视图。

[0081]

如图6a所示,使剥离层201在gaas等化合物半导体的单结晶的母基板200之上外延生长,并在剥离层201之上形成元件形成层202。在元件形成层202形成有包括图3所示的半导体元件45、发射极电极46e、集电极电极46c、基极电极46b、发射极布线47e、集电极布线47c、第二层的发射极布线48e等的元件结构。通过一般的半导体工序形成这些元件结构。在图6a中,对形成于元件形成层202的元件结构省略记载。在该阶段,在元件形成层202形成相当于多个第二部件40(图2a)的元件结构,不分离为各个第二部件40。在元件形成层202之上形成绝缘性的保护膜203。

[0082]

接下来,如图6b所示,将抗蚀剂图案(未图示)作为蚀刻掩模,对保护膜203、元件形成层202以及剥离层201进行图案化。在该阶段,元件形成层202被分离为各个第二部件40(图2a)。

[0083]

接下来,如图6c所示,在分离的保护膜203之上粘贴连结支承体204。由此,多个保护膜203经由连结支承体204相互连结。此外,也可以使在图6b的图案化工序中作为蚀刻掩模而使用的抗蚀剂图案残留,使保护膜 203与连结支承体204之间夹有抗蚀剂图案。

[0084]

接下来,如图6d所示,针对母基板200以及元件形成层202选择性地蚀刻剥离层201。由此,元件形成层202、保护膜203以及连结支承体 204从母基板200剥离。为了选择性地蚀刻剥离层201,使用蚀刻耐性与母基板200以及元件形成层202中的任何一个都不同的化合物半导体作为剥离层201。

[0085]

接下来,如图6e所示,将元件形成层202与第一部件30接合。在该阶段,第一部件30未分离为图2a以及图2b所示那样的单片,一个晶圆包括多个第一部件30。另外,在第一部件30形成有图4所示的第一电子电路39、多层布线结构34,但在图6e中,省略这些结构的图示。

[0086]

元件形成层202与第一部件30的接合基于范德华键或者氢键。除此之外,也可以通过静电力、共价键、共晶合金键等将元件形成层202与第一部件30接合。例如,也可以在第一部件30的表面的一部分区域形成 au膜,使元件形成层202与au膜紧贴并进行加压,由此来将两者接合。

[0087]

接下来,如图6f所示,从保护膜203剥离连结支承体204。利用到此为止的工序,得到在包括多个第一部件30的晶圆之上接合了单片化的第二部件40的结构。

[0088]

在剥离了连结支承体204之后,如图7a所示,在第一部件30以及第二部件40之上形成层间绝缘膜50以及再布线层。在再布线层包括有从配置在第二部件40之上的衬垫41、第二部件40之上起与第二部件40的边缘交叉并延伸到第一部件30之上的部件间连接布线51(图4)等。此外,虽然在图7a中未显现,但在再布线层也包括有配置在第一部件30 之上的衬垫31(图4)。

[0089]

接下来,如图7b所示,在再布线层之上形成保护膜52,在保护膜52 形成多个开口52a。多个开口52a分别在俯视时包含于衬垫41、衬垫31 (图4)。在开口52a内以及保护膜52之上形成第二导体突起42以及第一导体突起32(图4)。并且,在第一导体突起32以及第二导体突起42 的顶面放置焊料53并进行回流处理。

[0090]

最后,如图7c所示,对包括多个第一部件30的晶圆进行切割。由此,得到包括第一部件30、第二部件40、其上的再布线层、以及第二导体突起42、第一导体突起32(图4)等的单片化的半导体装置22。

[0091]

接下来,参照图8对第一实施例的优异的效果进行说明。

[0092]

图8是将搭载有第一实施例的半导体装置22的高频模块20安装于母板83的状态的剖视图。形成在第二部件40的半导体元件45(图2b)产生的热通过设置于第二部件40的第二导体突起42(图2b)到达模块基板 21的第一导热路径91、和经由第一部件30与第二部件40的接合面到达第一部件30的第二导热路径92。

[0093]

传导到第一部件30的热在第一部件30内扩散。一般而言,形成硅系的半导体元件35(图4)的基板33的主要材料的导热率比形成化合物半导体系的半导体元件45的第二部件40的主要材料的导热率高。因此,传导到第一部件30的热容易在第一部件30内扩散。扩散到

第一部件30内的热通过密封材料80传导至金属膜81。扩散到第一部件30内的热主要从第一部件30的顶面传导至其正上方的金属膜81。

[0094]

金属膜81的导热率比一般使用树脂等的密封材料80的导热率大。因此,通过第二导热路径92到达金属膜81的热通过覆盖密封材料80的顶面的金属膜81传导至覆盖密封材料80以及模块基板21的侧面的金属膜 81。从金属膜81的大致整个区域向外界进行散热,所以能够提高通过第二导热路径92传导至金属膜81的热的散热效率。

[0095]

像这样,在第二部件40的半导体元件45产生的热通过从第二部件 40观察时朝向下方的第一导热路径91、和朝向上方的第二导热路径92双方进行散热。因此,能够抑制半导体元件45的温度上升。

[0096]

gaas等化合物半导体的电子迁移率比硅的电子迁移率高。利用由在由化合物半导体构成的半导体薄膜44(图3)之上外延生长的化合物半导体层形成的半导体元件45构成功率放大器104,由此能够提高功率放大器104的动作频率。

[0097]

另外,在第一实施例中,使第二部件40在从外延生长用的母基板200 (图6d)剥离的状态下与第一部件30粘贴,所以与将第二部件40和母基板200一起与第一部件30粘贴的结构相比能够减小厚度方向的尺寸。例如,从母基板200剥离的第二部件40的厚度至多为数μm。由于第二部件40足够薄,所以能够在将第二部件40粘贴于第一部件30的状态下,使用半导体工序在两者的下表面之上形成再布线层。因此,与通过引线接合连接第一部件30所包括的第一电子电路39和第二部件40所包括的第二电子电路49的构成相比,能够实现布线的微细化、低成本化。

[0098]

在分别将包括第二电子电路49(图4)的mmic、和包括第一电子电路39(图4)的第一部件30安装于模块基板的不同的位置的情况下,必须利用模块基板上的布线连接第一电子电路39与第二电子电路49。在第一实施例中,利用配置于再布线层的部件间连接布线51(图4)连接第一电子电路39和第二电子电路49,所以能够缩短连接两者的布线的长度。由此,能够使高频信号的传输损耗降低。并且,能够实现高频模块20的小型化。

[0099]

接下来,参照图9以及图10,对第一实施例的变形例进行说明。

[0100]

图9以及图10分别是表示搭载有第一实施例的两个变形例的半导体装置22的高频模块20的电路构成的框图。

[0101]

在第一实施例(图5)中,输入开关101、频段选择开关105以及功率放大器控制电路110包括于第一部件30的第一电子电路39(图4),但在图9所示的变形例中,仅功率放大器控制电路110包括于第一电子电路39,输入开关101以及频段选择开关105与半导体装置22分开地安装于模块基板21(图2a)。

[0102]

输入开关101与前级放大电路102之间经由设置于第二部件40的第二导体突起42连接。发送侧匹配电路120与频段选择开关105经由模块基板21(图2a)内的布线连接。

[0103]

在图10所示的变形例中,输入开关101以及功率放大器控制电路110 包括于第一部件30(图4)的第一电子电路39,频段选择开关105与半导体装置22分开地安装于模块基板21(图2a)。后级放大电路103和发送侧匹配电路120与图9所示的变形例相同,经由模块基板21(图2a) 内的布线连接。

[0104]

接下来,对第一实施例的其它的变形例进行说明。

[0105]

搭载有第一实施例的半导体装置22的高频模块20具备六个双工器 106(图5),但

双工器106的个数并不限定于六个,也可以具备其它个数的双工器106。另外,接收信号输出端子lnaout1、lnaout2、lnaout3 (图5)等接收信号输出端子的个数并不限定于三个。天线端子ant1、 ant2等天线端子的个数并不限定于两个。也可以省略辅助输出端子 paaux1、paaux2、发送信号输入端子trx1、trx2、辅助输入端子 lnaaux1、lnaaux2中的任意一个端子,也可以增加这些端子的个数。

[0106]

如图9以及图10所示的变形例那样,也可以将输入开关101以及频段选择开关105中的至少一方与半导体装置22分开地安装于模块基板21。相反,也可以使天线开关107、接收用的频段选择开关108、低噪声放大器109、输出端子选择开关111、低噪声放大器控制电路112中的至少一个包括于第一电子电路39。

[0107]

虽然在第一实施例中,使用gaas作为第二部件40的半导体薄膜44 (图3),但也可以使用其它的化合物半导体。作为用于半导体薄膜44的化合物半导体,例如能够列举alas、inas、inp、gap、insb、gan、inn、 aln、sige、sic、ga2o3、gabi或者包括这些材料的元素的混晶半导体材料等。另外,虽然在第一实施例中,采用硅系的半导体元件作为形成于第一部件30的半导体元件35(图4),但也可以采用其它的单体半导体系、例如锗系的半导体元件。

[0108]

在第一实施例中,作为用于将半导体装置22安装于模块基板21的电极,使用第一导体突起32及其上的焊料53、以及第二导体突起42及其上的焊料53等,但也可以使用其它各种的导体突起。例如,作为外部连接用的导体突起,也可以使用由导体构成的柱、支柱,或者球凸块等。

[0109]

[第二实施例]

[0110]

接下来,参照图11对第二实施例的半导体装置进行说明。以下,对与参照图1~图8的附图进行了说明的第一实施例的半导体装置相同的构成省略说明。

[0111]

图11是表示搭载有第二实施例的半导体装置22(图4)的高频模块 20的电路构成的框图。在第一实施例中,在模块基板21搭载有两个接收用的频段选择开关108以及两个低噪声放大器109(图5)。与此相对,在第二实施例中,搭载有一个接收用的频段选择开关108和一个低噪声放大器109。

[0112]

频段选择开关108在输入侧具有八个接点。八个接点中的六个接点分别与六个双工器106的接收用输出端口连接。剩余的两个接点分别与辅助输入端子lnaaux1、lnaaux2连接。频段选择开关108使输入到从输入侧的八个接点中选择的一个接点的接收信号输入到低噪声放大器109。

[0113]

输出端子选择开关111的电路侧的接点与低噪声放大器109连接。由低噪声放大器109放大后的接收信号从由输出端子选择开关111自三个接收信号输出端子lnaout1、lnaout2、lnaout3中选择的一个端子输出。

[0114]

接下来,对第二实施例的优异的效果进行说明。

[0115]

在第二实施例中,也与第一实施例相同,能够使从第二部件40的半导体元件45(图4)的散热特性提高,并且实现高频模块20的小型化。第一实施例的高频模块20能够并行地处理两个频段的接收信号,但在不需要并行地处理两个频段的接收信号的功能的情况下,也可以采用第二实施例的构成。

[0116]

[第三实施例]

[0117]

接下来,参照图12对第三实施例的半导体装置进行说明。以下,对与参照图1~图8

的附图进行了说明的第一实施例的半导体装置相同的构成省略说明。

[0118]

图12是表示搭载有第三实施例的半导体装置的高频模块20的电路构成的框图。在第一实施例中,第二部件40的第二电子电路49(图4)包括一个功率放大器104(图5)。与此相对,在第三实施例中,第二电子电路49(图9)包括两个系统的功率放大器104。各个功率放大器104分别包括前级放大电路102以及后级放大电路103。

[0119]

另外,虽然在第一实施例中,输入开关101(图5)包括于第一部件 30的第一电子电路39(图4),但在第三实施例中,输入开关101与半导体装置22(图2a)独立地安装于模块基板21。

[0120]

输入开关101在电路侧具有两个接点。电路侧的两个接点分别经由设置于第二部件40的第二导体突起42与两个前级放大电路102连接。输入开关101对两个高频信号输入端子in1、in2与两个前级放大电路102的连接状态进行切换。即,输入到一个高频信号输入端子in1的高频信号输入到一个前级放大电路102,输入到另一个高频信号输入端子in2的高频信号输入到另一个前级放大电路102。

[0121]

发送用的频段选择开关105在输入侧具有两个接点。输入侧的两个接点分别经由两个发送侧匹配电路120与两个后级放大电路103连接。频段选择开关105将输入侧的一个接点与输出侧的多个接点中的一个接点连接,将输入侧的另一个接点与输出侧的多个接点中的其它的一个接点连接。

[0122]

从电源端子vcc1对两个前级放大电路102供给电源,从电源端子 vcc2对两个后级放大电路103供给电源。功率放大器控制电路110控制两个系统的功率放大器104。

[0123]

接下来,对第三实施例的优异的效果进行说明。

[0124]

在第三实施例中,也与第一实施例相同,能够使从第二部件40的半导体元件45(图4)的散热特性提高,并且实现高频模块20的小型化。并且,在第三实施例中,能够与同时发送两个频段的高频信号的载波聚合对应。

[0125]

接下来对第三实施例的变形例进行说明。

[0126]

在第三实施例中,将输入开关101与半导体装置22(图2a)分开地安装于模块基板21(图2a),但也可以与第一实施例相同地在第一部件 30(图4)的第一电子电路39包括输入开关101。

[0127]

[第四实施例]

[0128]

接下来,参照图13对第四实施例的半导体装置进行说明。以下,对与参照图1~图8的附图进行了说明的第一实施例的半导体装置相同的构成省略说明。

[0129]

图13是表示搭载有第四实施例的半导体装置22(图4)的高频模块 20的电路构成的框图。在第一实施例(图5)中,前级放大电路102包括于第二部件40(图4)的第二电子电路49。与此相对,在第四实施例中,前级放大电路102包括于第一部件30(图4)的第一电子电路39。前级放大电路102的输出端口与后级放大电路103的输入端口经由部件间连接布线51(图4)连接。

[0130]

从电源端子vcc1经由设置于第一部件30的第一导体突起32(图4) 对前级放大电路102供给电源。功率放大器控制电路110与前级放大电路 102经由配置在第一部件30的多层布线结构34内的布线34w(图4)连接。

[0131]

接下来,对第四实施例的优异的效果进行说明。在第四实施例中,也与第一实施例

相同,能够使从第二部件40的半导体元件45(图4)的散热特性提高,并且实现高频模块20的小型化。由于前级放大电路102与后级放大电路103相比输出功率较低,所以能够由硅系半导体元件实现。因此,能够使前级放大电路102包括于第一部件30(图4)的第一电子电路39。另外,通过使前级放大电路102包括于第一电子电路39,也能够得到前级放大电路102与输入开关101的相容性变好,改善噪声特性这样的效果。

[0132]

[第五实施例]

[0133]

接下来,参照图14对第五实施例的半导体装置进行说明。以下,对与参照图1~图8的附图进行了说明的第一实施例的半导体装置相同的构成省略说明。

[0134]

图14是表示搭载有第五实施例的半导体装置22(图4)的高频模块 20的电路构成的框图。第一实施例的高频模块20具有进行fdd方式的发送接收的功能。与此相对,第五实施例的高频模块20具有进行时分复用(tdd)方式的发送接收的功能。

[0135]

第五实施例的高频模块20具备对不同的频段的发送接收信号进行处理的两个系统的发送接收电路。两个发送接收电路分别包括功率放大器 104、发送侧匹配电路120、发送接收切换开关(第三开关)115、带通滤波器116、接收侧匹配电路121以及低噪声放大器109。功率放大器104 分别为前级放大电路102和后级放大电路103的两级结构。

[0136]

输入开关101的两个输入侧的接点分别与两个高频信号输入端子 in1、in2连接。输入开关101的两个输出侧的接点分别与两个前级放大电路102的输入端口连接。输入开关101切换两个高频信号输入端子in1、 in2与两个前级放大电路102之间的连接状态。

[0137]

后级放大电路103的输出端口经由发送侧匹配电路120与发送接收切换开关115的发送信号输入接点连接。发送接收切换开关115的接收信号输出接点经由接收侧匹配电路121与低噪声放大器109的输入端口连接。发送接收切换开关115还具有发送接收共用接点,通过选择性地将发送接收共用接点与发送信号输入接点以及接收信号输出接点中的一方连接,来切换发送和接收。

[0138]

两个发送接收切换开关115的发送接收共用接点分别经由带通滤波器116与天线开关107的电路侧的两个接点连接。天线开关107的两个天线侧的接点分别与天线端子ant1、ant2连接。

[0139]

连接两个低噪声放大器109与三个接收信号输出端子lnaout1、 lnaout2、lnaout3的输出端子选择开关111的构成与第一实施例的高频模块20的输出端子选择开关111的构成(图5)相同。

[0140]

输入开关101、两个前级放大电路102、功率放大器控制电路110、两个发送接收切换开关115包括于第一部件30(图4)的第一电子电路39。两个后级放大电路103包括于第二部件40(图4)的第二电子电路49。

[0141]

第一电子电路39与第二电子电路49经由形成于再布线层的部件间连接布线51(图4)连接。第一电子电路39与模块基板21(图4)上的电路经由设置于第一部件30的第一导体突起32(图2b)连接。第二电子电路49与模块基板21(图4)上的电路经由设置于第二部件40的第二导体突起42(图2b)连接。

[0142]

接下来,对第五实施例的优异的效果进行说明。

[0143]

在第五实施例中,也与第一实施例相同,能够使从第二部件40的半导体元件45(图4)的散热特性提高,并且实现高频模块20的小型化。

[0144]

接下来,参照图15、图16、图17对第五实施例的变形例的半导体装置进行说明。图15、图16、图17分别是表示搭载有第五实施例的变形例的半导体装置22的高频模块20的电路构成的框图。

[0145]

在图15所示的变形例中,第一部件30的第一电子电路39除了第五实施例的半导体装置22的第一电子电路39的构成之外,还包括两个带通滤波器116。例如,通过配置在第一部件30的基板33(图4)之上或者配置在多层布线结构34(图4)的内层的无源元件实现带通滤波器116。

[0146]

发送接收切换开关115的发送接收共用接点与带通滤波器116通过第一部件30的多层布线结构34(图4)内的布线34w等连接。带通滤波器 116与天线开关107的电路侧的接点经由设置于第一部件30的第一导体突起32(图2b)连接。

[0147]

在图16所示的变形例中,第一部件30的第一电子电路39除了图15 所示的变形例的半导体装置22的第一电子电路39的构成之外,还包括天线开关107。带通滤波器116与天线开关107的电路侧的接点通过第一部件30的多层布线结构34(图4)内的布线34w等连接。天线开关107的天线侧的接点经由设置于第一部件30的第一导体突起32(图2b)进行连接。

[0148]

在图17所示的变形例中,第一部件30的第一电子电路39除了图16 所示的变形例的半导体装置22的第一电子电路39的构成之外,还包括低噪声放大器控制电路112、两个低噪声放大器109、以及输出端子选择开关111。低噪声放大器109的输入端口与接收侧匹配电路121经由设置于第一部件30的第一导体突起32(图2b)连接。并且,输出端子选择开关 111的端子侧的接点与接收信号输出端子lnaout1、lnaout2、 lnaout3分别经由设置于第一部件30的第一导体突起32(图b)连接。低噪声放大器控制电路112经由设置于第一部件30的第一导体突起32(图 2b)与电源端子vio2、控制信号端子sdata2以及时钟端子sclk2连接。

[0149]

如图15、图16、图17所示的变形例那样,通过增加构成高频模块 20的多个电路部件中的构成包括于第一部件30的第一电子电路39的电路部件,能够减少应该安装于模块基板21(图2a)的部件件数。由此,能够实现高频模块20的小型化。

[0150]

[第六实施例]

[0151]

接下来,参照图18对第六实施例的半导体装置进行说明。以下,对与参照图14进行了说明的第五实施例的半导体装置相同的构成省略说明。

[0152]

图18是表示第六实施例的半导体装置22(图4)的电路构成的框图。搭载有第五实施例的半导体装置22的高频模块20具备两个系统的发送接收电路,但第六实施例的半导体装置22所具备的发送接收电路仅为一个系统。由于发送接收电路为一个系统,所以在第六实施例的半导体装置 22中不具备第五实施例的半导体装置22具备的输入开关101(图14)。

[0153]

除了功率放大器104的后级放大电路103以外的全部功能通过第一部件30所包括的第一电子电路39实现。即,第一电子电路39包括前级放大电路102、功率放大器控制电路110、低噪声放大器控制电路112、发送侧匹配电路120、接收侧匹配电路121、发送接收切换开关115、带通滤波器116、天线开关107、低噪声放大器109以及输出端子选择开关111。发送侧匹配电路120以及接收侧匹配电路121使用电容器、电感器等无源元件。

[0154]

由设置于第一部件30的第一导体突起32(图2b)构成用于将第一电子电路39与除第二部件40(图4)所包括的第二电子电路49以外的外部的电路连接的端子。由设置于第二部件40的第二导体突起42(图2b)构成后级放大电路103用的电源端子vcc2。

[0155]

接下来,对第六实施例的优异的效果进行说明。若使用第六实施例的半导体装置22,则为了构成高频模块20,不需要安装于模块基板21(图 2a)的表面安装部件23。即,能够以半导体装置22单体实现高频模块20。因此,能够进一步促进高频模块20的小型化。此外,也可以将第六实施例的半导体装置22安装于模块基板21。

[0156]

另外,在第六实施例的半导体装置22中,也形成使在第二部件40的半导体元件45产生的热通过第二导体突起42传导至下方的第一导热路径 91(图8)、和使其传导至第一部件30的第二导热路径92(图8)。因此,与第一实施例相同,能够使散热特性提高。

[0157]

接下来,对第六实施例的变形例进行说明。第六实施例的半导体装置 22具备一个系统的发送接收电路,但也可以如搭载有第五实施例的半导体装置22的高频模块20(图14)那样具备两个系统的发送接收电路,也可以具备三个系统以上的发送接收电路。该情况下,多个系统的发送接收电路分别包括的后级放大电路103以外的功能全部由第一电子电路39实现。在具备多个系统的发送接收电路的情况下,如第五实施例的半导体装置22(图14)那样,使第一电子电路39包括输入开关101即可。

[0158]

上述的各实施例为例示,当然能够进行不同的实施例所示的构成的部分的置换或者组合。并不对每个实施例依次提及多个实施例的相同的构成所带来的相同的作用效果。并且,本发明并不限定于上述的实施例。例如,本领域技术人员明确能够进行各种变更、改进、组合等。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。