1.本发明涉及半导体芯片制造领域,尤其涉及低漏电的齐纳二极管芯片及其制造方法。

背景技术:

2.齐纳二极管是由两边浓度极高的p /n 结构成,属于隧道击穿,i-v曲线击穿点较软,反向漏电较大。所以如果直接在很浓的n 衬底上直接注入p 来形成p /n 结,尽管电压可能会达到7.5v以内,但漏电会达到毫安级,基本上无法形成性能良好的二极管。

技术实现要素:

3.本发明的目的是为了克服目前技术中的缺陷,提出了解决7.5v以内低压齐纳二极管漏电偏大的技术方案,提出了一种制备低漏电齐纳二极管芯片的方法及其结构。

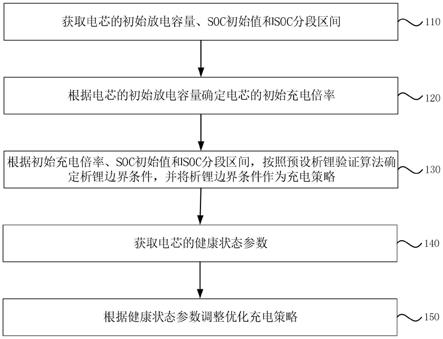

4.本发明提出的一种制备低漏电齐纳二极管芯片的方法及其结构包括如下步骤:

5.步骤1、在n 衬底上直接通过外延,形成n-外延层;

6.步骤2、再在n-外延层的有源区内通过注入磷,形成n 阱,其浓度比n 衬底淡,后续所形成的齐纳二极管的不同击穿电压(7.5v以内)主要通过n 阱的注入剂量来实现;

7.步骤3、n阱退火;

8.步骤4、通过光刻和刻蚀形成p-阱区域,其中p-阱面积大于n 阱面积,且覆盖其上。;

9.步骤5、p-阱退火;

10.步骤6、通过光刻和刻蚀形成p 主结区;

11.步骤7、p 主结区退火,形成欧姆接触;

12.步骤8、正面刻蚀接触孔,蒸发和反刻金属形成正面电极;

13.步骤9、背面减薄,蒸发金属做背面电极。

14.所述n 阱与p 主结之间形成的p n 结为单边突变结,所述齐纳二极管电压可以做到7.5v以内,以5.1v齐纳二极管为例,其漏电可以做到小于5.0μa@4.2v,片内电压均匀性在

±

2%以内。

附图说明

15.图1为本发明中所采用的n 衬底截面示意图;

16.图2为本发明中n 衬底上生长n-外延层后的截面示意图;

17.图3为本发明中在n-外延层的有源区内注入n 阱的截面示意图;

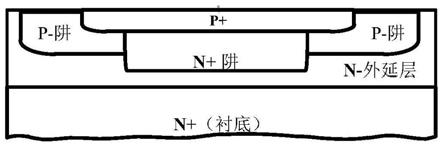

18.图4为本发明中在n-外延层的有源区内注入p-阱的截面示意图(其中p-阱面积大于n 阱面积,且覆盖其上);

19.图5为本发明中在n-外延层的有源区内注入p 主结的截面示意图。

具体实施方式

20.下面结合附图对本发明进一步描述,特别是以图2为例,具体实施方式如下:

21.本发明提出的一种制备低漏电齐纳二极管芯片的方法包括如下步骤:

22.步骤1、n 衬底电阻率约为0.002-0.010ω.cm,在1050℃条件下化学气相淀积生长厚度为5.0-10.0um,电阻率为0.5-3.0ω.cm的n-外延层。

23.步骤2、在n-外延层上通过光刻和刻蚀形成有源区,然后在有源区内注磷形成n 阱,n 阱的注入剂量视击穿电压而定,以5.1v的的低压齐纳二极管为例,剂量在1e14-3e14。

24.步骤3、n阱退火温度在1050℃-1150℃,时间1.5h-2.5h。

25.步骤4、通过光刻和刻蚀形成p-阱区域,p-阱剂量较淡,n 阱剂量是p-阱剂量的10-100倍,以5.1v的的低压齐纳二极管为例,p-剂量在1e12-3e13。同时p-阱面积大于n 阱面积,且覆盖其上。

26.步骤5、p-阱退火温度在1000℃-1050℃左右,时间1.5h-2.5h。

27.步骤6、通过光刻和刻蚀形成p 主结区,p 主结区注入剂量在2e15-1e16范围。

28.步骤7、p 主结区退火温度850℃-950℃左右,时间1h-2h。

29.步骤8、刻蚀接触孔,蒸发或溅射金属做正面电极;

30.步骤9、背面减薄到150μm,蒸发金属做背面电极,至此低漏电的齐纳二极管基本形成。本发明提出的一种制备低漏电齐纳二极管器件的结构是:

31.(1)、在n 衬底上直接通过外延,形成n-外延层。

32.(2)、再在n-外延层的有源区内通过注入磷,形成n 阱,其浓度比p 衬底淡,后续形成的齐纳二极管不同电压主要通过n 阱的浓度来实现。

33.(3)、加入了p-阱结构,n 阱剂量是p-阱剂量的10-100倍,以5.1v的的低压齐纳二极管为例,p-剂量在1e12-3e13。同时p-阱面积大于n 阱面积,且覆盖其上。以保证p /n 击主结穿都在底部的平面上,从而确保片内电压均匀性。同时形成的漏电可以控制到较小范围。

技术特征:

1.一种制备低漏电齐纳二极管芯片的方法,其特征在于,所述的方法包括如下步骤:步骤1、在n 衬底上直接通过外延,形成n-外延层;步骤2、再在n-外延层的有源区内通过注入磷,形成n 阱,其浓度比n 衬底淡,后续所形成的齐纳二极管的不同击穿电压(7.5v以内)主要通过n 阱的注入剂量来实现;步骤3、n阱退火;步骤4、通过光刻和刻蚀形成p-阱区域,其中p-阱面积大于n 阱面积,且覆盖其上。;步骤5、p-阱退火;步骤6、通过光刻和刻蚀形成p 主结区;步骤7、p 主结区退火,形成欧姆接触;步骤8、正面刻蚀接触孔,蒸发和反刻金属形成正面电极;步骤9、背面减薄,蒸发金属做背面电极。所述n 阱与p 主结之间形成的p n 结为单边突变结,所述齐纳二极管电压可以做到7.5v以内,以5.1v齐纳二极管为例,其漏电可以做到小于5.0μa@4.2v,片内电压均匀性在

±

2%以内。2.根据权利要求1所述的方法,其特征在于,所述的步骤1进一步包括:n 衬底电阻率约为0.002-0.010ω.cm,在1050℃条件下化学气相淀积生长厚度为5.0-10.0um,电阻率为0.5-3.0ω.cm的n-外延层。3.根据权利要求2所述的方法,其特征在于,所述的步骤2进一步包括:所述的n 阱的注入剂量视击穿电压而定,以5.1v的的低压齐纳二极管为例,剂量在1e14-3e14。4.根据权利要求3所述的方法,其特征在于,所述的步骤3进一步包括:n阱退火温度在1050℃-1150℃,时间1.5h-2.5h。5.根据权利要求4所述的方法,其特征在于,所述的步骤4进一步包括:p-阱剂量较淡,n 阱剂量是p-阱剂量的10-100倍,以5.1v的的低压齐纳二极管为例,p-剂量在1e12-3e13。同时p-阱面积大于n 阱面积,且覆盖其上。6.根据权利要求5所述的方法,其特征在于,所述的步骤5进一步包括:p-阱退火温度在1000℃-1050℃左右,时间1.5h-2.5h。7.根据权利要求6所述的方法,其特征在于,所述p 主结区注入剂量在2e15-1e16范围。8.根据权利要求7所述的方法,其特征在于,所述的步骤7进一步包括:p 主结区退火温度850℃-950℃左右,时间1h-2h。9.根据权利要求8所述的方法,其特征在于,所述的步骤9进一步包括:背面减薄到150μm,便于封装sot-23。

技术总结

本发明公开了一种制备低漏电齐纳二极管芯片的方法及结构,所述的方法包括如下步骤:在N 衬底上直接通过外延,形成N-外延层。通过注入磷和退火,形成N 阱。通过注入硼和退火形成P-阱区域,其中P-阱面积大于N 阱面积,且覆盖其上。通过注入硼和退火形成P 主结区。最后正面蒸发金属和反刻金属完成正面电极,减薄后背面蒸发金属完成背面电极;其结构是本发明采用特有的N-外延、N 阱、P-阱(其中P-阱面积大于N 阱面积,且覆盖其上)和P 注硼工艺,可以确保P /N 击穿都在平面上,避免侧向击穿,另外可以将齐纳二极管电压降到7.5V以下,以5.1V齐纳二极管为例,其漏电可以控制在小于5.0μA@4.2V,同时可以确保片内电压均匀性在

技术研发人员:钟平权

受保护的技术使用者:东莞市通科电子有限公司

技术研发日:2021.12.29

技术公布日:2022/4/5

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。