1.本发明涉及信道编码领域,具体涉及一种全局耦合低密度奇偶校验码的编码方法。

背景技术:

2.信道编码作为能提高传输可靠性的重要方法之一,一直是通信领域的一个研究热点。ldpc码凭借其优秀的纠错性能和硬件易实现特性,被视为纠错码领域的里程碑。近年来提出的全局耦合ldpc码相比传统结构,具有更好的耦合特性,能通过其全局耦合部分,增强译码迭代过程中校验节点和变量节点信息传递,对高速传输场景下的高可靠性需求提供了一种解决方案。

3.全局耦合低密度奇偶校验码的构造是该领域的一个研究热点,设计校验矩阵和对应的高效编码方法,对于其工程化应用有着重要的意义,但目前尚未有相关方案。

技术实现要素:

4.针对现有技术中的上述不足,本发明提供的一种全局耦合低密度奇偶校验码的编码方法提出了一种纠错能力强、编码效率高、对应编解码器易于工程化实现的全局耦合低密度奇偶校验码的编码方法。

5.为了达到上述发明目的,本发明采用的技术方案为:

6.提供一种全局耦合低密度奇偶校验码的编码方法,其包括以下步骤:

7.s1、构建全局耦合ldpc码的基矩阵;

8.s2、将基矩阵进行扩展置换和掩膜处理,得到全局耦合ldpc码的校验矩阵;

9.s3、采用全局耦合ldpc码的校验矩阵进行编码。

10.进一步地,步骤s1的具体方法包括以下子步骤:

11.s1-1、确定素数q与扩展因子z=q-1=r

×

l,取有限域gf(q)上的本原元α,获取本原元α的幂的集合{α0=1,α,α2,...,α

q-2

};其中r和l均为常数;

12.s1-2、将本原元α的幂的集合对素数q取模后减1,得到z

×

z的母矩阵b0:

[0013][0014]

s1-3、将母矩阵b0拆分成r

×

r个维度为l

×

l的子矩阵,并任取其中一个维度为l

×

l的子矩阵,将该l

×

l的子矩阵从上到下、从左到右取出m

×

n个元素组成矩阵b

local

;其中m≤l,n≤l;

[0015]

s1-4、将矩阵b

local

所在l

×

(r

×

l)矩阵除去用作矩阵b

local

的1

×

l向量以外的部分作为向量集合m;从向量集合m中取出s

×

r个不同的1

×

l向量,对每个取出的1

×

l向量从左

到右取出1

×

n个元素,得到维度为s

×

(r

×

n)的矩阵b

global

;即矩阵b

global

包含s

×

r个不同的1

×

n向量;其中s为常数;

[0016]

s1-5、将r个矩阵b

local

放置在对角线位置,将其余位置以0补充,得到本地矩阵

[0017]

s1-6、在本地矩阵的最下端耦合上矩阵b

global

,得到全局耦合ldpc码的基矩阵b

gc

:

[0018][0019]

其中b

global1

表示矩阵b

global

中的第一个子矩阵;b

globalr

表示矩阵b

global

中的第r个子矩阵,矩阵b

global

中每个子矩阵的大小均为s

×

n。

[0020]

进一步地,步骤s1-1中r的取值为2≤r≤4。

[0021]

进一步地,步骤s2的具体方法包括以下子步骤:

[0022]

s2-1、对当前的基矩阵b

gc

进行扩展置换:逐个将当前的基矩阵b

gc

中的元素替换成z

×

z单位矩阵根据元素系数值循环右移后的置换矩阵,得到矩阵h;

[0023]

s2-2、获取矩阵h中需求逆的子矩阵;

[0024]

s2-3、判断需求逆的子矩阵是否满秩,若是则将矩阵h作为全局耦合ldpc码的校验矩阵其中矩阵h1由b

local

中的元素替换成z

×

z单位矩阵根据元素系数值循环右移后的置换矩阵得到,矩阵h

r 1

由b

globalr

中的元素替换成z

×

z单位矩阵根据元素系数值循环右移后的置换矩阵得到;否则进入步骤s2-4;

[0025]

s2-4、获取并将矩阵h中需求逆但未满秩的子矩阵所对应的基矩阵b

gc

的子矩阵作为待掩膜矩阵;

[0026]

s2-5、随机生成矩阵b

mask

对待掩膜矩阵进行掩膜操作,得到新的基矩阵b

gc

,返回步骤s2-1。

[0027]

进一步地,步骤s3的具体方法包括以下子步骤:

[0028]

s3-1、将矩阵h1从左至右进行拆分,得到一个子矩阵ha和一个最大方形子矩阵hb;将子矩阵ha左右拆分成列数分别为n-m-s和s的子矩阵hm和hn;即h1=[hm,hn,hb];

[0029]

s3-2、将矩阵h

r 1

从左到右进行拆分,得到列数分别为n-m-s和s的子矩阵hj和矩阵hk,以及一个最大方形子矩阵hv;即h

r 1

=[hj,hk,hv];

[0030]

s3-3、将待编码信息序列分成r份,分别表示为s1,s2,...,sr;其中前r-1份待编码信息序列的比特长度均为(n-m)

×

(z),第r份待编码信息序列的比特长度为(n-m-s)

×

(z);

[0031]

s3-4、将r份待编码信息序列按照h

gc

·ct

=0的展开式,与拆分得到的子矩阵作乘加运算,得到校验序列p1,p2,...,p

r-1

,p

r1

,p

r2

;其中c为待获取的编码序列c=[c1,c2,...,cr],cr为待获取的编码子序列;(

·

)

t

表示矩阵的转置;

[0032]

s3-5、以[[s1,p1],[s2,p2],...,[s

r-1

,p

r-1

],[sr,p

r1

,p

r2

]]的形式进行拼接,得到编码序列c,完成编码。

[0033]

进一步地,步骤s3-4的具体方法为:

[0034]

当r=2时,根据公式:

[0035][0036]

获取校验序列p1,p

21

,p

22

;其中编码子序列c1=[s1,p1],编码子序列c2=[s2,p

21

,p

22

];

[0037]

当r=3时,根据公式:

[0038][0039]

获取校验序列p1,p2,p

31

,p

32

;其中编码子序列c1=[s1,p1],编码子序列c2=[s2,p2],编码子序列c3=[s3,p

31

,p

32

];

[0040]

当r=4时,根据公式:

[0041][0042]

获取校验序列p1,p2,p3,p

41

,p

42

;其中编码子序列c1=[s1,p1],编码子序列c2=[s2,p2],编码子序列c3=[s3,p3],编码子序列c4=[s4,p

41

,p

42

]。

[0043]

本发明的有益效果为:

[0044]

1、编码效率高:本发明基于全局耦合ldpc码字及其校验矩阵结构特点,对线性分组码的基本定义式h

gc

·ct

=0进行展开,能够更高效的实现编码。

[0045]

2、易于工程化实现:相比传统空间耦合方式,本方法给校验矩阵增加全局耦合部分后,由于本地矩阵的各个分块具有相同的维度与矩阵系数,在工程实现中,全局耦合低密度奇偶校验码在进行本地部分的解码时,可以对运算单元和矩阵系数存储rom进行复用,降低了硬件开销,具有较高的工程化价值。

附图说明

[0046]

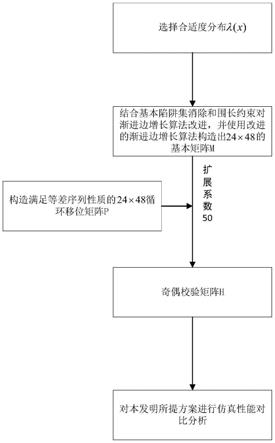

图1为本方法的流程示意图;

[0047]

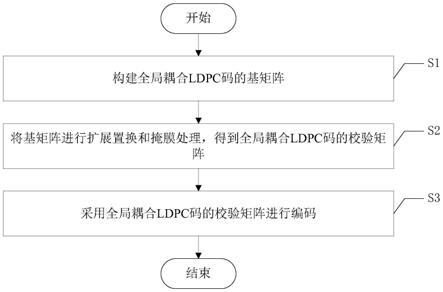

图2为本方法的纠错性能仿真示意图;

具体实施方式

[0048]

下面对本发明的具体实施方式进行描述,以便于本技术领域的技术人员理解本发明,但应该清楚,本发明不限于具体实施方式的范围,对本技术领域的普通技术人员来讲,只要各种变化在所附的权利要求限定和确定的本发明的精神和范围内,这些变化是显而易见的,一切利用本发明构思的发明创造均在保护之列。

[0049]

如图1所示,该全局耦合低密度奇偶校验码的编码方法包括以下步骤:

[0050]

s1、构建全局耦合ldpc码的基矩阵;

[0051]

s2、将基矩阵进行扩展置换和掩膜处理,得到全局耦合ldpc码的校验矩阵;

[0052]

s3、采用全局耦合ldpc码的校验矩阵进行编码。

[0053]

步骤s1的具体方法包括以下子步骤:

[0054]

s1-1、确定素数q与扩展因子z=q-1=r

×

l,取有限域gf(q)上的本原元α,获取本原元α的幂的集合{α0=1,α,α2,...,α

q-2

};其中r和l均为常数;r的取值为2≤r≤4;

[0055]

s1-2、将本原元α的幂的集合对素数q取模后减1,得到z

×

z的母矩阵b0:

[0056][0057]

s1-3、将母矩阵b0拆分成r

×

r个维度为l

×

l的子矩阵,并任取其中一个维度为l

×

l的子矩阵,将该l

×

l的子矩阵从上到下、从左到右取出m

×

n个元素组成矩阵b

local

;其中m≤l,n≤l;

[0058]

s1-4、将矩阵b

local

所在l

×

(r

×

l)矩阵除去用作矩阵b

local

的1

×

l向量以外的部分作为向量集合m;从向量集合m中取出s

×

r个不同的1

×

l向量,对每个取出的1

×

l向量从左到右取出1

×

n个元素,得到维度为s

×

(r

×

n)的矩阵b

global

;即矩阵b

global

包含s

×

r个不同的1

×

n向量;其中s为常数;m和s的选取是严格小于列重的正整数,n通常取接近l的正整数,m、s、n和r决定了码率,n和r配合z决定了码长;

[0059]

s1-5、将r个矩阵b

local

放置在对角线位置,将其余位置以0补充,得到本地矩阵

[0060]

s1-6、在本地矩阵的最下端耦合上矩阵b

global

,得到一个(m

×

r s)

×

(n

×

r)阶的全局耦合ldpc码的基矩阵b

gc

:

[0061][0062]

其中b

global1

表示矩阵b

global

中的第一个子矩阵;b

globalr

表示矩阵b

global

中的第r个子矩阵,矩阵b

global

中每个子矩阵的大小均为s

×

n。

[0063]

传统的用随机形式构造ldpc码的方法通常会引入短环,针对此问题,本方法首先构造了母矩阵b0,借助其特殊结构,该矩阵经理论证明本身即具有不含四环的优势,同时其对角线上各个本地子矩阵系数相同的优势使得在译码器的整体硬件实现中可以流水线形式的复用一个运算单元与一套系数存储rom进行解码,有效降低了硬件成本。

[0064]

步骤s2的具体方法包括以下子步骤:

[0065]

s2-1、对当前的基矩阵b

gc

进行扩展置换:逐个将当前的基矩阵b

gc

中的元素替换成z

×

z单位矩阵根据元素系数值循环右移后的置换矩阵,得到矩阵h;

[0066]

s2-2、获取矩阵h中需求逆的子矩阵;

[0067]

s2-3、判断需求逆的子矩阵是否满秩,若是则将矩阵h作为全局耦合ldpc码的校验矩阵其中矩阵h1由b

local

中的元素替换成z

×

z单位矩阵根据元素系数值循环右移后的置换矩阵得到,矩阵h

r 1

由b

globalr

中的元素替换成z

×

z单位矩阵根据元素系数值循环右移后的置换矩阵得到;否则进入步骤s2-4;

[0068]

s2-4、获取并将矩阵h中需求逆但未满秩的子矩阵所对应的基矩阵b

gc

的子矩阵作为待掩膜矩阵;

[0069]

s2-5、随机生成矩阵b

mask

对待掩膜矩阵进行掩膜操作,得到新的基矩阵b

gc

,返回步骤s2-1。

[0070]

步骤s3的具体方法包括以下子步骤:

[0071]

s3-1、将矩阵h1从左至右进行拆分,得到一个子矩阵ha和一个最大方形子矩阵hb;将子矩阵ha左右拆分成列数分别为n-m-s和s的子矩阵hm和hn;即h1=[hm,hn,hb];

[0072]

s3-2、将矩阵h

r 1

从左到右进行拆分,得到列数分别为n-m-s和s的子矩阵hj和矩阵hk,以及一个最大方形子矩阵hv;即h

r 1

=[hj,hk,hv];

[0073]

s3-3、将待编码信息序列分成r份,分别表示为s1,s2,...,sr;其中前r-1份待编码信息序列的比特长度均为(n-m)

×

(z),第r份待编码信息序列的比特长度为(n-m-s)

×

(z);

[0074]

s3-4、将r份待编码信息序列按照线性分组码的基本定义式h

gc

·ct

=0的展开式,与拆分得到的子矩阵作乘加运算,得到校验序列p1,p2,...,p

r-1

,p

r1

,p

r2

;其中c为待获取的编码序列c=[c1,c2,...,cr],cr为待获取的编码子序列;(

·

)

t

表示矩阵的转置;

[0075]

s3-5、以[[s1,p1],[s2,p2],...,[s

r-1

,p

r-1

],[sr,p

r1

,p

r2

]]的形式进行拼接,得到编码序列c,完成编码。

[0076]

步骤s3-4的具体方法为:

[0077]

当r=2时,根据公式:

[0078][0079]

获取校验序列p1,p

21

,p

22

;其中编码子序列c1=[s1,p1],编码子序列c2=[s2,p

21

,p

22

];

[0080]

当r=3时,根据公式:

[0081][0082]

获取校验序列p1,p2,p

31

,p

32

;其中编码子序列c1=[s1,p1],编码子序列c2=[s2,p2],编码子序列c3=[s3,p

31

,p

32

];

[0083]

当r=4时,根据公式:

[0084][0085]

获取校验序列p1,p2,p3,p

41

,p

42

;其中编码子序列c1=[s1,p1],编码子序列c2=[s2,p2],编码子序列c3=[s3,p3],编码子序列c4=[s4,p

41

,p

42

]。

[0086]

在本发明的一个实施例中,设计一个大小为2100

×

21150,平均行重为59.64,平均列重为5.92的全局耦合ldpc码的校验矩阵并利用其进行编码,选取素数为151,选择有限域gf(151),取本原元α=13,扩展因子z=150,m=4,n=47,s=2,r=3,l=50。根据设定的参数可知基矩阵b

gc

的大小为14

×

141,将母矩阵b0按照50

×

50划分为3

×

3个子矩阵。然后从该3

×

3个子矩阵中任选其一,沿主对角线选取前4行与前47列后进行左上至右下的重复排列并对空白处补零,得到基矩阵b

gc

的本地部分,即本地矩阵。

[0087]

由上述基矩阵b

gc

大小14

×

141和本地矩阵大小12

×

141,可知基矩阵全局耦合部分大小为2

×

141,由6个1

×

47的子矩阵构成。假设本地矩阵取自母矩阵b0中的第(x-1)

×

50 y至(x-1)

×

50 y 3行,则6个1

×

47的子矩阵需互不重复的取自(x-1)

×

50 1至x

×

50行中除开用于本地部分以外所剩余146个1

×

50子矩阵的集合,将基矩阵的本地部分和全局耦合部分上下拼接,得到基矩阵b

gc

。将基矩阵进行扩展置换和掩膜处理,得到全局耦合ldpc码的校验矩阵。

[0088]

对上述所得的(21150,19050)的全局耦合ldpc码进行如下仿真:

[0089]

仿真场景:信源生成并发送长度为19050的随机比特序列,编码器按照编码算法进行编码得到21150的编码序列,经过bpsk调制后得到调制序列,然后通过高斯白噪声信道达到译码器,译码器根据设计的校验矩阵与基矩阵,对接收到的序列采用分层最小和置信度传播译码算法,最大迭代次数设为10次,恢复出信源发送的消息。

[0090]

仿真内容:对本方法构造的全局耦合ldpc码的纠错性能进行仿真,得到如图2的仿真结果,仿真曲线代表的是本发明设计构造的校验矩阵对应的误比特率性能。图2中纵坐标ber表示比特出错率,横坐标表示接收机解调门限,每比特能量(eb)除以噪声功率谱密度(no)。

[0091]

综上所述,本发明提升了存储器、光通信等高速信道下的传输可靠性,且易于工程化实现,具有低硬件成本和高硬件吞吐量的优势。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。