技术特征:

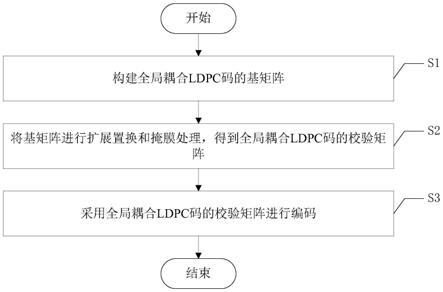

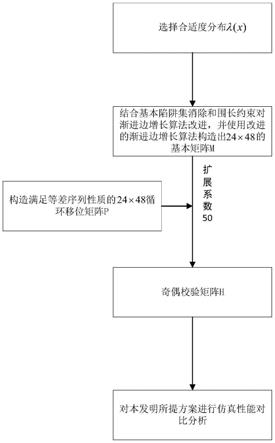

1.一种全局耦合低密度奇偶校验码的编码方法,其特征在于,包括以下步骤:s1、构建全局耦合ldpc码的基矩阵;s2、将基矩阵进行扩展置换和掩膜处理,得到全局耦合ldpc码的校验矩阵;s3、采用全局耦合ldpc码的校验矩阵进行编码。2.根据权利要求1所述的全局耦合低密度奇偶校验码的编码方法,其特征在于,步骤s1的具体方法包括以下子步骤:s1-1、确定素数q与扩展因子z=q-1=r

×

l,取有限域gf(q)上的本原元α,获取本原元α的幂的集合{α0=1,α,α2,...,α

q-2

};其中r和l均为常数;s1-2、将本原元α的幂的集合对素数q取模后减1,得到z

×

z的母矩阵b0:s1-3、将母矩阵b0拆分成r

×

r个维度为l

×

l的子矩阵,并任取其中一个维度为l

×

l的子矩阵,将该l

×

l的子矩阵从上到下、从左到右取出m

×

n个元素组成矩阵b

local

;其中m≤l,n≤l;s1-4、将矩阵b

local

所在l

×

(r

×

l)矩阵除去用作矩阵b

local

的1

×

l向量以外的部分作为向量集合m;从向量集合m中取出s

×

r个不同的1

×

l向量,对每个取出的1

×

l向量从左到右取出1

×

n个元素,得到维度为s

×

(r

×

n)的矩阵b

global

;即矩阵b

global

包含s

×

r个不同的1

×

n向量;其中s为常数;s1-5、将r个矩阵b

local

放置在对角线位置,将其余位置以0补充,得到本地矩阵s1-6、在本地矩阵的最下端耦合上矩阵b

global

,得到全局耦合ldpc码的基矩阵b

gc

:其中b

global1

表示矩阵b

global

中的第一个子矩阵;b

globalr

表示矩阵b

global

中的第r个子矩阵,矩阵b

global

中每个子矩阵的大小均为s

×

n。3.根据权利要求2所述的全局耦合低密度奇偶校验码的编码方法,其特征在于,步骤s1-1中r的取值为2≤r≤4。4.根据权利要求3所述的全局耦合低密度奇偶校验码的编码方法,其特征在于,步骤s2

的具体方法包括以下子步骤:s2-1、对当前的基矩阵b

gc

进行扩展置换:逐个将当前的基矩阵b

gc

中的元素替换成z

×

z单位矩阵根据元素系数值循环右移后的置换矩阵,得到矩阵h;s2-2、获取矩阵h中需求逆的子矩阵;s2-3、判断需求逆的子矩阵是否满秩,若是则将矩阵h作为全局耦合ldpc码的校验矩阵其中矩阵h1由b

local

中的元素替换成z

×

z单位矩阵根据元素系数值循环右移后的置换矩阵得到,矩阵h

r 1

由b

globalr

中的元素替换成z

×

z单位矩阵根据元素系数值循环右移后的置换矩阵得到;否则进入步骤s2-4;s2-4、获取并将矩阵h中需求逆但未满秩的子矩阵所对应的基矩阵b

gc

的子矩阵作为待掩膜矩阵;s2-5、随机生成矩阵b

mask

对待掩膜矩阵进行掩膜操作,得到新的基矩阵b

gc

,返回步骤s2-1。5.根据权利要求4所述的全局耦合低密度奇偶校验码的编码方法,其特征在于,步骤s3的具体方法包括以下子步骤:s3-1、将矩阵h1从左至右进行拆分,得到一个子矩阵h

a

和一个最大方形子矩阵h

b

;将子矩阵h

a

左右拆分成列数分别为n-m-s和s的子矩阵h

m

和h

n

;即h1=[h

m

,h

n

,h

b

];s3-2、将矩阵h

r 1

从左到右进行拆分,得到列数分别为n-m-s和s的子矩阵h

j

和矩阵h

k

,以及一个最大方形子矩阵h

v

;即h

r 1

=[h

j

,h

k

,h

v

];s3-3、将待编码信息序列分成r份,分别表示为s1,s2,...,s

r

;其中前r-1份待编码信息序列的比特长度均为(n-m)

×

(z),第r份待编码信息序列的比特长度为(n-m-s)

×

(z);s3-4、将r份待编码信息序列按照h

gc

·

c

t

=0的展开式,与拆分得到的子矩阵作乘加运算,得到校验序列p1,p2,...,p

r-1

,p

r1

,p

r2

;其中c为待获取的编码序列c=[c1,c2,...,c

r

],c

r

为待获取的编码子序列;(

·

)

t

表示矩阵的转置;s3-5、以[[s1,p1],[s2,p2],...,[s

r-1

,p

r-1

],[s

r

,p

r1

,p

r2

]]的形式进行拼接,得到编码序列c,完成编码。6.根据权利要求5所述的全局耦合低密度奇偶校验码的编码方法,其特征在于,步骤s3-4的具体方法为:当r=2时,根据公式:获取校验序列p1,p

21

,p

22

;其中编码子序列c1=[s1,p1],编码子序列c2=[s2,p

21

,p

22

];当r=3时,根据公式:

获取校验序列p1,p2,p

31

,p

32

;其中编码子序列c1=[s1,p1],编码子序列c2=[s2,p2],编码子序列c3=[s3,p

31

,p

32

];当r=4时,根据公式:获取校验序列p1,p2,p3,p

41

,p

42

;其中编码子序列c1=[s1,p1],编码子序列c2=[s2,p2],编码子序列c3=[s3,p3],编码子序列c4=[s4,p

41

,p

42

]。

技术总结

本发明公开了一种全局耦合低密度奇偶校验码的编码方法,其包括以下步骤:S1、构建全局耦合LDPC码的基矩阵;S2、将基矩阵进行扩展置换和掩膜处理,得到全局耦合LDPC码的校验矩阵;S3、采用全局耦合LDPC码的校验矩阵进行编码。本发明提升了存储器、光通信等高速信道下的传输可靠性,且易于工程化实现,具有低硬件成本和高硬件吞吐量的优势。成本和高硬件吞吐量的优势。成本和高硬件吞吐量的优势。

技术研发人员:包滨豪 管武 梁利平 任万春

受保护的技术使用者:包滨豪

技术研发日:2021.12.21

技术公布日:2022/4/5

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。