一种基于fpga的射频开关和tr组件控制系统和方法

技术领域

1.本发明涉及射频微波测试技术领域,特别是涉及一种基于fpga的射频开关和tr组件控制系统和方法。

背景技术:

2.随着有源相控阵雷达的阵面通道规模向着千/万级大规模化发展,其分辨率等性能要求也大幅提升。

3.其中相控阵雷达的核心是数字tr组件,目前单个tr组件的通道数量以及工作模式越来越多,这也就意味着需要测试参数的指标越来越多,包括直流参数、散射参数、功率参数以及噪声参数等,对于各类的参数需要不同的测试设备,包括矢量网络分析仪、信号源、频谱仪、功率计、示波器等。对于多通道的多指标测试,需要付出大量的人工成本,因此采用开关矩阵,实现将所有的测试设备纳入统一测试系统中,并根据不用的测试指标,在各类设备之间进行切换,同时,也能进行不同通道之间的测试切换,实现多通道多指标自动测试,节约人力成本,简化测试的操作,提高测试系统的测试效率及稳定性。

4.另一方面,随着单个tr组件的复杂程度不断提成,数控衰减器、数控移向器以及电源管理芯片等,成为了组件的标配。其中,电源管理芯片主要用于控制数控衰减器和数控移向器的工作状态以及组件的接收模式、发射模式的切换。电源管理芯片的输入包括多个控制信号电平,包括时钟信号、片选信号、锁存信号、数据信号等,数据信号表示一串包含衰减、移相、发射、接收等控制位的串行码。电源管理芯片接收的控制信号都存在特定的时序对应关系,因此需要通过设置pxi控制系统,实现对不同组件的不同控制信号的管理。

5.然而现有的开关矩阵以及pxi控制系统的价格高昂,动辄数十万,极大提高了雷达系统的成本,另外两台不同的设备和各自的操作系统也极大地提高了测试系统的复杂程度,增加了操作人员的学习成本、平台搭建的难度、自动化测试程序的开发难度、系统的维护成本等等。因此需要一款结构简单,并且能够实现测试通道切换以及tr组件工作状态切换的设备。

技术实现要素:

6.本发明的目的是解决现有技术的不足,提供一种基于fpga的射频开关和tr组件控制系统和方法。

7.为了解决上述问题,本发明采用如下技术方案:

8.一种基于fpga的射频开关和tr组件控制系统,包括机箱壳体、显示器部件、输出接口、按钮模块、jtag接口、串口通信接口以及射频开关接口;其中显示器部件设置于机箱壳体上的镂空部位,显示器部件与机箱壳体相匹配;机箱壳体上还设置有输出接口、按钮模块、jtag接口、串口通信接口以及射频开关接口;机箱壳体内部设置有fpga主控模块,fpga主控模块用于实现对tr组件的控制和测试;输出接口用于向外接的设备输出控制信号;射频开关接口通过射频电缆外接有单个开关或者组合开关;jtag接口以及串口通信接口用于

连接上位机。

9.进一步的,所述输出接口包括bnc接口、针座以及j30j接口;针座为40p的牛角针座。

10.进一步的,所述射频开关接口外接的单个开关或者组合开关,包括多通道tr组件以及测试设备,其中测试设备包括信号源、频谱仪、功率计、噪声源、矢量网络分析仪。

11.进一步的,所述射频开关接口包括输入端和输出端;射频开关接口中的输入端分别与信号源、频谱仪连接,输入端还与矢量网络分析仪的输出连接;射频开关接口中的输出端分别与功率计、噪声源连接,输出端还与矢量网络分析仪的输入连接;同为输入端或者同为输出端的测试设备之间能够进行切换。

12.进一步的,所述fpga主控模块包括fgpa芯片、jtag通信模块、串口通信模块、射频驱动电路、驱动模块以及电平转换模块;其中fgpa芯片分别与jtag通信模块、串口通信模块、射频驱动电路、驱动模块以及电平转换模块连接;串口通信模块和jtag通信模块还与外接的上位机连接;射频驱动模块与射频开关连接;驱动模块以及电平转换模块还与tr控制接口连接;fgpa芯片还与机箱壳体上的按钮模块以及显示器部件连接。

13.进一步的,所述jtag通信模块与jtag接口连接,jtag模块包括fgpa芯片的部分管脚、芯片u7以及芯片u9,其中芯片u7和芯片u9均采用集成芯片sn74avc2t245rswr;fpga芯片采用集成芯片xc7a35t-fgg484-2,fpga芯片的n9、n10、u9、u10引脚接地;fpga芯片的u12、n12、u11引脚分别连接电阻r9、r1、r2的一端,电阻r9、r1、r2的一端另一端均连接3.3v电压;fpga芯片的e12引脚连接1.8v电压;fpga芯片的m10、l9、k9引脚连接电感l1一端,电感l1的另一端接地;fpga芯片的k10连接电感l2一端,电感l2的另一端连接1.8v电压;k10引脚还与电容c1、c2的一端连接,电容c1、c2的另一端均与k9引脚连接;fpga芯片的v12、t13引脚分别连接芯片u7的第9和第8引脚;芯片u7的第6和第7引脚均与3.3v电压连接,其第1、2、3、10引脚均接地;芯片u7的第7和第6引脚分别与电容c57、c58的一端连接,电容c57、c58均接地;fpga芯片的u13、r13引脚分别连接芯片u9的第8和第9引脚;芯片u9的第6、7、10引脚均连接3.3v电压,芯片u9的第1、2、3引脚均接地;芯片u9的第7、6引脚分别与电容c59、c60连接,电容c59、c60均接地。

14.进一步的,所述串口通信模块与串口通信接口相连,串口通信模块包括收发芯片u16,u16采用集成芯片cp2103gm_mlp-28;收发芯片u16的第2、29、30引脚接地,其第3、4引脚分别与usb_mini的第3、2引脚连接,usb_mini为一种usb的接口标准;收发芯片u16的第5引脚通过电阻r98与引脚9连接,第5引脚还通过电感fb1与1.8v电压连接,第5引脚还通过电容c69、c70接地;收发芯片u16的第6引脚通过电容c68接地;收发芯片u16的第7引脚和第8引脚直接连接,并通过电感fb3与usb_mini的第1引脚相连接;usb_mini的第1引脚通过电容c71与其第5引脚相连接,usb_mini的第5引脚还通过电感fb2接地;usb_mini的第6、7、8、9引脚均与tvs二极管u15的第1引脚相连接,tvs二极管u15的第1引脚还通过电容c87接地;tvs二极管u15的第2引脚与usb_mini的第1引脚连接,u15的第3引脚与usb_mini的第2引脚连接,u15的第4引脚与usb_mini的第3引脚连接。

15.进一步的,所述fpga主控模块还包括时钟电路;时钟电路包括晶振芯片g1,晶振芯片g1的第2引脚接地;晶振芯片g1的第4引脚通过电感l3与3.3v电压连接,第4引脚还分别通过电容c64、电容c65接地;晶振芯片g1的第3引脚通过电容c66接地,第3引脚还通过电阻r94

作为输出,输出时钟信号。

16.进一步的,所述输出接口包括bnc接口、针座以及j30j接口;针座为40p的牛角针座。

17.进一步的,所述机箱壳体的侧面还设置有散热通风孔;两个散热通风孔相对设置,形成空气对流。

18.一种基于fpga的射频开关和tr组件控制方法,所述控制方法基于上述的控制系统,控制方法包括如下步骤:

19.步骤1:fgpa主控模块通过串口通信接口接收上位机的控制指令;

20.步骤2:fgpa主控模块识别控制指令的帧头,进入不同的工作模式,包括开关矩阵模式和pxi控制模式;若识别为开关矩阵模式,则进入步骤3;否则进入步骤4;

21.步骤3:fgpa主控模块进入开关矩阵模式,进一步识别控制指令中的测试对象;确定测试对象后,fpga主控模块切换射频开关接口8至对应的tr组件,开始测试,进入步骤31;测试包括发射功率测试、接收噪声测试以及发射和接收的移相衰减测试;

22.步骤31:fgpa主控模块控制tr组件为发射状态;并切换射频开关接口8的输入端至外接的信号源,输出端至外接的功率计;fgpa主控模块控制信号源发出的脉冲信号,通过功率计完成该tr组件的发射功率测试;其中功率计接收的信号会同步传输至上位机;

23.步骤32:fgpa主控模块控制tr组件为接收状态;并切换射频开关接口8的输入端至外接的频谱仪,输出端至外接的噪声源;fgpa主控模块控制噪声源发出的噪声信号,通过频谱仪完成该tr组件的接收噪声测试;其中频谱仪接收的信号会同步传输至上位机;

24.步骤33:fpga主控模块切换射频开关接口的输入端和输出端至外接矢量网络分析仪;fgpa主控模块控制矢量网络分析仪的发射控制位、接收控制位、移相衰减位,并切换tr组件的发射和接收工作状态,完成该tr组件的发射和接收的移相衰减测试;其中矢量网络分析仪接收的信号会同步传输至上位机;

25.步骤34:上位机判断tr组件是否已经完成所有测试,包括发射功率测试、接收噪声测试以及发射和接收的移相衰减测试;若已完成所有测试,则结束步骤;否则,上位机向fpga主控模块发送控制指令,fpga主控模块根据指令切换射频开关接口,完成相应测试,结束步骤;

26.步骤4:fgpa主控模块进入pxi控制模式;选择输出接口,输出接口包括bnc接口、针座以及j30j接口;fpga主控制板接收上位机发送的控制指令,并对控制指令进行处理发送给tr组件,实现发射状态控制、接收状态控制、移相位控制、衰减位控制、延时位控制操作;结束步骤。

27.本发明的有益效果为:

28.通过设置射频开关接口与fpga主控模块连接,fpga主控模块还与按钮模块以及上位机连接,实现射频开关切换,选择对应的测试通道以及测试设备,实现高效简单的tr组件测试,另一方面,通过编辑射频开关接口的输出信号,提高了测试装置的功能性;

29.通过设置上位机与fpga主控模块通过jtag接口连接,使得上位机能够重新烧写程序,定义fpga主控模块的处理内核;

30.通过设置fgpa主控模块包括开关矩阵模式和pxi控制模式,并且开关矩阵模式和pxi控制模式相对独立,既可以单独使用,也可以运用于同一测试系统,比如在步骤33中,在

tr组件的发射和接收的移相衰减测试过程中,还可以通过bnc接口向矢量网络分析仪输出脉冲信号,以供矢量网络分析仪触发进行脉冲同步测试,提高了tr组件测试效率,降低了测试成本,并具备通用性和扩展性,满足各类不同形式的多通道tr组件测试要求。

附图说明

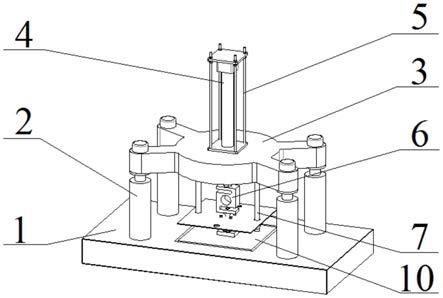

31.图1本发明实施例一的机箱外壳3d图;

32.图2本发明实施例一的机箱外壳前面板示意图;

33.图3本发明实施例一的具体应用实例框图;

34.图4本发明实施例一的基于fpga的系统总体设计框图;

35.图5本发明实施例一的fpga主控板jtag通信芯片部分原理图;

36.图6本发明实施例一的fpga主控板串口通信芯片部分原理图;

37.图7本发明实施例一的fpga主控板外部时钟部分原理图;

38.图8本发明实施例一的fpga程序流程图;

39.附图标记:

40.显示器部件1、bnc接口2、按钮模块3、针座4、j30j接口5、jtag接口6、串口通信接口7、射频开关接口8、散热通风孔9、机箱壳体10。

具体实施方式

41.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。

42.需要说明的是,以下实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

43.实施例一:

44.如图1、2所示,一种基于fpga的射频开关和tr组件控制系统,包括机箱壳体10、显示器部件1、输出接口、按钮模块3、jtag接口6、串口通信接口7以及射频开关接口8;其中显示器部件1设置于机箱壳体10上的镂空部位,显示器部件1与机箱壳体10相匹配;机箱壳体10上还设置有输出接口、按钮模块3、jtag接口6、串口通信接口7以及射频开关接口8;机箱壳体10内部设置有fpga主控模块,fpga主控模块用于实现对tr组件的控制和测试;输出接口用于向外接的设备输出控制信号,包括bnc接口2、针座4以及j30j接口5,针座4为牛角针座,在本例中为40p的牛角针座,在本例中输出接口外接的设备包括tr组件;射频开关接口8通过射频电缆外接有单个开关或者组合开关;fpga模块还通过jtag接口6以及串口通信接口7与外接的上位机连接,在本例中上位机通过jtag接口6向fpga模块烧录程序,fpga模块通过串口通信接口7与上位机进行信息交互。fpga主控模块中加载有下位机程序以及基于c#的上位机程序;上位机程序包括操作界面,通过操作界面能够切换射频开关接口8连接的

切换,还能够选择输出接口,包括bnc接口2、针座4以及j30j接口5;下位机程序为fpga主控模块的控制系统,用于分析上位机传入的指令,包括显示器部件1的开关、射频开关接口8的切换、控制信号的输出。

45.如图3所示,所述射频开关接口8外接的单个开关或者组合开关,包括多通道tr组件以及测试设备,其中测试设备包括但不限于信号源、频谱仪、功率计、噪声源、矢量网络分析仪。在本例中,为了便于实现测试设备之间的切换,射频开关接口8包括输入端和输出端,其中输入端的接口用于将测试设备的信号传输进入射频开关接口8,同理输出端的接口用于将处理后的信号传输出射频开关接口8;射频开关接口8中的输入端分别与信号源、频谱仪连接,输入端还与矢量网络分析仪的输出连接;射频开关接口8中的输出端分别与功率计、噪声源连接,输出端还与矢量网络分析仪的输入连接;同为输入端或者同为输出端的测试设备之间能够进行切换,比如从输入端从信号源切换至频谱仪。

46.所述按钮模块3包括副pcb板、硅胶按钮以及led灯,其中硅胶按钮以及led等均设置于副pcb板上,led灯与硅胶按钮对应设置。通过硅胶按钮能够控制射频开关接口8的切换,硅胶按钮上设置有与射频开关接口8相对应的数字标号,在本例中为数字1-16;led灯用于指示切换到的射频开关接口8,比如数字1的硅胶按钮对应的led等亮起,表示对应的射频开关接口8是打开的。

47.如图4所示,所述fpga主控模块包括fgpa芯片、jtag通信模块、串口通信模块、射频驱动电路、驱动模块以及电平转换模块,其中fgpa芯片分别与jtag通信模块、串口通信模块、射频驱动电路、驱动模块以及电平转换模块连接;串口通信模块和jtag通信模块还与外接的上位机连接,在本例中上位机为电脑;射频驱动模块与射频开关接口连接,在图4中射频开关接口表示为射频开关;驱动模块以及电平转换模块还与输出接口连接,在图4中输出接口表示为tr控制接口;fgpa芯片还与机箱壳体10上的按钮模块3以及显示器部件1连接。

48.如图5所示,所述jtag通信模块与jtag接口6连接,jtag模块包括fgpa芯片的部分管脚、芯片u7以及芯片u9,其中芯片u7和芯片u9均采用集成芯片sn74avc2t245rswr。fpga芯片采用集成芯片xc7a35t-fgg484-2,fpga芯片的n9、n10、u9、u10引脚接地;fpga芯片的u12、n12、u11引脚分别连接电阻r9、r1、r2的一端,电阻r9、r1、r2的一端另一端均连接3.3v电压;fpga芯片的e12引脚连接1.8v电压;fpga芯片的m10、l9、k9引脚连接电感l1一端,电感l1的另一端接地;fpga芯片的k10连接电感l2一端,电感l2的另一端连接1.8v电压;k10引脚还与电容c1、c2的一端连接,电容c1、c2的另一端均与k9引脚连接;fpga芯片的v12、t13引脚分别连接芯片u7的第9和第8引脚;芯片u7的第6和第7引脚均与3.3v电压连接,其第1、2、3、10引脚均接地;芯片u7的第7和第6引脚分别与电容c57、c58的一端连接,电容c57、c58均接地;fpga芯片的u13、r13引脚分别连接芯片u9的第8和第9引脚;芯片u9的第6、7、10引脚均连接3.3v电压,芯片u9的第1、2、3引脚均接地;芯片u9的第7、6引脚分别与电容c59、c60连接,电容c59、c60均接地;芯片u7的第4、5引脚分别与fpga芯片连接,芯片u9的第4、5引脚也分别与fpga芯片连接,芯片u7和u9的第4、5引脚均用于烧录程序。通过jtag通信模块能够实现对fpga主控模块的程序的烧录等操作。

49.如图6所示,所述串口通信模块与串口通信接口7相连,在本例中串口通信接口7为usb接口,串口通信模块包括收发芯片u16,在本例中采用集成芯片cp2103gm_mlp-28。收发芯片u16的第2、29、30引脚接地,其第3、4引脚分别与usb_mini的第3、2引脚连接,usb_mini

为一种usb的接口标准;收发芯片u16的第5引脚通过电阻r98与引脚9连接,第5引脚还通过电感fb1与1.8v电压连接,第5引脚还通过电容c69、c70接地;收发芯片u16的第6引脚通过电容c68接地;收发芯片u16的第7引脚和第8引脚直接连接,并通过电感fb3与usb_mini的第1引脚相连接;usb_mini的第1引脚通过电容c71与其第5引脚相连接,usb_mini的第5引脚还通过电感fb2接地;usb_mini的第6、7、8、9引脚均与tvs二极管u15的第1引脚相连接,tvs二极管u15的第1引脚还通过电容c87接地;tvs二极管u15的第2引脚与usb_mini的第1引脚连接,u15的第3引脚与usb_mini的第2引脚连接,u15的第4引脚与usb_mini的第3引脚连接。通过串口通信模块,能够实现上位机与fpga主控模块的实时通信,保证传递的控制信息的准确性和实时性。

50.如图7所示,所述fpga主控模块还包括时钟电路,通过时钟电路实现计时等操作。时钟电路包括晶振芯片g1,其中晶振芯片g1的第2引脚接地;晶振芯片g1的第4引脚通过电感l3与3.3v电压连接,第4引脚还分别通过电容c64、电容c65接地;晶振芯片g1的第3引脚通过电容c66接地,第3引脚还通过电阻r94输出,输出时钟信号。

51.所述机箱壳体10的侧面还设置有散热通风孔9,在本例中设置有两个散热通风孔9,两个散热通风孔9相对设置,形成空气对流,从而加速带走机箱壳体10内部的热量。

52.在实施的过程中,通过设置射频开关接口8与fpga主控模块连接,fpga主控模块还与按钮模块3以及上位机连接,实现射频开关切换,选择对应的测试通道以及测试设备,另一方面,通过编辑射频开关接口8的输出信号,提供了高效简单的测试方法;通过设置上位机与fpga主控模块通过jtag接口6连接,使得上位机能够重新烧写程序,定义fpga主控模块的处理内核。

53.如图8所示,一种基于fpga的射频开关和tr组件控制方法,包括如下步骤:

54.步骤1:fgpa主控模块通过串口通信接口7接收上位机的控制指令;

55.步骤2:fgpa主控模块识别控制指令的帧头,进入不同的工作模式,包括开关矩阵模式和pxi控制模式;若识别为开关矩阵模式,则进入步骤3;否则进入步骤4;

56.步骤3:fgpa主控模块进入开关矩阵模式,进一步识别控制指令中的测试对象;确定测试对象后,fpga主控模块切换射频开关接口8至对应的tr组件,开始测试,进入步骤31;在本例中测试包括发射功率测试、接收噪声测试以及发射和接收的移相衰减测试;

57.步骤31:fgpa主控模块控制tr组件为发射状态;并切换射频开关接口8的输入端至外接的信号源,输出端至外接的功率计;fgpa主控模块控制信号源发出的脉冲信号,通过功率计完成该tr组件的发射功率测试;其中功率计接收的信号会同步传输至上位机;

58.步骤32:fgpa主控模块控制tr组件为接收状态;并切换射频开关接口8的输入端至外接的频谱仪,输出端至外接的噪声源;fgpa主控模块控制噪声源发出的噪声信号,通过频谱仪完成该tr组件的接收噪声测试;其中频谱仪接收的信号会同步传输至上位机;

59.步骤33:fpga主控模块切换射频开关接口8的输入端和输出端至外接矢量网络分析仪;fgpa主控模块控制矢量网络分析仪的发射控制位、接收控制位、移相衰减位,并切换tr组件的发射和接收工作状态,完成该tr组件的发射和接收的移相衰减测试;其中矢量网络分析仪接收的信号会同步传输至上位机;

60.步骤34:上位机判断tr组件是否已经完成所有测试,包括发射功率测试、接收噪声测试以及发射和接收的移相衰减测试;若已完成所有测试,则结束步骤;否则,上位机向

fpga主控模块发送控制指令,fpga主控模块根据指令切换射频开关接口8,完成相应测试,结束步骤;

61.步骤4:fgpa主控模块进入pxi控制模式;选择输出接口,输出接口包括bnc接口2、针座4以及j30j接口5;fpga主控制板接收上位机发送的控制指令,并对控制指令进行处理发送给tr组件,实现发射状态控制、接收状态控制、移相位控制、衰减位控制、延时位控制操作;结束步骤。

62.需要说明的是,在一些其他实施方式中发射功率测试、接收噪声测试以及发射和接收的移相衰减测试的先后顺序可以任意切换。另外本技术还能够通过按钮模块3,手动控制切换射频开关接口,实现针对性的tr组件测试,组合更为灵活,可操作性更强。

63.所述步骤33中,矢量网络分析仪还能够与机箱壳体10上的bnc接口2连接,通过bnc接口2向矢量网络分析仪输出脉冲信号,以供矢量网络分析仪触发进行脉冲同步测试。

64.所述步骤4中上位机发送的控制指令可以为设定的控制指令,或者用户自定义的控制指令;控制指令包括脉冲信号、时钟信号clk、数据信号data、使能信号en、寄存器锁存信号load和组件收发切换信号tr等。控制指令包括3.3v、5v两种电平幅度。

65.在实施的过程中,通过设置fgpa主控模块包括开关矩阵模式和pxi控制模式,并且开关矩阵模式和pxi控制模式相对独立,既可以单独使用,也可以运用于同一测试系统,比如在步骤33中,在tr组件的发射和接收的移相衰减测试过程中,还可以通过bnc接口2向矢量网络分析仪输出脉冲信号,以供矢量网络分析仪触发进行脉冲同步测试,提高了tr组件测试效率,降低了测试成本,并具备通用性和扩展性,满足各类不同形式的多通道tr组件测试要求。

66.以上描述仅是本发明的一个具体实例,不构成对本发明的任何限制。显然对于本领域的专业人员来说,在了解了本发明内容和原理后,都可能在不背离本发明原理、结构的情况下,进行形式和细节上的各种修改和改变,但是这些基于本发明思想的修正和改变仍在本发明的权利要求保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。