1.本发明实施例涉及半导体领域,特别涉及一种存储器的制造方法和存储器。

背景技术:

2.存储器是用来存储程序和各种数据信息的记忆部件,随机存储器分为静态随机存储器和动态随机存储器。动态随机存储器通常包括电容器以及与电容器连接的晶体管,电容器用来存储代表存储信息的电荷,晶体管是控制电容器的电荷流入和释放的开关。在写入数据时字线给出高电平,晶体管导通,位线向电容器充电。读出时字线同样给出高电平,晶体管导通,电容器放电,使位线获得读出信号。

3.然而,随着存储器工艺节点的不断缩小,存储器的性能有待提高。

技术实现要素:

4.本发明实施例解决的技术问题为提供一种存储器的制造方法和存储器,以提高存储器的性能。为解决上述问题,本发明实施例提供一种存储器的制造方法,存储器的制造方法包括:提供基底以及多个分立的伪位线接触层,所述基底内具有多个有源区,且每一所述伪位线接触层与所述有源区连接;在所述伪位线接触层的顶部形成伪位线结构;形成填充相邻所述伪位线结构之间的区域的牺牲层,且所述牺牲层位于所述伪位线结构侧壁以及所述伪位线接触层侧壁;在形成所述牺牲层之后,去除所述伪位线结构,形成露出所述伪位线接触层的通孔;去除所述伪位线接触层,形成位于所述基底内的通孔;形成填充所述基底内的通孔的位线接触层,所述位线接触层与所述有源区电连接。

5.另外,所述伪位线接触层的材料与伪位线结构的材料不同。

6.另外所述伪位线接触层的材料包括氮化硅、氮氧化硅或碳氮化硅。

7.另外,所述伪位线结构的材料包括氮化硅、氮氧化硅或碳氮化硅。

8.另外,所述位线接触层的材料包括单晶硅。

9.另外,形成所述位线接触层的方法包括:外延生长技术。

10.另外,形成所述伪位线结构的步骤包括:在所述基底上形成伪位线层,所述伪位线层覆盖所述伪位线接触层;在所述伪位线层上形成图形化的掩膜层;以所述图形化的掩膜层为掩膜,刻蚀所述伪位线层,形成伪位线结构。

11.另外,形成所述图形化的掩膜层步骤包括:在所述伪位线层上形成多个分立的核心部;形成覆盖所述核心部顶部和侧壁以及所述伪位线层的侧墙膜;对所述侧墙膜进行刻蚀处理,形成位于所述核心部的相对的侧壁的侧墙层;去除所述核心部,所述侧墙层作为所述图形化的掩膜层。

12.另外,去除所述伪位线结构的工艺中,所述伪位线结构的材料与所述牺牲层的材料的刻蚀选择比为5-15。

13.另外,所述牺牲层的材料包括氧化硅。

14.另外,在形成所述牺牲层前,还包括:在所述伪位线结构及所述伪位线接触层的侧

壁形成介质层,所述介质层的材料与牺牲层的材料不同;形成的所述牺牲层还位于所述介质层的侧壁表面。

15.另外,所述介质层的材料包括低介电常数材料。

16.另外,在所述位线接触层上形成位线导电部,形成所述位线导电部的步骤包括:在所述位线接触层上的通孔的底部及侧壁形成阻挡层;在所述阻挡层的上表面形成导电层。

17.另外,形成所述位线导电部后,还包括:在所述位线导电部的顶部形成绝缘盖层;形成所述绝缘盖层后,去除所述牺牲层;去除所述牺牲层后,在所述位线导电部和绝缘盖层的表面形成保护层。

18.本发明实施例还提供一种如前述制造方法制造的存储器,包括:基底以及多个分立的位线接触层,所述基底内具有多个有源区,且每一所述位线接触层与所述有源区电连接;位线导电部,所述位线导电部位于所述位线接触层的顶部。

19.与现有技术相比,本发明实施例提供的技术方案具有以下优点:

20.本发明实施例中,去除伪位线结构及伪位线接触层后,在牺牲层之间形成了通孔;通孔可以作为位线接触层的填充区间,避免了刻蚀去除伪位线结构时对位线接触层造成损伤或残留杂质,从而提高了存储器的性能。

21.另外,通过外延生长技术形成的位线接触层的电阻更低,降低了位线接触层与有源区的接触面的电阻,从而提高存储器的运行速率。

22.另外,形成图形化的掩膜层步骤包括:在伪位线层上形成多个分立的核心部;形成覆盖核心部顶部和侧壁以及所述伪位线层的侧墙膜;对侧墙膜进行刻蚀处理,形成所述核心层的相对的侧壁的侧墙层;去除核心部,侧墙层作为图形化的掩膜层。即侧墙膜并不是通过光刻的方法形成的,而是在核心部的侧壁生长出来的;如此,侧墙层的尺寸可以不受光刻工艺的限制,通过缩小侧墙层的尺寸,可以缩小以侧墙层为掩模形成的伪位线结构的尺寸,进而减小存储器的尺寸。

附图说明

23.一个或多个实施例通过与之对应的附图中的图片进行示例性说明,这些示例性说明并不构成对实施例的限定,除非有特别申明,附图中的图不构成比例限制。

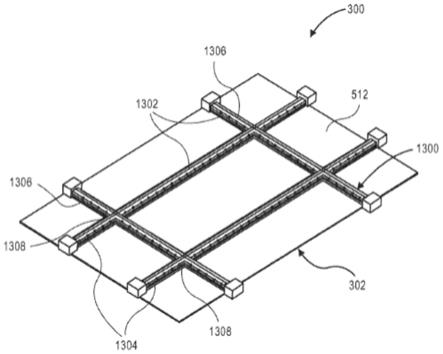

24.图1至图17为本发明第一实施例提供的存储器的制造方法中各步骤对应的结构示意图;

25.图18为本发明第二实施例提供的存储器的结构示意图。

具体实施方式

26.由背景技术可知,现有技术的存储器的性能有待提高。

27.分析发现,导致上述问题的主要原因包括:在位线接触层与牺牲层围成的通孔中形成伪位线结构,后续利用刻蚀的方法去除伪位线结构时,会对位线接触层造成损伤,同时也会在位线接触层中残留不易挥发的杂质,从而影响存储器的运行速度。

28.为解决上述问题,本发明实施例提供一种存储器的制造方法,在伪位线接触层与牺牲层围成的通孔中形成伪位线结构,后续在去除伪位线结构后,还去除伪位线接触层并在基底中形成通孔,在通孔中形成位线接触层;如此,可以避免刻蚀去除伪位线结构时对位

线接触层造成的损伤,避免在位线接触层中残留不易挥发的杂质,从而提高存储器的性能。

29.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合附图对本发明的各实施例进行详细的阐述。然而,本领域的普通技术人员可以理解,在本发明各实施例中,为了使读者更好地理解本技术而提出了许多技术细节。但是,即使没有这些技术细节和基于以下各实施例的种种变化和修改,也可以实现本技术所要求保护的技术方案。

30.本发明第一实施例提供一种存储器的制造方法,图1至图17为该制造方法中各步骤对应的结构示意图。

31.参考图1,提供基底100以及多个分立的伪位线接触层101,基底100内具有多个有源区102,且每一伪位线接触层101与有源区102连接。

32.基底100的材料包括硅、锗或者其它半导体材料。

33.相邻的有源区102之间的区域填充有第一隔离层103,第一隔离层103用于隔离多个有源区102。第一隔离层103的材料为绝缘材料,例如可以为二氧化硅。

34.在本实施例中,每一伪位线接触层101一部分位于基底100内,一部分高于基底100表面。在其他实施例中,伪位线接触层也可位于基底表面。

35.伪位线接触层101的材料包括氮化硅、氮氧化硅或碳氮化硅。

36.本实施例中,基底100表面还可以形成有第二隔离层104。第二隔离层104填充分立的伪位线接触层101之间的区域,用于隔离后续形的多个位线接触层。

37.第二隔离层104的材料为绝缘材料,例如可以为氮化硅。第二隔离层104的材料与伪位线接触层101的材料不同。

38.结合参考图1至图6,在伪位线接触层101的顶部形成伪位线结构117。

39.伪位线结构117用于定义后续形成的位线结构的位置和尺寸,也就是说,伪位线结构117的尺寸与后续形成的位线结构的尺寸相同。由于伪位线结构117不需要具有导电特性,因此可以采用绝缘材料作为伪位线结构117的材料。

40.形成伪位线结构117的步骤包括:在基底100上形成伪位线层105,伪位线层105覆盖伪位线接触层101;在伪位线层105上形成图形化的掩膜层115;以图形化的掩膜层115为掩膜,刻蚀伪位线层105,形成伪位线结构117。

41.具体的,在本实施例中,以双重图形化(sadp)的方法形成伪位线结构117。以下将结合附图对伪位线结构117的形成方法做详细说明。

42.参考图1,在基底100上形成伪位线层105,伪位线层105覆盖伪位线接触层101。

43.在伪位线层105上形成依次堆叠的底层掩膜层106和核心层109。本实施例中,底层掩膜层106包括:第一底层掩膜层107和第二底层掩模层108。

44.第一底层掩膜层107与第二底层掩膜层108的材料不同,具体地,第一底层掩膜层107的材料可以为氮氧化硅,第二底层掩膜层108的材料可以为含氢氧化硅。

45.可以理解的是,在其他实施例中,底层掩膜层也可以为单层结构。

46.本实施例中,核心层109包括第一核心层110和第二核心层111。第一核心层110的材料包括:氮氧化硅。第二核心层111的材料包括:含氢氧化硅。

47.在其他实施例中,核心层也可以为单层结构。

48.在核心层109上形成图形化的光刻胶层112。

49.参考图2,以图形化的光刻胶层为112(参考图1)为掩膜,刻蚀核心层109(参考图

1),形成多个分立的核心部113。核心部113为双层结构,在其他实施例中,核心部也可以为单层结构。

50.在形成核心部113之后,去除图形化的光刻胶层112。

51.参考图3,形成覆盖核心部113顶部和侧壁以及底层掩膜层106的侧墙膜114。

52.在本实施例中,采用原子层沉积技术沉积侧墙膜114;通过原子层沉积技术形成的侧墙膜114厚度更为均匀。在其他实施例中,可采用化学气相沉积、物理气相沉积等方法形成侧墙膜。

53.侧墙膜114的材料与核心部113的材料不同,例如可以为氧化硅。

54.参考图4,对侧墙膜114(参考图3)进行刻蚀处理,形成位于核心部113的相对的侧壁的侧墙层115。由于刻蚀负载效应,即刻蚀面积越大,越容易被刻蚀,沉积在核心部113侧壁的侧墙膜114(参考图3)不容易被刻蚀,从而形成了侧墙层115。

55.参考图5,去除核心部113(参考图4),侧墙层115作为图形化的掩膜层115。

56.以图形化的掩膜层115为掩膜,刻蚀底层掩膜层106(参考图4),形成图形化的底层掩模层116。本实施例中,图形化的底层掩膜层116为双层结构。在其他实施例中,图形化的底层掩膜层也可以为单层结构。

57.参考图6,以图形化的底层掩膜层116(参考图5)为掩膜,刻蚀伪位线层105(参考图5),形成伪位线结构117。形成伪位线结构117后,去除图形化的底层掩膜层116。

58.在本实施例中,图形化的掩膜层115(参考图4)通过图形化的底层掩膜层116,将图案传递给了伪位线结构117。因此,伪位线结构117的宽度与图形化的掩膜层115的宽度一致,图形化的掩膜层115的宽度越小,伪位线结构117的宽度就越小,进而存储器的尺寸也越小。

59.伪位线结构117的材料包括氮化硅、氮氧化硅或碳氮化硅。伪位线结构117的材料与伪位线接触层101的材料不同。

60.值得注意的是,在其他实施例中,也可以不采用双重图形化工艺形成伪位线结构,例如:直接在伪位线层上形成单层硬掩膜层,对该硬掩膜层进行光刻,形成位于伪位线层上的多个分立的核心部;形成覆盖核心部顶部和侧壁以及伪位线层的侧墙膜;对侧墙膜进行刻蚀处理,形成位于核心部的相对的侧壁的侧墙层;去除核心部,侧墙层为图形化的掩膜层,利用该图形化的掩膜层刻蚀伪位线层,形成伪位线结构。

61.参考图7至图8,在伪位线结构117及伪位线接触层101的侧壁形成介质层118。

62.在后续刻蚀去除牺牲层的过程中,介质层118能够保护位线导电部,保证位线导电部的形貌以及尺寸的精确性。

63.介质层118的材料包括低介电常数材料,低介电常数材料可以减小存储器的寄生电容,提高存储器的运行速率。

64.具体地,本实施例中,形成介质层118的工艺步骤包括:参考图7,在第二隔离层104的表面还形成初始介质膜128;参考图8,去除第二隔离层104表面和伪位线结构117顶部表面的初始介质膜128(参考图7)。

65.参考图9,形成填充相邻伪位线结构117之间的区域的牺牲层119,且牺牲层119位于伪位线结构117侧壁。

66.牺牲层119还覆盖第二隔离层104的表面及介质层118侧壁表面。

67.在其他实施例中,牺牲层还可位于伪位线接触层的侧壁。

68.牺牲层119的材料与介质层118的材料不同,例如可以为氧化硅。

69.参考图10,去除伪位线结构117(参考图9),形成露出伪位线接触层101的通孔。在本实施例中,伪位线结构117的刻蚀速率大于牺牲层119的刻蚀速率,且伪位线结构117的材料与牺牲层119的材料的刻蚀选择比为5-15,例如8、10、13。采用湿法刻蚀的方法去除伪位线结构117,刻蚀溶剂采用热磷酸溶液。在其他实施例中,也可采用干法刻蚀的方法去除伪位线结构。

70.参考图11,去除伪位线接触层101(参考图10),形成位于基底100(参考图5)内的通孔。

71.本实施例中,采用湿法刻蚀去除伪位线接触层101。在其他实施例中,也可采用干法刻蚀去除伪位线接触层。

72.参考图12,形成填充基底100(参考图5)内的通孔的位线接触层125,位线接触层125与有源区102电连接。

73.本实施例中,使用外延生长技术形成位线接触层125,且位线接触层125的材料包括单晶硅。同时,可以对单晶硅掺杂多种离子来提高导电能力。

74.因此,以外延生长技术形成的位线接触层125可以避免刻蚀去除伪位线结构117(参考图9)时造成的损伤或残留的杂质;同时,单晶硅或掺有离子的单晶硅的电阻比多晶硅的电阻更低;如此,可以提高位线接触层125的导电能力,降低位线接触层125与有源区102的接触面的电阻,从而提高存储器的运行速度。

75.参考图13及图14,形成填充通孔且覆盖位线接触层125的位线导电部120。

76.位线导电部120是位线结构中的导电结构。采用填充通孔的方法形成位线导电部,位线导电部120在形成过程中受到牺牲层119的支撑,因此,即使位线导电部120的宽度窄,也不易发生倾斜或坍塌的现象。另外,由于不采用刻蚀工艺,在位线导电部120中不会残留由刻蚀产生的杂质;从而降低位线导电部120的电阻,提高存储器的运行速度。

77.形成位线导电部120的步骤包括:在通孔的底部及侧壁形成阻挡层121;在阻挡层121表面形成填充满通孔的导电层122。

78.在本实施例中,通过原子沉积层沉积技术形成的导电层122以及阻挡层121的厚度更为均匀。在其他实施例,也可采用其他沉积技术。

79.阻挡层121的材料包括氮化钽或氮化钛中的一种或两种。氮化钽或氮化钛能够导电,且具有良好的阻挡能力,能够阻挡导电层122的扩散。导电层122的材料包括钌、钨、金或银中的一种或多种。钌、钨、金或银都属于低电阻金属,能够进一步降低导电层122的电阻,提高存储器的运行速度。

80.在其他实施例中,位线导电部也可以为单层结构。

81.本实施例中,如图13所示,形成导电层122以及阻挡层121还位于牺牲层119顶部表面上;如图14所示,对位线导电部120进行平坦化处理,去除高于牺牲层119顶部表面的导电层122以及阻挡层121(参考图11)。

82.本实施例中,采用化学机械抛光技术对位线导电部120进行平坦化处理。

83.参考图15,在位线导电部120的顶部形成绝缘盖层123。

84.绝缘盖层123作为位线结构中的绝缘结构。

85.本实施例中,采用双重图形化工艺(sadp)形成的绝缘盖层123,双重图形化工艺(sadp)使得形成的绝缘盖层123的尺寸更加精准。

86.参考图16,形成绝缘盖层123后,去除牺牲层119(参考图15)。

87.牺牲层119的刻蚀速率大于绝缘盖层123的刻蚀速率,且牺牲层119的材料与绝缘盖层123的材料的刻蚀选择比为5-15,比如可以为8、10、13。高的刻蚀选择比能够保证在去除牺牲层119的过程中,绝缘盖层123保持原有的形貌和尺寸。本实施例采用湿法刻蚀的方法去除牺牲层119,刻蚀试剂采用氢氟酸溶液。在其他实施例中,也可采用干法刻蚀的方法去除牺牲层。

88.参考图17,在位线导电部120和绝缘盖层123的表面形成保护层124。

89.本实施例中,保护层124还覆盖第二隔离层104的表面及介质层118的表面。

90.在本实施例中,采用原子层沉积技术形成保护层124。

91.保护层124的材料包括碳氮化硅。

92.综上所述,本实施例通过外延生长技术形成位线接触层125,可以避免刻蚀去除伪位线结构117过程中造成损伤和残留杂质;同时,单晶硅的位线接触层125的电阻比多晶硅材料的位线接触层更低,可以减少位线接触层125与有源区102的界面的电阻。如此,存储器的性能更好。

93.本发明第二实施例还提供的一种存储器,该存储器可由第一实施例中的存储器的制造方法制造。图18为本实施例提供的存储器的结构示意图。

94.参考图18,存储器包括:基底200以及多个分立的位线接触层225,基底200内具有多个有源区202,且每一位线接触层225与有源区202电连接;位线导电部205,位线导电部205位于位线接触层225的顶部。

95.以下将结合附图对本实施例提供的存储器进行详细说明。

96.有源区202之间还包括第一隔离层203,第一隔离层203用于隔离有源区202。

97.基底200表面还包括第二隔离层204,第二隔离层204用于隔离位线接触层225。

98.位线接触层225的材料包括单晶硅,或者含有掺杂离子的单晶硅。单晶硅的电阻较低,从而可以降低位线接触层225与有源区102的接触面的电阻。

99.位线导电部205还包括:位于位线接触层225顶部的导电层206;位于位线接触层225与导电层206之间的阻挡层207,阻挡层207还覆盖导电层206的侧壁。

100.导电层206的材料包括钌、钨、金或银中的一种或多种。钌、钨、金或银均为低电阻金属,能够降低导电层206的电阻,提高存储器的运行速度。

101.阻挡层207的材料为导电材料,例如可以为氮化钽或氮化钛。

102.阻挡层207的厚度为2.5-6nm,比如可以为3nm,该厚度的阻挡层207具有良好的阻挡导电层206扩散的能力。

103.位于位线导电部205及位线接触层225侧壁的介质层208;位于位线导电部205顶部的绝缘盖层209;位于绝缘盖层209及介质层208表面的保护层210,保护层210还位于第二隔离层204的表面上。

104.综上所述,本实施例提供的存储器的位线接触层225的材料包括单晶硅,或者含有掺杂离子的单晶硅。单晶硅的电阻较低,从而可以降低位线接触层225与有源区102的接触面的电阻。导电层206的材料为钌、钨、金或银等低电阻材料,导电层206的电阻低,存储器的

运行速度快。另外,本实施例提供的存储器的阻挡层具有良好的阻挡导电层扩散的能力,能够进一步提高存储器的性能。

105.本领域的普通技术人员可以理解,上述各实施方式是实现本发明的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本发明的精神和范围。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各自更动与修改,因此本发明的保护范围应当以权利要求限定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。