1.本技术涉及显示技术领域,具体而言,本技术涉及一种静电环电路、测试电路、阵列基板、显示面板及显示装置。

背景技术:

2.micro led(即微缩化led)显示技术作为目前众多显示技术中的一种具有颠覆性的显示技术,是一种将led微缩至1~10μm(微米),并通过矩阵化技术及巨量转移技术嫁接于显示面板中,以实现高清显示的一种新型显示技术。相比于现有的绝大多数显示技术,micro led显示技术具有高发光效率,高对比度,低功耗等优点。且随着时代的发展与进步,其日渐成为显示领域中的一股新兴力量,并对显示的高端市场产生深刻的影响。

3.通常情况下,显示面板在制程中一般需要经历三个检测阶段,分别为at(array test,阵列检测),ct(cell test,液晶盒检测)以及ft(final test,最终检测),以保证其用户端的最终品质。为了实现at检测,显示面板需要在面板周边设计相应的at pad信号线,以使at设备能接触到相应的面板测试点,实现检测信号的加载,但这些显示面板周边的信号线也成为了后续esd(electro-static discharge,静电释放)高发的风险点。

4.目前,常规的静电环电路主要包括两个tft(thin film transistor,薄膜晶体管),该两个tft形成环形连接方式。但该静电环电路在静电来临时,只能实现一次静电的压降,即正电压结构只能释放正向大电压,负电压结构只能释放负向大电压,导致现有的静电环电路抗静电能力有限。

技术实现要素:

5.本技术针对现有方式的缺点,提出一种静电环电路、测试电路、阵列基板、显示面板及显示装置。

6.第一方面,本技术实施例提供了一种静电环电路,位于显示面板的周边区域,静电环电路包括:依次电连接的静电环电路的第一端、第一开关单元、第三开关单元、第二开关单元和静电环电路的第二端;

7.第一开关单元和第二开关单元均包括两个开关模块;

8.静电环电路的第一端,与第一开关单元中的一个开关模块的控制端和第一端、以及第一开关单元中的另一个开关模块的第二端都电连接;

9.静电环电路的第二端,与第二开关单元中的一个开关模块的控制端和第一端、以及第二开关单元中的另一个开关模块的第二端都电连接;

10.静电环电路的第一端和静电环电路的第二端中的一端用于与显示面板的一个信号线电连接,静电环电路的第一端和静电环电路的第二端中的另一端用于与显示面板的另一个信号线或参考电极走线电连接。

11.第二方面,本技术实施例提供了一种测试电路,位于显示面板的周边区域;显示面板包括显示区域和位于显示区域外围的周边区域;

12.测试电路包括多个信号线、参考电极走线和多个如第一方面的静电环电路;

13.每个静电环电路的第一端和静电环电路的第二端中的一端,与一个信号线电连接;静电环电路的第一端和静电环电路的第二端中的另一端,与另一个信号线或参考电极走线电连接。

14.第三方面,本技术实施例提供了一种阵列基板,包括至少一个如第二方面的测试电路;

15.测试电路位于阵列基板所属显示面板的周边区域。

16.第四方面,本技术实施例提供了一种显示面板,包括如第三方面的阵列基板;

17.测试电路位于显示面板的周边区域;显示面板包括显示区域和位于显示区域外围的周边区域。

18.第五方面,本技术实施例提供了一种显示装置,包括柔性电路板和如第四方面的显示面板;柔性电路板包括柔性连接组件;

19.柔性连接组件的一端与显示面板电连接,柔性连接组件的另一端与柔性电路板电连接。

20.本技术实施例提供的技术方案,至少具有如下有益效果:

21.本技术实施例提供的静电环电路,通过设置依次电连接的三个开关单元,第一开关单元中的两个开关模块与第二开关单元中的两个开关模块交替正反对称电连接,静电环电路中第一开关单元、第三开关单元、第二开关单元,各对静电实现一次压降,使得静电环电路能够实现三次压降使静电从一端到另一端得到了极大的削弱,提升显示面板的抗静电能力,保证显示面板正常显示。

22.本技术附加的方面和优点将在下面的描述中部分给出,这些将从下面的描述中变得明显,或通过本技术的实践了解到。

附图说明

23.本技术上述的和/或附加的方面和优点从下面结合附图对实施例的描述中将变得明显和容易理解,其中:

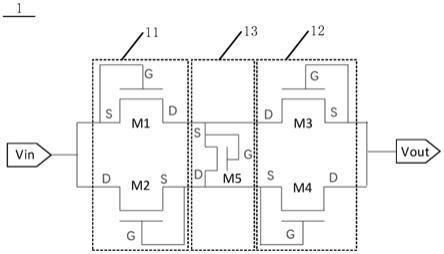

24.图1为本技术实施例提供的一种静电环电路的电路原理示意图;

25.图2为本技术实施例提供的一种显示面板的布局示意图;

26.图3为本技术实施例提供的一种测试电路的电路原理示意图;

27.图4为本技术实施例提供的一种测试电路的静电疏导流程示意图。

28.附图标记:

29.100-显示面板,101-测试电路,102-周边区域,103-显示区域,104-集成电路(ic);

30.200-柔性电路板(fpc),201-柔性连接组件(fpc connector),202-参考电极模块(gnd module);

31.1-静电环电路,11-第一开关单元,12-第二开关单元,13-第三开关单元。

具体实施方式

32.下面详细描述本技术,本技术实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的部件或具有相同或类似功能的部件。此外,如果已知技术的

详细描述对于示出的本技术的特征是不必要的,则将其省略。下面通过参考附图描述的实施例是示例性的,仅用于解释本技术,而不能解释为对本技术的限制。

33.本技术领域技术人员可以理解,除非另外定义,这里使用的所有术语(包括技术术语和科学术语),具有与本技术所属领域中的普通技术人员的一般理解相同的意义。还应该理解的是,诸如通用字典中定义的那些术语,应该被理解为具有与现有技术的上下文中的意义一致的意义,并且除非像这里一样被特定定义,否则不会用理想化或过于正式的含义来解释。

34.本技术领域技术人员可以理解,除非特意声明,这里使用的单数形式“一”、“一个”、“所述”和“该”也可包括复数形式。应该进一步理解的是,本技术的说明书中使用的措辞“包括”是指存在所述特征、整数、步骤、操作、元件和/或组件,但是并不排除存在或添加一个或多个其他特征、整数、步骤、操作、元件、组件和/或它们的组。应该理解,当我们称元件被“连接”或“耦接”到另一元件时,它可以直接连接或耦接到其他元件,或者也可以存在中间元件。此外,这里使用的“连接”或“耦接”可以包括无线连接或无线耦接。这里使用的措辞“和/或”包括一个或更多个相关联的列出项的全部或任一单元和全部组合。

35.本技术的发明人进行研究发现,由于显示面板周边的at pad信号线处于显示面板的边缘区域且裸露在外,这些信号线在后续生产或使用过程中极容易触碰环境、机器或人手,最终成为静电的主要切入点,导致esd高发,造成显示面板和其芯片的损坏。

36.现有技术中,避免显示面板周边的信号线可能会产生esd风险的方式主要包括:

37.1、有些显示面板厂家选择直接舍弃at测试,但会造成产品良率的损失。

38.2、在at测试后,对这些信号线进行激光切割,以杜绝esd的隐患,但这会增加一道工序,导致生产成本的增加。

39.本技术提供的一种静电环电路、测试电路、阵列基板、显示面板及显示装置,旨在解决现有技术的如上技术问题。

40.下面以具体地实施例对本技术的技术方案以及本技术的技术方案如何解决上述技术问题进行详细说明。下面这几个具体的实施例可以相互结合,对于相同或相似的概念或过程可能在某些实施例中不再赘述。下面将结合附图,对本技术的实施例进行描述。

41.首先对本技术涉及的几个名词进行介绍和解释:

42.fpc:flexible printed circuit,柔性电路板。

43.fpc connector:柔性连接组件。

44.ic:integrated circuit,集成电路(芯片)。

45.esd ring:electro-static discharge ring,静电环。

46.panel:显示面板。

47.本技术实施例提供了一种静电环电路1,如图1所示,静电环电路1位于显示面板的周边区域102,静电环电路1包括:依次电连接的静电环电路1的第一端、第一开关单元11、第三开关单元13、第二开关单元12和静电环电路1的第二端。

48.第一开关单元11和第二开关单元12均包括两个开关模块。

49.静电环电路1的第一端,与第一开关单元11中的一个开关模块的控制端和第一端、以及第一开关单元11中的另一个开关模块的第二端都电连接。

50.静电环电路1的第二端,与第二开关单元12中的一个开关模块的控制端和第一端、

以及第二开关单元12中的另一个开关模块的第二端都电连接。

51.静电环电路1的第一端和静电环电路1的第二端中的一端用于与显示面板的一个信号线电连接,静电环电路1的第一端和静电环电路1的第二端中的另一端用于与显示面板的另一个信号线或参考电极走线电连接。

52.可选地,静电环电路1的第一端可以为输入端,相应地静电环电路1的第二端可以为输出端,或者,静电环电路1的第一端可以为输出端,相应地静电环电路1的第二端可以为输入端。

53.可选地,信号线包括测试信号线。

54.可选地,参考电极包括gnd(接地)端子或vss端子等。

55.本技术实施例提供的静电环电路1,通过设置依次电连接的三个开关单元,第一开关单元11中的两个开关模块与第二开关单元12中的两个开关模块交替正反对称电连接,静电环电路中第一开关单元11、第三开关单元13、第二开关单元12,各对静电实现一次压降,使得静电环电路能够实现三次压降使静电从一端(起始端)到另一端(终端)得到了极大的削弱,提升显示面板的抗静电能力,保证显示面板正常显示。

56.在一些实施例中,如图1所示,第三开关单元13的一端,与第一开关单元11中的一个开关模块的第二端、第二开关单元12中的一个开关模块的第二端都电连接。

57.第三开关单元13的另一端,与第一开关单元11中的另一个开关模块的控制端和第一端、以及第二开关单元12中的另一个开关模块的控制端和第一端都电连接。

58.在一些实施例中,第三开关单元13包括:开关模块;开关模块的第一端与开关模块的控制端电连接,并共同作为第三开关单元13的一端;开关模块的第二端作为第三开关单元13的另一端。

59.在一些实施例中,每个开关模块都包括晶体管;晶体管的控制极、第一极、第二极分别作为开关模块的控制端、第一端、第二端。

60.可选地,控制极为晶体管的栅极,第一极为晶体管的源极,第二极为晶体管的漏极;或者,控制极为晶体管的栅极,第一极为晶体管的漏极,第二极为晶体管的源极。可选地,各晶体管均为薄膜晶体管,任一晶体管的控制极为所述薄膜晶体管的栅极;控制极所属的晶体管的第一极为薄膜晶体管的源极,第二极为与第一极相对应的所述薄膜晶体管的漏极。

61.静电环在正常情况下相当于一个大电阻,其两端信号在正常电压范围内互不干扰。而当大电压通过时,静电环结构才会导通,进而可以协助电路进行静电的疏导。

62.在一个示例中,参照图1所示,静电环电路1的第一端为输入端vin,相应地静电环电路1的第二端为输出端vout。第一开关单元11中的一个开关模块包括晶体管m1,第一开关单元11中的另一个开关模块包括晶体管m2。第二开关单元12中的一个开关模块包括晶体管m3,第二开关单元12中的另一个开关模块包括晶体管m4。第三开关单元13中的开关模块包括晶体管m5。晶体管m1至晶体管m5的g表示晶体管的栅极,d表示晶体管的漏极,s表示晶体管的源极。

63.具体的,参照图1所示,每个晶体管的栅极与各自的源极电连接,即晶体管m1的栅极与晶体管m1的源极电连接,晶体管m2的栅极与晶体管m2的源极电连接,晶体管m3的栅极与晶体管m3的源极电连接,晶体管m4的栅极与晶体管m4的源极电连接,晶体管m5的栅极与

晶体管m5的源极电连接。

64.具体的,静电环电路1的输入端vin与晶体管m1的栅极、晶体管m1的源极、晶体管m2的漏极都电连接。静电环电路1的输出端vout与晶体管m3的栅极、晶体管m3的源极、晶体管m4的漏极都电连接。

65.晶体管m5的源极与晶体管m5的栅极、晶体管m1的漏极、晶体管m3的漏极都电连接。晶体管m5的漏极与晶体管m1的漏极、晶体管m3的源极、晶体管m3的栅极、晶体管m4的源极、晶体管m4的栅极都电连接。

66.本技术实施例提供的静电环电路1中第一开关单元11包括2个晶体管(例如,tft管)、第三开关单元13包括1个晶体管(例如,tft管)、第二开关单元12包括2个晶体管(例如,tft管),也就是说,静电环电路1通过5个晶体管交替正反对称的电连接结构,使得第一开关单元11、第二开关单元12和第三开关单元13各对静电实现一次压降,从而静电环电路能够实现三次压降使静电从一端(起始端)到另一端(终端)得到了极大的削弱,提升显示面板的抗静电能力,保证显示面板正常显示。

67.如表一所示,采用本技术优化的静电环(esd ring)设计相比常规的静电环(esd ring)设计,50v以上的漏电流降低了3个数量级,抗静电能力提升了将近1000倍。

68.表一:常规esd ring电路与本技术esd ring电路的抗静电能力对比表

[0069][0070]

表一中,“ ”表示正向,例如图1中,正向表示静电的放电电流从静电环电路的vin被引导流向静电环电路的vout。

[0071]

表一中,

“‑”

表示负向,例如图1中,负向表示静电的放电电流从静电环电路的vout被引导流向静电环电路的vin。

[0072]

表一中,-1.5

·

10-7

表示负1.5乘以10的负7次方;1.7

·

10-7

表示1.7乘以10的负7次方;-2.1

·

10-10

表示负2.1乘以10的负10次方;3.7

·

10-10

表示负3.7乘以10的负10次方。

[0073]

基于同一发明构思,如图2所示,本技术实施例提供了一种测试电路101,位于显示面板100的周边区域102;显示面板100包括显示区域103和位于显示区域103外围的周边区域102。

[0074]

测试电路101包括多个信号线(例如,图2中sw信号线、gate信号线、sd信号线和vcom信号线)、参考电极走线(例如,图2中gnd走线)和多个如上述任意实施例提供的静电环电路1。

[0075]

每个静电环电路1的第一端和静电环电路1的第二端中的一端,与一个信号线电连接;静电环电路1的第一端和静电环电路1的第二端中的另一端,与另一个信号线或参考电极走线电连接。

[0076]

可选地,显示面板100包括集成电路104(如图2中ic)。

[0077]

可选地,多个信号线包括:at(array test,阵列检测)测试时,位于显示面板的周边区域102的at pad信号线。

[0078]

如图2所示,at pad信号线包括sw(总开关)信号线、gate(栅极)信号线、sd(源极)

信号线和vcom(公共电极)信号线。sw(总开关)信号线用于实现所有数据的传递。gate(栅极)信号线为显示面板100中所有栅线的总线。sd(源极)信号线为显示面板100中所有数据线的总线。

[0079]

通常情况下,显示面板100中的信号线位于绝缘层,当进行at测试时,该信号线需要通过跳孔的方式跳到表面的膜层。

[0080]

本实施例提供的测试电路101,各信号线通过静电环电路1串联后电连接至参考电极走线(如图2中gnd),或者,每个信号线都单独配置一个静电环电路1,每个静电环电路1的输出端都直接与参考电极走线(如图2中gnd)电连接。参考电极走线(如图2中gnd)与显示面板100外部的柔性电路板200(如图2中fpc)的参考电极模块202电连接,能够实现显示面板周边静电的疏导,进而减少静电对显示面板及其控制芯片(如图2中ic)的影响。无需舍弃at测试,提高产品良品率,无需在at测试后对这些信号线进行激光切割,能够减小一道工序,减小生产成本。

[0081]

在一些实施例中,每个信号线配置有一个对应的静电环电路1。

[0082]

信号线包括n个,静电环电路1包括n个,n为正整数。

[0083]

第i个静电环电路1的第一端与第i个信号线电连接,第i个静电环电路1的第二端与第i 1个信号线电连接,i为不小于1且小于n的正整数。

[0084]

第n个静电环电路1的第一端与第n个信号线电连接,第n个静电环电路1的第二端与参考电极走线(如图2中gnd)电连接。

[0085]

参考电极走线(如图2中gnd)用于与柔性电路板200(如图2中fpc)的参考电极模块202(如图2中gnd module)电连接。

[0086]

可选地,n为4。

[0087]

如图2所示,sw表示总开关信号线,gate表示栅极信号线,sd表示源极信号线,vcom表示公共电极信号线。sw信号线用于实现所有数据的传递。gate信号线为显示面板中所有栅线的总线。sd信号线为显示面板中所有数据线的总线,gnd表示参考电极走线。

[0088]

如图3所示,虚线箭头表示常规at检测过程中电流的流向(图3中normal array test),实线箭头表示产生静电时电流的流向(图3中when esd happen)。gnd module in fpc表示柔性电路板200的参考电极模块202,panel表示显示面板,esd ring 1~esd ring 4表示4个静电环电路1,即第一静电环电路1、第二静电环电路1、第三静电环电路1和第四静电环电路1。

[0089]

在常规at检测过程中,本技术的测试电路101,由于静电环电路1本身相当于大电阻,因此不会对信号造成影响,各信号正常加载于panel(显示面板)内,实现显示面板的正常检测。

[0090]

然而,当制程中esd产生大电压时,或后续使用过程中esd产生大电压时,静电环电路1会被该大电压打开,从而形成通路,静电会如图3中实线箭头部分所示,在at(array test,阵列检测)各信号pad间进行相互电压分担,并最终通过gnd(参考电极走线)疏导入fpc(柔性电路板200)中的gnd模块(参考电极模块202),实现静电疏导。

[0091]

如图4所示,at pad1至at pad 4表示4个at pad信号线,即第一at pad信号线、第二at pad信号线、第三at pad信号线和第四at pad信号线。esd ring1至esd ring 4表示4个静电环电路1,即第一静电环电路1、第二静电环电路1、第三静电环电路1和第四静电环电

路1。

[0092]

本技术实施例提供的测试电路101,静电会在at pad间进行传导,实现静电的大幅削弱,并最终流入fpc gnd(柔性电路板200的参考电极模块202),能够增强显示面板的抗esd能力,避免了显示面板及其芯片(如图2中ic)的损坏。

[0093]

在一些实施例中,每个信号线通过单独的静电环电路1与参考电极走线电连接;参考电极走线用于与柔性电路板200(如图2中fpc)的参考电极模块202(如图2中gnd module)电连接。

[0094]

基于同一发明构思,本技术实施例提供了一种阵列基板,包括至少一个如上述任一实施例提供的测试电路;测试电路位于阵列基板所属显示面板的周边区域。

[0095]

基于同一发明构思,如图2所示,本技术实施例提供了一种显示面板100,包括至少一个如上述任意实施例提供的阵列基板;

[0096]

测试电路101位于显示面板的周边区域102;显示面板包括显示区域103和位于显示区域103外围的周边区域102。可选地,显示面板为micro-led面板。

[0097]

本技术实施例提供的显示面板100,通过在显示面板100的周边区域设置测试电路101,能够增强显示面板的抗esd能力,避免了显示面板及其芯片(如图2中ic)的损坏。

[0098]

在一些实施例中,如图2所示,测试电路101的数量为两个,以显示区域103的中轴线对称分布。

[0099]

基于同一发明构思,如图2所示,本技术实施例提供了一种显示装置,包括柔性电路板200和如上述任意实施例提供的显示面板100;柔性电路板200包括柔性连接组件201;

[0100]

柔性连接组件201的一端与显示面板100电连接,柔性连接组件201的另一端与柔性电路板200电连接。

[0101]

可选地,柔性连接组件201的一端与显示面板100固定、且电连接,所述柔性连接组件201的另一端与所述柔性电路板200电连接。

[0102]

本技术实施例提供的显示装置,通过在显示面板100的周边区域设置测试电路101,能够增强抗esd能力,避免了显示面板100及其芯片(如图2中ic)的损坏。

[0103]

应用本技术实施例,至少能够实现如下有益效果:

[0104]

(1)本技术实施例提供的静电环电路1,通过设置依次电连接的三个开关单元,第一开关单元11中的两个开关模块与第二开关单元12中的两个开关模块交替正反对称电连接,静电环电路中第一开关单元11、第三开关单元13、第二开关单元12,各对静电实现一次压降,使得静电环电路能够实现三次压降使静电从一端(起始端)到另一端(终端)得到了极大的削弱,提升显示面板的抗静电能力,保证显示面板正常显示。

[0105]

(2)本实施例提供的测试电路101,各信号线通过静电环电路1串联后电连接至参考电极走线(如图2中gnd),或者,每个信号线都单独配置一个静电环电路1,每个静电环电路1的输出端都直接与参考电极走线(如图2中gnd)电连接。参考电极走线(如图2中gnd)与显示面板100外部的柔性电路板200(如图2中fpc)的参考电极模块202电连接,能够实现显示面板周边静电的疏导,进而减少静电对显示面板及其控制芯片(如图2中ic)的影响。无需舍弃at测试,提高产品良品率,无需在at测试后对这些信号线进行激光切割,能够减小一道工序,减小生产成本。

[0106]

本技术领域技术人员可以理解,本技术中已经讨论过的各种操作、方法、流程中的

步骤、措施、方案可以被交替、更改、组合或删除。进一步地,具有本技术中已经讨论过的各种操作、方法、流程中的其他步骤、措施、方案也可以被交替、更改、重排、分解、组合或删除。进一步地,现有技术中的具有与本技术中公开的各种操作、方法、流程中的步骤、措施、方案也可以被交替、更改、重排、分解、组合或删除。

[0107]

术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术的描述中,除非另有说明,“多个”的含义是两个或两个以上。

[0108]

应该理解的是,虽然附图的流程图中的各个步骤按照箭头的指示依次显示,但是这些步骤并不是必然按照箭头指示的顺序依次执行。除非本文中有明确的说明,这些步骤的执行并没有严格的顺序限制,其可以以其他的顺序执行。而且,附图的流程图中的至少一部分步骤可以包括多个子步骤或者多个阶段,这些子步骤或者阶段并不必然是在同一时刻执行完成,而是可以在不同的时刻执行,其执行顺序也不必然是依次进行,而是可以与其他步骤或者其他步骤的子步骤或者阶段的至少一部分轮流或者交替地执行。

[0109]

以上所述仅是本技术的部分实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本技术原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本技术的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。