一种tiadc特殊频率点时间失配误差校准结构及方法

技术领域

1.本发明涉及高速、高精度模数转换技术领域,具体来讲,涉及一种对高速高精度时间交织adc中特殊频率点通道间时间失配误差的校准结构和方法。

背景技术:

2.控阵雷达、5g无线通信试验系统、宽带数字接收机和数字示波器的高速发展正在将系统带宽不断推向更高,显著增加了数据采集系统对高速高精度adc(analog-to-digital converter)的急迫需求。时间交织adc(time-interleaved adc,tiadc)技术是提高采样率的最佳有效途径之一,但是由于工艺偏差,不可避免地引入了通道失配误差效应,主要包括失调失配,增益失配和采样时间失配,并严重降低了tiadc采样系统的性能。因此对通道失配的校准技术是基于tiadc采样系统能否实际应用化的关键所在,也是解决高速高精度采集系统设计的重要技术手段。失调失配和增益失配的全数字校准算法较为简单,通常是基于统计原理估计出各子adc通道的失调或者增益误差大小,然后在子adc输出上直接减去相应的失调系数或者乘以相应的增益系数来实现失调和增益误差的补偿[chen h.,yin y.,deng h.,lin f.a low complexity all-digital background calibration technique for time-interleaved adcs[j].vlsi design,2016,2016:1.]。相比之下,时间失配误差的全数字校准算法较为复杂,也是全数字校准算法的研究重点。已有的针对时间失配误差的全数字校准算法在误差估计方面可分为:基于过零点检测[王晓蕾,王玉莹,陈红梅,尹勇生.基于过零检测的tiadc时钟失配校准算法[j].微电子学与计算机,2016,33(5):72-75.]、基于通道相关性[yiny.s.,liu l.,chen h.m.,deng h.h.,meng x.,wu j.s.,et al.a channel multiplexing digital calibration technique for timing mismatch of time-interleaved adcs.ieice electron.express,2019,16:20190540.]、基于参考点(参考通道、劈分结构)[张睿.时间交叉模数转换器数字校准技术研究[d].合肥工业大学,2012.]、基于调制构造频谱相关性[qiuy.,liu y.j.,zhou j.,zhang g.,chen d.,du n.all-digital blind background calibration technique for any channel time-interleaved adc[j].ieee transactions on circuits and systems i:regular papers,2018,65:2503-2514.];在误差补偿方面可分为:基于分数延迟滤波器(多为farrow结构)[刘艳茹,田书林,王志刚,潘卉清.一种基于farrow滤波器的并行采样时间误差校正[j].电子测量与仪器学报,2010,024(001):50-54.]、基于泰勒插值[yin y.,sun k.,chen h.,wang x.,liu l.,deng h.,et al.calibration of timing mismatch in tiadc based on monotonicity detecting of sampled data.ieice electron.express,2020,17:20190699]、基于调制构造伪杂散信号[matsuno j.,yamaji t.,furuta m.,itakura t.all-digital background calibration technique for time-interleaved adc using pseudo aliasing signal[j].ieee transactions on circuits and systems i:regularpapers,2013,60(5):1113-1121.]。但大多数的全数字后台校准技术都具有一个缺陷,就是在与子adc奈奎斯特频率成倍数的特殊频率点不能正确的实行校准。传统的解决办

法是在提取模块的前面加上一个陷波滤波器[matsuno j.,yamaji t.,furuta m.,itakura t.all-digital background calibration technique for time-interleaved adc using pseudo aliasing signal[j].ieee transactions on circuits and systems i:regularpapers,2013,60(5):1113-1121.],将这些特殊频率点滤除。然而这种方法只能防止当输入信号是特殊频率点时校准不会出现误校准的情况,而实际上由特殊频率点引入的失配杂散并没有得到消除。

技术实现要素:

[0003]

本发明的目的在于克服现有技术的不足,提供一种新的tiadc特殊频率点时间失配误差校准结构及方法,具有如下特征:可完成tiadc特殊频率点实时检测并利用数字滤波器完成补偿,整个校准过程在纯数字域进行,能够应用于任意通道数的tiadc通道失配误差校准。

[0004]

本发明为解决技术问题采用如下技术方案:

[0005]

本发明一种tiadc特殊频率点时间失配误差校准结构及方法,其特点是:

[0006]

该全数字校准结构包括:数据复合模块、特殊频率点检测模块组、特殊频率判定逻辑模块、滤波器模块组、选通复合输出模块;其中,数据复合模块对外部输入的模拟信号x进行数据转换处理,得到第n次采样的m个通道的输出信号;特殊频率点检查模块对特殊频率点进行检测;特殊频率判定逻辑模块对特殊频率点检测模块输出结果进行判断,可以得到特殊频率点具体位置;选通复合模块根据频率点位置选通滤波器模块组中的合适滤波器模块电路对特殊频率点引入杂散信号进行滤除,得到最后校准后输出。

[0007]

本发明一种tiadc特殊频率点时间失配误差校准结构及方法是按如下步骤实现:

[0008]

a、所述数据复合模块对外部输入的模拟信号x进行数据转换处理,得到第n次采样的m个通道的输出信号{y1(n),y2(n),

…

,yi(n),

…

,ym(n)},其中yi(n)表示第n次采样的第i个通道的输出信号,再将第n次采样的m个通道的输出信号{y1(n),y2(n),

…

,yi(n),

…

,ym(n)}进行复合处理得到第n次采样的复合输出信号y(n)并传递给所述选通复合输出模块;i=1,2,

…

,m;

[0009]

b、所述特殊频率点检测模块组,对于m通道tiadc,输入特殊频率点满足f

in

=kfs/2m,k=1,2,3,4,

…

,m-1,时间失配误差出现频率点会跟输入信号频率点重合,从而无法进行误差点正确估计,因此所述特殊频率点检测模块组包含m-1个特殊频率点检测模块,每个频率点检测模块均包括一个加法器、绝对值、平均器和一个比较逻辑。首先加法器是让复合输出信号y与其延迟的信号做差,然后对加法器的结果先取绝对值和求平均,最后把求平均结果跟比较器的阈值进行比较输出;

[0010]

c、所述特殊频率判定逻辑模块,它以所述特殊频率点检测模块组所有比较输出进行逻辑运算输出,得到特殊频率点准确位置;

[0011]

d、所述滤波器模块组,根据特殊频率点输入时对应的输出频谱位置关系,合理设置数字滤波器带宽,使信号在带宽内受保护,而使杂散频率分量处在滤波器的阻带被滤除,从而达到校准的目的。所述特殊频率点检测模块组包含m-1个特殊频率点检测模块,对应m-1个特殊频率点。

[0012]

e、所述选通复合输出模块,依据所述特殊频率判定逻辑模块输出结果,选通所述

滤波器模块组中的滤波器模块,然后从所述数据复合模块y(n)通过滤波器处理的结果y

cal

(n)作为系统最终的校准后的数据。

[0013]

与已有技术相比,本发明有益效果体现在:

[0014]

本发明一种tiadc特殊频率点时间失配误差校准结构及方法克服传统全数字校准结构在特殊频率点输入时无法校准的问题,整个校准结构纯数字域完成,结构简单,且不受通道数限制,可以用于校准任意通道数量的tiadc。

附图说明

[0015]

图1是时间交织adc中通道误差模型示意图;

[0016]

图2是本发明原理框图;

[0017]

图3是本发明特殊频率点检测模块的原理框图;

[0018]

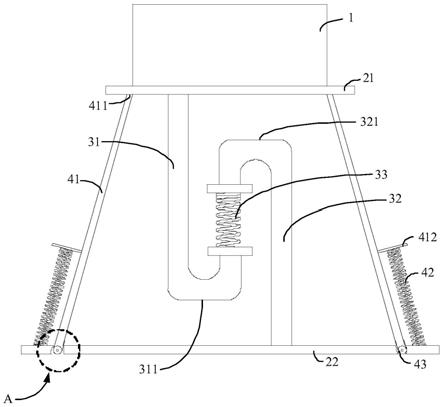

图4是4通道tiadc特殊频率点校准原理框图;

[0019]

图5是4通道tiadc特殊频率点采样情况示意图;

[0020]

图6是4通道tiadc特殊频率点杂散频谱位置关系图;

[0021]

图7是图4中三种滤波器的频率响应;

[0022]

图8是图4中fs/8特殊频率输入时校准前后的频谱图;

[0023]

图9是图4中3fs/4特殊频率输入时校准前后的频谱图;

[0024]

图10是图4中3fs/8特殊频率输入时校准前后的频谱图。

具体实施方式

[0025]

以将本发明应用在4个子通道adc通道构成的采样速率为640mhz的tiadc为例,各个子adc通道采样信号误差模型如图1所示,实施步骤如下:

[0026]

a、所述数据复合模块对外部输入的模拟信号x进行数据转换处理,得到第n次采样的4个通道的输出信号{y1(n),y2(n),y3(n),y4(n)},其中yi(n)表示第n次采样的第i(i=1,2,

…

,4)个通道的输出信号,再将第n次采样的4个通道的输出信号进行复合处理得到第n次采样的复合输出信号y(n)并传递给所述选通复合输出模块;

[0027]

b、对于4通道tiadc,所述特殊频率点检测模块组包含三个检测模块,分别来检测输入信号频率为fs/8、fs/4和3fs/8,如图4所示。当输入信号为fs/4时,此时输入信号的频率等于子通道的采样频率,即此时单通道每一个周期的采样值是一样的,如图5(a)所示;当输入信号是fs/8或者3fs/8,此时输入信号频率是单通道的采样频率的一半或者3/2,因此单通道每两个周期的采样值相同,如图5(b)和5(c)所示。因此只要判断子通道的隔一个采样点的输出是否相等,当然首先要排除不是fs/4,就可以判断输入信号是否为fs/8或者3fs/8的单频信号。判断了之后,需要做第二次判断来区分fs/8或者3fs/8。依据此特点,每个检测模块包括一个加法器、绝对值、平均器和一个比较逻辑,如图3所示。首先加法器是让复合输出信号y(n)与其延迟4个采样周期ts后的信号做差,相当让子通道内部的相邻采样点作差。当输入信号为fs/4时,加法器的输出应该为0,然而考虑到有时钟抖动或者其他的一些噪声存在,导致不会完全等于0,所以需要对加法器的结果先取绝对值和求平均,然后再设置一个接近0的阈值(图4中为0.001)作为比较。观察图5(b)和图5(c)发现fs/8和3fs/8的区别就是相邻通道相邻采样点的幅值差值的大小,对于fs/8来说,此时它们之间的差值不超过信

号摆幅一半的采样点占绝大部分,而对于3fs/8情况相反。因此在图4中,子通道的隔一个采样点的输出是否相等(fs/8或者3fs/8的单频信号的判断逻辑)通过让y(n)与其延迟8个ts后的信号相减来判断;相邻通道的点的间隔的大小是否超过信号摆幅的一半(区分fs/8和3fs/8单频信号的逻辑)由让y(n)与其延迟1个ts后的信号相减来判断。

[0028]

c、针对特殊频率点输入时的通道失配误差的校准,本发明通过低通滤波器1、低通滤波器2和带通滤波器等三个滤波器来实现。根据通道失配误差原理,当输入信号的频率确定时,由通道失配误差造成杂散频谱位置也是确定的。因此在四通道tiadc中,对于fs/8、fs/4和3fs/8等特殊频率点,它们通道失配误差杂散频谱位置关系图如图6所示。图6中的虚线表示与信号主频重叠的一部分杂散分量,但这部分杂散分量只是对信号的相位和幅值造成一定的影响,不会带来非线性的问题也不影响系统的动态性能,因此可不校准。故根据图6的频谱位置关系,合理设置低通滤波器或者带通滤波器的带宽,使信号在带宽内受保护,而使杂散频率分量处在滤波器的阻带被滤除,从而达到校准的目的。因此分别针对fs/4、fs/8和3fs/8校准的低通滤波器1、低通滤波器2和带通滤波器的频率响应范围如图7所示。这些滤波器的阶数分别为10、28、30。

[0029]

d、所述特殊频率判定逻辑模块包含三个判断逻辑,三个判断逻辑产生的高低电平分别控制三个级联的2选1电路,使得最后一级的2选1电路会输出有bit“0”、bit“1”,bit“2”、bit“3”四种可能的比特逻辑。其中bit“0”代表正常频率的输入信号,bit“1”代表频率为fs/4的特殊频率输入信号,bit“2”代表频率为fs/8的特殊频率输入信号,bit“3”代表频率为3fs/8的特殊频率输入信号。

[0030]

e.最后,通过这些比特逻辑选通复合信号y(n),经过非特殊频率点校准算法或者滤波器组处理的结果作为系统最终的校准后的数据y

cal

(n)。

[0031]

图8、图9、图10是图4实施例中分别针对fs/8、fs/4和3fs/8特殊频率点输入进行仿真验证结果,可以看出,输入经过滤波器校准后,其输出频谱中的杂散频谱得到有效抑制并压至噪底附近,系统的动态性能得到有效提升,其中系统的sndr提升42db以上,sfdr提升65db以上,enob提升7bit以上,充分证明该校准结构和方法的有效性。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。