1.本发明是关于一种驱动电路及驱动方法,特别系关于一种包含脉幅调变电路以及脉宽调变电路的驱动电路及驱动方法。

背景技术:

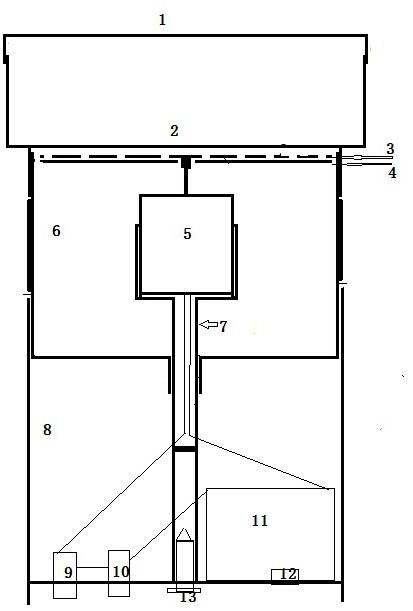

::2.显示器上不同位置的薄膜晶体管(thin-filmtransistors,tfts)所接收的驱动信号会有不同的延迟,因而产生亮度不均的问题。特别是在低灰阶度(graylevel)的情形下,亮度的一致性将可能降至80%以下。由于无法于同时切断不同位置薄膜晶体管的驱动信号,必须以他法解决显示器面板亮度不均的问题。技术实现要素:3.本揭示内容的一实施例提出一种驱动电路,包含脉幅调变电路以及脉宽调变电路。脉幅调变电路用以控制驱动信号的大小。脉宽调变电路用以控制驱动信号的持续时间。脉幅调变电路包含第一晶体管、第一电容以及第二晶体管。脉宽调变电路包含第二电容、第三晶体管以及第四晶体管。第一电容其第一端电性连接第一晶体管的栅极端。第二晶体管,其第一端电性连接第一电容的第一端,其第二端电性连接第一晶体管的第二端。第三晶体管其栅极端电性连接第二电容的第二端。第四晶体管其第一端电性连接第三晶体管的栅极端,其第二端电性连接第三晶体管的第二端,其栅极端电性连接第二晶体管的栅极端并用以接收第一控制信号。4.本揭示内容的一实施例另提出一种驱动方法,包含:在第一模式下,调变脉宽调变电压馈入端的电压,并固定脉幅调变电压馈入端的电压;以及在第二模式下,固定脉宽调变电压馈入端的电压,调变脉幅调变电压馈入端的电压。其中,脉宽调变电压馈入端的电压控制驱动信号的持续时间,脉幅调变电压馈入端的电压控制驱动信号的大小。附图说明5.为使本揭露的上述和其他目的、特征、优点与实施例能更明显易懂,所附图式的说明如下:6.图1为根据本揭示内容一实施例的驱动电路的电路架构图。7.图2为根据本揭示内容一实施例的图1中的驱动电路的控制信号时序图。8.图3a为根据本揭示内容一实施例的图1中的驱动电路在重置期间中的电路状态图。9.图3b为根据本揭示内容一实施例的图1中的驱动电路在数据写入期间中的电路状态图。10.图3c为根据本揭示内容一实施例的图1中的驱动电路在开启电流路径期间中的电路状态图。11.图3d为根据本揭示内容一实施例的图1中的驱动电路在发光期间中的电路状态图。12.图4a为根据本揭示内容一实施例的驱动电路的电路架构图。13.图4b为根据本揭示内容一实施例的图4a中的驱动电路在第一模式下的控制信号时序图。14.图4c为根据本揭示内容一实施例的图4a中的驱动电路在第二模式下的控制信号时序图。15.图4d为根据本揭示内容一实施例的第一模式及第二模式下的驱动电流-时间关系图。16.图5a为根据本揭示内容一实施例的驱动电路的电路架构图。17.图5b为根据本揭示内容一实施例的图5a中的驱动电路在第一模式下的控制信号时序图。18.图5c为根据本揭示内容一实施例的图5a中的驱动电路在第二模式下的控制信号时序图。19.图6a为根据本揭示内容一实施例的驱动电路的电路架构图。20.图6b为根据本揭示内容一实施例的驱动电路的电路架构图。21.图6c为根据本揭示内容一实施例的图6a中的驱动电路在第一模式下的控制信号时序图。22.图6d为根据本揭示内容一实施例的图6a中的驱动电路在第二模式下的控制信号时序图。23.图7为根据本揭示内容一实施例的驱动方法的流程图。24.其中,附图标记:25.100:驱动电路26.100’:驱动电路27.400:驱动电路28.500:驱动电路29.600:驱动电路30.700:驱动方法31.c1:第一电容32.c2:第二电容33.c3:第三电容34.c4:第四电容35.em:发光信号36.emc:发光控制电路37.emd:发光装置38.ic1:第一集成电路39.ic2:第二集成电路40.ic3:第三集成电路41.ic4:第四集成电路42.led:发光二极管43.m1r、m1g、m1b:第一多工器44.m2r、m2g、m2b:第二多工器45.m3r、m3g、m3b:第三多工器46.m4r、m4g、m4b:第四多工器47.p1:重置期间48.p2:数据写入期间49.p3:开启电流路径期间50.p4:发光期间51.pam:脉幅调变电路52.pg:第一控制信号53.pxr、pxg、pxb:子像素驱动电路54.pwm:脉宽调变电路55.rst:重置信号56.s710、s720:步骤57.sic1:信号58.sic2:信号59.sic3:信号60.sic4:信号61.sigr1、sigg1、sigb1、sigr2、sigg2、sigb2:信号62.sigr3、sigg3、sigb3、sigr4、sigg4、sigb4:信号63.sigr5、sigg5、sigb5、sigr6、sigg6、sigb6:信号64.set:设定信号65.sm1r、sm1g、sm1b、sm2r、sm2g、sm2b:控制信号66.sm3r、sm3g、sm3b:控制信号67.sm4r、sm4g、sm4b:控制信号68.sp:第三控制信号69.sp1:第四控制信号70.sp2:第五控制信号71.swp:第二控制信号72.t1:第一晶体管73.t2:第二晶体管74.t3:第三晶体管75.t4:第四晶体管76.t5:第五晶体管77.t6:第六晶体管78.t7:第七晶体管79.t8:第八晶体管80.t9:第九晶体管81.t10:第十晶体管82.t11:第十一晶体管83.t12:第十二晶体管84.t13:第十三晶体管85.t14r、t14g、t14b:第十四晶体管86.t15r、t15g、t15b:第十五晶体管87.t16r、t16g、t16b:第十六晶体管88.t17r、t17g、t17b:第十七晶体管89.t18r、t18g、t18b:第十八晶体管90.t19r、t19g、t19b:第十九晶体管91.t20:第二十晶体管92.t21:第二十一晶体管93.t22:第二十二晶体管94.t23:第二十三晶体管95.vdd:第一系统电压端96.vpam:脉幅调变电压馈入端97.vpwm:脉宽调变电压馈入端98.vset:第三系统电压端99.vss:第二系统电压端具体实施方式100.下列系举实施例配合所附图示做详细说明,但所提供的实施例并非用以限制本揭露所涵盖的范围,而结构运作的描述非用以限制其执行顺序,任何由元件重新组合的结构,所产生具有均等功效的装置,皆为本揭露所涵盖的范围。另外,图示仅以说明为目的,并未依照原尺寸作图。为使便于理解,下述说明中相同元件或相似元件将以相同的符号标示来说明。101.在全篇说明书与申请专利范围所使用的用词(terms),除有特别注明除外,通常具有每个用词使用在此领域中、在此揭露的内容中与特殊内容中的平常意义。102.于本文中,除非内文对于冠词有特别限定,否则“一”与“该”可泛指单一个或多个。此外,本文使用的“包含”、“包括”、“具有”、以及相似词汇,系用以指明所记载的特征、区域、整数、步骤、操作、元件及/或组件,惟其并不排除其所述的或额外的一个或多个特征、区域、整数、步骤、操作、元件、组件、及/或其中的群组。又,本文以下使用的“及/或”的词汇,系包含了列出的关联项目中的一个或多个的任何组合。103.于本文中,当一元件被描述为系“连接”、“耦接”或“电性连接”至另一元件时,该元件可为直接连接、直接耦接或直接电性连接至该另一元件,亦可为该二元件之间有一额外元件存在,而该元件间接连接、间接耦接或间接电性连接至该另一元件。然而,当一元件被描述为系“直接连接”、“直接耦接”或“直接电性连接”至另一元件时,该二元件应被理解为其中是没有额外元件存在的。此外,当一元件被描述为系“连线”、“通讯连接”至另一元件时,该元件可为通过其他元件而间接与另一元件进行有线与/或无线通讯,亦可为一元件无须通过其他元件而实体连接至另一元件。此外,虽然本文中使用“第一”、“第二”、…等用语描述不同元件,该用语仅是用以区别以相同技术用语描述的元件或操作。104.本揭示内容揭露一种驱动电路。请参照图1,图1为根据本揭示内容一实施例的驱动电路100的电路架构图。驱动电路100包含脉幅调变电路pam及脉宽调变电路pwm。脉幅调变电路pam用以控制驱动信号的大小,脉宽调变电路pwm用以控制驱动信号的持续时间,驱动信号用以驱动发光二极管。在一实施例中,驱动信号用以驱动微型发光二极管(microlightemittingdiode)。脉幅调变电路pam包含第一晶体管t1、第一电容c1以及第二晶体管t2。如图1所示,第一晶体管t1的栅极端、第一电容c1的第一端以及第二晶体管t2的第一端相互电性连接,第二晶体管t2的第二端电性连接第一晶体管t1的第二端。脉宽调变电路pwm包含第二电容c2、第三晶体管t3以及第四晶体管t4。如图1所示,第三晶体管t3的栅极端、第二电容c2的第二端以及第四晶体管t4的第一端相互电性连接,第四晶体管t4的第二端电性连接第三晶体管t3的第二端,第四晶体管t4的栅极端电性连接第二晶体管t2的栅极端且用以接收第一控制信号pg。105.在一实施例中,脉幅调变电路pam进一步包含第五晶体管t5、第六晶体管t6以及第七晶体管t7,脉宽调变电路pwm进一步包含第八晶体管t8、第九晶体管t9以及第十晶体管t10。如图1所示,第五晶体管t5的第一端、第一晶体管t1的第一端以及第六晶体管t6的第一端相互电性连接,第五晶体管t5的栅极端用以接收发光信号em,第五晶体管t5的第二端、第一电容c1的第二端以及第七晶体管t7的第一端相互电性连接,第六晶体管t6的栅极端用以接收发光信号em,第六晶体管t6的第二端电性连接第一系统电压端vdd,第七晶体管t7的第二端电性连接第一系统电压端vdd;第八晶体管t8的第一端电性连接第一系统电压端vdd,第八晶体管t8的栅极端用以接收发光信号em,第八晶体管t8的第二端、第十晶体管t10的第一端以及第三晶体管t3的第一端相互电性连接,第十晶体管t10的栅极端用以接收发光信号em,第十晶体管t10的第二端、第九晶体管t9的第二端以及第二电容c2的第一端相互电性连接,第九晶体管t9的第一端电性连接第一系统电压端vdd。106.在一实施例中,脉幅调变电路pam进一步包含第十一晶体管t11,脉宽调变电路pwm进一步包含第十二晶体管t12以及第三电容c3。如图1所示,第十一晶体管t11的第一端电性连接脉幅调变电压馈入端vpam,第十一晶体管t11的第二端、第一晶体管t1的第一端、第五晶体管t5的第一端以及第六晶体管t6的第一端相互电性连接,第十二晶体管t12的第一端电性连接脉宽调变电压馈入端vpwm,第十二晶体管t12的第二端、第八晶体管t8的第二端、第十晶体管t10的第一端以及第三晶体管t3的第一端相互电性连接,第三电容c3的第一端、第二电容c2的第二端、第三晶体管t3的栅极端以及第四晶体管t4的第一端相互电性连接,第三电容c3的第二端用以接收第二控制信号swp。107.在一实施例中,如图1所示,第七晶体管t7、第九晶体管t9、第十一晶体管t11及第十二晶体管t12各自的栅极端皆用以接收第三控制信号sp。108.在一实施例中,驱动电路100进一步包含发光控制电路emc以及发光装置emd,发光装置emd包含第十三晶体管t13及发光二极管led。如图1所示,发光控制电路emc电性连接脉幅调变电路pam及脉宽调变电路pwm,第十三晶体管t13的第一端电性连接发光控制电路emc,第十三晶体管t13的栅极端用以接收发光信号em,发光二极管led的阳极端电性连接第十三晶体管t13的第二端,发光二极管led的阴极端电性连接第二系统电压端vss。在一实施例中,脉幅调变电路pam用以控制流经发光二极管led的电流大小,脉宽调变电路pwm用以控制开启至关断发光二极管led电流的时间。109.在一实施例中,发光控制电路emc进一步包含第二十晶体管t20、第二十一晶体管t21、第二十二晶体管t22、第二十三晶体管t23以及第四电容c4。如图1所示,第二十晶体管t20的第一端、第一晶体管t1的第二端及第二晶体管t2的第二端相互电性连接,第二十晶体管t20的栅极端、第三晶体管t3的第二端、第四晶体管t4的第二端、第二十一晶体管t21的第一端、第二十二晶体管t22的第一端以及第四电容c4的第一端相互电性连接,第二十晶体管t20的第二端、第十三晶体管t13的第一端及第二十三晶体管t23的第一端相互电性连接,第二十一晶体管t21的栅极端用以接收重置信号rst,第二十一晶体管t21的第二端电性连接第三系统电压端vset,第二十二晶体管t22的栅极端用以接收设定信号set,第二十二晶体管t22的第二端电性连接第三系统电压端vset并与第四电容c4的第二端以及第二十三晶体管t23的第二端相互电性连接,第二十三晶体管t23的栅极端用以接收重置信号rst。110.在一实施例中,驱动电路100中使用的晶体管皆为p型晶体管(p-typetransistor),当其栅极端受有低电位或低逻辑电平时,其源极端至漏极端间将被导通。111.在一实施例中,驱动电路100依序操作于重置期间p1、数据写入期间p2、开启电流路径期间p3以及发光期间p4。请参照图2,图2为根据本揭示内容一实施例的图1中的驱动电路100的控制信号时序图。在重置期间p1内,重置信号rst具有低逻辑电平,第一控制信号pg具有低逻辑电平,第三控制信号sp具有高逻辑电平,设定信号set具有高逻辑电平,发光信号em具有高逻辑电平,第二控制信号swp具有高逻辑电平。112.请接着参照图3a,图3a为根据本揭示内容一实施例的图1中的驱动电路100在重置期间p1中的电路状态图。在重置期间p1内,根据前述重置信号rst、第一控制信号pg、第三控制信号sp、设定信号set、发光信号em以及第二控制信号swp的逻辑电平,第十一晶体管t11、第十二晶体管t12、第六晶体管t6、第八晶体管t8、第五晶体管t5、第十晶体管t10、第七晶体管t7、第九晶体管t9、第十三晶体管t13以及第二十二晶体管t22为关闭状态,第四晶体管t4、第二十一晶体管t21、第二晶体管t2、第二十晶体管t20以及第二十三晶体管t23为导通状态。113.在重置期间p1内,第三系统电压端vset的电压电平通过第二十一晶体管t21及第四晶体管t4传送至第三晶体管t3的栅极端,使得第三晶体管t3栅极端的电压电平实质等于第三系统电压端vset的电压电平,此外,第三系统电压端vset的电压电平通过第二十三晶体管t23、第二十晶体管t20及第二晶体管t2传送至第一晶体管t1的栅极端,使得第一晶体管t1栅极端的电压电平实质等于第三系统电压端vset的电压电平。因此,在重置期间p1内,驱动电路100将第三晶体管t3栅极端及第一晶体管t1栅极端的电压电平重置为实质等于第三系统电压端vset的电压电平,以利进行驱动电路100进行后续的发光操作。在一实施例中,第三系统电压端vset的电压电平为低电位。114.请再参照图2。在数据写入期间p2内,重置信号rst具有高逻辑电平,第一控制信号pg具有低逻辑电平,第三控制信号sp具有低逻辑电平,设定信号set具有高逻辑电平,发光信号em具有高逻辑电平,第二控制信号swp具有高逻辑电平。115.请接着参照图3b,图3b为根据本揭示内容一实施例的图1中的驱动电路100在数据写入期间p2中的电路状态图。在数据写入期间p2内,根据前述重置信号rst、第一控制信号pg、第三控制信号sp、设定信号set、发光信号em以及第二控制信号swp的逻辑电平,第六晶体管t6、第八晶体管t8、第五晶体管t5、第十晶体管t10、第二十晶体管t20、第二十一晶体管t21、第二十二晶体管t22、第二十三晶体管t23以及第十三晶体管t13为关闭状态,第七晶体管t7、第九晶体管t9、第十二晶体管t12、第三晶体管t3、第四晶体管t4、第十一晶体管t11、第一晶体管t1以及第二晶体管t2为导通状态。116.在数据写入期间p2内,第一系统电压端vdd的电压电平通过第七晶体管t7传送至第一电容c1的第二端,并通过第九晶体管t9传送至第二电容c2的第一端,使得第一电容c1第二端以及第二电容c2第一端的电压电平实质等于第一系统电压端vdd的电压电平。同时,脉幅调变电压馈入端vpam的电压电平通过第十一晶体管t11、第一晶体管t1以及第二晶体管t2传送至第一晶体管t1的栅极端(亦为第一电容c1的第一端),使得第一晶体管t1栅极端的电压电平实质等于脉幅调变电压馈入端vpam的电压电平。同时,脉宽调变电压馈入端vpwm的电压电平将通过第十二晶体管t12、第三晶体管t3以及第四晶体管t4传送至第三晶体管t3的栅极端(亦为第二电容c2的第二端),使得第三晶体管t3栅极端的电压电平实质等于脉宽调变电压馈入端vpwm的电压电平。117.请再参照图2。在开启电流路径期间p3内,重置信号rst具有高逻辑电平,第一控制信号pg具有高逻辑电平,第三控制信号sp具有高逻辑电平,设定信号set具有低逻辑电平,发光信号em具有高逻辑电平,第二控制信号swp具有高逻辑电平。118.请接着参照图3c,图3c为根据本揭示内容一实施例的图1中的驱动电路100在开启电流路径期间p3中的电路状态图。在开启电流路径期间p3内,根据前述重置信号rst、第一控制信号pg、第三控制信号sp、设定信号set、发光信号em以及第二控制信号swp的逻辑电平,第十一晶体管t11、第十二晶体管t12、第六晶体管t6、第八晶体管t8、第五晶体管t5、第十晶体管t10、第七晶体管t7、第九晶体管t9、第二晶体管t2、第四晶体管t4、第二十一晶体管t21、第二十三晶体管t23以及第十三晶体管t13为关闭状态,第二十二晶体管t22为导通状态。119.在开启电流路径期间p3内,第三系统电压端vset的电压电平通过第二十二晶体管t22传送至第二十晶体管t20的栅极端,使得第二十晶体管t20栅极端的电压电平实质等于第三系统电压端vset的电压电平。因此,在开启电流路径期间p3内,第二十晶体管t20的栅极端具有低电位,第二十晶体管t20因而被导通。120.请再参照图2。在发光期间p4内,重置信号rst具有高逻辑电平,第一控制信号pg具有高逻辑电平,第三控制信号sp具有高逻辑电平,设定信号set具有高逻辑电平,发光信号em具有低逻辑电平,第二控制信号swp具有由高至低下降的逻辑电平。在一实施例中,第二控制信号swp具有三角波的波形。121.请接着参照图3d,图3d为根据本揭示内容一实施例的图1中的驱动电路100在发光期间p4中的电路状态图。在发光期间p4内,根据前述重置信号rst、第一控制信号pg、第三控制信号sp、设定信号set、发光信号em以及第二控制信号swp的逻辑电平,第十一晶体管t11、第十二晶体管t12、第七晶体管t7、第九晶体管t9、第二晶体管t2、第四晶体管t4、第二十一晶体管t21、第二十二晶体管t22以及第二十三晶体管t23为关闭状态,第六晶体管t6、第一晶体管t1、第二十晶体管t20、第十三晶体管t13、第八晶体管t8、第三晶体管t3、第五晶体管t5以及第十晶体管t10为导通状态。122.在发光期间p4内,第一系统电压端vdd的电压电平通过第六晶体管t6、第一晶体管t1、第二十晶体管t20及第十三晶体管t13传送至发光二极管led的阳极端,以产生驱动信号来驱动发光二极管led进行发光。在发光期间p4的初始,第二控制信号swp为高逻辑电平,且第三晶体管t3为关闭状态;而在发光期间p4内,由于第三电容c3电性连接第三晶体管t3的栅极端,随着第二控制信号swp降低,第三晶体管t3栅极端的电压电平亦会开始降低,而当第三晶体管t3栅极端的电压电平降低至一定程度时,第三晶体管t3即会被导通,第一系统电压端vdd的电压电平将会通过第八晶体管t8及第三晶体管t3传送至第二十晶体管t20的栅极端。当第二十晶体管t20栅极端的电压电平升高至一定程度时,第二十晶体管t20即会被关闭,发光二极管led亦不再进行发光。脉宽调变电路pwm即是通过以上机制来关断脉幅调变电路pam所提供用以驱动发光二极管led的电流。123.此外,在发光期间p4内,当电流流经发光二极管led时驱动电路100将出现大的电压降(irdrop),此时通过第一电容c1耦合至第一晶体管t1的栅极端以及通过第二电容c2耦合至第三晶体管t3的栅极端,将可补偿如此的电压降情形。详细言之,第一系统电压端vdd的电压电平通过第六晶体管t6及第五晶体管t5传送至第一电容c1的第二端,因此第一电容c1的第一端可与第二端维持在与数据写入期间p2时相同的电压差,使第一晶体管t1的栅极漏极电压差(vgd)不因电压降而产生变异;第一系统电压端vdd的电压电平将通过第八晶体管t8及第十晶体管t10传送至第二电容c2的第一端,因此第二电容c2的第一端与第二端将可维持在与数据写入期间p2时相同的电压差,使第三晶体管t3的栅极漏极电压差不因电压降而产生变异。因此,第一电容c1可以稳定第一晶体管t1栅极端的电压电平,第二电容c2可以稳定第一晶体管t3栅极端的电压电平,进而补偿驱动电路100的电压降。124.综上所述,驱动电路100通过以上电路配置及信号传输方式可达到稳压的功效并防止电压降对驱动电路100造成的影响。125.在一实施例中,驱动电路100具有两种驱动模式,并根据不同的灰阶度(graylevel)来决定使用哪一种驱动模式。驱动模式包含第一模式及第二模式,在一实施例中,在八位元灰阶(8-bitgrayscale)下,当灰阶度大于等于第十一阶(l11)时,驱动电路100使用第一模式来驱动发光二极管led,当灰阶度小于第十一阶时,驱动电路100使用第二模式来驱动发光二极管led。应注意的是,前述实施例中的第十一阶不应被理解为限制本揭示内容,本

技术领域:

:中具有通常知识者可根据实际需求及/或显示器的设计,决定应在何种的条件下切换为不同模式。126.承前实施例,在第一模式下,脉宽调变电压馈入端vpwm的电压为可调变的(adjustable),脉幅调变电压馈入端vpam的电压为固定的;在第二模式下,脉宽调变电压馈入端vpwm的电压为固定的,脉幅调变电压馈入端vpam的电压为可调变的。换言之,在第一模式下,脉宽调变电路pwm以可调变的脉宽调变电压馈入端vpwm电压来控制驱动信号的持续时间(亦即控制何时关闭发光二极管led),脉幅调变电路pam以固定的脉幅调变电压馈入端vpam电压来控制驱动信号的大小(亦即控制发光二极管led的驱动电流大小)。而当灰阶度较小而切换为第二模式时,脉宽调变电路pwm以固定的脉宽调变电压馈入端vpwm电压来控制驱动信号的持续时间,脉幅调变电路pam以可调变的脉幅调变电压馈入端vpam电压来控制驱动信号的大小。127.在一实施例中,在第二模式下,固定的脉宽调变电压馈入端vpwm电压用以使发光时间延长,可调变的脉幅调变电压馈入端vpam电压用以使流经发光二极管led的电流降低,如此一来,当驱动电路100用以驱动一显示器上的多个发光二极管led时,发光二极管led位置差异所导致的信号延迟对于显示器亮度一致性(uniformity)的影响即可被降低。128.以下段落说明可藉由何种电路配置及信号传输使驱动电路100得于第一模式及第二模式之间切换。请参照图4a,图4a为根据本揭示内容一实施例的驱动电路400的电路架构图。在一实施例中,驱动电路400包含子像素驱动电路pxr、子像素驱动电路pxg、子像素驱动电路pxb,此三者分别对应至显示器中红色、绿色、蓝色的子像素(sub-pixel),此外驱动电路400尚包含第十四晶体管t14r、t14g、t14b,第一多工器m1r、m1g、m1b,第十五晶体管t15r、t15g、t15b,以及第二多工器m2r、m2g、m2b。第十四晶体管t14r、第一多工器m1r、第十五晶体管t15r以及第二多工器m2r对应至子像素驱动电路pxr,第十四晶体管t14g、第一多工器m1g、第十五晶体管t15g以及第二多工器m2g对应至子像素驱动电路pxg,第十四晶体管t14b、第一多工器m1b、第十五晶体管t15b以及第二多工器m2b对应至子像素驱动电路pxb。129.承前实施例,请同时参照图1及图4a,驱动电路400的子像素驱动电路pxr、pxg、pxb与图1实施例中的驱动电路100具有相同的电路配置,其每一者皆包含脉宽调变电路pwm、脉幅调变电路pam、发光控制电路emc及发光装置emd,且其中的所有元件(即晶体管、电容、发光二极管等)及其连接关系亦相同。130.承前实施例,请同时参照图1及图4a,在子像素驱动电路pxr中的脉宽调变电压馈入端vpwm及脉幅调变电压馈入端vpam的电压是通过第一集成电路ic1来提供,以下说明驱动电路400中子像素驱动电路pxr与第一集成电路ic1之间的电路配置。第十四晶体管t14r其第一端电性连接第一集成电路ic1,其第二端电性连接脉宽调变电路pwm中的脉宽调变电压馈入端vpwm;第一多工器m1r电性连接第十四晶体管t14r的栅极端并用以控制第十四晶体管t14r导通的时点;第十五晶体管t15r其第一端电性连接第一集成电路ic1,其第二端电性连接脉幅调变电路pam中的脉幅调变电压馈入端vpam;第二多工器m2r电性连接第十五晶体管t15r的栅极端并用以控制第十五晶体管t15r导通的时点。131.如图4a所示,子像素驱动电路pxg与第一集成电路ic1间的电路配置,相似于上述子像素驱动电路pxr与第一集成电路ic1间的电路配置。换言之,子像素驱动电路pxg的脉宽调变电路pwm通过第十四晶体管t14g电性连接第一集成电路ic1,子像素驱动电路pxg的脉幅调变电路pam通过第十五晶体管t15g电性连接第一集成电路ic,第一多工器m1g电性连接第十四晶体管t14g的栅极端,第二多工器m2g电性连接第十五晶体管t15g的栅极端。同样地,子像素驱动电路pxb与第一集成电路ic1间的电路配置相似于子像素驱动电路pxr、pxg与第一集成电路ic1间的电路配置,其电路配置及连接关系请参照以上说明,不再赘述。132.在一实施例中,如图4a所示,第十四晶体管t14r、t14g、t14b各自的第一端,以及第十五晶体管t15r、t15g、t15b各自的第一端相互电性连接。133.接着说明驱动电路400在第一模式下的控制信号。请同时参照图4a及图4b,图4b为根据本揭示内容一实施例的图4a中的驱动电路400在第一模式下的控制信号时序图。在一实施例中,第一集成电路ic1用以对子像素驱动电路pxr、pxg、pxb传送信号sic1,且信号sic1包含信号sigr1、sigg1、sigb1、sigr2、sigg2、sigb2,第一多工器m1r用以传送控制信号sm1r至第十四晶体管t14r的栅极端,第一多工器m1g用以传送控制信号sm1g至第十四晶体管t14g的栅极端,第一多工器m1b用以传送控制信号sm1b至第十四晶体管t14b的栅极端,第二多工器m2r用以传送控制信号sm2r至第十五晶体管t15r的栅极端,第二多工器m2g用以传送控制信号sm2g至第十五晶体管t15g的栅极端,第二多工器m2b用以传送控制信号sm2b至第十五晶体管t15b的栅极端。134.如图4b所示,在此实施例中,当第三控制信号sp具有低逻辑电平时(亦即子像素驱动电路pxr、pxg、pxb操作于如图3b实施例的数据写入期间p2),第一集成电路ic1传送信号sic1至子像素驱动电路pxr、pxg、pxb,以将信号sigr1、sigg1、sigb1、sigr2、sigg2、sigb2分别写入子像素驱动电路pxr、pxg、pxb中的第三晶体管t3及第一晶体管t1的栅极端(请参照图3b)。135.详细来说,如图4b所示,第一集成电路ic1首先输出信号sigr1,此时除了第三控制信号sp外,仅有控制信号sm1r具有低逻辑电平,因此第一多工器m1r传送控制信号sm1r至第十四晶体管t14r的栅极端,使第十四晶体管t14r被导通,信号sigr1因此被传送至子像素驱动电路pxr的脉宽调变电路pwm。136.接着,第一集成电路ic1输出信号sigg1,此时除了第三控制信号sp外,仅有控制信号sm1g具有低逻辑电平,因此第一多工器m1g传送控制信号sm1g至第十四晶体管t14g的栅极端,使第十四晶体管t14g被导通,信号sigg1被传送至子像素驱动电路pxg的脉宽调变电路pwm。类似地,第一集成电路ic1输出信号sigb1,且信号sigb1将被传送至子像素驱动电路pxb的脉宽调变电路pwm。137.第一集成电路ic1在输出信号sigb1后,将依序输出信号sigr2、sigg2、sigb2,此些信号分别被传送至子像素驱动电路pxr、pxg、pxb的脉幅调变电路pam。详细来说,首先,第一集成电路ic1输出信号sigr2,第二多工器m2r传送控制信号sm2r至第十五晶体管t15r的栅极端使第十五晶体管t15r被导通,因此信号sigr2被传送至子像素驱动电路pxr的脉幅调变电路pam。接着,第一集成电路ic1输出信号sigg2,第二多工器m2g传送控制信号sm2g至第十五晶体管t15g的栅极端使第十五晶体管t15g被导通,因此信号sigg2被传送至子像素驱动电路pxg的脉幅调变电路pam。最后,第一集成电路ic1输出信号sigb2,第二多工器m2b传送控制信号sm2b至第十五晶体管t15b的栅极端使第十五晶体管t15b被导通,因此信号sigb2被传送至子像素驱动电路pxb的脉幅调变电路pam。138.值得注意的是,由于在第一模式下,脉宽调变电压馈入端vpwm的电压为可调变的,脉幅调变电压馈入端vpam的电压为固定的,因此第一集成电路ic1所输出至子像素驱动电路pxr、pxg、pxb各自脉宽调变电路pwm的信号sigr1、sigg1、sigb1可具有不同的信号大小(如图4b所示),另一方面,第一集成电路ic1所输出至子像素驱动电路pxr、pxg、pxb各自脉幅调变电路pam的信号sigr2、sigg2、sigb2具有固定的信号大小(如图4b所示)。应注意的是,图4b中信号sigr1、sigg1、sigb1、sigr2、sigg2、sigb2的相对大小并非意欲限制本揭示内容,而仅为例示说明信号sigr1、sigg1、sigb1具有可调变的大小,信号sigr2、sigg2、sigb2则具有相同且固定的大小。139.关于驱动电路400在第二模式下的控制信号,请同时参照图4a及图4c,图4c为根据本揭示内容一实施例的图4a中的驱动电路400在第二模式下的控制信号时序图。类似于图4b的实施例,在图4c的实施例中,控制信号sm1r、sm1g、sm1b、sm2r、sm2g、sm2b分别在不同的时段具有低逻辑电平,第一集成电路c1则针对不同的时段输出对应的信号sigr1、sigg1、sigb1、sigr2、sigg2、sigb2。例如,第一集成电路ic1首先输出信号sigr1,此时除了第三控制信号sp外,仅有控制信号sm1r具有低逻辑电平,因此第十四晶体管t14r被导通,信号sigr1将被传送至子像素驱动电路pxr的脉宽调变电路pwm。关于其他信号(即信号sigg1、sigb1、sigr2、sigg2、sigb2)在第二模式下的传输,可参照前述相关说明,不再赘述。140.值得注意的是,由于在第二模式下,脉宽调变电压馈入端vpwm的电压为固定的,脉幅调变电压馈入端vpam的电压为可调变的,因此第一集成电路ic1所输出至子像素驱动电路pxr、pxg、pxb各自脉宽调变电路pwm的信号sigr1、sigg1、sigb1具有固定的信号大小(如图4c所示),另一方面,第一集成电路ic1所输出至子像素驱动电路pxr、pxg、pxb各自脉幅调变电路pam的信号sigr2、sigg2、sigb2可具有不同的信号大小(如图4c所示)。应注意的是,图4c中信号sigr1、sigg1、sigb1、sigr2、sigg2、sigb2的相对大小并非意欲限制本揭示内容,而仅为例示说明信号sigr1、sigg1、sigb1具有相同且固定的大小,信号sigr2、sigg2、sigb2则具有可调变的大小。141.请参照图4d,图4d为根据本揭示内容一实施例的第一模式及第二模式下的驱动电流-时间关系图。如前所述,本揭示内容的驱动电路在高灰阶度(即高亮度)时使用第一模式。在图4d中,曲线c1及曲线c2代表显示器中不同位置的发光二极管在第一模式下驱动电路与时间的关系。在第一模式下,脉幅调变电压馈入端vpam的电压为固定的,因此可以提供大的驱动电流以提高发光二极管至最大亮度,进而提升显示器的对比度。142.另一方面,本揭示内容在低灰阶度(即低亮度)时使用第二模式。在图4d中,曲线c3及曲线c4代表显示器中不同位置的发光二极管在第二模式下驱动电路与时间的关系。由于曲线c4所代表的发光二极管相对于曲线c3所代表的发光二极管,与显示器中驱动电路的控制信号具有较远的距离,因此驱动电路控制信号关断两个发光二极管的时间将有一时间差dt(或者说信号延迟)。如此的时间差dt即会造成两个发光二极管的亮度不一致,此亮度不一致等同于曲线c3所形成面积与曲线c4所形成面积之间的差异(即图4d中的面积a1)。143.值得注意的是,在低灰阶时使用第二模式,相较于不使用第二模式,能够降低不同位置发光二极管的亮度不一致。曲线c5及曲线c6代表显示器中不同位置的发光二极管在低灰阶时使用第一模式的驱动电路与时间的关系。曲线c5及曲线c6所代表发光二极管接收的控制信号同样地会有时间差dt,且其亮度不一致等同面积a2。从曲线c5及曲线c6可看出,在低灰阶时若使用大的驱动电流则其发光时间将较短,因此时间差dt所造成的不同位置发光二极管的亮度差异将影响较大。由于面积a2相比于曲线c5所形成面积具有较高的比值,面积a1相比于曲线c3所形成面积具有较低的比值,因此在低灰阶时使用第一模式的亮度不一致将大于使用第二模式的亮度不一致,代表在低灰阶时使用第二模式有助于提高不同位置发光二极管的亮度一致性。144.在另一实施例中,驱动电路100可通过不同的电路配置及信号传输以于第一模式及第二模式之间切换。请参照图5a,图5a为根据本揭示内容一实施例的驱动电路500的电路架构图。在一实施例中,驱动电路500包含子像素驱动电路pxr、子像素驱动电路pxg、子像素驱动电路pxb,此外驱动电路500尚包含第十六晶体管t16r、t16g、t16b,第三多工器m3r、m3g、m3b,以及第十七晶体管t17r、t17g、t17b。子像素驱动电路pxr、pxg、pxb与图1实施例的驱动电路100具有相同元件及其连接关系,第十六晶体管t16r、第三多工器m3r以及第十七晶体管t17r对应至子像素驱动电路pxr,第十六晶体管t16g、第三多工器m3g以及第十七晶体管t17g对应至子像素驱动电路pxg,第十六晶体管t16b、第三多工器m3b以及第十七晶体管t17b对应至子像素驱动电路pxb。子像素驱动电路pxr、pxg、pxb与图1实施例中的驱动电路100具有相同的电路配置。145.承前实施例,请同时参照图1及图5a,子像素驱动电路pxr、pxg、pxb中各自的脉宽调变电压馈入端vpwm的电压是通过第二集成电路ic2来提供,而其各自的脉幅调变电压馈入端vpam的电压是通过第三集成电路ic3来提供。146.以下说明子像素驱动电路pxr与第二集成电路ic2及第三集成电路ic3间的电路配置。第十六晶体管t16r其第一端电性连接第二集成电路ic2,其第二端电性连接脉宽调变电路pwm中的脉宽调变电压馈入端vpwm;第十七晶体管t17r其第一端电性连接第三集成电路ic3,其第二端电性连接脉幅调变电路pam中的脉幅调变电压馈入端vpam;第三多工器m3r电性连接第十六晶体管t16r以及第十七晶体管t17r的栅极端,且用以控制第十六晶体管t16r以及第十七晶体管t17r导通的时点。147.如图5a所示,子像素驱动电路pxg与第二集成电路ic2及第三集成电路ic3间的电路配置,相似于上述子像素驱动电路pxr与第二集成电路ic2及第三集成电路ic3间的电路配置。换言之,子像素驱动电路pxg的脉宽调变电路pwm通过第十六晶体管t16g电性连接第二集成电路ic2,子像素驱动电路pxg的脉幅调变电路pam通过第十七晶体管t17g电性连第三集成电路ic3,第三多工器m3g电性连接第十六晶体管t16g以及第十七晶体管t17g的栅极端。同样地,子像素驱动电路pxb与第二集成电路ic2及第三集成电路ic3间的电路配置相似于子像素驱动电路pxr、pxg与第二集成电路ic2及第三集成电路ic3间的电路配置,请参照以上说明。148.在一实施例中,如图5a所示,第十六晶体管t16r、t16g、t16b各自的第一端,以及第十七晶体管t17r、t17g、t17b各自的第一端相互电性连接。149.接着说明驱动电路500在第一模式下的控制信号。请同时参照图5a及图5b,图5b为根据本揭示内容一实施例的图5a中的驱动电路500在第一模式下的控制信号时序图。在一实施例中,第二集成电路ic2用以对子像素驱动电路pxr、pxg、pxb传送信号sic2,且信号sic2包含信号sigr3、sigg3、sigb3,第三集成电路ic3用以对子像素驱动电路pxr、pxg、pxb传送信号sic3,且信号sic3包含信号sigr4、sigg4、sigb4,第一多工器m3r用以传送控制信号sm3r至第十七晶体管t17r的栅极端,第一多工器m3g用以传送控制信号sm3g至第十七晶体管t17g的栅极端,第一多工器m3b用以传送控制信号sm3b至第十七晶体管t17b的栅极端。150.如图5b所示,在此实施例中,当第三控制信号sp具有低逻辑电平时(亦即子像素驱动电路pxr、pxg、pxb操作于如图3b实施例的数据写入期间p2时),第二集成电路ic2传送信号sic2至子像素驱动电路pxr、pxg、pxb,第三集成电路ic3传送信号sic3至子像素驱动电路pxr、pxg、pxb,以将信号sigr3、sigg3、sigb3、sigr4、sigg4、sigb4分别写入子像素驱动电路pxr、pxg、pxb中的第三晶体管t3及第一晶体管t1的栅极端(请参照图3b)。151.详细来说,如图5b所示,首先,第二集成电路ic2输出信号sigr3,同时第三集成电路ic3输出信号sigr4,此时除了第三控制信号sp外,仅有控制信号sm3r具有低逻辑电平,因此第十六晶体管t16r及第十七晶体管t17r被导通,信号sigr3进而被传送至子像素驱动电路pxr的脉宽调变电路pwm,信号sigr4被传送至子像素驱动电路pxr的脉幅调变电路pam。152.接着,第二集成电路ic2输出信号sigg3,同时第三集成电路ic3输出信号sigg4,此时除了第三控制信号sp外,仅有控制信号sm3g具有低逻辑电平,因此第十六晶体管t16g及第十七晶体管t17g被导通,信号sigg3进而被传送至子像素驱动电路pxg的脉宽调变电路pwm,信号sigg4被传送至子像素驱动电路pxg的脉幅调变电路pam。153.接着,第二集成电路ic2输出信号sigb3,同时第三集成电路ic3输出信号sigb4,此时除了第三控制信号sp外,仅有控制信号sm3b具有低逻辑电平,因此第十六晶体管t16b及第十七晶体管t17b被导通,信号sigb3进而被传送至子像素驱动电路pxb的脉宽调变电路pwm,信号sigb4被传送至子像素驱动电路pxb的脉幅调变电路pam。154.值得注意的是,由于在第一模式下,脉宽调变电压馈入端vpwm的电压为可调变的,脉幅调变电压馈入端vpam的电压为固定的,因此第二集成电路ic2所输出至子像素驱动电路pxr、pxg、pxb各自脉宽调变电路pwm的信号sigr3、sigg3、sigb3可具有不同的信号大小(如图5b所示),另一方面,第三集成电路ic3所输出至子像素驱动电路pxr、pxg、pxb各自脉幅调变电路pam的信号sigr4、sigg4、sigb4具有固定的信号大小(如图5b所示)。应注意的是,图5b中信号sigr3、sigg3、sigb3、sigr4、sigg4、sigb4的相对大小并非意欲限制本揭示内容,而仅为例示说明信号sigr3、sigg3、sigb3具有可调变的大小,信号sigr4、sigg4、sigb4则具有相同且固定的大小。155.关于驱动电路500在第二模式下的控制信号,请参照图5c,图5c为根据本揭示内容一实施例的图5a中的驱动电路500在第二模式下的控制信号时序图。类似于图5b的实施例,在图5c的实施例中,控制信号sm3r、sm3g、sm3b分别在不同的时段具有低逻辑电平,第二集成电路ic2及第三集成电路ic3则针对不同的时段输出对应的信号sigr3、sigg3、sigb3、sigr4、sigg4、sigb4。例如,首先,第二集成电路ic2输出信号sigr3,同时第三集成电路ic3输出信号sigr4,此时除了第三控制信号sp外,仅有控制信号sm3r具有低逻辑电平,因此第十六晶体管t16r及第十七晶体管t17r被导通,信号sigr3将被传送至子像素驱动电路pxr的脉宽调变电路pwm,信号sigr4将被传送至子像素驱动电路pxr的脉幅调变电路pam。关于后续其他信号(sigg3、sigb3、sigg4、sigb4)的传输,可参照前述相关说明。156.值得注意的是,由于在第二模式下,脉宽调变电压馈入端vpwm的电压为固定的,脉幅调变电压馈入端vpam的电压为可调变的,因此第二集成电路ic2所输出至子像素驱动电路pxr、pxg、pxb中各自脉宽调变电路pwm的信号sigr3、sigg3、sigb3具有固定的信号大小(如图5c所示),另一方面,第三集成电路ic3所输出至子像素驱动电路pxr、pxg、pxb各自脉幅调变电路pam的信号sigr4、sigg4、sigb4可具有不同的信号大小(如图5c所示)。应注意的是,图5c中信号sigr3、sigg3、sigb3、sigr4、sigg4、sigb4的相对大小并非意欲限制本揭示内容,而仅为例示说明信号sigr3、sigg3、sigb3具有相同且固定的大小,信号sigr4、sigg4、sigb4则具有可调变的大小。157.同样地,驱动电路500通过在低灰阶时切换为使用第二模式,有助于提升显示器上不同位置发光二极管的亮度一致性。请参照前述关于图4d的说明。158.在另一实施例中,驱动电路100可通过不同的电路配置及信号传输以于第一模式及第二模式之间切换。请参照图6a,图6a为根据本揭示内容一实施例的驱动电路600的电路架构图。在一实施例中,驱动电路600包含子像素驱动电路pxr、子像素驱动电路pxg、子像素驱动电路pxb,此外驱动电路600尚包含第十八晶体管t18r、t18g、t18b,第四多工器m4r、m4g、m4b,以及第十九晶体管t19r、t19g、t19b。第十八晶体管t18r、第四多工器m4r以及第十九晶体管t19r对应至子像素驱动电路pxr,第十八晶体管t18g、第四多工器m4g以及第十九晶体管t19g对应至子像素驱动电路pxg,第十八晶体管t18b、第四多工器m4b以及第十九晶体管t19b对应至子像素驱动电路pxb。159.图6a实施例中的子像素驱动电路pxr、pxg、pxb与图1实施例中的驱动电路100具有类似的元件及其连接关系,不过其控制信号的接收则有不同。请同时参照图1及图6b,图6b为根据本揭示内容一实施例的驱动电路100’的电路架构图。驱动电路100’即为图6a实施例中子像素驱动电路pxr、pxg、pxb三者各自的电路结构。驱动电路100’与图1的驱动电路100具有同样的元件及连接关系,两者的不同点在于在驱动电路100’中,如图6b所示,第九晶体管t9及第十二晶体管t12的栅极端用以接收第四控制信号sp1,第七晶体管t7及第十一晶体管t11的栅极端用以接收第五控制信号sp2。相反地,在图1的驱动电路100中,第九晶体管t9、第十二晶体管t12、第七晶体管t7及第十一晶体管t11的栅极端皆用以接收相同的第三控制信号sp。160.请同时参照图6a及图6b,在子像素驱动电路pxr、pxg、pxb中,其各自的脉宽调变电压馈入端vpwm及脉幅调变电压馈入端vpam的电压是通过第四集成电路ic4来提供。以下说明在驱动电路600中子像素驱动电路pxr与第四集成电路ic4间的电路配置。第十八晶体管t18r其第一端电性连接第四集成电路ic4,其第二端电性连接脉宽调变电路pwm中的脉宽调变电压馈入端vpwm;第十九晶体管t19r其第一端电性连接第四集成电路ic4,其第二端电性连接脉幅调变电路pam中的脉幅调变电压馈入端vpam;第四多工器m4r电性连接第十八晶体管t18r以及第十九晶体管t19r的栅极端,且用以控制第十八晶体管t18r以及第十九晶体管t19r导通的时点。161.如图6a所示,子像素驱动电路pxg与第四集成电路ic4间的电路配置,相似于上述子像素驱动电路pxr与第四集成电路ic4间的电路配置。换言之,子像素驱动电路pxg的脉宽调变电路pwm通过第十八晶体管t18g电性连接第四集成电路ic4,子像素驱动电路pxg的脉幅调变电路pam通过第十九晶体管t19g电性连接第四集成电路ic4,第四多工器m4g电性连接第十八晶体管t18g以及第十九晶体管t19g的栅极端。同样地,子像素驱动电路pxb与第四集成电路ic4间的电路配置相似于子像素驱动电路pxr、pxg与第四集成电路ic4间的电路配置,请参照以上说明。162.在一实施例中,如图6a所示,第十八晶体管t18r、t18g、t18b各自的第一端,以及第十九晶体管t19r、t19g、t19b各自的第一端相互电性连接。163.接着说明驱动电路600在第一模式下的控制信号。请同时参照图6a及图6c,图6c为根据本揭示内容一实施例的图6a中的驱动电路600在第一模式下的控制信号时序图。在一实施例中,第四集成电路ic4用以对子像素驱动电路pxr、pxg、pxb传送信号sic4,且信号sic4包含信号sigr5、sigg5、sigb5、sigr6、sigg6、sigb6,第四多工器m4r用以传送控制信号sm4r至第十八晶体管t18r及第十九晶体管t19r的栅极端,第四多工器m4g用以传送控制信号sm4g至第十八晶体管t18g及第十九晶体管t19g的栅极端,第四多工器m4b用以传送控制信号sm4b至第十八晶体管t18b及第十九晶体管t19b的栅极端。164.请同时参照图6a、图6b及图6c,当第四控制信号sp1具有低逻辑电平时,第四集成电路ic4传送信号sigr5、sigg5、sigb5至子像素驱动电路pxr、pxg、pxb的脉宽调变电路pwm,以将信号sigr5、sigg5、sigb5分别写入子像素驱动电路pxr、pxg、pxb中的第三晶体管t3的栅极端。而当第五控制信号sp2具有低逻辑电平时,第四集成电路ic4传送信号sigr6、sigg6、sigb6至子像素驱动电路pxr、pxg、pxb的脉幅调变电路pam,以将信号sigr6、sigg6、sigb6分别写入子像素驱动电路pxr、pxg、pxb中的第一晶体管t1的栅极端。165.详细来说,如图6c所示,首先,第四集成电路ic4输出信号sigr5,此时除了第四控制信号sp1外,仅有控制信号sm4r具有低逻辑电平,因此第十八晶体管t18r及第十九晶体管t19r被导通,信号sigr5被传送至子像素驱动电路pxr的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第五控制信号sp2为高逻辑电平,因此子像素驱动电路pxr的脉幅调变电路pam的第十一晶体管t11并不会被导通(请参照图6b),信号sigr5不会被写入至第一晶体管t1的栅极端。166.接着,第四集成电路ic4输出信号sigg5,此时除了第四控制信号sp1外,仅有控制信号sm4g具有低逻辑电平,因此第十八晶体管t18g及第十九晶体管t19g被导通,信号sigg5被传送至子像素驱动电路pxg的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第五控制信号sp2为高逻辑电平,因此子像素驱动电路pxg的脉幅调变电路pam的第十一晶体管t11并不会被导通(请参照图6b),信号sigg5不会被写入至第一晶体管t1的栅极端。167.接着,第四集成电路ic4输出信号sigb3,此时除了第四控制信号sp1外,仅有控制信号sm4b具有低逻辑电平,因此第十八晶体管t18b及第十九晶体管t19b被导通,信号sigb5被传送至子像素驱动电路pxb的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第五控制信号sp2为高逻辑电平,因此子像素驱动电路pxb的脉幅调变电路pam的第十一晶体管t11并不会被导通(请参照图6b),信号sigb5不会被写入至第一晶体管t1的栅极端。168.接着,第四集成电路ic4输出信号sigr6,此时除了第五控制信号sp2外,仅有控制信号sm4r具有低逻辑电平,因此第十八晶体管t18r及第十九晶体管t19r被导通,信号sigr6被传送至子像素驱动电路pxr的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第四控制信号sp1为高逻辑电平,因此子像素驱动电路pxr的脉宽调变电路pwm的第十二晶体管t12并不会被导通(请参照图6b),信号sigr6不会被写入至第三晶体管t3的栅极端。169.接着,第四集成电路ic4输出信号sigg6,此时除了第五控制信号sp2外,仅有控制信号sm4g具有低逻辑电平,因此第十八晶体管t18g及第十九晶体管t19g被导通,信号sigg6被传送至子像素驱动电路pxg的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第四控制信号sp1为高逻辑电平,因此子像素驱动电路pxg的脉宽调变电路pwm的第十二晶体管t12并不会被导通(请参照图6b),信号sigg6不会被写入至第三晶体管t3的栅极端。170.接着,第四集成电路ic4输出信号sigb6,此时除了第五控制信号sp2外,仅有控制信号sm4b具有低逻辑电平,因此第十八晶体管t18b及第十九晶体管t19b被导通,信号sigb6被传送至子像素驱动电路pxb的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第四控制信号sp1为高逻辑电平,因此子像素驱动电路pxb的脉宽调变电路pwm的第十二晶体管t12并不会被导通(请参照图6b),信号sigb6不会被写入至第三晶体管t3的栅极端。171.值得注意的是,由于在第一模式下,脉宽调变电压馈入端vpwm的电压为可调变的,脉幅调变电压馈入端vpam的电压为固定的,因此第四集成电路ic4所输出至子像素驱动电路pxr、pxg、pxb中各自脉宽调变电路pwm的信号sigr5、sigg5、sigb5可具有不同的信号大小(如图6c所示),另一方面,第四集成电路ic4所输出至子像素驱动电路pxr、pxg、pxb中各自脉幅调变电路pam的信号sigr6、sigg6、sigb6具有固定的信号大小(如图6c所示)。应注意的是,图6c中信号sigr5、sigg5、sigb5、sigr6、sigg6、sigb6的相对大小并非意欲限制本揭示内容,而仅为例示说明信号sigr5、sigg5、sigb5具有可调变的大小,信号sigr6、sigg6、sigb6则具有相同且固定的大小。172.关于驱动电路600在第二模式下的控制信号,请参照图6d,图6d为根据本揭示内容一实施例的图6a中的驱动电路600在第二模式下的控制信号时序图。类似于图6c的实施例,在图6d的实施例中,控制信号sm4r、sm4g、sm4b分别在不同的时段具有低逻辑电平,第四集成电路ic4则针对不同的时段输出对应的信号sigr5、sigg5、sigb5、sigr6、sigg6、sigb6。例如,首先,第四集成电路ic4输出信号sigr5,此时除了第四控制信号sp1外,仅有控制信号sm4r具有低逻辑电平,因此第十八晶体管t18r及第十九晶体管t19r被导通,信号sigr5将被传送至子像素驱动电路pxr的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第五控制信号sp2为高逻辑电平,因此子像素驱动电路pxr的脉幅调变电路pam的第十一晶体管t11并不会被导通(请参照图6b),信号sigr5不会被写入至第一晶体管t1的栅极端。关于后续其他信号(亦即sigg5、sigb5、sigr6、sigg6、sigb6)的传输,可参照前述相关说明,不再赘述。173.值得注意的是,由于在第二模式下,脉宽调变电压馈入端vpwm的电压为固定的,脉幅调变电压馈入端vpam的电压为可调变的,因此第四集成电路ic4所输出至子像素驱动电路pxr、pxg、pxb中各自脉宽调变电路pwm的信号sigr5、sigg5、sigb5具有固定的信号大小(如图6d所示),另一方面,第四集成电路ic4所输出至子像素驱动电路pxr、pxg、pxb中各自脉幅调变电路pam的信号sigr6、sigg6、sigb6可具有不同的信号大小(如图6d所示)。应注意的是,图6d中信号sigr5、sigg5、sigb5、sigr6、sigg6、sigb6的相对大小并非意欲限制本揭示内容,而仅为例示说明信号sigr5、sigg5、sigb5具有相同且固定的大小,信号sigr6、sigg6、sigb6则具有可调变的大小。174.同样地,驱动电路600通过在低灰阶时切换为使用第二模式,有助于提升显示器上不同位置发光二极管的亮度一致性。请参照前述关于图4d的说明。175.综上所述,通过如图4a、图5a、图6a及图6b所示的电路配置,以及如图4b、图4c、图5b、图5c、图6c、图6d所示的控制信号时序,本揭示内容的驱动电路可具有第一模式及第二模式,以根据不同的灰阶度采取不同驱动模式,进而改善显示器的亮度一致性。176.根据前揭实施例的说明,本揭示内容亦揭露一种驱动方法。请参照图7,图7为根据本揭示内容一实施例的驱动方法700的流程图。驱动方法700用以驱动像素电路(如图1的驱动电路100或图6b实施例的驱动电路100’)。如图7所示,驱动方法700包含步骤s710及步骤s720。177.在步骤s710中,在第一模式下,调变像素电路的脉宽调变电压馈入端的电压,并固定变像素电路的脉幅调变电压馈入端的电压。关于如何调变脉宽调变电压馈入端的电压并固定脉幅调变电压馈入端的电压,可参照前述图4a、图4b、图5a、图5b、图6a、图6c实施例的相关说明,应注意的是,此些实施例仅作为可执行驱动方法700的例示电路结构及控制信号时序,相关

技术领域:

:具有通常知识者若以其他类似的电路配置及控制信号执行驱动方法700,应理解为仍为本揭示内容所涵括。178.在步骤s720中,在第二模式下,固定变像素电路的脉宽调变电压馈入端的电压,调变变像素电路的脉幅调变电压馈入端的电压。可参照前述图4a、图4c、图5a、图5c、图6a、图6d实施例的相关说明,应注意的是,此些实施例仅作为可执行驱动方法700的例示电路结构及控制信号时序,相关

技术领域:

:具有通常知识者若以其他类似的电路配置及控制信号执行驱动方法700,应理解为仍为本揭示内容所涵括。179.其中,脉宽调变电压馈入端的电压控制驱动信号的持续时间,脉幅调变电压馈入端的电压控制驱动信号的大小。驱动信号用以驱动像素电路中的发光二极管进行发光。180.应注意的是,在一实施例中,步骤s710及步骤s720的顺序可以交换。在一实施例中,驱动方法700是根据显示器的灰阶度以决定进行第一模式或第二模式中之一者,例如在八位元灰阶下,当灰阶度大于等于第十一阶时,驱动方法使用第一模式来驱动发光二极管,当灰阶度小于第十一阶时,驱动方法使用第二模式来驱动发光二极管。181.综上所述,驱动方法700在第一模式及第二模式下,对显示器驱动面板的脉宽调变电压馈入端及脉幅调变电压馈入端施以不同的电压,进而改善显示器的亮度一致性。182.虽然本揭示内容已以实施方式揭露如上,然其并非用以限定本发明。任何熟习此技艺之人,在不脱离本揭示内容的精神及范围内,当可作各种更动及润饰。本揭示内容的保护范围当视后附的申请专利范围所界定者为准。当前第1页12当前第1页12

背景技术:

::2.显示器上不同位置的薄膜晶体管(thin-filmtransistors,tfts)所接收的驱动信号会有不同的延迟,因而产生亮度不均的问题。特别是在低灰阶度(graylevel)的情形下,亮度的一致性将可能降至80%以下。由于无法于同时切断不同位置薄膜晶体管的驱动信号,必须以他法解决显示器面板亮度不均的问题。技术实现要素:3.本揭示内容的一实施例提出一种驱动电路,包含脉幅调变电路以及脉宽调变电路。脉幅调变电路用以控制驱动信号的大小。脉宽调变电路用以控制驱动信号的持续时间。脉幅调变电路包含第一晶体管、第一电容以及第二晶体管。脉宽调变电路包含第二电容、第三晶体管以及第四晶体管。第一电容其第一端电性连接第一晶体管的栅极端。第二晶体管,其第一端电性连接第一电容的第一端,其第二端电性连接第一晶体管的第二端。第三晶体管其栅极端电性连接第二电容的第二端。第四晶体管其第一端电性连接第三晶体管的栅极端,其第二端电性连接第三晶体管的第二端,其栅极端电性连接第二晶体管的栅极端并用以接收第一控制信号。4.本揭示内容的一实施例另提出一种驱动方法,包含:在第一模式下,调变脉宽调变电压馈入端的电压,并固定脉幅调变电压馈入端的电压;以及在第二模式下,固定脉宽调变电压馈入端的电压,调变脉幅调变电压馈入端的电压。其中,脉宽调变电压馈入端的电压控制驱动信号的持续时间,脉幅调变电压馈入端的电压控制驱动信号的大小。附图说明5.为使本揭露的上述和其他目的、特征、优点与实施例能更明显易懂,所附图式的说明如下:6.图1为根据本揭示内容一实施例的驱动电路的电路架构图。7.图2为根据本揭示内容一实施例的图1中的驱动电路的控制信号时序图。8.图3a为根据本揭示内容一实施例的图1中的驱动电路在重置期间中的电路状态图。9.图3b为根据本揭示内容一实施例的图1中的驱动电路在数据写入期间中的电路状态图。10.图3c为根据本揭示内容一实施例的图1中的驱动电路在开启电流路径期间中的电路状态图。11.图3d为根据本揭示内容一实施例的图1中的驱动电路在发光期间中的电路状态图。12.图4a为根据本揭示内容一实施例的驱动电路的电路架构图。13.图4b为根据本揭示内容一实施例的图4a中的驱动电路在第一模式下的控制信号时序图。14.图4c为根据本揭示内容一实施例的图4a中的驱动电路在第二模式下的控制信号时序图。15.图4d为根据本揭示内容一实施例的第一模式及第二模式下的驱动电流-时间关系图。16.图5a为根据本揭示内容一实施例的驱动电路的电路架构图。17.图5b为根据本揭示内容一实施例的图5a中的驱动电路在第一模式下的控制信号时序图。18.图5c为根据本揭示内容一实施例的图5a中的驱动电路在第二模式下的控制信号时序图。19.图6a为根据本揭示内容一实施例的驱动电路的电路架构图。20.图6b为根据本揭示内容一实施例的驱动电路的电路架构图。21.图6c为根据本揭示内容一实施例的图6a中的驱动电路在第一模式下的控制信号时序图。22.图6d为根据本揭示内容一实施例的图6a中的驱动电路在第二模式下的控制信号时序图。23.图7为根据本揭示内容一实施例的驱动方法的流程图。24.其中,附图标记:25.100:驱动电路26.100’:驱动电路27.400:驱动电路28.500:驱动电路29.600:驱动电路30.700:驱动方法31.c1:第一电容32.c2:第二电容33.c3:第三电容34.c4:第四电容35.em:发光信号36.emc:发光控制电路37.emd:发光装置38.ic1:第一集成电路39.ic2:第二集成电路40.ic3:第三集成电路41.ic4:第四集成电路42.led:发光二极管43.m1r、m1g、m1b:第一多工器44.m2r、m2g、m2b:第二多工器45.m3r、m3g、m3b:第三多工器46.m4r、m4g、m4b:第四多工器47.p1:重置期间48.p2:数据写入期间49.p3:开启电流路径期间50.p4:发光期间51.pam:脉幅调变电路52.pg:第一控制信号53.pxr、pxg、pxb:子像素驱动电路54.pwm:脉宽调变电路55.rst:重置信号56.s710、s720:步骤57.sic1:信号58.sic2:信号59.sic3:信号60.sic4:信号61.sigr1、sigg1、sigb1、sigr2、sigg2、sigb2:信号62.sigr3、sigg3、sigb3、sigr4、sigg4、sigb4:信号63.sigr5、sigg5、sigb5、sigr6、sigg6、sigb6:信号64.set:设定信号65.sm1r、sm1g、sm1b、sm2r、sm2g、sm2b:控制信号66.sm3r、sm3g、sm3b:控制信号67.sm4r、sm4g、sm4b:控制信号68.sp:第三控制信号69.sp1:第四控制信号70.sp2:第五控制信号71.swp:第二控制信号72.t1:第一晶体管73.t2:第二晶体管74.t3:第三晶体管75.t4:第四晶体管76.t5:第五晶体管77.t6:第六晶体管78.t7:第七晶体管79.t8:第八晶体管80.t9:第九晶体管81.t10:第十晶体管82.t11:第十一晶体管83.t12:第十二晶体管84.t13:第十三晶体管85.t14r、t14g、t14b:第十四晶体管86.t15r、t15g、t15b:第十五晶体管87.t16r、t16g、t16b:第十六晶体管88.t17r、t17g、t17b:第十七晶体管89.t18r、t18g、t18b:第十八晶体管90.t19r、t19g、t19b:第十九晶体管91.t20:第二十晶体管92.t21:第二十一晶体管93.t22:第二十二晶体管94.t23:第二十三晶体管95.vdd:第一系统电压端96.vpam:脉幅调变电压馈入端97.vpwm:脉宽调变电压馈入端98.vset:第三系统电压端99.vss:第二系统电压端具体实施方式100.下列系举实施例配合所附图示做详细说明,但所提供的实施例并非用以限制本揭露所涵盖的范围,而结构运作的描述非用以限制其执行顺序,任何由元件重新组合的结构,所产生具有均等功效的装置,皆为本揭露所涵盖的范围。另外,图示仅以说明为目的,并未依照原尺寸作图。为使便于理解,下述说明中相同元件或相似元件将以相同的符号标示来说明。101.在全篇说明书与申请专利范围所使用的用词(terms),除有特别注明除外,通常具有每个用词使用在此领域中、在此揭露的内容中与特殊内容中的平常意义。102.于本文中,除非内文对于冠词有特别限定,否则“一”与“该”可泛指单一个或多个。此外,本文使用的“包含”、“包括”、“具有”、以及相似词汇,系用以指明所记载的特征、区域、整数、步骤、操作、元件及/或组件,惟其并不排除其所述的或额外的一个或多个特征、区域、整数、步骤、操作、元件、组件、及/或其中的群组。又,本文以下使用的“及/或”的词汇,系包含了列出的关联项目中的一个或多个的任何组合。103.于本文中,当一元件被描述为系“连接”、“耦接”或“电性连接”至另一元件时,该元件可为直接连接、直接耦接或直接电性连接至该另一元件,亦可为该二元件之间有一额外元件存在,而该元件间接连接、间接耦接或间接电性连接至该另一元件。然而,当一元件被描述为系“直接连接”、“直接耦接”或“直接电性连接”至另一元件时,该二元件应被理解为其中是没有额外元件存在的。此外,当一元件被描述为系“连线”、“通讯连接”至另一元件时,该元件可为通过其他元件而间接与另一元件进行有线与/或无线通讯,亦可为一元件无须通过其他元件而实体连接至另一元件。此外,虽然本文中使用“第一”、“第二”、…等用语描述不同元件,该用语仅是用以区别以相同技术用语描述的元件或操作。104.本揭示内容揭露一种驱动电路。请参照图1,图1为根据本揭示内容一实施例的驱动电路100的电路架构图。驱动电路100包含脉幅调变电路pam及脉宽调变电路pwm。脉幅调变电路pam用以控制驱动信号的大小,脉宽调变电路pwm用以控制驱动信号的持续时间,驱动信号用以驱动发光二极管。在一实施例中,驱动信号用以驱动微型发光二极管(microlightemittingdiode)。脉幅调变电路pam包含第一晶体管t1、第一电容c1以及第二晶体管t2。如图1所示,第一晶体管t1的栅极端、第一电容c1的第一端以及第二晶体管t2的第一端相互电性连接,第二晶体管t2的第二端电性连接第一晶体管t1的第二端。脉宽调变电路pwm包含第二电容c2、第三晶体管t3以及第四晶体管t4。如图1所示,第三晶体管t3的栅极端、第二电容c2的第二端以及第四晶体管t4的第一端相互电性连接,第四晶体管t4的第二端电性连接第三晶体管t3的第二端,第四晶体管t4的栅极端电性连接第二晶体管t2的栅极端且用以接收第一控制信号pg。105.在一实施例中,脉幅调变电路pam进一步包含第五晶体管t5、第六晶体管t6以及第七晶体管t7,脉宽调变电路pwm进一步包含第八晶体管t8、第九晶体管t9以及第十晶体管t10。如图1所示,第五晶体管t5的第一端、第一晶体管t1的第一端以及第六晶体管t6的第一端相互电性连接,第五晶体管t5的栅极端用以接收发光信号em,第五晶体管t5的第二端、第一电容c1的第二端以及第七晶体管t7的第一端相互电性连接,第六晶体管t6的栅极端用以接收发光信号em,第六晶体管t6的第二端电性连接第一系统电压端vdd,第七晶体管t7的第二端电性连接第一系统电压端vdd;第八晶体管t8的第一端电性连接第一系统电压端vdd,第八晶体管t8的栅极端用以接收发光信号em,第八晶体管t8的第二端、第十晶体管t10的第一端以及第三晶体管t3的第一端相互电性连接,第十晶体管t10的栅极端用以接收发光信号em,第十晶体管t10的第二端、第九晶体管t9的第二端以及第二电容c2的第一端相互电性连接,第九晶体管t9的第一端电性连接第一系统电压端vdd。106.在一实施例中,脉幅调变电路pam进一步包含第十一晶体管t11,脉宽调变电路pwm进一步包含第十二晶体管t12以及第三电容c3。如图1所示,第十一晶体管t11的第一端电性连接脉幅调变电压馈入端vpam,第十一晶体管t11的第二端、第一晶体管t1的第一端、第五晶体管t5的第一端以及第六晶体管t6的第一端相互电性连接,第十二晶体管t12的第一端电性连接脉宽调变电压馈入端vpwm,第十二晶体管t12的第二端、第八晶体管t8的第二端、第十晶体管t10的第一端以及第三晶体管t3的第一端相互电性连接,第三电容c3的第一端、第二电容c2的第二端、第三晶体管t3的栅极端以及第四晶体管t4的第一端相互电性连接,第三电容c3的第二端用以接收第二控制信号swp。107.在一实施例中,如图1所示,第七晶体管t7、第九晶体管t9、第十一晶体管t11及第十二晶体管t12各自的栅极端皆用以接收第三控制信号sp。108.在一实施例中,驱动电路100进一步包含发光控制电路emc以及发光装置emd,发光装置emd包含第十三晶体管t13及发光二极管led。如图1所示,发光控制电路emc电性连接脉幅调变电路pam及脉宽调变电路pwm,第十三晶体管t13的第一端电性连接发光控制电路emc,第十三晶体管t13的栅极端用以接收发光信号em,发光二极管led的阳极端电性连接第十三晶体管t13的第二端,发光二极管led的阴极端电性连接第二系统电压端vss。在一实施例中,脉幅调变电路pam用以控制流经发光二极管led的电流大小,脉宽调变电路pwm用以控制开启至关断发光二极管led电流的时间。109.在一实施例中,发光控制电路emc进一步包含第二十晶体管t20、第二十一晶体管t21、第二十二晶体管t22、第二十三晶体管t23以及第四电容c4。如图1所示,第二十晶体管t20的第一端、第一晶体管t1的第二端及第二晶体管t2的第二端相互电性连接,第二十晶体管t20的栅极端、第三晶体管t3的第二端、第四晶体管t4的第二端、第二十一晶体管t21的第一端、第二十二晶体管t22的第一端以及第四电容c4的第一端相互电性连接,第二十晶体管t20的第二端、第十三晶体管t13的第一端及第二十三晶体管t23的第一端相互电性连接,第二十一晶体管t21的栅极端用以接收重置信号rst,第二十一晶体管t21的第二端电性连接第三系统电压端vset,第二十二晶体管t22的栅极端用以接收设定信号set,第二十二晶体管t22的第二端电性连接第三系统电压端vset并与第四电容c4的第二端以及第二十三晶体管t23的第二端相互电性连接,第二十三晶体管t23的栅极端用以接收重置信号rst。110.在一实施例中,驱动电路100中使用的晶体管皆为p型晶体管(p-typetransistor),当其栅极端受有低电位或低逻辑电平时,其源极端至漏极端间将被导通。111.在一实施例中,驱动电路100依序操作于重置期间p1、数据写入期间p2、开启电流路径期间p3以及发光期间p4。请参照图2,图2为根据本揭示内容一实施例的图1中的驱动电路100的控制信号时序图。在重置期间p1内,重置信号rst具有低逻辑电平,第一控制信号pg具有低逻辑电平,第三控制信号sp具有高逻辑电平,设定信号set具有高逻辑电平,发光信号em具有高逻辑电平,第二控制信号swp具有高逻辑电平。112.请接着参照图3a,图3a为根据本揭示内容一实施例的图1中的驱动电路100在重置期间p1中的电路状态图。在重置期间p1内,根据前述重置信号rst、第一控制信号pg、第三控制信号sp、设定信号set、发光信号em以及第二控制信号swp的逻辑电平,第十一晶体管t11、第十二晶体管t12、第六晶体管t6、第八晶体管t8、第五晶体管t5、第十晶体管t10、第七晶体管t7、第九晶体管t9、第十三晶体管t13以及第二十二晶体管t22为关闭状态,第四晶体管t4、第二十一晶体管t21、第二晶体管t2、第二十晶体管t20以及第二十三晶体管t23为导通状态。113.在重置期间p1内,第三系统电压端vset的电压电平通过第二十一晶体管t21及第四晶体管t4传送至第三晶体管t3的栅极端,使得第三晶体管t3栅极端的电压电平实质等于第三系统电压端vset的电压电平,此外,第三系统电压端vset的电压电平通过第二十三晶体管t23、第二十晶体管t20及第二晶体管t2传送至第一晶体管t1的栅极端,使得第一晶体管t1栅极端的电压电平实质等于第三系统电压端vset的电压电平。因此,在重置期间p1内,驱动电路100将第三晶体管t3栅极端及第一晶体管t1栅极端的电压电平重置为实质等于第三系统电压端vset的电压电平,以利进行驱动电路100进行后续的发光操作。在一实施例中,第三系统电压端vset的电压电平为低电位。114.请再参照图2。在数据写入期间p2内,重置信号rst具有高逻辑电平,第一控制信号pg具有低逻辑电平,第三控制信号sp具有低逻辑电平,设定信号set具有高逻辑电平,发光信号em具有高逻辑电平,第二控制信号swp具有高逻辑电平。115.请接着参照图3b,图3b为根据本揭示内容一实施例的图1中的驱动电路100在数据写入期间p2中的电路状态图。在数据写入期间p2内,根据前述重置信号rst、第一控制信号pg、第三控制信号sp、设定信号set、发光信号em以及第二控制信号swp的逻辑电平,第六晶体管t6、第八晶体管t8、第五晶体管t5、第十晶体管t10、第二十晶体管t20、第二十一晶体管t21、第二十二晶体管t22、第二十三晶体管t23以及第十三晶体管t13为关闭状态,第七晶体管t7、第九晶体管t9、第十二晶体管t12、第三晶体管t3、第四晶体管t4、第十一晶体管t11、第一晶体管t1以及第二晶体管t2为导通状态。116.在数据写入期间p2内,第一系统电压端vdd的电压电平通过第七晶体管t7传送至第一电容c1的第二端,并通过第九晶体管t9传送至第二电容c2的第一端,使得第一电容c1第二端以及第二电容c2第一端的电压电平实质等于第一系统电压端vdd的电压电平。同时,脉幅调变电压馈入端vpam的电压电平通过第十一晶体管t11、第一晶体管t1以及第二晶体管t2传送至第一晶体管t1的栅极端(亦为第一电容c1的第一端),使得第一晶体管t1栅极端的电压电平实质等于脉幅调变电压馈入端vpam的电压电平。同时,脉宽调变电压馈入端vpwm的电压电平将通过第十二晶体管t12、第三晶体管t3以及第四晶体管t4传送至第三晶体管t3的栅极端(亦为第二电容c2的第二端),使得第三晶体管t3栅极端的电压电平实质等于脉宽调变电压馈入端vpwm的电压电平。117.请再参照图2。在开启电流路径期间p3内,重置信号rst具有高逻辑电平,第一控制信号pg具有高逻辑电平,第三控制信号sp具有高逻辑电平,设定信号set具有低逻辑电平,发光信号em具有高逻辑电平,第二控制信号swp具有高逻辑电平。118.请接着参照图3c,图3c为根据本揭示内容一实施例的图1中的驱动电路100在开启电流路径期间p3中的电路状态图。在开启电流路径期间p3内,根据前述重置信号rst、第一控制信号pg、第三控制信号sp、设定信号set、发光信号em以及第二控制信号swp的逻辑电平,第十一晶体管t11、第十二晶体管t12、第六晶体管t6、第八晶体管t8、第五晶体管t5、第十晶体管t10、第七晶体管t7、第九晶体管t9、第二晶体管t2、第四晶体管t4、第二十一晶体管t21、第二十三晶体管t23以及第十三晶体管t13为关闭状态,第二十二晶体管t22为导通状态。119.在开启电流路径期间p3内,第三系统电压端vset的电压电平通过第二十二晶体管t22传送至第二十晶体管t20的栅极端,使得第二十晶体管t20栅极端的电压电平实质等于第三系统电压端vset的电压电平。因此,在开启电流路径期间p3内,第二十晶体管t20的栅极端具有低电位,第二十晶体管t20因而被导通。120.请再参照图2。在发光期间p4内,重置信号rst具有高逻辑电平,第一控制信号pg具有高逻辑电平,第三控制信号sp具有高逻辑电平,设定信号set具有高逻辑电平,发光信号em具有低逻辑电平,第二控制信号swp具有由高至低下降的逻辑电平。在一实施例中,第二控制信号swp具有三角波的波形。121.请接着参照图3d,图3d为根据本揭示内容一实施例的图1中的驱动电路100在发光期间p4中的电路状态图。在发光期间p4内,根据前述重置信号rst、第一控制信号pg、第三控制信号sp、设定信号set、发光信号em以及第二控制信号swp的逻辑电平,第十一晶体管t11、第十二晶体管t12、第七晶体管t7、第九晶体管t9、第二晶体管t2、第四晶体管t4、第二十一晶体管t21、第二十二晶体管t22以及第二十三晶体管t23为关闭状态,第六晶体管t6、第一晶体管t1、第二十晶体管t20、第十三晶体管t13、第八晶体管t8、第三晶体管t3、第五晶体管t5以及第十晶体管t10为导通状态。122.在发光期间p4内,第一系统电压端vdd的电压电平通过第六晶体管t6、第一晶体管t1、第二十晶体管t20及第十三晶体管t13传送至发光二极管led的阳极端,以产生驱动信号来驱动发光二极管led进行发光。在发光期间p4的初始,第二控制信号swp为高逻辑电平,且第三晶体管t3为关闭状态;而在发光期间p4内,由于第三电容c3电性连接第三晶体管t3的栅极端,随着第二控制信号swp降低,第三晶体管t3栅极端的电压电平亦会开始降低,而当第三晶体管t3栅极端的电压电平降低至一定程度时,第三晶体管t3即会被导通,第一系统电压端vdd的电压电平将会通过第八晶体管t8及第三晶体管t3传送至第二十晶体管t20的栅极端。当第二十晶体管t20栅极端的电压电平升高至一定程度时,第二十晶体管t20即会被关闭,发光二极管led亦不再进行发光。脉宽调变电路pwm即是通过以上机制来关断脉幅调变电路pam所提供用以驱动发光二极管led的电流。123.此外,在发光期间p4内,当电流流经发光二极管led时驱动电路100将出现大的电压降(irdrop),此时通过第一电容c1耦合至第一晶体管t1的栅极端以及通过第二电容c2耦合至第三晶体管t3的栅极端,将可补偿如此的电压降情形。详细言之,第一系统电压端vdd的电压电平通过第六晶体管t6及第五晶体管t5传送至第一电容c1的第二端,因此第一电容c1的第一端可与第二端维持在与数据写入期间p2时相同的电压差,使第一晶体管t1的栅极漏极电压差(vgd)不因电压降而产生变异;第一系统电压端vdd的电压电平将通过第八晶体管t8及第十晶体管t10传送至第二电容c2的第一端,因此第二电容c2的第一端与第二端将可维持在与数据写入期间p2时相同的电压差,使第三晶体管t3的栅极漏极电压差不因电压降而产生变异。因此,第一电容c1可以稳定第一晶体管t1栅极端的电压电平,第二电容c2可以稳定第一晶体管t3栅极端的电压电平,进而补偿驱动电路100的电压降。124.综上所述,驱动电路100通过以上电路配置及信号传输方式可达到稳压的功效并防止电压降对驱动电路100造成的影响。125.在一实施例中,驱动电路100具有两种驱动模式,并根据不同的灰阶度(graylevel)来决定使用哪一种驱动模式。驱动模式包含第一模式及第二模式,在一实施例中,在八位元灰阶(8-bitgrayscale)下,当灰阶度大于等于第十一阶(l11)时,驱动电路100使用第一模式来驱动发光二极管led,当灰阶度小于第十一阶时,驱动电路100使用第二模式来驱动发光二极管led。应注意的是,前述实施例中的第十一阶不应被理解为限制本揭示内容,本

技术领域:

:中具有通常知识者可根据实际需求及/或显示器的设计,决定应在何种的条件下切换为不同模式。126.承前实施例,在第一模式下,脉宽调变电压馈入端vpwm的电压为可调变的(adjustable),脉幅调变电压馈入端vpam的电压为固定的;在第二模式下,脉宽调变电压馈入端vpwm的电压为固定的,脉幅调变电压馈入端vpam的电压为可调变的。换言之,在第一模式下,脉宽调变电路pwm以可调变的脉宽调变电压馈入端vpwm电压来控制驱动信号的持续时间(亦即控制何时关闭发光二极管led),脉幅调变电路pam以固定的脉幅调变电压馈入端vpam电压来控制驱动信号的大小(亦即控制发光二极管led的驱动电流大小)。而当灰阶度较小而切换为第二模式时,脉宽调变电路pwm以固定的脉宽调变电压馈入端vpwm电压来控制驱动信号的持续时间,脉幅调变电路pam以可调变的脉幅调变电压馈入端vpam电压来控制驱动信号的大小。127.在一实施例中,在第二模式下,固定的脉宽调变电压馈入端vpwm电压用以使发光时间延长,可调变的脉幅调变电压馈入端vpam电压用以使流经发光二极管led的电流降低,如此一来,当驱动电路100用以驱动一显示器上的多个发光二极管led时,发光二极管led位置差异所导致的信号延迟对于显示器亮度一致性(uniformity)的影响即可被降低。128.以下段落说明可藉由何种电路配置及信号传输使驱动电路100得于第一模式及第二模式之间切换。请参照图4a,图4a为根据本揭示内容一实施例的驱动电路400的电路架构图。在一实施例中,驱动电路400包含子像素驱动电路pxr、子像素驱动电路pxg、子像素驱动电路pxb,此三者分别对应至显示器中红色、绿色、蓝色的子像素(sub-pixel),此外驱动电路400尚包含第十四晶体管t14r、t14g、t14b,第一多工器m1r、m1g、m1b,第十五晶体管t15r、t15g、t15b,以及第二多工器m2r、m2g、m2b。第十四晶体管t14r、第一多工器m1r、第十五晶体管t15r以及第二多工器m2r对应至子像素驱动电路pxr,第十四晶体管t14g、第一多工器m1g、第十五晶体管t15g以及第二多工器m2g对应至子像素驱动电路pxg,第十四晶体管t14b、第一多工器m1b、第十五晶体管t15b以及第二多工器m2b对应至子像素驱动电路pxb。129.承前实施例,请同时参照图1及图4a,驱动电路400的子像素驱动电路pxr、pxg、pxb与图1实施例中的驱动电路100具有相同的电路配置,其每一者皆包含脉宽调变电路pwm、脉幅调变电路pam、发光控制电路emc及发光装置emd,且其中的所有元件(即晶体管、电容、发光二极管等)及其连接关系亦相同。130.承前实施例,请同时参照图1及图4a,在子像素驱动电路pxr中的脉宽调变电压馈入端vpwm及脉幅调变电压馈入端vpam的电压是通过第一集成电路ic1来提供,以下说明驱动电路400中子像素驱动电路pxr与第一集成电路ic1之间的电路配置。第十四晶体管t14r其第一端电性连接第一集成电路ic1,其第二端电性连接脉宽调变电路pwm中的脉宽调变电压馈入端vpwm;第一多工器m1r电性连接第十四晶体管t14r的栅极端并用以控制第十四晶体管t14r导通的时点;第十五晶体管t15r其第一端电性连接第一集成电路ic1,其第二端电性连接脉幅调变电路pam中的脉幅调变电压馈入端vpam;第二多工器m2r电性连接第十五晶体管t15r的栅极端并用以控制第十五晶体管t15r导通的时点。131.如图4a所示,子像素驱动电路pxg与第一集成电路ic1间的电路配置,相似于上述子像素驱动电路pxr与第一集成电路ic1间的电路配置。换言之,子像素驱动电路pxg的脉宽调变电路pwm通过第十四晶体管t14g电性连接第一集成电路ic1,子像素驱动电路pxg的脉幅调变电路pam通过第十五晶体管t15g电性连接第一集成电路ic,第一多工器m1g电性连接第十四晶体管t14g的栅极端,第二多工器m2g电性连接第十五晶体管t15g的栅极端。同样地,子像素驱动电路pxb与第一集成电路ic1间的电路配置相似于子像素驱动电路pxr、pxg与第一集成电路ic1间的电路配置,其电路配置及连接关系请参照以上说明,不再赘述。132.在一实施例中,如图4a所示,第十四晶体管t14r、t14g、t14b各自的第一端,以及第十五晶体管t15r、t15g、t15b各自的第一端相互电性连接。133.接着说明驱动电路400在第一模式下的控制信号。请同时参照图4a及图4b,图4b为根据本揭示内容一实施例的图4a中的驱动电路400在第一模式下的控制信号时序图。在一实施例中,第一集成电路ic1用以对子像素驱动电路pxr、pxg、pxb传送信号sic1,且信号sic1包含信号sigr1、sigg1、sigb1、sigr2、sigg2、sigb2,第一多工器m1r用以传送控制信号sm1r至第十四晶体管t14r的栅极端,第一多工器m1g用以传送控制信号sm1g至第十四晶体管t14g的栅极端,第一多工器m1b用以传送控制信号sm1b至第十四晶体管t14b的栅极端,第二多工器m2r用以传送控制信号sm2r至第十五晶体管t15r的栅极端,第二多工器m2g用以传送控制信号sm2g至第十五晶体管t15g的栅极端,第二多工器m2b用以传送控制信号sm2b至第十五晶体管t15b的栅极端。134.如图4b所示,在此实施例中,当第三控制信号sp具有低逻辑电平时(亦即子像素驱动电路pxr、pxg、pxb操作于如图3b实施例的数据写入期间p2),第一集成电路ic1传送信号sic1至子像素驱动电路pxr、pxg、pxb,以将信号sigr1、sigg1、sigb1、sigr2、sigg2、sigb2分别写入子像素驱动电路pxr、pxg、pxb中的第三晶体管t3及第一晶体管t1的栅极端(请参照图3b)。135.详细来说,如图4b所示,第一集成电路ic1首先输出信号sigr1,此时除了第三控制信号sp外,仅有控制信号sm1r具有低逻辑电平,因此第一多工器m1r传送控制信号sm1r至第十四晶体管t14r的栅极端,使第十四晶体管t14r被导通,信号sigr1因此被传送至子像素驱动电路pxr的脉宽调变电路pwm。136.接着,第一集成电路ic1输出信号sigg1,此时除了第三控制信号sp外,仅有控制信号sm1g具有低逻辑电平,因此第一多工器m1g传送控制信号sm1g至第十四晶体管t14g的栅极端,使第十四晶体管t14g被导通,信号sigg1被传送至子像素驱动电路pxg的脉宽调变电路pwm。类似地,第一集成电路ic1输出信号sigb1,且信号sigb1将被传送至子像素驱动电路pxb的脉宽调变电路pwm。137.第一集成电路ic1在输出信号sigb1后,将依序输出信号sigr2、sigg2、sigb2,此些信号分别被传送至子像素驱动电路pxr、pxg、pxb的脉幅调变电路pam。详细来说,首先,第一集成电路ic1输出信号sigr2,第二多工器m2r传送控制信号sm2r至第十五晶体管t15r的栅极端使第十五晶体管t15r被导通,因此信号sigr2被传送至子像素驱动电路pxr的脉幅调变电路pam。接着,第一集成电路ic1输出信号sigg2,第二多工器m2g传送控制信号sm2g至第十五晶体管t15g的栅极端使第十五晶体管t15g被导通,因此信号sigg2被传送至子像素驱动电路pxg的脉幅调变电路pam。最后,第一集成电路ic1输出信号sigb2,第二多工器m2b传送控制信号sm2b至第十五晶体管t15b的栅极端使第十五晶体管t15b被导通,因此信号sigb2被传送至子像素驱动电路pxb的脉幅调变电路pam。138.值得注意的是,由于在第一模式下,脉宽调变电压馈入端vpwm的电压为可调变的,脉幅调变电压馈入端vpam的电压为固定的,因此第一集成电路ic1所输出至子像素驱动电路pxr、pxg、pxb各自脉宽调变电路pwm的信号sigr1、sigg1、sigb1可具有不同的信号大小(如图4b所示),另一方面,第一集成电路ic1所输出至子像素驱动电路pxr、pxg、pxb各自脉幅调变电路pam的信号sigr2、sigg2、sigb2具有固定的信号大小(如图4b所示)。应注意的是,图4b中信号sigr1、sigg1、sigb1、sigr2、sigg2、sigb2的相对大小并非意欲限制本揭示内容,而仅为例示说明信号sigr1、sigg1、sigb1具有可调变的大小,信号sigr2、sigg2、sigb2则具有相同且固定的大小。139.关于驱动电路400在第二模式下的控制信号,请同时参照图4a及图4c,图4c为根据本揭示内容一实施例的图4a中的驱动电路400在第二模式下的控制信号时序图。类似于图4b的实施例,在图4c的实施例中,控制信号sm1r、sm1g、sm1b、sm2r、sm2g、sm2b分别在不同的时段具有低逻辑电平,第一集成电路c1则针对不同的时段输出对应的信号sigr1、sigg1、sigb1、sigr2、sigg2、sigb2。例如,第一集成电路ic1首先输出信号sigr1,此时除了第三控制信号sp外,仅有控制信号sm1r具有低逻辑电平,因此第十四晶体管t14r被导通,信号sigr1将被传送至子像素驱动电路pxr的脉宽调变电路pwm。关于其他信号(即信号sigg1、sigb1、sigr2、sigg2、sigb2)在第二模式下的传输,可参照前述相关说明,不再赘述。140.值得注意的是,由于在第二模式下,脉宽调变电压馈入端vpwm的电压为固定的,脉幅调变电压馈入端vpam的电压为可调变的,因此第一集成电路ic1所输出至子像素驱动电路pxr、pxg、pxb各自脉宽调变电路pwm的信号sigr1、sigg1、sigb1具有固定的信号大小(如图4c所示),另一方面,第一集成电路ic1所输出至子像素驱动电路pxr、pxg、pxb各自脉幅调变电路pam的信号sigr2、sigg2、sigb2可具有不同的信号大小(如图4c所示)。应注意的是,图4c中信号sigr1、sigg1、sigb1、sigr2、sigg2、sigb2的相对大小并非意欲限制本揭示内容,而仅为例示说明信号sigr1、sigg1、sigb1具有相同且固定的大小,信号sigr2、sigg2、sigb2则具有可调变的大小。141.请参照图4d,图4d为根据本揭示内容一实施例的第一模式及第二模式下的驱动电流-时间关系图。如前所述,本揭示内容的驱动电路在高灰阶度(即高亮度)时使用第一模式。在图4d中,曲线c1及曲线c2代表显示器中不同位置的发光二极管在第一模式下驱动电路与时间的关系。在第一模式下,脉幅调变电压馈入端vpam的电压为固定的,因此可以提供大的驱动电流以提高发光二极管至最大亮度,进而提升显示器的对比度。142.另一方面,本揭示内容在低灰阶度(即低亮度)时使用第二模式。在图4d中,曲线c3及曲线c4代表显示器中不同位置的发光二极管在第二模式下驱动电路与时间的关系。由于曲线c4所代表的发光二极管相对于曲线c3所代表的发光二极管,与显示器中驱动电路的控制信号具有较远的距离,因此驱动电路控制信号关断两个发光二极管的时间将有一时间差dt(或者说信号延迟)。如此的时间差dt即会造成两个发光二极管的亮度不一致,此亮度不一致等同于曲线c3所形成面积与曲线c4所形成面积之间的差异(即图4d中的面积a1)。143.值得注意的是,在低灰阶时使用第二模式,相较于不使用第二模式,能够降低不同位置发光二极管的亮度不一致。曲线c5及曲线c6代表显示器中不同位置的发光二极管在低灰阶时使用第一模式的驱动电路与时间的关系。曲线c5及曲线c6所代表发光二极管接收的控制信号同样地会有时间差dt,且其亮度不一致等同面积a2。从曲线c5及曲线c6可看出,在低灰阶时若使用大的驱动电流则其发光时间将较短,因此时间差dt所造成的不同位置发光二极管的亮度差异将影响较大。由于面积a2相比于曲线c5所形成面积具有较高的比值,面积a1相比于曲线c3所形成面积具有较低的比值,因此在低灰阶时使用第一模式的亮度不一致将大于使用第二模式的亮度不一致,代表在低灰阶时使用第二模式有助于提高不同位置发光二极管的亮度一致性。144.在另一实施例中,驱动电路100可通过不同的电路配置及信号传输以于第一模式及第二模式之间切换。请参照图5a,图5a为根据本揭示内容一实施例的驱动电路500的电路架构图。在一实施例中,驱动电路500包含子像素驱动电路pxr、子像素驱动电路pxg、子像素驱动电路pxb,此外驱动电路500尚包含第十六晶体管t16r、t16g、t16b,第三多工器m3r、m3g、m3b,以及第十七晶体管t17r、t17g、t17b。子像素驱动电路pxr、pxg、pxb与图1实施例的驱动电路100具有相同元件及其连接关系,第十六晶体管t16r、第三多工器m3r以及第十七晶体管t17r对应至子像素驱动电路pxr,第十六晶体管t16g、第三多工器m3g以及第十七晶体管t17g对应至子像素驱动电路pxg,第十六晶体管t16b、第三多工器m3b以及第十七晶体管t17b对应至子像素驱动电路pxb。子像素驱动电路pxr、pxg、pxb与图1实施例中的驱动电路100具有相同的电路配置。145.承前实施例,请同时参照图1及图5a,子像素驱动电路pxr、pxg、pxb中各自的脉宽调变电压馈入端vpwm的电压是通过第二集成电路ic2来提供,而其各自的脉幅调变电压馈入端vpam的电压是通过第三集成电路ic3来提供。146.以下说明子像素驱动电路pxr与第二集成电路ic2及第三集成电路ic3间的电路配置。第十六晶体管t16r其第一端电性连接第二集成电路ic2,其第二端电性连接脉宽调变电路pwm中的脉宽调变电压馈入端vpwm;第十七晶体管t17r其第一端电性连接第三集成电路ic3,其第二端电性连接脉幅调变电路pam中的脉幅调变电压馈入端vpam;第三多工器m3r电性连接第十六晶体管t16r以及第十七晶体管t17r的栅极端,且用以控制第十六晶体管t16r以及第十七晶体管t17r导通的时点。147.如图5a所示,子像素驱动电路pxg与第二集成电路ic2及第三集成电路ic3间的电路配置,相似于上述子像素驱动电路pxr与第二集成电路ic2及第三集成电路ic3间的电路配置。换言之,子像素驱动电路pxg的脉宽调变电路pwm通过第十六晶体管t16g电性连接第二集成电路ic2,子像素驱动电路pxg的脉幅调变电路pam通过第十七晶体管t17g电性连第三集成电路ic3,第三多工器m3g电性连接第十六晶体管t16g以及第十七晶体管t17g的栅极端。同样地,子像素驱动电路pxb与第二集成电路ic2及第三集成电路ic3间的电路配置相似于子像素驱动电路pxr、pxg与第二集成电路ic2及第三集成电路ic3间的电路配置,请参照以上说明。148.在一实施例中,如图5a所示,第十六晶体管t16r、t16g、t16b各自的第一端,以及第十七晶体管t17r、t17g、t17b各自的第一端相互电性连接。149.接着说明驱动电路500在第一模式下的控制信号。请同时参照图5a及图5b,图5b为根据本揭示内容一实施例的图5a中的驱动电路500在第一模式下的控制信号时序图。在一实施例中,第二集成电路ic2用以对子像素驱动电路pxr、pxg、pxb传送信号sic2,且信号sic2包含信号sigr3、sigg3、sigb3,第三集成电路ic3用以对子像素驱动电路pxr、pxg、pxb传送信号sic3,且信号sic3包含信号sigr4、sigg4、sigb4,第一多工器m3r用以传送控制信号sm3r至第十七晶体管t17r的栅极端,第一多工器m3g用以传送控制信号sm3g至第十七晶体管t17g的栅极端,第一多工器m3b用以传送控制信号sm3b至第十七晶体管t17b的栅极端。150.如图5b所示,在此实施例中,当第三控制信号sp具有低逻辑电平时(亦即子像素驱动电路pxr、pxg、pxb操作于如图3b实施例的数据写入期间p2时),第二集成电路ic2传送信号sic2至子像素驱动电路pxr、pxg、pxb,第三集成电路ic3传送信号sic3至子像素驱动电路pxr、pxg、pxb,以将信号sigr3、sigg3、sigb3、sigr4、sigg4、sigb4分别写入子像素驱动电路pxr、pxg、pxb中的第三晶体管t3及第一晶体管t1的栅极端(请参照图3b)。151.详细来说,如图5b所示,首先,第二集成电路ic2输出信号sigr3,同时第三集成电路ic3输出信号sigr4,此时除了第三控制信号sp外,仅有控制信号sm3r具有低逻辑电平,因此第十六晶体管t16r及第十七晶体管t17r被导通,信号sigr3进而被传送至子像素驱动电路pxr的脉宽调变电路pwm,信号sigr4被传送至子像素驱动电路pxr的脉幅调变电路pam。152.接着,第二集成电路ic2输出信号sigg3,同时第三集成电路ic3输出信号sigg4,此时除了第三控制信号sp外,仅有控制信号sm3g具有低逻辑电平,因此第十六晶体管t16g及第十七晶体管t17g被导通,信号sigg3进而被传送至子像素驱动电路pxg的脉宽调变电路pwm,信号sigg4被传送至子像素驱动电路pxg的脉幅调变电路pam。153.接着,第二集成电路ic2输出信号sigb3,同时第三集成电路ic3输出信号sigb4,此时除了第三控制信号sp外,仅有控制信号sm3b具有低逻辑电平,因此第十六晶体管t16b及第十七晶体管t17b被导通,信号sigb3进而被传送至子像素驱动电路pxb的脉宽调变电路pwm,信号sigb4被传送至子像素驱动电路pxb的脉幅调变电路pam。154.值得注意的是,由于在第一模式下,脉宽调变电压馈入端vpwm的电压为可调变的,脉幅调变电压馈入端vpam的电压为固定的,因此第二集成电路ic2所输出至子像素驱动电路pxr、pxg、pxb各自脉宽调变电路pwm的信号sigr3、sigg3、sigb3可具有不同的信号大小(如图5b所示),另一方面,第三集成电路ic3所输出至子像素驱动电路pxr、pxg、pxb各自脉幅调变电路pam的信号sigr4、sigg4、sigb4具有固定的信号大小(如图5b所示)。应注意的是,图5b中信号sigr3、sigg3、sigb3、sigr4、sigg4、sigb4的相对大小并非意欲限制本揭示内容,而仅为例示说明信号sigr3、sigg3、sigb3具有可调变的大小,信号sigr4、sigg4、sigb4则具有相同且固定的大小。155.关于驱动电路500在第二模式下的控制信号,请参照图5c,图5c为根据本揭示内容一实施例的图5a中的驱动电路500在第二模式下的控制信号时序图。类似于图5b的实施例,在图5c的实施例中,控制信号sm3r、sm3g、sm3b分别在不同的时段具有低逻辑电平,第二集成电路ic2及第三集成电路ic3则针对不同的时段输出对应的信号sigr3、sigg3、sigb3、sigr4、sigg4、sigb4。例如,首先,第二集成电路ic2输出信号sigr3,同时第三集成电路ic3输出信号sigr4,此时除了第三控制信号sp外,仅有控制信号sm3r具有低逻辑电平,因此第十六晶体管t16r及第十七晶体管t17r被导通,信号sigr3将被传送至子像素驱动电路pxr的脉宽调变电路pwm,信号sigr4将被传送至子像素驱动电路pxr的脉幅调变电路pam。关于后续其他信号(sigg3、sigb3、sigg4、sigb4)的传输,可参照前述相关说明。156.值得注意的是,由于在第二模式下,脉宽调变电压馈入端vpwm的电压为固定的,脉幅调变电压馈入端vpam的电压为可调变的,因此第二集成电路ic2所输出至子像素驱动电路pxr、pxg、pxb中各自脉宽调变电路pwm的信号sigr3、sigg3、sigb3具有固定的信号大小(如图5c所示),另一方面,第三集成电路ic3所输出至子像素驱动电路pxr、pxg、pxb各自脉幅调变电路pam的信号sigr4、sigg4、sigb4可具有不同的信号大小(如图5c所示)。应注意的是,图5c中信号sigr3、sigg3、sigb3、sigr4、sigg4、sigb4的相对大小并非意欲限制本揭示内容,而仅为例示说明信号sigr3、sigg3、sigb3具有相同且固定的大小,信号sigr4、sigg4、sigb4则具有可调变的大小。157.同样地,驱动电路500通过在低灰阶时切换为使用第二模式,有助于提升显示器上不同位置发光二极管的亮度一致性。请参照前述关于图4d的说明。158.在另一实施例中,驱动电路100可通过不同的电路配置及信号传输以于第一模式及第二模式之间切换。请参照图6a,图6a为根据本揭示内容一实施例的驱动电路600的电路架构图。在一实施例中,驱动电路600包含子像素驱动电路pxr、子像素驱动电路pxg、子像素驱动电路pxb,此外驱动电路600尚包含第十八晶体管t18r、t18g、t18b,第四多工器m4r、m4g、m4b,以及第十九晶体管t19r、t19g、t19b。第十八晶体管t18r、第四多工器m4r以及第十九晶体管t19r对应至子像素驱动电路pxr,第十八晶体管t18g、第四多工器m4g以及第十九晶体管t19g对应至子像素驱动电路pxg,第十八晶体管t18b、第四多工器m4b以及第十九晶体管t19b对应至子像素驱动电路pxb。159.图6a实施例中的子像素驱动电路pxr、pxg、pxb与图1实施例中的驱动电路100具有类似的元件及其连接关系,不过其控制信号的接收则有不同。请同时参照图1及图6b,图6b为根据本揭示内容一实施例的驱动电路100’的电路架构图。驱动电路100’即为图6a实施例中子像素驱动电路pxr、pxg、pxb三者各自的电路结构。驱动电路100’与图1的驱动电路100具有同样的元件及连接关系,两者的不同点在于在驱动电路100’中,如图6b所示,第九晶体管t9及第十二晶体管t12的栅极端用以接收第四控制信号sp1,第七晶体管t7及第十一晶体管t11的栅极端用以接收第五控制信号sp2。相反地,在图1的驱动电路100中,第九晶体管t9、第十二晶体管t12、第七晶体管t7及第十一晶体管t11的栅极端皆用以接收相同的第三控制信号sp。160.请同时参照图6a及图6b,在子像素驱动电路pxr、pxg、pxb中,其各自的脉宽调变电压馈入端vpwm及脉幅调变电压馈入端vpam的电压是通过第四集成电路ic4来提供。以下说明在驱动电路600中子像素驱动电路pxr与第四集成电路ic4间的电路配置。第十八晶体管t18r其第一端电性连接第四集成电路ic4,其第二端电性连接脉宽调变电路pwm中的脉宽调变电压馈入端vpwm;第十九晶体管t19r其第一端电性连接第四集成电路ic4,其第二端电性连接脉幅调变电路pam中的脉幅调变电压馈入端vpam;第四多工器m4r电性连接第十八晶体管t18r以及第十九晶体管t19r的栅极端,且用以控制第十八晶体管t18r以及第十九晶体管t19r导通的时点。161.如图6a所示,子像素驱动电路pxg与第四集成电路ic4间的电路配置,相似于上述子像素驱动电路pxr与第四集成电路ic4间的电路配置。换言之,子像素驱动电路pxg的脉宽调变电路pwm通过第十八晶体管t18g电性连接第四集成电路ic4,子像素驱动电路pxg的脉幅调变电路pam通过第十九晶体管t19g电性连接第四集成电路ic4,第四多工器m4g电性连接第十八晶体管t18g以及第十九晶体管t19g的栅极端。同样地,子像素驱动电路pxb与第四集成电路ic4间的电路配置相似于子像素驱动电路pxr、pxg与第四集成电路ic4间的电路配置,请参照以上说明。162.在一实施例中,如图6a所示,第十八晶体管t18r、t18g、t18b各自的第一端,以及第十九晶体管t19r、t19g、t19b各自的第一端相互电性连接。163.接着说明驱动电路600在第一模式下的控制信号。请同时参照图6a及图6c,图6c为根据本揭示内容一实施例的图6a中的驱动电路600在第一模式下的控制信号时序图。在一实施例中,第四集成电路ic4用以对子像素驱动电路pxr、pxg、pxb传送信号sic4,且信号sic4包含信号sigr5、sigg5、sigb5、sigr6、sigg6、sigb6,第四多工器m4r用以传送控制信号sm4r至第十八晶体管t18r及第十九晶体管t19r的栅极端,第四多工器m4g用以传送控制信号sm4g至第十八晶体管t18g及第十九晶体管t19g的栅极端,第四多工器m4b用以传送控制信号sm4b至第十八晶体管t18b及第十九晶体管t19b的栅极端。164.请同时参照图6a、图6b及图6c,当第四控制信号sp1具有低逻辑电平时,第四集成电路ic4传送信号sigr5、sigg5、sigb5至子像素驱动电路pxr、pxg、pxb的脉宽调变电路pwm,以将信号sigr5、sigg5、sigb5分别写入子像素驱动电路pxr、pxg、pxb中的第三晶体管t3的栅极端。而当第五控制信号sp2具有低逻辑电平时,第四集成电路ic4传送信号sigr6、sigg6、sigb6至子像素驱动电路pxr、pxg、pxb的脉幅调变电路pam,以将信号sigr6、sigg6、sigb6分别写入子像素驱动电路pxr、pxg、pxb中的第一晶体管t1的栅极端。165.详细来说,如图6c所示,首先,第四集成电路ic4输出信号sigr5,此时除了第四控制信号sp1外,仅有控制信号sm4r具有低逻辑电平,因此第十八晶体管t18r及第十九晶体管t19r被导通,信号sigr5被传送至子像素驱动电路pxr的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第五控制信号sp2为高逻辑电平,因此子像素驱动电路pxr的脉幅调变电路pam的第十一晶体管t11并不会被导通(请参照图6b),信号sigr5不会被写入至第一晶体管t1的栅极端。166.接着,第四集成电路ic4输出信号sigg5,此时除了第四控制信号sp1外,仅有控制信号sm4g具有低逻辑电平,因此第十八晶体管t18g及第十九晶体管t19g被导通,信号sigg5被传送至子像素驱动电路pxg的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第五控制信号sp2为高逻辑电平,因此子像素驱动电路pxg的脉幅调变电路pam的第十一晶体管t11并不会被导通(请参照图6b),信号sigg5不会被写入至第一晶体管t1的栅极端。167.接着,第四集成电路ic4输出信号sigb3,此时除了第四控制信号sp1外,仅有控制信号sm4b具有低逻辑电平,因此第十八晶体管t18b及第十九晶体管t19b被导通,信号sigb5被传送至子像素驱动电路pxb的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第五控制信号sp2为高逻辑电平,因此子像素驱动电路pxb的脉幅调变电路pam的第十一晶体管t11并不会被导通(请参照图6b),信号sigb5不会被写入至第一晶体管t1的栅极端。168.接着,第四集成电路ic4输出信号sigr6,此时除了第五控制信号sp2外,仅有控制信号sm4r具有低逻辑电平,因此第十八晶体管t18r及第十九晶体管t19r被导通,信号sigr6被传送至子像素驱动电路pxr的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第四控制信号sp1为高逻辑电平,因此子像素驱动电路pxr的脉宽调变电路pwm的第十二晶体管t12并不会被导通(请参照图6b),信号sigr6不会被写入至第三晶体管t3的栅极端。169.接着,第四集成电路ic4输出信号sigg6,此时除了第五控制信号sp2外,仅有控制信号sm4g具有低逻辑电平,因此第十八晶体管t18g及第十九晶体管t19g被导通,信号sigg6被传送至子像素驱动电路pxg的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第四控制信号sp1为高逻辑电平,因此子像素驱动电路pxg的脉宽调变电路pwm的第十二晶体管t12并不会被导通(请参照图6b),信号sigg6不会被写入至第三晶体管t3的栅极端。170.接着,第四集成电路ic4输出信号sigb6,此时除了第五控制信号sp2外,仅有控制信号sm4b具有低逻辑电平,因此第十八晶体管t18b及第十九晶体管t19b被导通,信号sigb6被传送至子像素驱动电路pxb的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第四控制信号sp1为高逻辑电平,因此子像素驱动电路pxb的脉宽调变电路pwm的第十二晶体管t12并不会被导通(请参照图6b),信号sigb6不会被写入至第三晶体管t3的栅极端。171.值得注意的是,由于在第一模式下,脉宽调变电压馈入端vpwm的电压为可调变的,脉幅调变电压馈入端vpam的电压为固定的,因此第四集成电路ic4所输出至子像素驱动电路pxr、pxg、pxb中各自脉宽调变电路pwm的信号sigr5、sigg5、sigb5可具有不同的信号大小(如图6c所示),另一方面,第四集成电路ic4所输出至子像素驱动电路pxr、pxg、pxb中各自脉幅调变电路pam的信号sigr6、sigg6、sigb6具有固定的信号大小(如图6c所示)。应注意的是,图6c中信号sigr5、sigg5、sigb5、sigr6、sigg6、sigb6的相对大小并非意欲限制本揭示内容,而仅为例示说明信号sigr5、sigg5、sigb5具有可调变的大小,信号sigr6、sigg6、sigb6则具有相同且固定的大小。172.关于驱动电路600在第二模式下的控制信号,请参照图6d,图6d为根据本揭示内容一实施例的图6a中的驱动电路600在第二模式下的控制信号时序图。类似于图6c的实施例,在图6d的实施例中,控制信号sm4r、sm4g、sm4b分别在不同的时段具有低逻辑电平,第四集成电路ic4则针对不同的时段输出对应的信号sigr5、sigg5、sigb5、sigr6、sigg6、sigb6。例如,首先,第四集成电路ic4输出信号sigr5,此时除了第四控制信号sp1外,仅有控制信号sm4r具有低逻辑电平,因此第十八晶体管t18r及第十九晶体管t19r被导通,信号sigr5将被传送至子像素驱动电路pxr的脉宽调变电路pwm及脉幅调变电路pam,不过由于此时第五控制信号sp2为高逻辑电平,因此子像素驱动电路pxr的脉幅调变电路pam的第十一晶体管t11并不会被导通(请参照图6b),信号sigr5不会被写入至第一晶体管t1的栅极端。关于后续其他信号(亦即sigg5、sigb5、sigr6、sigg6、sigb6)的传输,可参照前述相关说明,不再赘述。173.值得注意的是,由于在第二模式下,脉宽调变电压馈入端vpwm的电压为固定的,脉幅调变电压馈入端vpam的电压为可调变的,因此第四集成电路ic4所输出至子像素驱动电路pxr、pxg、pxb中各自脉宽调变电路pwm的信号sigr5、sigg5、sigb5具有固定的信号大小(如图6d所示),另一方面,第四集成电路ic4所输出至子像素驱动电路pxr、pxg、pxb中各自脉幅调变电路pam的信号sigr6、sigg6、sigb6可具有不同的信号大小(如图6d所示)。应注意的是,图6d中信号sigr5、sigg5、sigb5、sigr6、sigg6、sigb6的相对大小并非意欲限制本揭示内容,而仅为例示说明信号sigr5、sigg5、sigb5具有相同且固定的大小,信号sigr6、sigg6、sigb6则具有可调变的大小。174.同样地,驱动电路600通过在低灰阶时切换为使用第二模式,有助于提升显示器上不同位置发光二极管的亮度一致性。请参照前述关于图4d的说明。175.综上所述,通过如图4a、图5a、图6a及图6b所示的电路配置,以及如图4b、图4c、图5b、图5c、图6c、图6d所示的控制信号时序,本揭示内容的驱动电路可具有第一模式及第二模式,以根据不同的灰阶度采取不同驱动模式,进而改善显示器的亮度一致性。176.根据前揭实施例的说明,本揭示内容亦揭露一种驱动方法。请参照图7,图7为根据本揭示内容一实施例的驱动方法700的流程图。驱动方法700用以驱动像素电路(如图1的驱动电路100或图6b实施例的驱动电路100’)。如图7所示,驱动方法700包含步骤s710及步骤s720。177.在步骤s710中,在第一模式下,调变像素电路的脉宽调变电压馈入端的电压,并固定变像素电路的脉幅调变电压馈入端的电压。关于如何调变脉宽调变电压馈入端的电压并固定脉幅调变电压馈入端的电压,可参照前述图4a、图4b、图5a、图5b、图6a、图6c实施例的相关说明,应注意的是,此些实施例仅作为可执行驱动方法700的例示电路结构及控制信号时序,相关

技术领域:

:具有通常知识者若以其他类似的电路配置及控制信号执行驱动方法700,应理解为仍为本揭示内容所涵括。178.在步骤s720中,在第二模式下,固定变像素电路的脉宽调变电压馈入端的电压,调变变像素电路的脉幅调变电压馈入端的电压。可参照前述图4a、图4c、图5a、图5c、图6a、图6d实施例的相关说明,应注意的是,此些实施例仅作为可执行驱动方法700的例示电路结构及控制信号时序,相关

技术领域:

:具有通常知识者若以其他类似的电路配置及控制信号执行驱动方法700,应理解为仍为本揭示内容所涵括。179.其中,脉宽调变电压馈入端的电压控制驱动信号的持续时间,脉幅调变电压馈入端的电压控制驱动信号的大小。驱动信号用以驱动像素电路中的发光二极管进行发光。180.应注意的是,在一实施例中,步骤s710及步骤s720的顺序可以交换。在一实施例中,驱动方法700是根据显示器的灰阶度以决定进行第一模式或第二模式中之一者,例如在八位元灰阶下,当灰阶度大于等于第十一阶时,驱动方法使用第一模式来驱动发光二极管,当灰阶度小于第十一阶时,驱动方法使用第二模式来驱动发光二极管。181.综上所述,驱动方法700在第一模式及第二模式下,对显示器驱动面板的脉宽调变电压馈入端及脉幅调变电压馈入端施以不同的电压,进而改善显示器的亮度一致性。182.虽然本揭示内容已以实施方式揭露如上,然其并非用以限定本发明。任何熟习此技艺之人,在不脱离本揭示内容的精神及范围内,当可作各种更动及润饰。本揭示内容的保护范围当视后附的申请专利范围所界定者为准。当前第1页12当前第1页12

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。