1.本发明涉及电子电路技术领域,特别是涉及印制电路板技术领域。

背景技术:

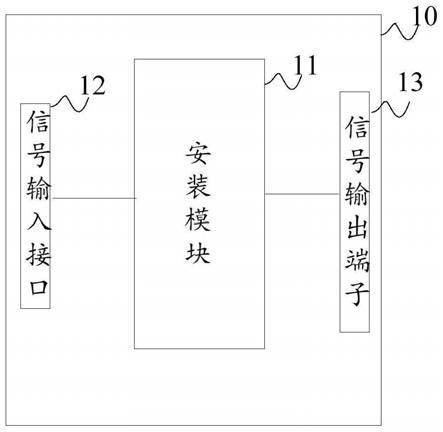

2.如图1所示,印制电路板上在设置有封装芯片110和两个连接器(例如图1中所示的连接器120和连接器130)时,从封装芯片110到连接器120的信号分布在靠近底层,从封装芯片110到连接器130的信号层分布在靠近顶层;走线1为从连接器120的焊盘(pad)连接到过孔(via)的走线,走线2为封装芯片110连接到过孔(via)的走线;走线3为过孔(via)到连接器130的走线。

3.其中,连接器120上面的走线会连接到另外一块印制电路板(pcb)或者线缆(cable),而连接器130上面的走线同样会连接到另一块印制电路板(pcb)或者线缆(cable)。

4.如何避免上述连接方式导致的高速线无法达到正常效果的问题,让封装芯片110和连接器120之间及封装芯片110和连接器130之间的高速线都可以正常工作成为本领域技术人员亟待解决的技术问题。

技术实现要素:

5.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种印制电路板及其走线布设方法,用于在一个印制电路板上连接不同连接器时对高速线的走线进行优化。

6.为实现上述目的及其他相关目的,本发明提供一种印制电路板,包括:封装芯片和至少两个连接器,其中:所述封装芯片连接不同连接器的走线分布于不同的板层;在所述封装芯片连接其中一个所述连接器时,使过孔背钻形成所述封装芯片到该连接器的高速通路,并将其他连接器对应的所述板层的铜壁钻掉。

7.于本发明的一实施例中,所述连接器包括第一连接器和第二连接器;所述封装芯片到所述第一连接器的走线布设于所述印制电路板的第一板层,所述封装芯片到所述第二连接器的走线布设于所述印制电路板的第二板层。

8.于本发明的一实施例中,在所述封装芯片连接所述第一连接器时,使过孔背钻形成所述封装芯片到所述第一连接器的高速通路,并将所述第二板层的铜壁钻掉;

9.在所述封装芯片连接所述第二连接器时,使过孔背钻形成所述封装芯片到所述第二连接器的高速通路,并将所述第一板层的铜壁钻掉。

10.于本发明的一实施例中,所述第一板层位于所述第二板层的下方时:在所述封装芯片连接所述第一连接器时,过孔的背钻从第一层开始到第一板层上面的层结束,且将所述第二板层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第一连接器的高速通路,第一连接器在所述过孔处保持连接,而第二连接器在所述过孔处断开连接;在所述封装芯片连接所述第二连接器时,过孔的背钻从第n层开始到第二层下面的层结束,且将所述第一板层和所述印制电路板的底层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第二连

接器的高速通路,所述第二连接器在所述过孔处保持连接,而所述第一连接器在所述过孔处断开连接,其中,n为印制电路板的总层数。

11.于本发明的一实施例中,在所述第一板层位于所述第二板层的上方时:在所述封装芯片连接所述第二连接器时,过孔的背钻从第一层开始到第二板层上面的层结束,且将所述第一板层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第二连接器的高速通路,第二连接器在所述过孔处保持连接,而第一连接器在所述过孔处断开连接;在所述封装芯片连接所述第一连接器时,过孔的背钻从第n层开始到第一层下面的层结束,且将所述第二板层和所述印制电路板的底层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第一连接器的高速通路,所述第一连接器在所述过孔处保持连接,而所述第二连接器在所述过孔处断开连接,其中,n为印制电路板的总层数。

12.本发明的实施例还提供一种印制电路板的走线布设方法,包括:将封装芯片连接不同连接器的走线分布于不同的板层;在所述封装芯片连接其中一个所述连接器时,使过孔背钻形成所述封装芯片到该连接器的高速通路,并将其他连接器对应的所述板层的铜壁钻掉。

13.于本发明的一实施例中,所述连接器包括第一连接器和第二连接器;所述封装芯片到所述第一连接器的走线布设于所述印制电路板的第一板层,所述封装芯片到所述第二连接器的走线布设于所述印制电路板的第二板层。

14.于本发明的一实施例中,在所述封装芯片连接所述第一连接器时,使过孔背钻形成所述封装芯片到所述第一连接器的高速通路,并将所述第二板层的铜壁钻掉;在所述封装芯片连接所述第二连接器时,使过孔背钻形成所述封装芯片到所述第二连接器的高速通路,并将所述第一板层的铜壁钻掉。

15.于本发明的一实施例中,在所述第一板层位于所述第二板层的下方时:在所述封装芯片连接所述第一连接器时,过孔的背钻从第一层开始到第一板层上面的层结束,且将所述第二板层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第一连接器的高速通路,第一连接器在所述过孔处保持连接,而第二连接器在所述过孔处断开连接;在所述封装芯片连接所述第二连接器时,过孔的背钻从第n层开始到第二层下面的层结束,且将所述第一板层和所述印制电路板的底层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第二连接器的高速通路,所述第二连接器在所述过孔处保持连接,而所述第一连接器在所述过孔处断开连接,其中,n为印制电路板的总层数。

16.于本发明的一实施例中,在所述第一板层位于所述第二板层的上方时:在所述封装芯片连接所述第二连接器时,过孔的背钻从第一层开始到第二板层上面的层结束,且将所述第一板层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第二连接器的高速通路,第二连接器在所述过孔处保持连接,而第一连接器在所述过孔处断开连接;在所述封装芯片连接所述第一连接器时,过孔的背钻从第n层开始到第一层下面的层结束,且将所述第二板层和所述印制电路板的底层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第一连接器的高速通路,所述第一连接器在所述过孔处保持连接,而所述第二连接器在所述过孔处断开连接,其中,n为印制电路板的总层数。

17.如上所述,本发明的一种印制电路板及其走线布设方法具有以下有益效果:

18.本发明通过封装芯片连接不同连接器的走线分布于不同的板层;在所述封装芯片

连接其中一个所述连接器时,并通过不同深度的背钻,使过孔背钻形成封装芯片到该连接器的高速通路,并将其他连接器对应的板层的铜壁钻掉,达到不需要做两块或多块印制电路板,就能满足高速走线连接两个(或更多)连接器的应用,从而达到降低成本的效果。

附图说明

19.图1显示为印制电路板上配置有两个连接器连接区域时的整体结构示意图;

20.图2显示为本发明的印制电路板中配置有两个连接器连接区域时的走线连接示意图;

21.图3显示为本发明的印制电路板中封装芯片连接第一连接器时实现的高速通路有效的背钻孔示意图;

22.图4显示为本发明的印制电路板中封装芯片连接第二连接器时实现的高速通路有效的背钻孔示意图。

具体实施方式

23.以下由特定的具体实施例说明本发明的实施方式,熟悉此技术的人士可由本说明书所揭露的内容轻易地了解本发明的其他优点及功效。

24.请参阅图1至图4。须知,本说明书所附图式所绘示的结构、比例、大小等,均仅用以配合说明书所揭示的内容,以供熟悉此技术的人士了解与阅读,并非用以限定本发明可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本发明所能产生的功效及所能达成的目的下,均应仍落在本发明所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“下”、“左”、“右”、“中间”及“一”等的用语,亦仅为便于叙述的明了,而非用以限定本发明可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当亦视为本发明可实施的范畴。

25.本实施例的目的在于提供一种印制电路板及其走线布设方法,用于解决在一个印制电路板上连接不同连接器时高速线无法正常工作的技术问题。

26.以下将详细阐述本实施例的一种印制电路板及其走线布设方法原理及实施方式,使本领域技术人员不需要创造性劳动即可理解本实施例的一种印制电路板及其走线布设方法。

27.如图1所示,本实施例提供一种印制电路板,所述印制电路板包括:封装芯片和至少两个连接器。

28.其中,所述封装芯片采用球栅阵列封装(bga,ball grid array package)或栅格阵列封装(lga,land grid array)。

29.其中,所述印制电路板的过孔有vippo(via-in-pad plated over,在焊盘上钻过孔)过孔和非vippo过孔(常规通孔)种孔类型,本实施例中,所述印制电路板的背面布设的为vippo过孔。

30.具体地,于本实施例中,所述封装芯片连接不同连接器的走线分布于不同的板层;在所述封装芯片连接其中一个所述连接器时,使过孔背钻形成所述封装芯片到该连接器的高速通路,并将其他连接器对应的所述板层的铜壁钻掉。

31.本实施例中的印制电路板通过封装芯片连接不同连接器的走线分布于不同的板

层;在所述封装芯片连接其中一个所述连接器时,并通过不同深度的背钻,使过孔背钻形成封装芯片到该连接器的高速通路,并将其他连接器对应的板层的铜壁钻掉,达到不需要做两块或多块印制电路板,就能满足高速走线连接两个(或更多)连接器的应用,从而达到降低成本的效果。

32.具体地,于实施例中,所述连接器包括第一连接器和第二连接器;所述封装芯片到所述第一连接器的走线布设于所述印制电路板的第一板层,所述封装芯片到所述第二连接器的走线布设于所述印制电路板的第二板层。即本实施例中的印制电路板通过封装芯片连接不同连接器的走线分布于不同的板层。

33.于本实施例中,在所述封装芯片连接所述第一连接器时,使过孔背钻形成所述封装芯片到所述第一连接器的高速通路,并将所述第二板层的铜壁钻掉;在所述封装芯片连接所述第二连接器时,使过孔背钻形成所述封装芯片到所述第二连接器的高速通路,并将所述第一板层的铜壁钻掉。

34.于本实施例中,所述第一板层位于所述第二板层的下方时:

35.在所述封装芯片连接所述第一连接器时,过孔的背钻从第一层开始到第一板层上面的层结束,且将所述第二板层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第一连接器的高速通路,第一连接器在所述过孔处保持连接,而第二连接器在所述过孔处断开连接;

36.在所述封装芯片连接所述第二连接器时,过孔的背钻从第n层开始到第二层下面的层结束,且将所述第一板层和所述印制电路板的底层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第二连接器的高速通路,所述第二连接器在所述过孔处保持连接,而所述第一连接器在所述过孔处断开连接,其中,n为印制电路板的总层数。

37.以下结合图2至图4,并以印制电路板的总层数n为28进行举例说明。

38.如图2所示,假设所述封装芯片到所述第一连接器的走线2走在第24层,所述第一连接器到所述第二连接器的走线3走在第18层,走线1是连接过孔4(via)和第一连接器的焊盘(pad)的走线,走线1、走线2、走线3这三路走线在过孔4(via)处连接。

39.如图3所示,在所述封装芯片需要连接所述第一连接器时,若要想所述封装芯片到第一连接器的高速通路有效,需要背钻从第一层开始到第24层上面的层结束,保证第24层不被钻掉,而第18层的铜壁必须钻掉,从而保证第二连接器在过孔4(via)处断开连接,而第一连接器的走线在过孔4(via)处保持连接。

40.如图4所示,在所述封装芯片需要连接所述第二连接器时,要想封装芯片到第二连接器的高速通路有效,需要背钻从第28层开始到第18层下面的层结束,保证第18层不被钻掉,而底层(bottom层)和第24层的铜壁必须钻掉,从而保证和第一连接器在过孔4(via)处断开连接,而第二连接器的走线在过孔4(via)处保持连接。

41.从上述描述中可以看出,只要第一连接器连接到封装芯片的信号所在层分布在第一连接器连接到第二连接器的信号所在层的下方,通过改变背钻方式就可以选择不同的连接器安装,而不会有任何信号质量问题。所以本实施例的印制电路板通过不同深度的背钻,使过孔4背钻形成封装芯片到该连接器的高速通路,并将其他连接器对应的板层的铜壁钻掉,达到不需要做两块或多块印制电路板,就能满足高速走线连接两个(或更多)连接器的应用。

42.相对应地,与所述第一板层位于所述第二板层的下方时相反,于本实施例中,在所述第一板层位于所述第二板层的上方时:

43.1)在所述封装芯片连接所述第二连接器时,过孔的背钻从第一层开始到第二板层上面的层结束,且将所述第一板层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第二连接器的高速通路,第二连接器在所述过孔处保持连接,而第一连接器在所述过孔处断开连接;

44.2)在所述封装芯片连接所述第一连接器时,过孔的背钻从第n层开始到第一层下面的层结束,且将所述第二板层和所述印制电路板的底层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第一连接器的高速通路,所述第一连接器在所述过孔处保持连接,而所述第二连接器在所述过孔处断开连接,其中,n为印制电路板的总层数。

45.所述第一板层位于所述第二板层的上方时的背钻方式实现原理与所述第一板层位于所述第二板层的下方时的背钻方式实现原理相同,在此不再赘述。

46.此外,本实施例仅以所述连接器为两个为例进行保护说明,当所述连接器为多个时,实现原理与所述连接器为两个时的实现原理相同或相似,在此不再赘述。

47.此外,本发明的实施例还提供一种印制电路板的走线布设方法,所述印制电路板的走线布设方法包括:

48.将封装芯片连接不同连接器的走线分布于不同的板层;在所述封装芯片连接其中一个所述连接器时,使过孔背钻形成所述封装芯片到该连接器的高速通路,并将其他连接器对应的所述板层的铜壁钻掉。

49.具体地,于本实施例中,所述连接器包括第一连接器和第二连接器;所述封装芯片到所述第一连接器的走线布设于所述印制电路板的第一板层,所述封装芯片到所述第二连接器的走线布设于所述印制电路板的第二板层。

50.其中,在所述封装芯片连接所述第一连接器时,使过孔背钻形成所述封装芯片到所述第一连接器的高速通路,并将所述第二板层的铜壁钻掉;在所述封装芯片连接所述第二连接器时,使过孔背钻形成所述封装芯片到所述第二连接器的高速通路,并将所述第一板层的铜壁钻掉。

51.于本实施例中,在所述第一板层位于所述第二板层的下方时:在所述封装芯片连接所述第一连接器时,过孔的背钻从第一层开始到第一板层上面的层结束,且将所述第二板层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第一连接器的高速通路,第一连接器在所述过孔处保持连接,而第二连接器在所述过孔处断开连接;在所述封装芯片连接所述第二连接器时,过孔的背钻从第n层开始到第二层下面的层结束,且将所述第一板层和所述印制电路板的底层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第二连接器的高速通路,所述第二连接器在所述过孔处保持连接,而所述第一连接器在所述过孔处断开连接,其中,n为印制电路板的总层数。

52.于本实施例中,在所述第一板层位于所述第二板层的上方时:在所述封装芯片连接所述第二连接器时,过孔的背钻从第一层开始到第二板层上面的层结束,且将所述第一板层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第二连接器的高速通路,第二连接器在所述过孔处保持连接,而第一连接器在所述过孔处断开连接;在所述封装芯片连接所述第一连接器时,过孔的背钻从第n层开始到第一层下面的层结束,且将所述第二板层和

所述印制电路板的底层的铜壁钻掉,使得过孔背钻形成所述封装芯片到所述第一连接器的高速通路,所述第一连接器在所述过孔处保持连接,而所述第二连接器在所述过孔处断开连接,其中,n为印制电路板的总层数。

53.所述印制电路板的走线布设方法的技术原理与上述基于图1至图4中所述的印制电路板的走线布设的技术原理相同在此不再赘述。

54.综上所述,本发明通过封装芯片连接不同连接器的走线分布于不同的板层;在所述封装芯片连接其中一个所述连接器时,并通过不同深度的背钻,使过孔背钻形成封装芯片到该连接器的高速通路,并将其他连接器对应的板层的铜壁钻掉,达到不需要做两块或多块印制电路板,就能满足高速走线连接两个(或更多)连接器的应用,从而达到降低成本的效果。所以,本发明有效克服了现有技术中的种种缺点而具有度产业利用价值。

55.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。