1.本发明主要涉及到高性能计算机技术领域,特指一种大规模多运算浮点矩阵计算加速实现方法及装置。

背景技术:

2.在许多科学和工程当中,矩阵计算是一种基础和应用广泛的运算模式,比如数字图像的存储、处理和识别,神经网络计算,控制系统中卡尔曼滤波器等。矩阵计算直接影响到高性能计算机的性能。

3.目前,cpu、gpgpu等平台利用mkl、cublas等软件库来进行矩阵计算加速,但这些方法受能耗和复杂的层级的限制,在移动系统或嵌入式系统中应用效果不佳。

4.在fpga(field-programmable gate arrays,现场可编程门阵列)开发方面,现有的相关技术中有一些关于密集矩阵-矩阵乘、稀疏矩阵-向量乘的相关研究。然而,其中大多数结构只能处理单独的某一种矩阵运算模式。实际上,在许多工程应用中,某一种矩阵运算通常是不够的,而是需要支持多种矩阵运算模式。

5.针对浮点矩阵的多运算的融合问题,有从业者提出中国专利申请“基于fpga的通用浮点矩阵处理器硬件结构”中(公开号cn104391820a),其公开了一种集成一个主机带多个不同类型矩阵操作加速器的通用矩阵计算系统,这种多个独立的矩阵运算加速器单纯组合的方式相对简单。但是,这类技术的不足之处就在于:各个模块加起来会消耗的更多的逻辑资源,面积也会增大,结构的复用性相对不足。

技术实现要素:

6.本发明要解决的技术问题就在于:针对现有技术存在的技术问题,本发明提供一种低存储需求、高计算效率、复用度高、适用范围广的的大规模多运算浮点矩阵计算加速实现方法及装置。

7.为解决上述技术问题,本发明采用以下技术方案:

8.一种大规模多运算浮点矩阵计算加速实现方法,包括:

9.步骤s1:根据待处理矩阵的操作类型,接收外部输入信号,判断矩阵运算模式:当运算模式是矩阵加、矩阵减时,转入执行步骤s3,当运行模式是矩阵乘、矩阵-向量乘、矩阵-标量乘时,转入执行步骤s2;

10.步骤s2:初始化片上ram为零,转入执行步骤s4;

11.步骤s3:通过ram通道加载数据源c到片上ram中,转入执行步骤s4;

12.步骤s4:通过ram通道预加载部分数据流a,而后边计算边加载数据流a和数据流b;

13.步骤s5:计算完后,将计算结果传输到片外存储器。

14.作为本发明方法的进一步改进:所述矩阵乘是指矩阵a和矩阵b的乘积,即实现cm×n=am×k×bk

×n cm×n,其中,数据流a、数据流b为输入数据流,数据流c在片上直接初始化为零。

15.作为本发明方法的进一步改进:所述矩阵加、矩阵减是指矩阵a和矩阵c的相加、相

减,即实现cm×k=am×k×

ik×k±cm

×k,其中,数据流a、数据流c为输入数据流,数据流b为引入的单位矩阵i,直接在片上由一个计数器产生。

16.作为本发明方法的进一步改进:所述矩阵-向量乘是指矩阵a和向量b的乘积,即实现cm×1=ak×k×bk

×1 cm×1,其中,数据流a、数据流b为输入数据流,数据流c在片上直接初始化为零。

17.作为本发明方法的进一步改进:所述矩阵-标量乘是指矩阵a和标量b的乘积,即实现cm×k=am×k×

b,其中,数据流a、数据流b为输入数据流,数据流c在片上直接初始化为零。

18.作为本发明方法的进一步改进:所述数据源包括数据源a、数据源b、数据源c,其中,数据源a指矩阵a,数据源b指矩阵b、向量b或标量b,数据源c指片上存储的参与累加矩阵或向量。

19.作为本发明方法的进一步改进:采用分块矩阵方法,包括:

20.在步骤s1之前,根据待处理矩阵规模计算分块大小,而后逐一对子块进行操作;

21.在步骤s5之后,继续进行下一个子矩阵块的计算,即重复步骤s2-s5,直至所有子块计算完成。

22.本发明进一步提供一种大规模多运算浮点矩阵计算加速装置,其包括:

23.预处理模块,用于将矩阵、向量分块,并根据待处理矩阵的操作类型,接收外部输入信号,判断矩阵运算模式:当运算模式是矩阵加、矩阵减时,通过ram通道加载数据源c到片上ram中;当运行模式是矩阵乘、矩阵-向量乘、矩阵-标量乘时,初始化片上ram为零,通过ram通道预加载部分数据流a,而后边计算边加载数据流a和数据流b;

24.数据传输控制模块,用于加载各数据源及返回数据计算结果;

25.矩阵计算加速单元模块,为若干个完全相同的基本计算单元pe组成的线性阵列结构,用于实现矩阵运算操作。

26.作为本发明装置的进一步改进:所述基本计算单元pe包括一个浮点计算部件、两个寄存器、一个fifo和一个双端口ram。

27.作为本发明装置的进一步改进:所述浮点计算部件是符合ieee 754标准的ip核,集成了乘加操作或乘减操作,具体计算时根据外部操作模式信号。

28.与现有技术相比,本发明的优点就在于:

29.1、本发明的大规模多运算浮点矩阵计算加速实现方法及装置,可完成包括矩阵乘、矩阵加、矩阵减、矩阵-向量乘、矩阵-标量乘的多种模式矩阵运算,适用范围广、使用灵活,相比于传统的基于多个加速器的方法,本发明的各个运算是基于统一的硬件结构,逻辑结构复用度高,具有资源消耗少和面积小的优势。

30.2、本发明的大规模多运算浮点矩阵计算加速实现方法及装置,采用结合流水线策略和分块策略,在一定的资源上,有效开发了计算的并行性和数据复用,可以处理任意规模的矩阵计算问题,具有低存储需求和高计算效率的优点。

附图说明

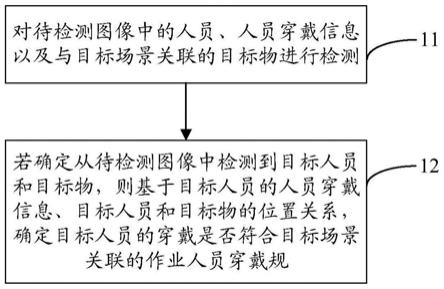

31.图1是本发明方法的流程示意图。

32.图2是本发明装置的拓扑结构原理示意图。

33.图3是本发明在具体应用实例中矩阵乘运算功能过程示意图。

34.图4是本发明在具体应用实例中矩阵加、矩阵减运算功能过程示意图。

35.图5是本发明在具体应用实例中矩阵-向量乘运算功能过程示意图。

36.图6是本发明在具体应用实例中矩阵-标量乘运算功能过程示意图。

具体实施方式

37.以下将结合说明书附图和具体实施例对本发明做进一步详细说明。

38.如图1所示,本发明的大规模多运算浮点矩阵计算加速实现方法,其步骤包括:

39.步骤s1:根据待处理矩阵的操作类型,接收外部输入信号,判断矩阵运算模式:当运算模式是矩阵加、矩阵减时,转入执行步骤s3,当运行模式是矩阵乘、矩阵-向量乘、矩阵-标量乘时,转入执行步骤s2;

40.步骤s2:初始化片上ram为零,转入执行步骤s4;

41.步骤s3:通过ram通道加载数据源c到片上ram中,转入执行步骤s4;

42.步骤s4:通过ram通道预加载部分数据流a,而后边计算边加载数据流a和数据流b;

43.步骤s5:计算完后,将计算结果传输到片外存储器;

44.在具体应用实例中,本发明可以最大限度的复用矩阵乘、矩阵加、矩阵减、矩阵-向量乘、矩阵-标量乘等运算的逻辑结构,并使用类似的数据源和数据流模式。

45.在具体应用实例中,所述数据源包括数据源a、数据源b、数据源c,其中,数据源a指矩阵a,数据源b指矩阵b、向量b或标量b,数据源c指片上存储的参与累加矩阵或向量。

46.在具体应用实例中,所述数据流与所述数据源相对应,包括数据流a、数据流b、数据流c。在本发明中,数据流a和数据流c相对固定,数据流b为矩阵、向量或者标量。

47.在具体应用实例中,本发明中的矩阵乘功能是指矩阵a和矩阵b的乘积,即实现cm×n=am×k×bk

×n cm×n,其中,数据流a、数据流b为输入数据流,数据流c在片上直接初始化为零。

48.在具体应用实例中,本发明中的矩阵加、矩阵减功能是指矩阵a和矩阵c的相加、相减,即实现cm×k=am×k×

ik×k±cm

×k,其中,数据流a、数据流c为输入数据流,数据流b为引入的单位矩阵i,其可直接在片上由一个计数器产生。

49.在具体应用实例中,本发明中的矩阵-向量乘功能是指矩阵a和向量b的乘积,即实现cm×1=am×k×bk

×1 cm×1,其中,数据流a、数据流b为输入数据流,数据流c在片上直接初始化为零。

50.在具体应用实例中,本发明中的矩阵-标量乘功能是指矩阵a和标量b的乘积,即实现cm×k=am×k×

b,其中,数据流a、数据流b为输入数据流,数据流c在片上直接初始化为零。

51.作为较佳的实施例,本发明结合分块矩阵思想,将大规模矩阵计算问题分解成小矩阵计算问题,具体步骤为:在步骤s1之前,根据待处理矩阵规模计算分块大小,而后逐一对子块进行操作;在步骤s5之后,继续进行下一个子矩阵块的计算,即重复步骤s2-s5,直至所有子块计算完成。

52.如图2所示,本发明进一步提供一种大规模多运算浮点矩阵计算加速装置,包含:

53.预处理模块,用于将矩阵、向量分块,并根据待处理矩阵的操作类型,接收外部输入信号,判断矩阵运算模式:当运算模式是矩阵加、矩阵减时,转入执行上述方法中的步骤s3,当运行模式是矩阵乘、矩阵-向量乘、矩阵-标量乘时,转入执行上述方法中的步骤s2;

54.数据传输控制模块,用于加载各数据源及返回数据计算结果;

55.矩阵计算加速单元模块为若干个完全相同的基本计算单元pe组成的线性阵列结构,用于实现矩阵各类运算操作。

56.在具体应用实例中,所述基本计算单元pe包括一个浮点计算部件,两个寄存器,一个fifo和一个简单双端口ram。

57.在具体应用实例中,所述浮点计算部件是符合ieee 754标准的ip核,集成了乘加操作或乘减操作,具体计算时根据外部操作模式信号。

58.如图3所示,本实施例记载了矩阵乘运算,具体功能是矩阵a和矩阵b的乘积,即实现cm×n=am×k×bk

×n cm×n,其中,数据流a、数据流b为输入数据流,数据流c的值在片上直接初始化为零。

59.本实施例进行矩阵乘分块后的形式为其中子矩阵a的大小为s

p

×

k,子矩阵b的大小为k

×

sq,子矩阵c的大小为s

p

×

sa,s

p

表示子矩阵a的行数,同时也表示线性阵列单元数目,sq表示子矩阵b的列数,同时也表示片上ram的深度,k表示子矩阵a的列数和子矩阵b的行数,同时也表示迭代次数。

60.具体计算过程为:初始化子矩阵c为零矩阵,预先加载子矩阵a的一列元素(s

p

个),随后按行依次流入子矩阵b的元素到线性阵列计算单元中,通过流水线的方式和重写机制完成c[cnt]=a

×

b c运算,中间结果保存在局部存储器中,经过k次迭代,将计算结果子矩阵c搬移到片外存储器,接着进行下一个子块的计算,如此反复。

[0061]

如图4所示,本实施例记载了矩阵加、矩阵减运算,具体功能是矩阵a和矩阵c的相加、相减,即实现cm×k=am×k×

ik×k±cm

×k,其中,数据流a、数据流c为输入数据流,数据流b为引入的单位矩阵i,其可直接在片上由一个计数器产生。

[0062]

本实施例进行矩阵加或矩阵减运算时,分块后的形式为本实施例进行矩阵加或矩阵减运算时,分块后的形式为其中子矩阵a的大小为s

p

×

k,子矩阵b的大小为k

×

k,子矩阵c的大小为s

p

×

k,s

p

表示子矩阵a的行数,同时也表示线性阵列单元数目,k表示子矩阵a的列数和子矩阵b的列数及行数,同时也表示迭代次数。

[0063]

具体计算过程为:预先加载子矩阵c所有元素和子矩阵a的一列元素(s

p

个),随后按行依次流入子矩阵b的元素到线性阵列计算单元中,通过流水线的方式和重写机制完成c[cnt]=a

×b±

c运算,中间结果保存在局部存储器中,经过k次迭代,将计算结果子矩阵c搬移到片外存储器,接着进行下一个子块的计算,如此反复。

[0064]

如图5所示,本实施例记载了矩阵-向量乘运算,具体功能是矩阵a和向量b的乘积,即实现cm×1=am×k×bk

×1 cm×1,其中,数据流a、数据流b为输入数据流,数据流c的值在片上直接初始化为零。

[0065]

本实施例进行矩阵-向量乘时,数据流b变成了向量,分块后的形式为其中子矩阵a的大小为s

p

×

k,子向量b的大小为k

×

1,子向量c的大小为s

p

×

1,s

p

表示子矩阵a的行数,同时也表示线性阵列单元数目,k表示子矩阵a的列数。

[0066]

具体计算过程为:初始化子向量块c为零向量,预先加载子矩阵a的一列元素(s

p

个),随后流入子向量b的元素到线性阵列计算单元中,通过流水线的方式和重写机制完成c

[cnt]=a

×

b c运算,中间结果保存在局部存储器中,经过k次迭代,将计算结果子向量块c搬移到片外存储器,接着进行下一个子块的计算,如此反复。

[0067]

如图6所示,本实施例记载了矩阵-标量乘功能是指矩阵a和标量b的乘积,即实现cm×k=am×k×

b,其中,数据流a、数据流b为输入数据流,数据流c在片上直接初始化为零。

[0068]

本实施例进行矩阵-标量乘时,数据流b变成了标量,分块后的形式为其中子矩阵a的大小为s

p

×

k,子矩阵c的大小为s

p

×

k,s

p

表示子矩阵a的行数,同时也表示线性阵列单元数目,k表示子矩阵a的列数。

[0069]

具体计算过程为:初始化子矩阵c为零矩阵,预先加载子矩阵a的一列元素(s

p

个),随后流入元素b到线性阵列计算单元中,完成单次c[cnt]=a

×

b c运算,将计算结果子矩阵c搬移到片外存储器,接着进行下一个子块的计算,如此反复。

[0070]

由上可知,本发明可完成多种模式矩阵运算,适用范围广、使用灵活,相比于传统的基于多个加速器的方法,本实施例中各个运算是基于统一的硬件结构,逻辑结构复用度高,具有资源消耗少和面积小的优势。

[0071]

以上仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。