1.本发明涉及在实现神经形态系统时能够控制电导率逐渐变化的存储器装置。更具体地,本发明涉及一种存储器装置,其中从存储器阵列中选择的一个或更多个存储器单元被识别为作为一个突触元件运行。

背景技术:

2.人工智能半导体产业可以说处于萌芽阶段。半导体设计和制造公司最近开始发布测试产品或早期版本的产品。这些测试产品或早期版本的产品都是基于cmos的第一代人工智能半导体产品,从材料的角度来看与现有的半导体产品没有什么不同。因此,期望在第二代人工智能半导体中引入和利用新材料。

3.对于具有类似于生物神经网络的集成度的第二代人工半导体,需要将具有生物突触的所有基本特征的人工突触实现为一个元件。生物系统的突触伴随着用于处理从神经元递送的信号的过程中的突触权重的改变,并且通过其表现出学习和存储功能。因此,人工突触元件旨在模拟生物突触以输出突触权重的变化作为电流(或电阻),从而表现出学习和存储功能。为此,开发一种其中发生可控和可区分的逐渐的电流(或电阻)变化的元件是非常重要的。在最理想的人工突触元件中,逐渐的电流(或电阻)变化可以与所施加的脉冲的数量精确地成比例地发生。

4.为了实现该目的,已经提出并制造了各种人工突触元件。在用于制造突触元件的半导体领域中已经研究的技术中,在电阻可以改变的诸如rram、pram或mram的存储器阵列中区分低电阻状态和高电阻状态,并且关于区分状态的信息存储在每个单元中。已经在实现数字开或关型的高电阻变化并且根据这种电阻变化读取存储器阵列中的单元的逻辑状态的方向上进行了研究。

5.然而,为了实现人工突触元件,不仅一个元件需要具有各种电阻状态,而且电阻状态也需要是可控的。使用上述rram或pram元件的这种元件的研究和开发正在进行中,但是开发的结果是不对称的并且缺乏再现性。另外,形成可区分电阻状态并同时进行控制是不够的。

技术实现要素:

6.技术问题

7.本发明的目的是提供一种存储器装置,该存储器装置能够以与用于实现神经形态系统的突触元件类似的方式引起用于信息处理的逐渐的电阻变化。

8.技术方案

9.为了实现上述目的,本发明的一个方面提供了一种存储器装置,该存储器装置包括:存储器阵列,其包括能够选择性地存储逻辑状态的多个存储器单元以及连接到所述多个存储器单元的多条位线和字线;控制器,其用于控制写入步骤和读取步骤;写入单元;以及读取单元,其中,在所述写入步骤中,所述控制器通过所述写入单元从所述多个存储器单

元中选择一个或更多个存储器单元,依次向所选的一个或更多个存储器单元施加写入电压以允许在其中写入逻辑状态,并且在所述读取步骤中,通过所述读取单元将读取电压施加到被选择为在其中写入所述逻辑状态的所述一个或更多个存储器单元,以便通过流经所述一个或更多个存储器单元的电流的总和来确定突触权重,使得允许将所选择的一个或更多个存储器单元识别为作为一个突触元件运行。

10.本发明的另一方面提供一种用于确定存储器装置中的突触权重的方法,所述存储器装置包括存储器阵列,该存储器阵列包括能够选择性地存储逻辑状态的多个存储器单元、连接到所述多个存储器单元的位线和字线,所述方法包括以下步骤:(a)从所述多个存储器单元中选择一个或更多个存储器单元,并在所选的一个或更多个存储器单元中依次施加写入电压以写入逻辑状态;(b)将读取电压施加到已被选择为在其中写入所述逻辑状态的所述一个或更多个存储器单元;以及(c)通过所施加的读取电压,通过流经已被选择为在其中写入逻辑状态的所述一个或更多个存储器单元的电流的总和来确定突触权重,其中,所选择的一个或更多个存储器单元被识别为作为一个突触元件运行。

11.本发明的另一方面提供一种神经形态系统,该神经形态系统包括:输入信号单元,其生成输入信号;突触部分,其包括接收所述输入信号单元的信号并根据设置的权重生成电流的多个突触单元和放大在所述突触单元中生成的电流的乘法器;以及输出信号单元,其通过接收从所述突触部分生成的电流来生成输出信号,其中,所述突触单元中的每一个包括彼此连接并且能够选择性地存储逻辑状态的多个存储器单元,在所述多个存储器单元中的每一个中设置放大因数,并且由所述乘法器通过所述放大因数对通过所述输入信号流经所述多个存储器单元的电流进行放大。

12.本发明的另一方面提供一种用于在神经形态系统中运行该神经形态系统的突触设备的方法,所述神经形态系统包括多个突触单元,所述突触单元包括彼此连接并位于具有交叉点结构的多个存储器阵列中的多个存储器单元,所述交叉点结构包括彼此交叉的输入电极线和输出电极线,所述多个存储器单元选择性地存储逻辑状态,所述方法包括以下步骤:(a)为所述多个存储器阵列中的每一个设置放大因数;(b)从为其设置所述放大因数的多个存储器阵列中的每一个中选择和组合一个或更多个存储器单元,并且设置包括所述多个存储器单元的多个突触单元;(c)将输入信号施加到所述多个突触单元;(d)通过针对每个存储器阵列施加的输入信号来测量流过所述突触单元的存储器单元的电流,并将所述电流相加;以及(e)根据所设置的存储器阵列的放大因数放大针对每个存储器阵列测量的电流,并且测量在各个存储器阵列中放大的电流的总和。

13.本发明的另一方面提供一种用于在神经形态系统中运行该神经形态系统的突触设备的方法,所述神经形态系统包括多个突触单元,所述突触单元包括彼此连接并位于具有交叉点结构的一个存储器阵列中的多个存储器单元,所述交叉点结构包括彼此交叉的输入电极线和输出电极线,所述多个存储器单元选择性地存储逻辑状态,所述方法包括以下步骤:(a)为所述存储器阵列的每条输出电极线设置放大因数;(b)选择和组合连接到为其设置所述放大因数的输出电极线的一个或更多个存储器单元,并且设置包括所述多个存储器单元的多个突触单元;(c)将输入信号施加到所述多个突触单元;(d)通过针对每条输出电极线施加的输入信号来测量流经所述突触单元的存储器单元的电流;以及(e)根据所设置的所述输出电极线的放大因数放大针对每条输出线测量的电流,并且测量在各个输出电

极线中放大的电流的总和。

14.有益效果

15.根据本发明,可以在存储器装置和存储器阵列中设置能够通过用于确定突触权重的方法通过高度线性比例控制逐渐的电阻变化的突触元件。

附图说明

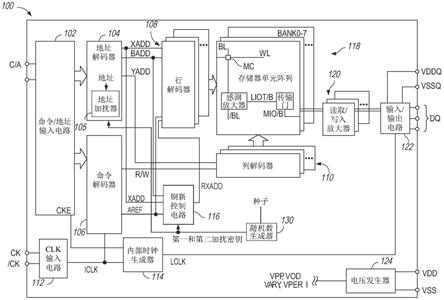

16.图1示出了根据本发明的存储器装置的配置图;

17.图2示出了在根据本发明的存储器装置中选择多个存储器单元的示例;

18.图3示出了在根据本发明的存储器装置中发生逐渐的电导率变化;

19.图4示出了应用于根据本发明的存储器装置的存储器单元的配置示例;

20.图5示出了在根据本发明的存储器装置中选择多个存储器单元的示例;

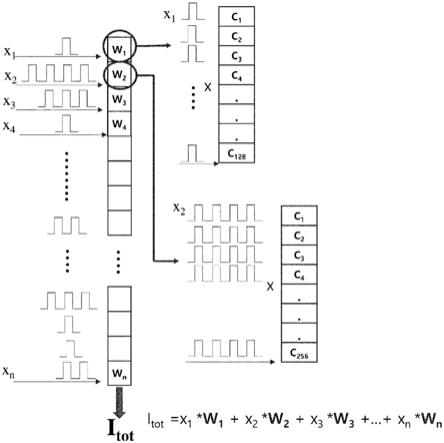

21.图6是示出根据本发明的用于确定突触权重的方法的图;

22.图7是示出其中包括具有切换功能的存储器单元的交叉点结构的存储器阵列中的典型读取方法的图;

23.图8是示出根据本发明的用于其中包括具有切换功能的存储器单元的交叉点结构的存储器阵列的读取方法的图;

24.图9是示出根据本发明的用于其中包括具有选择性存储器元件的存储器单元的交叉点结构的存储器阵列的写入和读取方法的图;

25.图10是示出通过矢量-矩阵乘法运算的推断方法的图;

26.图11是示出使用交叉点结构的存储器阵列的矢量-矩阵乘法操作的图;

27.图12是根据本发明的神经形态系统的配置图;

28.图13是示出根据本发明的神经形态系统的图;

29.图14是示出根据本发明的神经形态系统及其运行方法的图;

30.图15是示出根据本发明的神经形态系统及其运行方法的图;

31.图16是示出根据本发明的神经形态系统及其运行方法的图;

32.图17是示出根据本发明的神经形态系统及其运行方法的图;以及

33.图18是示出根据本发明的神经形态系统及其运行方法的图。

具体实施方式

34.在下文中,将结合附图描述本发明的实施方式的配置和操作。在以下描述中,将省略对公知功能或构造的详细描述,因为它们将以不必要的细节模糊本发明。另外,当元件被称为“包括”或“包含”组件时,其不排除另一组件,而是可以进一步包括另一组件,除非上下文清楚地另外指示。

35.根据本发明,提供了一种存储器装置,该存储器装置包括:存储器阵列,其包括多个存储器单元,每个存储器单元能够选择性地存储逻辑状态、连接到所述多个存储器单元的位线和字线;控制器,其用于控制写入步骤和读取步骤;写入单元;以及读取单元,其中,在所述写入步骤中,所述控制器通过所述写入单元从所述多个存储器单元中选择一个或更多个存储器单元,并且依次施加写入电压以写入逻辑状态。在读取步骤中,控制器将读取电压施加到由读取单元选择为在其中写入逻辑状态的一个或更多个存储器单元,并且通过流

经存储器单元的电流的总和来确定突触权重。因此,使所选择的一个或更多个存储器单元被识别为作为一个突触元件运行。

36.如图1所示,存储器阵列10可以具有交叉点结构,其中作为水平地址线的字线11和作为垂直地址线的位线12以网格结构布置,并且存储器单元13布置在字线11和位线12的交叉点处。然而,这是为了便于说明,并且本发明不限于此。

37.控制器20通过写入单元30从交叉点结构的存储器阵列10中选择多个存储器单元13的一部分,并且依次向所选择的存储器单元施加电压以编程逻辑状态。可以根据突触元件的权重来确定所选存储器单元的数目。例如,当存储器单元可以存储一个比特的逻辑状态并且需要128个突触权重时,选择128个存储器单元。当所选择的128个存储器单元被导通时,在读取步骤中使电流流动以读取128个突触权重。另外,在需要256个突触权重的情况下,在写入步骤中选择256个存储器单元并且将这些选择的存储器单元编程为导通状态。然后,在读取步骤中可以读取256个突触权重。

38.图2中示出了以这种方式选择的存储器单元的示例。图2的(a)示出了选择位于存储器阵列10中的3x2矩阵处的6个存储器单元以形成一个突触元件,图2的(b)示出了一个突触元件通过位于16x16矩阵中的256个存储器单元形成。

39.图2的(b)中的突触元件可通过256个单元(t1至t256)表示256个突触权重。由于为了在处理图像信息时实现输入图像信息的准确图像,优选存在256个突触权重,因此表示这样的突触权重是非常重要的。

40.另外,在基于计算机中的二进制系统的基础上,所选择的存储器单元的数目可以优选地为2n。因此,所选择的存储器单元的数目优选为1、2、4、8、16、32、64、128、256、1024或2048中的一个。当存储器单元的数目超过2048时,从阵列中选择的存储器单元的数目变得太多,并且其控制变得困难。因此,存储器单元的数目优选地可以是2048或更小。

41.在读取步骤中,通过施加到存储器阵列10的电压来测量流经存储器阵列10的电流的总和,并且可以通过该总和来确定存储器阵列10中的突触权重。电流的总和根据以这种方式选择以在其中写入逻辑状态的存储器单元的数目而不同,并且可以以各种方式确定突触权重。

42.图3中示出了这种电流(电导率)变化。在根据本发明的存储器装置中,电流的总和根据所选择的存储器单元的数目逐渐的改变,并且该改变与所选择的存储器单元的数目线性地成比例。由于当电导率上升和下降时也具有极好的对称性,因此存储器单元适合用作突触元件。

43.另外,本发明中能够存储逻辑状态的多个存储器单元可以是能够存储一个或更多个比特的逻辑状态的存储器装置。当逻辑状态不只是开(on)或关(off),而是具有几个阶段时,即使当存储器单元的数目较小时,也可以表示较大的突触权重。例如,当每个存储器单元仅表示开或关时,表示256个突触权重所需的所选存储器单元的数目是256。另一方面,当存储器单元由可变电阻元件形成并且可以表示四级电阻状态时,可以用64个存储器单元表示256个突触权重。

44.可以存储逻辑状态的多个存储器单元中的每一个可以包括非易失性存储器元件和选择器元件。非易失性存储器是必要的,以便在存储器单元中以低功率存储逻辑状态,并且每个存储器单元13需要包括选择器元件,以便在写入步骤中依次选择存储器单元并向其

写入逻辑状态,并且在读取步骤中测量流过经编程的存储器单元的电流的总和。

45.非易失性存储器元件可以是闪存、电阻式随机存取存储器(rram)、相变随机存取存储器(pram)或磁随机存取存储器(mram)中的任何一种。特别地,非易失性存储器元件可以是诸如rram、pram或mram的可变电阻元件。该可变电阻元件可以根据所施加的写入电压和/或电流脉冲来表示各种电阻状态,并通过该电阻状态来存储一个或更多个比特的逻辑状态。

46.此外,选择器元件可以是晶体管、二极管或双端开关元件中的任何一个。每个存储器单元可以通过包括在其中的选择器元件而被单独地选择,以通过写入步骤和读取步骤。

47.特别地,选择器元件可以是双端开关元件。应用双端开关元件作为用于选择存储器单元的选择器元件可以提高集成度并减少功耗。双端开关元件可以是双向(ovonic)阈值开关、过渡金属氧化物开关、混合离子电子导体(miec)开关、互补电阻开关或掺杂非晶硅中的任何一种。

48.另外,本发明中的多个存储器单元可以包括可以存储逻辑状态的选择性存储器元件。选择性存储器元件是指既具有非易失性存储器特性又具有选择器元件特性的元件。选择性存储器元件是指能够通过电阻变化来存储逻辑状态并且同时通过基于恒定电压(即,阈值电压)引起电阻变化而作为选择元件运行的元件。

49.例如,在由硫属化物材料制成的双向阈值开关的情况下,可以通过施加具有不同极性的写入电压来创建不同的电阻状态,并且使用双向阈值开关进行写入和读取是可能的。没有相变的硫属化物材料也可以是可变电阻元件,并且具有导致恒定电阻在阈值电压附近发生变化的独特开关特性。

50.以此方式,当使用包括硫属化物材料而没有相变的可变电阻元件时,如现有的双向阈值开关元件,可以通过开关特性选择一个或更多个存储器单元,并且可以通过可变电阻特性存储每个逻辑状态。

51.这样的元件可以表示为选择性存储器元件,并且在这种情况下,附加存储器元件或选择器元件不是必需的。因此,实现了高密度存储器装置,并且可以减少功耗。作为这种硫属化物材料,可以使用in-ge-as-se合金、te-se合金、as-se合金、ge-te合金、ge-se合金、as-se-te合金、ge-as-se合金、ge-as-sb合金、ge-sb-te合金、ge-sb-se合金、ge-as-te合金、si-ge-as-se合金、si-te-as-ge合金、in-sb-te合金、in-sb-se合金、in-ge-as合金、in-ge-te合金、in-te合金等。然而,除了上述材料之外,还可以采用这样的材料,通过该材料可以存储逻辑状态并且根据电阻变化启用开关功能。

52.图4中示出了如上所述的存储器单元13的示例。作为参考,可以以各种方式修改每个存储器单元的形状和配置。例如,可以省略选择器元件或存储器元件,或者可以省略电极。另选地,可以切换选择器元件和存储器元件的位置。

53.图4的(a)示出了包括存储器元件和选择器元件的存储器单元。作为对存储器单元的存取线之一的字线11垂直地穿过该平面,位线12平行地穿过该平面。存储器单元13设置在这些垂直交叉的字线11和位线12之间。电极1331和1332设置在与字线11和位线12连接的存储器元件1310和选择器元件1320之间。在电极1331和1332之间,包括存储器元件1310、选择器元件1320和用于在其之间连接的电极1333。存储器单元13的存储器元件1310可以是诸如闪存、rram、pram或mram的非易失性存储器中的任何一个,并且选择器元件1320可以是晶

体管、二极管或双端开关元件中的任何一个。例如,存储器元件1310可以是闪存、rram、pram或mram中的任何一个,并且选择器元件1320可以是晶体管。作为另一示例,存储器元件1310可以是rram、pram或mram中的任何一个,并且选择器元件1320可以是双端开关元件。这里,双端开关元件可以是双向阈值开关。

54.另外,存储器单元13可以包括选择性存储器元件。图4的(b)示出了存储器单元13包括选择性存储器元件1330以及电极1331和1332的示例。选择性存储器元件1330可具有没有相变的硫属化物材料,通过该硫属化物材料使得能够使用独特的开关特性来选择存储器单元,并且可使用根据写入条件出现的可变电阻特性来写入逻辑状态。该选择性存储器元件1330的示例可为包含硫族化物材料的双向阈值开关元件。虽然典型地与rram、pram等连接以用作选择器元件,但是双向阈值开关元件可以仅用于表现可变电阻特性和选择功能两者。硫属化物材料可以是包括in-ge-as-se的合金。

55.另外,根据本发明的写入单元30是包括dc计数器的存储器装置。控制器20通过包括dc计数器的写入单元30从存储器阵列10依次选择一个或更多个存储器单元,并且依次编程逻辑状态。可以存在一个或更多个dc计数器。

56.此外,根据本发明,读取单元40提供包括模数转换器adc的存储器装置。adc是用于将连续物理量转换为数字值的设备,并且通过使用adc,控制器20可以通过流经整个存储器阵列10的电流的流动来确定突触权重。

57.在写入步骤中已被选择为在其中编程有逻辑状态的一个或更多个存储器单元可以是这样的存储器装置,其中所有存储器单元连接到位线中的一条位线。当所选择的存储器单元连接到一条位线并且仅测量流经所连接的位线的电流时,可以测量流经整个存储器阵列的电流,这在装置配置方面是有效的。

58.另外,本发明可提供一种存储器装置,其中在写入步骤中已被选择为在其中对逻辑状态进行编程的一个或更多个单元与字线之一连接。类似地,可以仅测量流过所连接的字线的电流,这在装置配置方面是高效的。

59.图5示出了各种突触元件的配置示例。这些仅仅是为了便于说明,并且本发明不限于此。存储器单元阵列中包括的列线和行线的数目可以根据需要改变。

60.图5的(a)示出了这样的结构,其中被选择为具有写入其中的逻辑状态的存储器单元,即,形成一个突触元件的存储器单元a1至an都连接到一个相同的位线bla1。这样,当形成一个突触元件的存储器单元a1至an连接到一条位线时,在写入步骤中,控制器20通过多条字线wla1至wlan和一条位线bla1施加电压,以使逻辑状态依次存储在存储器单元a1至an中。写入单元30可以使得电压通过dc计数器被依次施加到存储器单元a1至an,使得逻辑状态被写入其中。这里,可以将一个或更多个dc计数器连接到存储器单元a1至an所连接的字线,并且控制选择性写入。

61.此后,在读取步骤中,控制器20使读取单元40通过流经存储器单元a1至an(即,突触元件)的电流的和来确定突触权重。读取单元40可包括adc以一次测量电流的总和,并且当所选择的单元全部连接到一条位线时,adc可连接到位线以辅助待测量的电流的总和。这种adc可以是感测放大器。

62.图5的(b)示出了这样的结构,其中被选择以具有写入其中的逻辑状态的存储器单元,即,形成一个突触元件的存储器单元b1至bm都连接到同一字线wlb1。这样,当形成一个

突触元件的存储器单元b1至bm连接到一条字线时,在写入步骤中,控制器20通过多条位线blb1至blbm和一条字线wlb1施加电压,以使逻辑状态依次存储在存储器单元b1至bm中。写入单元30可以使得电压通过dc计数器被依次施加到存储器单元b1至bm,使得逻辑状态被写入其中。这里,可以将一个或更多个dc计数器连接到存储器单元b1至bm所连接的位线,并且控制选择性写入。此后,在读取步骤中,控制器20使读取单元40通过流经存储器单元b1至bm(即,突触元件)的电流的和来确定突触权重。读取单元40可包括adc以一次测量电流的总和,并且当所选择的单元全部连接到一条字线时,adc可连接到字线以辅助待测量的电流的总和。这种adc可以是感测放大器。

63.图5的(c)示出了这样的结构,其中被选择以具有写入其中的逻辑状态的存储器单元,即,形成一个突触元件的存储器单元c1至cpk都连接到多条字线和多条位线。这样,对于形成一个突触元件的存储器单元c1至cpk,在写入步骤中,控制器20通过连接到存储器单元c1至cpk的多条字线wlc1至wlck和多条位线blc1至blcp依次施加电压,并且将逻辑状态存储在存储器单元c1至cpk中。写入单元30可以使电压通过dc计数器依次施加到存储器单元c1至cpk,并在其中写入逻辑状态。这里,可以将一个或更多个dc计数器连接到存储器单元c1至cpk所连接的位线和字线,并控制选择性写入。此后,在读取步骤中,控制器20使读取单元40测量流经存储器单元c1至cpk(即,突触元件)的电流之和,以确定突触权重。读取单元40可以包括adc以一次测量电流的总和,并且当所选择的单元连接到多条字线和位线时,adc还可以连接到字线和位线以辅助待测量的电流的总和。这种adc可以是感测放大器。

64.本发明提供一种用于在存储器装置中确定突触权重的方法,该存储器装置包括设置有可选择性地存储逻辑状态的多个存储器单元的存储器阵列、以及连接到所述多个存储器单元的位线和字线,所述方法包括以下步骤:(a)从所述多个存储器单元中选择一个或更多个存储器单元,并依次施加写入电压以在其中写入逻辑状态;(b)将读取电压施加到已被选择为在其中写入所述逻辑状态的所述一个或更多个存储器单元;以及(c)通过流经已被选择为具有写入其中的逻辑状态的一个或更多个存储器单元的电流的总和来确定突触权重,其中,所选择的一个或更多个存储器单元被识别为作为一个突触元件运行。

65.在交叉点结构的存储器阵列中,选择一个或更多个存储器单元,在其中写入逻辑状态,通过流经存储器单元的电流的总和来确定突触权重,所述存储器单元被选择为具有以这种方式写入其中的逻辑状态,因此,所选择的一个或更多个存储器单元可以被识别为作为一个突触元件运行。

66.可以根据突触元件的权重来确定所选存储器单元的数目。在神经形态系统中,来自前神经元的信号x1至xn被输入到突触,并且通过根据为每个突触设置的权重对输入信号进行加权来输出输出信号。为此,对相应的突触具有不同的权重是很重要的。当使用突触作为存储器元件时,需要对于各个存储器元件具有各种导电性,以便具有各种权重。为此,在本发明中,通过用多个存储器单元代替一个存储器单元来配置一个突触元件来示出各种导电性。

67.例如,当存储器单元可以存储一个比特逻辑状态并且需要128个突触权重时,选择128个单元并导通所选择的128个单元。然后,通过在读取步骤中使电流流过128个单元,可以读取128个突触权重。类似地,当需要256个突触权重时,在写入步骤中选择并导通256个单元。然后在读取步骤中,可以读取256个突触权重。

68.当在图6中更详细地描述这一点时,如果x1的输入信号被施加到突触w1并且在突触w1中设置128的权重,则针对w1的突触权重导通128个单元c1至c

128

。x1的输入信号被施加到128个单元,并测量从其输出的电流。

69.类似地,如果x2的输入信号被施加到突触w2并且在突触w2中设置256的权重,则针对w2的突触权重导通256个单元c1至c

256

,并且x1的输入信号被施加到256个单元并且测量从其输出的电流。

70.这样,就可以通过同时测量流经几个存储器单元的电流来设置各种突触权重。

71.同时,存储器单元可以是能够存储一个比特或多个逻辑状态的存储器装置。当逻辑状态不是简单地开或关而是具有多个阶段时,即使当存储器单元的所选数目较小时,也可以表示更大的突触权重。例如,当每个存储器单元仅表示开或关时,表示256个突触权重所需的所选存储器单元的数目是256。另一方面,当存储器单元由可变电阻元件形成并且可以表示四级电阻状态时,256个突触权重可以用64个存储器单元表示。

72.另外,在本发明中,能够选择性地存储逻辑状态的一个或更多个存储器单元在包括双端开关元件或选择性存储器元件的存储器装置中提供了用于确定突触权重的方法,其中,在上述步骤(b)中,读取电压处于这样的范围中,在该范围中,已经被选择为具有写入其中的逻辑状态的所有一个或更多个存储器单元未被导通,并且该范围大于施加到未从存储器阵列中选择的一个或更多个存储器单元的电压。

73.双端开关元件或选择性存储器元件具有当施加等于或大于特定电平的电压时发生较大电阻变化的开关功能。在该双端开关元件或选择性存储器元件中引起电阻变化的电压被表示为阈值电压,并且其中发生电阻变化的现象被表示为导通。

74.通过使用开关元件的特性仅使非常低的电流流过未在阈值电压或更低电压下选择的单元,并且通过向所选择的单元施加,来执行其中在如本发明的交叉点结构的存储器阵列中使用开关功能的典型读取过程,可允许区分所述单元的逻辑状态的电压。

75.将通过图7描述用于读取包括双端开关元件或选择性存储器元件的交叉点结构的存储器阵列中的所选单元的电流的典型方法。在图7中,当将v

inh

施加到未被选择的单元时,在该区域中,没有将具有高电阻的单元与具有低电阻的单元区分开,并且电流的流动非常小。同时,将v

read1

应用于所选单元,并且使得v

read1

满足v

th_a

《v

read1

《v

th_b

,其中,v

th_a

是具有低电阻的单元的阈值电压,v

th_b

是具有高电阻的单元的阈值电压,并且允许通过流过所选择的单元的电流来区分逻辑状态。在图7中,根据v

read1

,电流i

target,off

流过具有高电阻的单元,而电流i

target,on

流过具有低电阻的单元。该方法可允许仅从存储器阵列中选择一个单元并且仅允许读取数字型中的开或关状态。这是因为,当将读取电压施加到处于导通状态的一个单元时,流过该单元的电流如此大,使得不可能对其他单元进行电流测量。

76.将参照图8描述用于读取所选存储器单元的电流的另一方法。当向未被选择的单元施加v

inh

时,在该区域中,根据单元的电阻状态的电流流动没有彼此区分,并且电流非常小。同时,与上述用于向所选单元施加读取电压v

read1

(v

th_a

《v

read1

《v

th_b

)的方法不同,该读取电压v

read1

(v

th_a

《v

read1

《v

th_b

)在具有低电阻的单元的阈值电压v

th_a

和具有高电阻的单元的阈值电压v

th_b

之间,如具有

‘vread2’的图8中所示,读取电压在其中所有所选择的一个或更多个单元未被导通的子阈值区域的电压范围内,并且在大于施加到未被选择的一个或更多个单元的电压的范围内。换句话说,在图8中,读取电压v

read2

大于v

inh

,并且在小于所选择的单

元中处于最低电阻状态的单元的阈值电压v

th1

的范围内。以此方式,当在子阈值区域中执行读取时,对于多个单元的同时读取也变得可能。这是因为,与典型的方法不同,即使当读取电压被施加到处于导通状态的单元时,流过该单元的电流也不大,因此可以通过同时将读取电压施加到多个单元来容易地测量流过多个单元的电流的总和。

77.在本发明中,双端开关元件可以是双向阈值开关元件、过渡金属氧化物开关元件、混合离子-电子导体开关元件、互补电阻开关元件和掺杂非晶硅中的任何一种。除了上述材料之外,还可采用其中启用开关功能的材料,该开关功能基于阈值电压引起电阻变化。

78.另选地,选择性存储器元件是指既具有非易失性存储器特性又具有选择器元件特性的元件。换句话说,其意味着能够通过电阻变化来存储逻辑状态,并且还通过基于恒定电压(即,阈值电压)引起电阻变化来作为选择器元件运行。这样的元件可以表示为选择性存储器元件,并且在这种情况下,附加存储器元件或选择器元件不是必需的。因此,实现了高密度存储器装置,并且可以减少功耗。这种选择性存储器元件的示例可以是包括硫属化物材料的双向阈值开关元件。这是因为虽然硫属化物阈值开关元件通常与用作选择器元件的rram、pram等连接,但是可以仅用于显示可变电阻特性和选择功能两者。作为硫属化物材料,可以使用in-ge-as-se合金、te-se合金、as-se合金、ge-te合金、ge-se合金、as-se-te合金、ge-as-se合金、ge-as-sb合金、ge-sb-te合金、ge-sb-se合金、ge-as-te合金、si-ge-as-se合金、si-te-as-ge合金、in-sb-te合金、in-sb-se合金、in-ge-as合金、in-ge-te合金、in-te合金等。然而,除了上述材料之外,还可采用可通过电阻变化存储逻辑状态和启用开关功能的材料。

79.另外,能够选择性地存储逻辑状态的多个存储器单元在包括双端开关元件或选择性存储器元件的存储器装置中提供了用于确定突触权重的方法,其中,在上述步骤(a)中,写入电压使从多个存储器单元中选择的一个或更多个存储器单元导通,并且具有用于写入第一逻辑状态的第一极性和用于写入第二逻辑状态的第二极性,所述第一极性和所述第二极性彼此相反,并且在上述步骤(b)中,读取电压具有与写入电压的第一极性相同的极性,其中,使得所选择的一个或更多个所选择的存储器单元被识别为作为一个突触元件运行。

80.当将等于或高于阈值电压的第一极性的电压施加到包括双端开关元件或选择性存储器元件的存储器单元,然后将第一极性的电压施加到存储器单元时,存储器单元在第一极性的方向上具有低阈值电压,以示出低电阻状态。最初,即使在具有第一极性的高阈值电压并且处于高电阻状态的情况下,当施加等于或大于阈值电压的第一极性的电压时,存储器单元也变为低电阻状态。另外,当具有与第一极性相反的第二极性的等于或大于阈值电压的电压被施加到存储器单元,然后施加第一极性的电压时,存储器单元在第一极性的方向上具有高阈值电压,并且示出高电阻状态。即使在具有第一极性并且在施加第二极性的电压之前处于低电阻状态的情况下,当施加第二极性的阈值电压或更高电压时,存储器单元也变得在第一极性方向上具有高阈值电压。

81.这在图9中示出。在图9的(a)中的电压-电流曲线图中,当沿着线101施加第一极性( )的第一正向导通电压v

t

并且然后施加相同第一极性( )的读取电压时,存储器单元具有沿着线102的低阈值电压v

t,lrs

(换句话说,低电阻状态)。然而,当沿着具有第一极性( )的相反极性的线103施加具有第二极性(-)的等于或大于阈值电压的电压并且然后施加第一极性( )的读取电压时,存储器单元沿着线104显示高阈值电压v

t,hrs

以具有高电阻状态。这样,

当在写入步骤中写入电压的极性不同时,电阻状态变得不同,并且电阻差异可以通过图9的(a)和图9(b)中的存储器窗口106示出。此后,在读取步骤中,如上所述,可通过在范围105内施加读取电压来测量流经所选存储器单元的电流,以确定突触权重,在该范围105内存储器单元未导通并且该范围105大于施加到未从存储器阵列选择的一个或更多个单元的电压。

82.在本发明中,可以提供一种用于确定突触权重的方法,其中被选择为在其中写入逻辑状态的一个或更多个存储器单元是全部连接到位线中的一条位线的存储器单元。另外,在本发明中,可以提供一种用于确定突触权重的方法,其中被选择以具有写入其中的逻辑状态的一个或更多个存储器单元是全部连接到字线中的一条字线的存储器单元。以这种方式选择的存储器单元连接到一条字线或一条位线,这在装置配置方面是有效的。

83.此外,本发明提供了一种用于确定突触权重的方法,其中在(a)步骤中选择具有写入其中的逻辑状态的一个或更多个存储器单元的数目是1、2、4、8、16、32、64、128、256、1024和2048中的任何一个,其中所选择的一个或更多个存储器单元被识别为作为一个突触元件运行。这是因为在基于计算机中的二进制系统的基础上,所选单元的数目优选为2n。因此,所选单元的数目优选为1、2、4、8、16、32、64、128、256、1024和2048中的任何一个。在超过2048的情况下,从阵列中选择的单元的数量太多,因此控制变得困难。因此,所选单元的数目优选为2048个或更小。

84.在本发明中,将描述一种新的神经形态系统及其运行方法。

85.在深度学习算法中,向量矩阵乘法(vmm)操作是训练和推理的关键计算操作。

86.当参照图10描述用于识别图像的vmm方法时,将图像划分为n

×

n个区域,对n

×

n个区域分别设置权重,并将亮度和暗度等信息作为各种输入信号输入。当用神经形态系统表达时,输入信号xi是来自前神经元的信号,输出电流i

tot

是到后神经元的输出信号,并且wi是通过突触乘以输入信号的权重。以此方式,通过将i

tot

与参考值进行比较并找到具有最接近权重的突触来识别图像,i

tot

是由输入信号和权重的乘积之和得到的电流。

87.然而,在现有计算系统中实现这样的操作时存在许多问题,诸如功耗问题和装置尺寸问题。

88.为了解决这个问题,最近的研究正积极地尝试通过使用使用诸如电阻随机存取存储器(rram)、相变随机存取存储器(pram)和磁随机存取存储器(mram)的新存储器的交叉点结构来解决这个问题。

89.交叉点结构的存储器阵列具有输入电极线和输出电极线彼此交叉的结构,并且输入电极线和输出电极线在输入电极线和输出电极线彼此交叉的交叉点处通过存储器单元连接。

90.图11中已经描述了使用交叉点结构的存储器阵列的vmm。在图11中,当在保持列金属线121处于接地状态的同时向行金属线122施加可以表示为向量xi的输入信号时,流过交叉点(i,j)位置处的每个存储器的电流变为xiw

ij

。由于流经这些列线121的电流变为流经位于同一列线121中的存储器的电流的总和,因此ij=x1*w

1j

x2*w

2j

x3*w

3j

... xn*w

nj

(图11中j为1至m)。

91.以此方式,通过将通过列线121输出的m个电流中的每一个与参考值进行比较来执行推断处理。

92.这里,输入信号xi可以是具有恒定宽度和不同高度的脉冲、具有恒定高度和不同

宽度的脉冲、或者具有恒定宽度和高度以及不同次数的脉冲。作为权重的w

ij

可以用交叉点结构的存储器阵列的每个点处的存储器的电导率来表示。

93.顺便说一下,这里,权重w

ij

对应于存储器的电导率。为了提高推断的准确性,需要在存储器中逐步存储各种值,即各种电导率。随着多样性的增加,推断的精度也增加,因此,为此目的,积极地开发了能够在各个阶段存储电导率的新存储器,但是尚未获得令人满意的结果。

94.为了改善该结果,本发明可以提供一种新的神经形态系统及其使用该系统的方法,该神经形态系统能够使用多个存储器单元而不是一个存储器单元来表现出各种电导率w

ij

。即,权重不是通过用一个存储器单元配置突触来表示的,而是可以通过用多个存储器单元配置突触来自由地设置各种权重。

95.通过本发明提供的新型神经形态系统和使用该系统的方法,使用多个单元而不是一个存储器单元来表示作为对应于单个输入值的权重的w

ij

,并且可以通过根据多个单元中的每个单元中的位数来设置放大因数来表达各种电导率。放大因数可以跟随二进制数系统中的位数。

96.这在图12中简化并表示。图12的(a)示出了包括输入信号单元200、突触部分300和输出信号单元400的神经形态系统,突触部分300包括多个突触单元310和乘法器320,所述乘法器320能够放大流过这些突触单元的电流,并且向突触部分300施加从输入信号单元200生成的输入信号,输出信号单元400测量流过突触部分300的电流。

97.在这种神经形态系统中,位于突触部分300中的每个突触单元310包括多个存储器单元311,并且在这些存储器单元311中的每个存储器单元中设置放大因数,并且通过乘法器320用放大因数放大流过这些存储器单元的电流,从而这些放大电流的和最终可以变成流过突触单元310的电流。由于在一个突触单元310中包括对其设置了放大因数的多个存储器单元,因此可以表达各种权重。

98.在这种情况下,根据多个存储器单元的位置和用于放大电流的乘法器的连接,可以出现各种形状。

99.首先,包括在一个突触单元中的多个存储器单元可以定位在不同的存储器阵列中。在这种情况下,在每个存储器阵列中设置放大因数,使得位于同一存储器阵列中的所有存储器单元具有相同的放大因数。一个乘法器连接到一个存储器阵列。通过这种连接,包括在一个突触单元中的存储器单元分散地定位在几个存储器阵列中,并且权重由流过存储器单元的电流的总和确定。

100.这将参照图13更详细地描述。如在交叉点结构的一般神经形态系统中那样,输入信号xi通过具有权重的突触单元w

11

至w

n1

以输出输出信号。这里,突触单元传统上配置有一个存储器单元,而在本发明中,突触单元配置有多个存储器单元,并且多个存储器单元再次设置在多个存储器阵列中。尽管在图13中示出了k个存储器阵列,存储器阵列的数目可以根据需要而不同地采用,例如2、4、16、32、64等。

101.对于多个存储器阵列分别设置放大因数m.f(1)至m.f(k),并且放大因数可以是2n(n包括0和正整数)以表示二进制数系统中的位数。例如,在图12中,存储器阵列的数目是8。因此,m.f(1)是27,m.f(2)是26,m.f(3)是25,并且最后的m.f(8)可以是20。

102.在图13中,突触单元w

11

配置有k个存储器单元a1c

11

、a2c

11

、a3c

11

、

...

、a

kc11

。当输入信

号x1被输入到k个存储器单元中的每一个时,在k个存储器单元中分别产生电流x1*a1c

11

、x1*a2c

11

、x1*a3c

11

、

...

、x1*a

kc11

。

103.所产生的电流分别由乘法器mp(1)至mp(k)放大,乘法器mp(1)至mp(k)分别连接到存储器阵列,其中放大因数m.f(1)至m.f(k)分别根据存储器单元分别所处的存储器阵列设置,并且最终示出以下输出信号。

104.x1w

11

=x1*(a1c

11

*m.f(1) a2c

11

*m.f(2) ... a

kc11

*m.f(k))

105.最后,通过对n个突触单元的输出信号求和,可以如下获得可用于推断的输出信号i1,如图14所示。

106.i1=x1*w

11

x2*w

21

x3*w

31

... xn*w

n1

107.=x1*(a1c

11

*m.f(1) a2c

11

*m.f(2) ... a

kc11

*m.f(k)) x2*(a1c

21

*m.f(1) a2c

21

*m.f(2) ... a

kc21

*m.f(k)) ... xn*(a1c

n1

*m.f(1) a2c

n1

*m.f(2) ... a

kcn1

*m.f(k))

108.因此,有必要根据放大因数放大流过每个突触单元的每个存储器单元的电流,并将这些电流相加。结果,得到的值变得等于通过乘法器mp(k)用在存储器阵列中设置的放大因数m.f(k)将值x1*a

kc11

x2*a

kc21

... xn*a

kcn1

放大并相加所获得的值,该值是每个存储器阵列中流过相同输出电极线的电流之和。因此,其可以再次表示如下。

109.i1=(x1*a1c

11

x2*a1c

21

... xn*a1c

n1

)*m.f(1) (x1*a2c

11

x2*a2c

21

... xn*a2c

n1

)*m.f(2) ... (x1*a

kc11

x2*a

kc21

... xn*a

kcn1

)*m.f(k)

110.当更详细地描述使用包括多个存储器阵列的这种神经形态系统的运行方法时,运行方法可以包括:(a)为所述多个存储器阵列中的每一个设置放大因数;(b)从为其设置所述放大因数的多个存储器阵列中的每一个中选择和组合一个或更多个存储器单元,并且设置包括所述多个存储器单元的多个突触单元;(c)将输入信号施加到所述多个突触单元;(d)通过针对每个存储器阵列施加的输入信号来测量流过所述突触单元的存储器单元的电流;以及(e)根据所设置的存储器阵列的放大因数放大针对每个存储器阵列测量的电流,并且测量在各个存储器阵列中放大的电流的总和。

111.分别为存储器阵列设置放大因数m.f(1)至m.f(k),并且从存储器阵列中选择存储器单元并将其组合以设置多个突触单元。在图14中,突触单元w

11

变为a1c

11

、a2c

11

、a3c

11

、...、a

kc11

的组合,w

21

变为a1c

21

、a2c

21

、a3c

31

、...、a

kc21

的组合,最后的w

n1

变为a1c

n1

、a2c

n1

、a3c

n1

、...、a

kcn1

的组合。

112.当输入信号x1至xn被施加到以这种方式设置的突触单元时,电流在包括在这些突触单元中的每一个中的存储器单元中流动。例如,x1*a1c

11

、x1*a2c

11

、x1*a3c

11

、...、x1*a

kc11

的电流分别流过包括在突触单元w

11

中的存储器单元a1c

11

、a2c

11

、a3c

11

、..、a

kc11

。

113.通过这种方式,为每个存储器阵列测量并添加流过突触单元的单个存储器单元的电流。也就是说,在图14中,流经存储器阵列a1的电流之和为x1*a1c

11

x2*a1c

21

... xn*a1c

n1

。当测量和相加的电流之和乘以为每个存储器阵列设置的放大因数((x1*a1c

11

x2*a1c

21

... xn*a1c

n1

)*m.f(1))时,测量每个存储器阵列a1至ak中的放大电流之和,导出i1,i1是推断所必需的电流值。

114.另一方面,当存储器单元包括双端开关元件或选择性存储器件并且测量流过一个存储器阵列的电流的总和时,当一个存储器单元由于处于低电阻状态而导通时,大电流在导通的存储器单元中流动,因此,出现大的电压降,使得不可能读取其他存储器单元中的电

流变化。因此,当输入信号处于存储器单元可以改变到低电阻状态的电压范围内时(参照图7),需要以这样的方式进行,即对于一个存储器阵列中的存储器单元逐个依次测量输入信号的输入和根据输入信号的输出信号的输入,然后获得它们的和。为此,存储器阵列还可以包括能够存储针对每个输出线流动的电流的电容器。

115.另一方面,即使当存储器单元包括双端开关元件或选择性存储器元件并且测量流过一个存储器阵列的电流的和时,输入信号的电压可以被设置在由双端开关元件或选择性存储器元件的特性形成的处于高电阻状态的存储器单元和处于低电阻状态的存储器单元都不导通的范围内(参见图8)。据此,由于不存在导通的存储器单元,所以可以降低整体功耗,并且由于电压降不显著发生,所以可以同时测量流过一个存储器阵列的电流。

116.为了获得不同的电流值ij,针对每个存储器阵列的每个输出线重复上述方法,如图15所示。通过将如此导出的电流值i1至im与参考值进行比较通过常数函数来确定最接近的电流值。

117.另外,在本发明中,多个存储器单元可以位于一个存储器阵列中。此外,在这种情况下,其可以是神经形态系统,其中存储器阵列具有包括彼此交叉的输入电极线和输出电极线的交叉点结构,乘法器连接到每个输出电极线,突触单元的多个存储器单元位于多条输出电极线中,为每条输出电极线设置放大因数,并且对位于相同输出电极线中的所有存储器单元设置相同的放大因数,并且根据放大因数通过乘法器放大在突触单元的每个存储器单元中由输入信号流动的电流。

118.如上所述,n个输入信号x1至xi通过具有权重的n个突触单元w

11

至w

n1

以输出输出信号,如在交叉点结构的一般神经形态系统中那样。这里,在本发明中,突触单元配置有多个存储器单元,并且可以在一个存储器阵列中为每条输出线设置多个存储器单元。

119.这在图16和图17中示出,突触单元w

11

包括多个存储器单元l1c

11

、l2c

11

、...l

kc11

。放大因数m.f(1)至m.f(k)分别被设置到其上各设置有多个存储器单元的输出电极线,并且因此乘法器m.p(1)至m.p(k)分别连接到输出电极线。这里再次,放大因数可以是2n(n是包括0的正整数),以表示二进制系统中的位数。例如,在图16和图17中,具有不同放大因数的输出电极线的数目k为8。因此,m.f(1)是27,m.f(2)是26,m.f(3)是25,并且最后的m.f(8)可以是20。

120.图16示出了具有相同放大因数的输出电极线聚集在一起的情况,图17示出了其中针对每个输出电极线设置乘法器的情况,因为放大因数对于每个相邻的输出电极线是不同的。

121.在图16中,突触单元w

11

配置有k个存储器单元l1c

11

、l2c

11

、l3c

11

、

...

、l

kc11

,并且当输入信号x1被输入到k个存储器单元中的每一个时,相应地,在k个存储器单元中分别产生电流x1*l1c

11

、x1*l2c

11

、x1*l3c

11

、

...

、x1*l

kc11

。

122.再次,x2*l1c

21

、x2*l2c

21

、x2*l3c

21

、

...

、x2*l

kc21

的电流分别在作为突触单元的w

21

的存储器单元中产生。

123.该产生的电流通过根据存储器单元分别所处的输出电极线设置的放大因数来放大,并且最终,突触单元w

11

的输出信号如下所示。

124.x1w

11

=x1*(l1c

11

*m.f(1) l2c

11

*m.f(2) ... l

kc11

*m.f(k))

125.最后,通过对各个突触单元的输出信号求和,可以如下获得可用于推断的输出信

号i1,如图16所示。

126.i1=x1*w

11

x2*w

21

x3*w

31

... xn*w

n1

127.=x1*(l1c

11

*m.f(1) l2c

11

*m.f(2) ... l

kc11

*m.f(k)) x2*(l1c

21

*m.f(1) l2c

21

*m.f(2) ... l

kc21

*m.f(k)) ... xn*(l1c

n1

*m.f(1) l2c

n1

*m.f(2) ... l

kcn1

*m.f(k))

128.因此,有必要根据放大因数放大流过每个突触单元的每个存储器单元的电流,并将这些电流相加。结果,得到的值变得等于通过在存储器阵列中设置的放大因数m.f(k)将值x1*a

kc11

x2*a

kc21

... xn*a

kcn1

放大并相加所获得的值,该值是每个存储器阵列中流过相同输出电极线的电流之和。

129.i1=(x1*a1c

11

x2*a1c

21

... xn*a1c

n1

)*m.f(1) (x1*a2c

11

x2*a2c

21

... xn*a2c

n1

)*m.f(2) ... (x1*a

kc11

x2*a

kc21

... xn*a

kcn1

)*m.f(k)

130.如图16所示,与图17所示的输出电极线彼此相邻的情况不同,在一个存储器阵列中具有相同放大因数的输出电极线可以对于每个相邻电极线具有不同的放大因数。

131.当描述使用神经形态系统的运行方法时,在该神经形态系统中一个突触单元包括多个存储器单元,并且所述多个存储器单元位于一个存储器中,更详细地,所述运行方法可以是运行用于神经形态系统的突触设备的方法,所述方法包括:(a)为所述存储器阵列的每个输出电极线设置放大因数;(b)选择和组合连接到为其设置所述放大因数的输出电极线的一个或更多个存储器单元,并且设置包括所述多个存储器单元的多个突触单元;(c)将输入信号施加到所述多个突触单元;(d)通过针对每个输出电极线施加的输入信号来测量流过所述突触单元的存储器单元的电流;以及(e)根据所设置的所述输出电极线的放大因数放大针对每个输出线测量的电流,并且测量在各个输出电极线中放大的电流的总和。

132.分别为输出电极线设置放大因数m.f(1)至m.f(k)。这里,通过选择和组合存储器单元来设置多个突触单元。在图16中,突触单元w

11

是l1c

11

、l2c

11

、l3c

11

、...、l

kc11

的组合。

133.当输入信号x1至xn被施加到以这种方式设置的突触单元时,电流在包括在这些突触单元中的每一个中的存储器单元中流动。例如,x1*l1c

11

、x1*l2c

11

、x1*l3c

11

、...、x1*l

kc11

的电流分别流过包括在突触单元w

11

中的存储器单元l1c

11

、l2c

11

、l3c

11

、...、l

kc11

。

134.以这种方式,针对每个输出电极线,测量并相加流过突触单元的各个存储器单元的电流。也就是说,在图16中,流过存储器输出电极线l

1-1

的电流之和是x1*l1c

11

x2*l1c

21

... xn*l1c

n1

。当测量和相加的电流之和乘以为每条输出电极线((x1*l1c

11

x2*l1c

21

... xn*l1c

n1

)*m.f(1))设置的放大因数时,测量每条输出电极线l

1-1

至l

k-1

中的放大电流之和,导出作为推断所需的电流值的i1。

135.另一方面,当存储器单元包括双端开关元件或选择性存储器件并且测量流过一条输出电极线的电流的总和时,当一个存储器单元由于处于低电阻状态而导通时,大电流在导通的存储器单元中流动,因此,出现大的电压降,使得不可能读取同一输出电极线上的其他存储器单元中的电流变化。因此,当输入信号处于存储器单元可以改变到低电阻状态的电压范围内时(参照图7),需要以这样的方式进行,即对于一条输出电极线中的存储器单元逐个依次测量输入信号的输入和根据输入信号的输出信号的输入,然后获得它们的和。为此,存储器阵列还可以包括能够存储针对每个输出线流动的电流的电容器。

136.另一方面,即使当存储器单元包括双端开关元件或选择性存储器元件并且测量流过一条输出电极线的电流的和时,输入信号的电压可以被设置在由双端开关元件或选择性

存储器元件的特性形成的处于高电阻状态的存储器单元和处于低电阻状态的存储器单元都不导通的范围内(参见图8)。据此,由于不存在导通的存储器单元,因此能够降低整体功耗,并且由于电压降不显著发生,因此能够一次测量流过一条输出电极线上的存储器单元的电流的总和。

137.另外,为了获得不同的电流值ij,针对每个存储器阵列的每个输出线重复上述方法,如图17所示。通过将如此导出的电流值i1至im与参考值进行比较通过常数函数来确定最接近的电流值。

138.另外,在本发明中,能够存储逻辑状态的多个存储器单元可以是能够存储一个或更多比特的逻辑状态的存储器装置。当逻辑状态不只是开或关,而是具有几个阶段时,即使当存储器单元的数目较小时,也可以表示较大的突触权重。

139.可以存储逻辑状态的多个存储器单元中的每一个可以包括非易失性存储器元件和选择器元件。需要使用非易失性存储器以便在存储器单元中以低功率存储逻辑状态,并且每个存储器单元需要包括选择器元件,以便依次选择存储器单元并在写入步骤中向其写入逻辑状态,并且在读取步骤中测量流过经编程存储器单元的电流的总和。

140.非易失性存储器元件可以是闪存、电阻式随机存取存储器(rram)、相变随机存取存储器(pram)或磁随机存取存储器(mram)中的任何一种。特别地,非易失性存储器元件可以是诸如rram、pram或mram的可变电阻元件。该可变电阻元件可以根据所施加的输入信号来表示各种电阻状态,并且通过该电阻状态来存储一个或更多个比特的逻辑状态。

141.此外,选择器元件可以是存储器装置,其是晶体管、二极管或双端开关元件中的任何一个。每个存储器单元可以通过包括在其中的选择器元件被单独地选择并且经受写入步骤和读取步骤。

142.特别地,选择器元件可以是双端开关元件。应用双端开关元件作为用于选择存储器单元的选择器元件可以提高集成度并减少功耗。双端开关元件可以是任何元件,例如,双向阈值开关、过渡金属氧化物开关、混合离子电子导体(miec)开关、互补电阻开关、掺杂非晶硅等。

143.另外,在本发明中,能够存储逻辑状态的多个存储器单元中的每一个可以包括选择性存储器元件。选择性存储器元件是指既具有非易失性存储器特性又具有选择器元件特性的元件。选择性存储器元件是指能够通过电阻的变化来存储逻辑状态,并且同时通过基于恒定电压(即阈值电压)引起电阻的变化来作为选择器元件运行的元件。

144.例如,在由硫属化物材料制成的双向阈值开关的情况下,可以通过施加具有不同极性的写入电压来产生不同的电阻状态。没有相变的硫属化物材料也可以是可变电阻元件,并且具有导致在阈值电压附近发生恒定电阻变化的独特开关特性。

145.以此方式,当使用包括硫属化物材料而没有相变的可变电阻元件时,如现有的双向阈值开关元件,可以通过开关特性选择一个或更多个存储器单元,并且每个逻辑状态可以通过可变电阻特性存储在其中。

146.这样的元件可以表示为选择性存储器元件,并且在这种情况下,附加存储器元件或选择器元件不是必需的。因此,实现了高密度存储器装置,并且可以减少功耗。作为这种硫属化物材料,可以使用in-ge-as-se合金、te-se合金、as-se合金、ge-te合金、ge-se合金、as-se-te合金、ge-as-se合金、ge-as-sb合金、ge-sb-te合金、ge-sb-se合金、ge-as-te合

金、si-ge-as-se合金、si-te-as-ge合金、in-sb-te合金、in-sb-se合金、in-ge-as合金、in-ge-te合金、in-te合金等。然而,除了上述材料之外,能够存储逻辑状态并且能够通过电阻变化执行开关功能的任何材料都不受特别限制。

147.另外,在本发明中,输出信号单元可以包括模数转换器,并且从输出信号单元接收的电流的和是模拟信号,该模拟信号可以通过模数转换器数字化并输出。该模数转换器可以是感测放大器。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。