1.本公开涉及信息处理装置、信息处理系统和信息处理方法。

背景技术:

2.近年来,神经网络作为模拟脑神经系统机制的数学模型受到关注。此外,已经提出了用于减少神经网络中运算的处理负荷的各种方法。例如,非专利文献1描述了通过将加权系数二值化来减少处理负荷的方法。此外,非专利文献2描述了通过将输入信号转换为对数域来将乘法转换为加法的方法。

3.引文列表

4.非专利文献

5.非专利文献1:matthieu courbariaux和另外两个人,

″

binaryconnect:training deep neural networks with binary weights during propagations”,[online],2015年11月2日,arxiv,[2017年3月22日搜索],互联网《url:https://arxiv.org/pdf/1511.00363.pdf》

[0006]

非专利文献2:daisuke miyashita和另外两个人,“convolutional neural networks using logarithmic data representation”,[online],2016年3月3日,arxiv,[2017年3月22日搜索],互联网《url:https://arxiv.org/pdf/1603.01025.pdf》

技术实现要素:

[0007]

技术问题

[0008]

然而,在非专利文献1中描述的方法中,由于执行使用 1或-1的二值化,因此假设量化粒度随着加权系数的维数的增加而变得粗糙。此外,尽管非专利文献2中描述的方法在避免乘法方面具有预定的效果,但假定有更大的减少处理负荷的空间。

[0009]

因此,本公开提出了能够进一步减少与内积运算相关的处理负荷并保证加权系数的量化粒度的新的和改进的信息处理装置、信息处理系统和信息处理方法。

[0010]

问题的解决方案

[0011]

为解决上述问题,根据本公开的一个方面的信息处理装置包括:积和运算电路,被配置为基于由幂表达式量化的多个输入值和与各个输入值相对应的由幂表达式量化的多个加权系数来执行积和运算,其中,每个输入值的指数由分母中具有预定除数的分数表示,每个加权系数的指数由分母中具有除数的分数表示,积和运算电路使用基于余数的多个加法乘数执行积和运算,余数是进行以通过将与每个输入值的指数相关的分子和与每个加权系数的指数相关的分子相加而获得的值为被除数的除法时的余数,并且每个加法乘数都是指数部分的基数为2的浮点数。

附图说明

[0012]

[图1]是用于说明根据本公开的相关技术的神经网络中的基本运算的概要的概念

图。

[0013]

[图2]是用于说明根据本公开的相关技术的输入向量和权重向量的内积运算的示意图。

[0014]

[图3]是用于说明根据本公开的相关技术的在二维空间中二进制量化的权重向量的图。

[0015]

[图4]是用于说明根据本公开的相关技术的在二维空间中四进制量化的权重向量的图。

[0016]

[图5]是用于说明根据本公开的相关技术的三维空间中的权重向量的粒度变化的图。

[0017]

[图6]是用于说明根据本公开的相关技术的n维空间中的权重向量的粒度变化的图。

[0018]

[图7]是根据基础技术的信息处理装置的功能框图的示例。

[0019]

[图8]是根据基础技术的信息处理装置中包括的积和运算电路的电路框图的示例。

[0020]

[图9]是根据基础技术的与在地址表中保存的地址信息相关的偏移标记的示例。

[0021]

[图10]是示出根据基础技术的信息处理方法的处理图像的图。

[0022]

[图11]是用于说明根据基础技术的量化粒度δθ的图。

[0023]

[图12]是示出根据基础技术的根据α的量化粒度δθ的最大值的曲线图。

[0024]

[图13]是用于说明根据基础技术的最大幂的图。

[0025]

[图14]是示出根据基础技术的关于输入数量n的乘法次数的示例的图。

[0026]

[图15]是示出根据基础技术的关于输入数量n的乘法次数的示例的图。

[0027]

[图16]是在根据基础技术的开发示例的权重向量被量化的情况下的积和运算电路的示例。

[0028]

[图17]是在根据基础技术的开发示例的权重向量和输入向量两者都被量化的情况下的积和运算电路的示例。

[0029]

[图18]是在根据基础技术的开发示例的权重向量和输入向量两者都被量化的情况下的积和运算电路的示例。

[0030]

[图19]是示出根据基础技术的开发示例的在比较实验中使用的resnet的网络结构的图。

[0031]

[图20]是示出根据基础技术的开发示例的不包括最大池化层的resnet网络配置的图。

[0032]

[图21]是示出根据基础技术的开发示例的包括最大池化层的resnet网络配置的图。

[0033]

[图22]是示出根据基础技术的开发示例的图像识别率的比较结果的图。

[0034]

[图23]是在根据基础技术的开发示例的权重向量和输入向量两者都被量化的情况下的积和运算电路的示例。

[0035]

[图24]是示出根据第一实施例的索引和表值之间的关系的图。

[0036]

[图25]是示出根据第一实施例的索引和表值之间的另一关系的图。

[0037]

[图26]是将根据第一实施例的以2的幂表示的表值和以线性表示的表值绘制在同

一曲线图上的图。

[0038]

[图27]是示出根据第一实施例的第一具体示例的积和运算电路的示意性配置示例的电路图。

[0039]

[图28]是示出根据第一实施例的第二具体示例的积和运算电路的示意性配置示例的电路图。

[0040]

[图29]是示出根据第二实施例的量化器的舍入的示例的图。

[0041]

[图30]是示出作为比较示例的神经网络电路的示意性配置示例的框图。

[0042]

[图31]是示出作为另一比较示例的神经网络电路的示意性配置示例的框图。

[0043]

[图32]是示出作为又一比较示例的神经网络电路的示意性配置示例的框图。

[0044]

[图33]是示出根据第二实施例的神经网络电路的示意性配置示例的框图。

[0045]

[图34]是示出根据第三实施例的积和运算电路的示意性配置示例的电路图。

[0046]

[图35]是示出根据第三实施例的量化电路的示意性配置示例的电路图。

[0047]

[图36]是用于说明一般dnn和cnn的致动的示意图。

[0048]

[图37]是示出输入到图36中的第一层的卷积层的系数w1的图。

[0049]

[图38]是示出输入到图36中的第二层的卷积层的系数w2的图。

[0050]

[图39]是示出输入到图36中的第一层的卷积层的系数w3的图。

[0051]

[图40]是示出图36中的卷积神经网络的输入(变量)x0的图。

[0052]

[图41]是示出来自图36中的第一层的输出(变量)x1的图。

[0053]

[图42]是示出来自图36中的第二层的输出(变量)x2的图。

[0054]

[图43]是示出来自图36中的第三层的输出(变量)x3的图。

[0055]

[图44]是示出根据第四实施例的2的幂的数值表的示例的图。

[0056]

[图45]是示出根据第四实施例的s.e.m格式、s.b.q格式、数字格式信息(数字格式信息)和容器(数值数据容器)之间的关系的图。

[0057]

[图46]是示出根据第四实施例的基本结构(基本结构)的分组的结构示例的图。

[0058]

[图47]是示出根据第四实施例的连续结构(连续结构)的分组的结构示例的图。

[0059]

[图48]是示出根据第四实施例的扩展结构(扩展结构)的分组的结构示例的图。

[0060]

[图49]是示出根据第四实施例的仅作为有效载荷排列的分组的结构示例的图。

[0061]

[图50]是示出根据第四实施例的自定义扩展结构(自定义结构)的报头的示例的图。

[0062]

[图51]是示出根据第四实施例的自定义扩展结构(自定义结构)的有效载荷的示例的图。

[0063]

[图52]是示出根据第四实施例的基本结构(基本结构)的分组的实施示例的图。

[0064]

[图53]是示出根据第四实施例的连续结构(连续结构)的分组的实施示例的图。

[0065]

[图54]是示出根据第四实施例的扩展结构(扩展结构)的分组的实施示例的图。

[0066]

[图55]是示出根据第四实施例的仅连续有效载荷区域(有效载荷)的分组的实施示例的图。

[0067]

[图56]是示出根据第四实施例的自定义结构(自定义结构)的分组的实施示例的图。

[0068]

[图57]是示出根据第四实施例的仅连续有效载荷区域(有效载荷)的分组的实施

示例的图。

[0069]

[图58]是示出根据第四实施例的处理字节流的系统的示意性配置示例的框图。

[0070]

[图59]是示出当根据本公开的量化方法应用于带通滤波器时关于频率特征(增益特征)的仿真结果的图。

[0071]

[图60]是示出当根据本公开的量化方法应用于带通滤波器时关于相位特征的仿真结果的图。

[0072]

[图61]是根据本公开的用于ber评估的框图。

[0073]

[图62]是示出当根据本公开的bpsk用于调制方法时的ber评估结果的图。

[0074]

[图63]是图62中的snr7至9db的数据的放大图。

[0075]

[图64]是示出当根据本公开的qpsk用于调制方法时的ber评估结果的图。

[0076]

[图65]是图64中的snr10至12db的数据的放大图。

[0077]

[图66]是示出当根据本公开的16qam用于调制方法时的ber评估结果的图。

[0078]

[图67]是图66中的snr16至18db的数据的放大图。

[0079]

[图68]是示出根据本公开的实施例的硬件配置示例的图。

具体实施方式

[0080]

下面将基于附图详细描述本公开的实施例。注意,在以下描述的每个实施例中,相同的部分用相同的附图标记指定,并且将省略重复的描述。

[0081]

此外,本公开将根据以下描述的项目顺序描述。

[0082]

1.基础技术

[0083]

1.1背景

[0084]

1.2信息处理装置10的功能配置示例

[0085]

1.3权重向量的量化

[0086]

1.4积和运算电路的配置示例

[0087]

1.5学习期间的量化

[0088]

1.6基础技术的效果

[0089]

2.基础技术的开发示例

[0090]

2.1概要

[0091]

2.2权重向量的量化

[0092]

2.3权重向量和输入向量两者的量化

[0093]

2.4开发示例的效果

[0094]

3.结论

[0095]

4.第一实施例

[0096]

4.1基础技术的问题

[0097]

4.2值表的示例

[0098]

4.3积和运算电路的具体示例

[0099]

4.3.1第一具体示例

[0100]

4.3.2第二具体示例

[0101]

4.4运算和效果

[0102]

5.第二实施例

[0103]

5.1基础技术的问题

[0104]

5.2量化电路的具体示例

[0105]

5.3运算和效果

[0106]

6.第三实施例

[0107]

6.1基础技术的问题

[0108]

6.2积和运算电路的具体示例

[0109]

6.3量化方法的开发

[0110]

6.4量化电路的具体示例

[0111]

6.5运算和效果

[0112]

6.6变型示例

[0113]

6.6.1第一变型示例

[0114]

6.6.2第二变型示例

[0115]

6.6.3第三变型示例

[0116]

6.6.4第四变型示例

[0117]

6.6.5第五变型示例

[0118]

6.6.6第六变型示例

[0119]

7.第四实施例

[0120]

7.1基础技术的问题

[0121]

7.2数字格式信息的具体示例

[0122]

7.2.1 s.e.m格式

[0123]

7.2.2 s.b.q格式

[0124]

7.3实际数据的管理方法:容器与数字格式信息的关系

[0125]

7.4字节流

[0126]

7.4.1按基本结构(基本结构)和连续结构(连续结构)分组的字节流

[0127]

7.4.2按扩展结构(扩展结构)分组的字节流

[0128]

7.4.3按自定义扩展结构(自定义结构)的分组报头的有效载荷可变长度流

[0129]

7.5字节流的实施示例

[0130]

7.5.1基本结构(基本结构)和连续结构(连续结构)的字节流实施示例

[0131]

7.5.2扩展结构(扩展结构)的字节流实施示例

[0132]

7.5.3自定义结构(自定义结构)的字节流实施示例

[0133]

7.6字节流处理系统的配置示例

[0134]

7.7运算和效果

[0135]

8.通信技术应用示例

[0136]

9.硬件配置示例

[0137]

1.基础技术

[0138]

首先,将参考附图详细描述作为本公开的基础的技术(以下,称为基础技术)。

[0139]

1.1背景

[0140]

近年来,广泛研究了使用神经网络的学习方法,例如深度学习。虽然使用神经网络

的学习方法具有高精度,但与运算相关的处理负荷大。因此,需要有效降低处理负荷的运算方法。

[0141]

为此,近年来,例如,还提出了一种用于减少运算量和信息量的运算方法,例如二进制权重网络和xnor网络。

[0142]

这里,将描述一般神经网络中的基本运算的概要。图1是用于说明神经网络中的基本运算的概要的概念图。图1示出了构成神经网络的两层,以及属于这两层的单元c11至c1n和单元c21。

[0143]

此时,基于输入向量和与属于较低层的单元c11至c1n相关的加权系数(以下,也称为权重向量),确定输入到单元c21的输入信号(以下,也称为输入向量)。更具体地,输入到单元c21的输入向量是通过对与单元c11至c1n相关的输入向量和权重向量的内积运算结果加上偏置b,并通过激活函数h进一步处理该结果而获得的值。

[0144]

即,当与单元c11至c1n相关的输入向量和权重向量分别为x=(x1,x2,x3,...xn)和w=(w1,w2,w3,...wn)时,输入到单元c21的输入向量z由下面描述的公式(1)定义。

[0145]

z=h(∑xiwi b)

ꢀꢀꢀ

(1)

[0146]

此时,如图2所示,假设以权重向量w为法线的超平面h,可以用将输入向量x相对于超平面h投影到权重向量w而获得的投影距离d乘以||w||所获得的值来表示以n维表示的输入向量x和权重向量w的内积。这里,上面描述的||w||是向量w的范数。图2是用于说明输入向量x和权重向量w的内积运算的示意图。

[0147]

这里,在输入向量x和权重向量w是二维的情况下,当权重向量w被量化为如非专利文献1中 1或-1的二进制值时,权重向量w可以如图3表示。图3是用于说明在二维空间中二进制量化的权重向量w的图。此时,权重向量w的粒度可以用平面内的旋转角θ表示,粒度为90度,如图3所示。

[0148]

接下来,将考虑权重向量w被量化为四个值{0,1/4,1/2,1}的情况。图4是用于说明在二维空间中四进制量化的权重向量w的图。在这种情况下,权重向量w的粒度,即旋转角θ约为15度,与二进制量化的情况相比,可以保证更细的粒度。

[0149]

另一方面,假设权重向量w的粒度随着维数的增加而变化更大。图5是用于说明三维空间中的权重向量w的粒度变化的图。例如,如图5所示,在考虑由(1,1,0)和(0,0,1)定义的平面中的权重向量w的量化的情况下,(1,1,0)方向边的长度是(0,0,1)方向边的长度的√2倍,由此可以看出,量化时粒度的变化增大。

[0150]

此外,如上面所描述的粒度的变化,即,非均匀性随着维度数的增加而变得更加显著。图6是用于说明n维空间中的权重向量w的粒度变化的图。图6示出了n维空间中由(1,1,...,1,0)和(0,0,...,0,1)定义的平面。此时,(1,1,...,1,0)方向边的长度可以用√(n-1)乘以(0,0,...,0,1)方向边的长度来表示。例如,当n=100时,(1,1,...,1,0)方向边的长度是(0,0,...,0,1)方向边的√99倍(≈10倍)。

[0151]

由于如上所述的与权重向量w相关的粒度的不均匀性会导致神经网络性能的降低,因此期望更精确的量化方法。根据本公开的技术思想是围绕以上几点构思的,并且使得能够在保持n维空间中的权重向量的高近似精度的同时有效地减少处理负荷。为此目的,根据本公开的基础技术的信息处理装置和信息处理方法的特征在于,使用基于n维超球面中的向量方向上的粒度量化的权重向量来执行内积运算。根据本公开的基础技术的信息处理

装置和信息处理方法可以通过以不太细和不太粗的粒度量化权重向量来实现高近似精度和处理负荷的减少。更具体地,根据本公开的基础技术的信息处理装置和信息处理方法可以使用由幂表示的权重向量来执行内积运算。以下,将详细描述根据本公开的基础技术的信息处理装置和信息处理方法的上述特征。

[0152]

1.2信息处理装置10的功能配置示例

[0153]

接下来,将描述实现根据基础技术的信息处理方法的信息处理装置10的功能配置示例。图7是根据基础技术的信息处理装置10的功能框图的示例。参考图7,根据基础技术的信息处理装置10包括输入单元110、运算单元120、存储单元130和输出单元140。以下,将侧重于配置的功能来描述上述配置。

[0154]

(输入单元110)

[0155]

输入单元110具有检测操作人员的各种输入操作的功能。为此目的,输入单元110可以包括用于检测操作人员的输入操作的各种装置。输入单元110可以通过例如各种按钮、键盘、触摸面板、鼠标、开关等来实现。

[0156]

(运算单元120)

[0157]

运算单元120具有通过基于多个输入值和分别对应于输入值的多个加权系数执行内积运算来计算输出值的功能。具体地,运算单元120执行与神经网络的前向传播相关的内积运算。此时,运算单元120的特征之一是基于在n维超球面上基于向量方向上的粒度量化的加权系数来计算输出值。更具体地,运算单元120可以基于由幂表示的加权系数来计算输出值。内积运算的特征将单独详细描述。

[0158]

(存储单元130)

[0159]

存储单元130具有存储在信息处理装置10中包括的每个配置中使用的程序、数据等的功能。例如,存储单元130存储用于神经网络的各种参数。

[0160]

(输出单元140)

[0161]

输出单元140具有向操作人员输出各种类型的信息的功能。为此目的,输出单元140可以被配置为包括输出视觉信息的显示装置。这里,例如,上述显示装置可以通过阴极射线管(crt)显示装置、液晶显示(lcd)装置、有机发光二极管(oled)装置等来实现。

[0162]

上面已经描述了根据基本技术的信息处理装置10的功能配置示例。注意,上面描述的功能配置示例仅仅是示例,并且功能配置示例不限于这样的示例。信息处理装置10可以进一步包括除图1中所示的配置之外的配置。例如,信息处理装置10可进一步包括与另一信息处理终端执行信息通信的通信单元。即,可以灵活地重新设计根据基础技术的信息处理装置10的功能配置。

[0163]

1.3权重向量的量化

[0164]

接下来,将详细描述根据基础技术权重向量的量化。如上所述,根据基础技术的信息处理装置10通过使用由幂表示的权重向量w执行量化,可以保持粒度的高均匀性。此时,运算单元120的特征之一是以值的升序重新排列多个权重向量分量wi,并以具有最大值的加权系数wi对多个权重向量分量wi进行归一化。这里,假设重新排列和归一化的权重向量是wj,权重向量wj由下面描述的公式(2)至(4)表示。

[0165]

[0166]

wn=1

ꢀꢀꢀ

(3)

[0167]

wj≤w

j 1

ꢀꢀꢀ

(4)

[0168]

然而,此时,上述公式(2)中的α可能是0<α<1,sj可能是sj∈{-1,1},nj可能是nj∈{0,1,2,...}。即,运算单元120以nj为整数执行量化。此时,由运算单元120执行的内积运算由下面描述的公式(5)表示。注意,下面描述的公式(5)中的k表示归一化常数。此外,即使适当地修改下面描述的公式(5)时,如果在内积运算中最终确定上述α的值在上述范围内就足够了。本公开中指示的公式仅仅是示例,并且可以灵活地修改。

[0169][0170]

因此,预计运算单元120的内积运算可以通过n次加法运算和-1/2log(n-1)/logα数量级的乘法次数来处理。

[0171]

如上所述,根据基础技术的信息处理方法的特征之一是权重向量w用α的幂的表达式近似,并且权重向量w按值的升序重新排列。此时,在根据基础技术的信息处理方法中,通过根据n对α的指数进行t值转换来执行权重向量w的量化。

[0172]

例如,在n=100的情况下,在根据基础技术的信息处理方法中可以采用t=4(2bit)、8(3bit)、16(4bit)等。通过如上所述设置t,上述公式(5)中n

1-n2、n

2-n3、n

3-n4...中的许多被量化为相同的值为0,因此可以大大减少乘法次数。在更具体的示例中,在相对于n=100的t=4的情况下,n

j-1-nj只能取四次除0以外的值。因此,在本示例的情况下,与内积运算相关的乘法次数为四次,其余的全部为加法,从而可以有效地减少处理负荷。

[0173]

1.4积和运算电路的配置示例

[0174]

接下来,将描述实现根据基础技术的运算方法的积和运算电路。如上所述,在权重向量w通过幂表达式量化并执行重排的情况下,还需要重排对应于权重向量w的输入向量x。

[0175]

因此,信息处理装置10可以包括积和运算电路,该积和运算电路具有表,该表保存与按值的升序重新排列的多个权重向量w相对应的输入向量x的地址信息。

[0176]

图8是根据基础技术的信息处理装置10中包括的积和运算电路200的电路框图的示例。如图8所示,根据基础技术的积和运算电路包括:存储电路,其保存表wt,该表wt保存与权重向量w相对应的输入向量x的地址信息;ram 210、加法电路220、累加器230、执行与α相关的乘法的第一乘法电路240、以及执行与归一化常数相关的乘法的第二乘法电路250。

[0177]

(地址表wt)

[0178]

根据基础技术的地址表wt保存与按值的升序重新排列的多个权重向量w相对应的输入向量x的地址信息、符号信息和乘法指令信息。注意,如图8所示,上述地址信息可以包括空指针。在这种情况下,0被加到累加器230,并且累加器230的值可以简单地乘以α。此外,上述符号信息是表示与上述公式(5)中的sj相对应的值的信息。

[0179]

此外,上述乘法指令信息是指示第一乘法电路240的处理内容的信息。例如,根据基础技术的乘法指令信息可以包括指定乘法必要性的信息。图8示出了当乘法指令信息为0时第一乘法电路240不执行乘法,并且当乘法指令信息为1时第一乘法电路240执行乘以α的情况的示例。

[0180]

注意,根据基础技术的乘法指令信息不限于上述示例,并且可以包括指定各种处理内容的信息。例如,根据基础技术的乘法指令信息可以包括乘法次数、指定移位运算的信

息等。

[0181]

(ram210)

[0182]

ram210基于从地址表wt输入的地址信息,将与权重向量分量wj对应的输入向量分量xj输出到加法电路220。

[0183]

(加法电路220)

[0184]

加法电路220基于从ram210输入的输入向量分量xj和从第一乘法电路240输出的值执行加法。此时,加法电路220基于在地址表wt中保存的符号信息执行上述加法。

[0185]

(累加器230)

[0186]

累加器230累加从加法电路220输出的运算结果。累加器230将累加值输出到第一乘法电路240和第二乘法电路250。此外,将用于将累加值复位为0的复位信号被适当地输入到累加器230。

[0187]

(第一乘法电路240)

[0188]

第一乘法电路240将累加器230累加的值乘以α。此时,如上所述,第一乘法电路240基于在地址表wt中保存的乘法指令信息执行上述乘法。第一乘法电路240将运算结果输出到加法电路220。

[0189]

(第二乘法电路250)

[0190]

第二乘法电路250将从累加器230输出的值乘以归一化常数k。

[0191]

上面已经描述了根据基本技术的积和运算电路200的配置示例。利用根据基础技术的积和运算电路200,可以有效地减少内积运算中的乘法次数,并且可以减少处理负荷。

[0192]

另一方面,由于通过保存输入向量x的地址信息,地址表wt的容量增加,因此还假定功耗增加。因此,如图9所示,地址表wt可以包括指示地址之间的相对位置的偏移量。图9是根据基础技术的与在地址表wt中保存的地址信息相关的偏移标记的示例。

[0193]

如图9所示,地址表wt可以按照地址顺序对上述公式(5)中nj-1-nj的值连续为0的部分中的地址进行排序,即,不执行乘法的部分,并保存地址之间的偏移量作为地址信息。利用上述根据基础技术描述的地址表wt,可以大幅减少与地址信息相关的信息量,并有效地降低功耗。

[0194]

注意,地址表wt可以采取除图8和图9所示的形式之外的各种形式。例如,在地址表wt中,符号信息和乘法指令信息可以不清楚地分离和保存,或者可以采用除上述以外的地址压缩方法。可以根据神经网络的配置、信息处理装置10的性能等灵活地修改地址表wt。

[0195]

1.5学习期间的量化

[0196]

接下来,将描述根据基础技术在学习时的权重向量w的量化。在根据基础技术的信息处理方法中,可以通过下面描述的公式(6)计算在学习时的权重向量分量wi的更新。

[0197]

ni=int(log|wi/w

max

|/logα)

ꢀꢀꢀ

(6)

[0198]

这里,上述公式(6)中的w

max

表示wi的最大值。此外,对于整数转换int,可以选择向上舍入或向下舍入,以更接近的方式进行。在根据基础技术的信息处理方法中,通过在最终学习时重新排列ni,可以生成上述地址表wt。

[0199]

注意,在α接近于1的情况下,也可以采用使用基于使用普通浮点运算的深度神经网络(dnn)的学习算法执行运算并在学习完成后量化wi的方法。即,在与权重向量w相关的量化粒度小的情况下,在不修改网络结构的情况下,期望识别精度不劣化的效果。

[0200]

1.6基础技术的效果

[0201]

接下来,将详细描述根据基础技术权重向量的量化所施加的效果如上所述,在根据基础技术的信息处理方法中,通过以值的升序执行重排和归一化,将由幂表达式量化的wi定义为wj。此时,当重新排列的基向量为qj时,权重向量w由下面描述的公式(7)表示。

[0202][0203]

即,如图10所示,根据基础技术的信息处理方法具有如下意义:在由投影在由q1、q2、...q

j-1

和qj所跨越的空间中的权重向量形成的平面中重复创建向量的处理并将向量乘以α

nj-nj 1

。图10是示出根据基础技术的信息处理方法的处理图像的图。

[0204]

因此,在根据基础技术的信息处理方法中,权重向量的量化粒度δθ可以在逆时针旋转方向和顺时针旋转方向上分别用公式(8)和(9)表示,如图11所示,在通过将权重向量投影到q1、q2、...q

j-1

空间和qj所获得的轴所跨越的平面上。然而,此时,公式(8)和(9)中的l由公式(10)定义。图11是用于说明根据基础技术的量化粒度δθ的图。注意,在图11中,示出了投影到第一象限的权重向量。

[0205][0206][0207][0208]

此外,当量化粒度δθ1和δθ2被1微分并设置为0时,相应的最大值由下面描述的公式(11)定义。

[0209][0210]

图12是示出根据基础技术的根据α的量化粒度δθ的最大值的曲线图。如上所述,通过根据基础技术的信息处理方法,保证了在n维空间中的所有正交旋转方向上的量化粒度。

[0211]

注意,在中间停止幂运算的情况下,如图13所示,留下量化粒度δθ。

[0212]

图13是用于说明根据基础技术的最大幂的图。注意,在图13中,示出了投影到第一象限的权重向量。此时,如果通过将下面描述的公式(13)添加到满足下面描述的公式(12)的最小m中,获得用于保证量化粒度δθ的最大幂就足够了。因此,由信息处理装置10执行的乘法次数可以通过下面描述的公式(14)获得。

[0213][0214]

[0215][0216]

例如,在α=3/4的情况下,关于输入数量n的乘法次数如图14所示的曲线图中所确定。此外,在α=7/8的情况下,关于输入数量n的乘法次数如图15所示的曲线图中所确定。即,在运算单元120的内积运算中,可以说,基于权重向量的基的值来确定乘法次数。图14和图15是示出根据基础技术的关于输入数量n的乘法次数的示例的图。

[0217]

如上所述,利用实现基础技术中的信息处理方法的信息处理装置,在与神经网络的前向传播相关的内积运算中,乘法次数可以大大减少,并且积和运算电路200的功耗可以有效地减少。此外,利用实现基础技术中的信息处理方法的信息处理装置,可以提高权重向量的量化的精度,并且与使用相同位数的传统量化方法相比,期望通过神经网络提高识别精度和近似精度的效果。

[0218]

2.基础技术的开发示例

[0219]

2.1概要

[0220]

接下来,将描述基础技术的开发示例。在上述基础技术中,已经描述了通过用αn表示权重向量分量wj,实现对数阶内积运算的高近似精度和减少乘法次数的方法。

[0221]

然而,尽管在基础技术中例示的方法在内积空间的维数相对较大的情况下是有效的,但也假定对于维数相对较少的内积运算,例如卷积神经网络(cnn),减少处理负荷的效果不够。

[0222]

因此,在基础技术的开发示例(以下,简称为开发示例)中,提出了即使在内积空间的维数相对较小时,也能够有效地降低内积运算的处理负荷的运算电路。

[0223]

具体地,权重向量分量wi和输入向量分量xi可以表示为α-n/p

。此时,在α=2的情况下,α-n/p

的可能值可以表示为下面描述的表1。

[0224]

表1

[0225] p=1p=2p=3p=4p=5n=10.50.7071070.7937010.8408960.870551n=20.250.50.6299610.7071070.757858n=30.1250.3535530.50.5946040.659754n=40.06250.250.396850.50.574349n=50.031250.1767770.314980.4204480.5n=60.0156250.1250.250.3535530.435275n=70.0078130.0883880.1984250.2973020.378929n=80.0039060.06250.157490.250.329877n=90.0019530.0441940.1250.2102240.287175

[0226]

上面描述的表1说明了p的值越大,量化的粒度可以越小。因此,在开发示例中,通过对权重向量分量wi和输入向量分量xi量化为α-n/p

,与基础技术相比,可以减小量化误差。此外,通过开发示例的运算方法,只需通过移位运算和加法就可以执行与基础技术中描述的内积运算等效的处理,可以有效地降低内积运算中的处理负荷。

[0227]

2.2权重向量的量化

[0228]

首先,将描述在仅权重向量w被α-n/p

量化的情况下的方法。这里,使用自然数通过下面描述的公式(15)执行内积运算的情况:α=2和p∈{1,2,3,...}。注意,p对应于本公开中的除数。此外,下面描述的公式(15)中的wi由下面描述的公式(16)表示。此外,下面描述的公式(16)中的si和ni分别为si∈{-1,1}和ni∈{0,1,2,...}。

[0229][0230][0231]

此时,当对w进行归一化以满足所有wi的|wi|≤1,并且随后根据需要将y乘以归一化乘数时,上面描述的公式(15)可以表示为下面描述的公式(17)。此外,这里,yr由下面描述的公式(18)定义。

[0232][0233][0234]

这里,当r∈{0,1,...,p-1}时,如果i=j,则δ

i,j

=1,否则为0,yr可以用正规定点符号表示,其中负数用补数2表示。此外,

[0235][0236]

在上面描述的公式(18)中,可以通过在其中负数由补数2表示的定点符号中移位xi来计算,

[0237][0238]

即,通过整数值int(ni/p),向右作为有符号二进制。即,与输入向量x和权重向量w相关的内积运算可以由下面描述的公式(19)表示。

[0239][0240]

此时,例如,可以通过图16所示的积和运算电路300来实现上述公式(19)中所示的内积运算。图16是在根据开发示例的权重向量被量化的情况下的积和运算电路的示例。

[0241]

参考图16,积和运算电路300包括移位运算器310、余数运算器320、选择器330和340、累加器组350、加法器-减法器360、乘法器组370和加法器380。

[0242]

(移位运算器310)

[0243]

移位运算器310基于输入的输入向量分量xi和ni执行移位运算。具体地,移位运算

器310将输入向量分量xi向右位移位int(ni/p)值。

[0244]

(余数运算器320)

[0245]

余数运算器320基于输入ni执行n

i mod p的运算,并将余数的值输入到选择器330和340。

[0246]

(选择器330和340)

[0247]

选择器330和340基于余数运算器320的运算结果,在累加器组350中包括的多个累加器中选择电路连接到的累加器。此时,选择器330和340启动,使得累加器和对应于余数的值的电路被连接。例如,当余数为0时,选择器330和340启动以使电路与累加器y0耦合,并且当余数为1时,选择器330和340启动以使电路与累加器y1耦合。

[0248]

(累加器组350)

[0249]

累加器组350包括多个累加器,每个累加器对应于n

i mod p的余数的值。也就是说,累加器组350对余数的每个值保存yr。

[0250]

(加法器-减法器360)

[0251]

加法器-减法器360基于输入si、移位运算结果和yr的值执行加法和减法。此时,如上所述,由基于n

i mod p的余数的值选择的累加器保存的yr值被输入到加法器-减法器360。此外,基于加法器-减法器360的运算结果,更新上述选择的累加器的yr。

[0252]

(乘法器组370)

[0253]

乘法器组370将通过上述处理针对每个余数更新的yr乘以根据余数的加法乘数。为此目的,乘法器组370包括对应于n

i mod p的每个余数的多个乘法器。例如,乘法器组370将从累加器组350输入的y0乘以1,并将y1乘以2-1/p

。

[0254]

(加法器380)

[0255]

加法器380将乘法器组370为每个余数计算出的yr值相加,并输出最终运算结果y。

[0256]

上面已经描述了积和运算电路300。如上所述,利用积和运算电路300,在与n

i mod p的每个余数相对应的累加器中累加yr,并且在最后一起执行乘法,从而可以最小化乘法次数。注意,在图16所示的示例中,尽管对i执行顺序计算以更新yr,但也可以并行计算上述计算的一部分或全部。

[0257]

2.3权重向量和输入向量两者的量化

[0258]

接下来,将描述权重向量w和输入向量x都被α-n/p

量化的情况下的方法。这里,使用自然数执行内积运算的情况:α=2和p∈{1,2,3,...}。这里,输入向量分量xi和权重向量分量wi分别由下面描述的公式(20)和(21)表示。此外,在下面描述的公式(20)和(21)中,s

xi

,s

wi

∈{-1,1}并且ni,mi∈{0,1,2,...}。

[0259][0260][0261]

这里,当输入向量x和权重向量w被归一化以分别满足|xi|≤1和|wi|≤1,并且随后根据需要将v乘以归一化乘数时,内积运算可以由下面描述的公式(22)表示。此外,这里,yr由下面描述的公式(23)定义。

减法器根据从xor电路440输入的u/d的值,对由相应累加器保存的值o仅加或减1位。对于根据开发示例的累加器组450,由于yr的值可以通过与高阶位相加或相减1位来更新,因此不需要普通的加法器-减法器,从而能够减小电路规模。

[0278]

(乘法器组460)

[0279]

乘法器组460将通过上述处理为每个余数更新的yr乘以对应于该余数的值。为此目的,乘法器组460包括对应于(mi ni)mod p的每个余数的多个乘法器。例如,乘法器组460将从累加器组450输入的y0乘以1,并将y1乘以2-1/p

。

[0280]

(第二加法器470)

[0281]

第二加法器470将乘法器组460为每个余数计算出的yr值相加,并输出最终运算结果y。

[0282]

上面已经描述了积和运算电路400。如上所述,利用根据开发示例的积和运算电路400,在与(mi ni)mod p的每个余数相对应的累加器中累加yr,并且在最后一起执行乘法,从而可以最小化乘法次数。注意,在图17所示的示例中,尽管对i执行顺序计算以更新yr,但也可以并行计算上述计算的一部分或全部。

[0283]

此外,关于图17所示的积和运算电路400,已经描述了与累加器对应的多个加法器-减法器(1位上下计数器)并行安装的情况下的示例。然而,根据开发示例的积和运算电路400可以包括选择器和单个加法器-减法器来代替上述配置,如图16所示的积和运算电路300中的那样。此外,类似地,多个加法器-减法器可以并行安装在积和运算电路300上。可以适当地设计根据开发示例的积和运算电路的配置,使得电路规模按照p的值变小。

[0284]

此外,关于图17所示的积和运算电路400,已经描述了基于(mi ni)的低阶q位选择加法器-减法器和累加器的情况。另一方面,上面描述的公式(22)可以修改为下面描述的公式(24)。

[0285][0286]

因此,可以通过如图18所示的积和运算电路500中的单个加法器-减法器来实现内积运算。图18是在根据开发示例的权重向量和输入向量两者都被量化的情况下的积和运算电路的示例。

[0287]

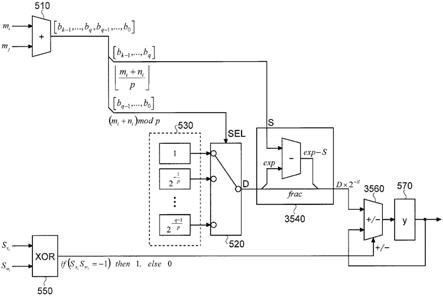

参考图18,积和运算电路500包括加法器510、选择器520、存储电路组530、移位运算器540、xor电路550、加法器-减法器560和累加器570。

[0288]

(加法器510)

[0289]

加法器510将输入mi和ni相加。加法器510可以执行与图17中所示的第一加法器410的致动相同的致动。

[0290]

(选择器520)

[0291]

选择器520基于与低阶q位对应的值[b

q-1

,...,b0]在存储电路组530中包括的多个存储电路中选择与该电路连接的存储电路。

[0292]

(存储电路组530)

[0293]

存储电路组530包括多个存储电路,每个存储电路对应于(mi ni)mod p的余数的值。对应于每个余数的加法乘数存储在每个存储电路中。注意,存储电路组530中包括的每个存储电路可以是将加法乘数保存为常数的只读电路,或者可以是可重写寄存器。当加法乘数作为常数存储在只读电路中时,具有可以简化电路配置和降低功耗的优点。

[0294]

(移位运算器540)

[0295]

移位运算器540对存储在连接的存储电路中的加法乘数执行与[b

k-1

,...,bq]相对应的高阶位的值的右移位运算。

[0296]

(xor电路550)

[0297]

xor电路550基于输入s

xi

和s

wi

输出1或0。xor电路550可以执行与图17中所示的xor电路440相同的致动。

[0298]

(加法器-减法器560)

[0299]

加法器-减法器560基于移位运算器540的运算结果和来自xor电路550的输入,对在累加器570中保存的y重复执行加法或减法。

[0300]

(累加器570)

[0301]

累加器570保存内积运算的结果y。

[0302]

如上所述,利用根据开发示例的积和运算电路500,可以通过单个加法器-减法器560和单个累加器570实现内积运算,并且可以进一步减小电路规模。

[0303]

注意,在上面描述中,已经作为示例描述了输入向量x和权重向量w使用公共p的情况。然而,在根据开发示例的信息处理方法中,可以将不同的p用于输入向量x和权重向量w。在这种情况下,输入向量x和权重向量w可以分别由下面描述的公式(25)和(26)表示。

[0304][0305][0306]

此时,当pm和pn的最小公倍数为p0,即apm=p0和bpn=p0时,输入向量分量xi和权重向量分量wi分别由下面描述的公式(27)和(28)表示。

[0307][0308][0309]

因此,通过将mi ni的运算替换为ami bni,并进一步将p替换为p0,即使在p不同的情况下,也可以类似于上述描述执行计算。此外,在pm和pn用幂表示的情况下,可以通过移位运算获得ami和bni。

[0310]

接下来,将详细描述根据开发示例的输入向量x的量化方法。当输入向量x和权重向量w都被量化时,权重向量w的量化可以预先计算,但是输入向量x的量化需要在运行时执行。为此,需求通过小规模运算电路实现输入向量x量化的方法。

[0311]

这里,|xi|≤1是c=[c

k-1

,...,c0]的位数组。注意,c是定点符号,其中c

k-1

对应于1。

[0312]

此时,从c的msb(最高有效位)开始连续0的位数被设置为l。此外,通过将c=

[c

k-1

,...,c0]左移l位而获得的位数组为d,并且该位数组被视为msb为0.5的定点。

[0313]

接下来,将下面描述的最小r满足公式(29)定义为r

min

。注意,这里是r∈{0,...,p-1},但是当找不到最小r时,可以设置r

min

=p。这里,当mi由下面描述的公式(30)定义时,|xi|可以近似,即量化为下面描述的公式(31)。

[0314][0315]

mi=p(l-1) r

min

ꢀꢀꢀ

(30)

[0316][0317]

注意,上述计算可以通过包括从c的msb计数连续0的位数l的配置和与固定值p次执行比较的配置来实现。

[0318]

2.4开发示例的效果

[0319]

接下来,将详细描述根据开发示例的权重向量w和输入向量x的量化所施加的效果。这里,在以权重向量分量wi和输入向量分量xi为

±

2-n/p

执行量化的情况下,比较使用p=1(即基础技术中描述的量化方法)的情况下的识别率和使用p=2(即开发示例的量化方法)的情况下的识别率。

[0320]

具体地,在通过浮点学习权重向量w和输入向量x之后,通过p的各自值将所获得的系数量化到最近的量化点,并执行实验来比较在不重新学习的情况下执行推断的情况下的图像识别率。

[0321]

注意,cifar-10图像集(10个类的分类,学习数据=50,000个图像,测试数据=10,000个图像)被用作数据集。

[0322]

此外,使用基于resnet23的11层的resnet作为网络。图19是示出根据开发示例的在比较实验中使用的resnet的网络结构的图。在图19中,附图中右侧示出了输入到每一层的输入大小,附图中左侧示出了内核大小。此外,如图19所示,创建的网络包括不包括最大池化层的resblock和包括最大池化层的resblock。图20和图21是分别示出不包括最大池化层的resblock和包括最大池化层的resblock的网络配置的图。

[0323]

接下来将详细描述实验中使用的权重向量w和输入向量x的量化方法。

[0324]

首先,将描述在以p=1执行量化的情况下的数据。这里,n=-3至12的32个值(16个值

×2±

)用于权重向量w的量化。此时,量化权重向量分量wi=

±

(2-n

)的可能值如下面描述的表2所示。

[0325]

表2

[0326]

n-3-2-101234

±

2-n

±8±4±2±1±

0.5

±

0.25

±

0.125

±

0.0625n56789101112

±

2-n

±

0.03125

±

0.015625

±

0.007813

±

0.003906

±

0.001953

±

0.000977

±

0.000488

±

0.000244

[0327]

此外,在对输入向量x的量化中,有三种不同的量化:在输入relu块前,执行了16个值(8个值

×2±

)n=-4至3,32个值(16个值

×2±

)n=-4至11,64个值(32个值

×2±

)n=-4至27。此时,量化输入向量分量xi=

±

(2-n

)的可能值如下面描述的表3至5所示。

[0328]

表3

[0329]

n-4-3-2-10123

±

2-n

±

16

±8±4±2±1±

0.5

±

0.25

±

0.125

[0330]

表4

[0331]

n-4-3-2-10123

±

2-n

±

16

±8±4±2±1±

0.5

±

0.25

±

0.125n4567891011

±

2-n

±

0.0625

±

0.03125

±

0.015625

±

0.007813

±

0.003906

±

0.001953

±

0.000977

±

0.000488

[0332]

表5

[0333]

n-4-3-2-10123

±2n

±

16

±8±4±2±1±

0.5

±

0.25

±

0.125n4567891011

±

2-n

±

0.0625

±

0.03125

±

0.015625

±

0.007813

±

0.003905

±

0.001953

±

0.000977

±

0.000488n1213141516171819

±2n

±

0.000244

±

0.000122

±

6.10e-05

±

3.05e-05

±

1.53e-05

±

7.63e-06

±

3.81e-06

±

1.91e-06n2021222324252627

±2n

±

9.54e-07

±

4.77e-07

±

2.38e-07

±

1.19e-07

±

5.96e-08

±

2.98e-08

±

1.49e-08

±

7.45e-09

[0334]

接下来,将描述使用p=2执行量化的情况下的数据,即根据开发示例的方法。其中,n=-6至9的32个值(16个值

×2±

)用于权重向量w的量化。此时,量化权重向量分量wi=

±

(2-n/2

)的可能值如下面描述的表6所示。

[0335]

表6

[0336]

n-6-5-43-2-101

±

2-n/2

±8±

5.656854

±4±

2.828427

±2±

1.414214

±1±

0.707107n23456789

±

2-n/2

±

0.5

±

0.353553

±

0.25

±

0.176777

±

0.125

±

0.088388

±

0.0625

±

0.044194

[0337]

此外,在对输入向量x的量化中,有三种不同的量化:在输入relu块前,执行了16个值(8个值

×2±

)n=-8至-1,32个值(16个值

×2±

)n=-8至7,64个值(32个值

×2±

)n=-8至23。此时,量化输入向量分量xi=

±

(2-n/2

)的可能值如下面描述的表7至9所示。

[0338]

表7

[0339]

n-8-7-6-5-4-3-2-1

±

2-n/2

±

16

±

11.31371

±8±

5.656854

±4±

2.828427

±2±

1.414214

[0340]

表8

[0341]

n-8-7-6-5-4-3-2-1

±

2-n/2

±

16

±

11.31371

±8±

5.655854

±4±

2.828427

±2±

1.414214n01234567

±

2-n/2

±1±

0.707107

±

0.5

±

0.353553

±

0.25

±

0.176777

±

0.125

±

0.088388

[0342]

表9

[0343]

n-8-7-6-5-4-3-2-1

±

2-n/2

±

16

±

11.31371

±8±

5.656854

±4±

2.828427

±2±

1.414214n01234567

±

2-n/2

±1±

0.707107

±

0.5

±

0.353553

±

0.25

±

0.176777

±

0.125

±

0.088388n89101112131415

±

2-n/2

±

0.0625

±

0.044194

±

0.03125

±

0.022097

±

0.015625

±

0.011049

±

0.007813

±

0.005524

n1617181920212223

±

2-n/2

±

0.003906

±

0.002762

±

0.001953

±

0.001381

±

0.000977

±

0.000691

±

0.000488

±

0.000345

[0344]

图22示出了在不通过上述量化进行重新学习而执行推断的情况下的图像识别率的比较结果。在图22中,纵轴表示识别精度,并且横轴表示输入向量x的量化数(n值)。此外,在图22中,量化前的识别精度由线段c表示,在以p=1执行量化的情况下的识别精度由线段p1表示,并且在以p=2执行量化的情况下的识别精度由线段p2表示。

[0345]

这里,当比较线段p1和线段p2时,在将输入向量x的量化数设置为32个值或64个值的情况下,可以看出,与以p=1执行量化的情况相比,以p=2执行量化的情况下识别精度显著提高。此外,可以看到,即使当比较线段p2和线段c时,也没有观察到识别精度的显著劣化。这表明,在输入向量x的量化次数足够的情况下,通过采用根据开发示例的量化方法,即使在不执行再学习的情况下,也可以保持高识别精度。

[0346]

如上所述,通过根据开发示例的量化方法,可以有效地减少内积运算中的处理负荷,并保持学习设备的高性能。

[0347]

3.结论

[0348]

如上所述,根据基础技术及其开发示例的信息处理装置包括积和运算电路,该积和运算电路基于多个输入值和由对应于各个输入值的幂表达式量化的多个加权系数执行积和运算。量化加权系数的指数由分母中具有预定除数p的分数表示。此外,积和运算电路基于从除数p确定的余数,使用不同的加法乘数执行积和运算。通过这样的配置,可以进一步降低与内积运算相关的处理负荷,并保证加权系数的量化粒度。

[0349]

4.第一实施例

[0350]

下面,将参考附图详细描述本公开的第一实施例。请注意,在下面描述的描述中,基础技术及其开发示例被简单地称为基础技术。

[0351]

4.1基础技术的问题

[0352]

图23中再次示出了在根据基础技术的权重向量和输入向量都被量化的情况下的积和运算电路的示例(对应于图18)。如图23所示,基础技术例示了通过表查找实现积和运算的方法。具体地,提供表(存储电路组530),其中由指示量化粒度的p确定条目的数量和值,并且使用该表执行针对dnn/cnn推断处理的积和运算。

[0353]

因此,在下面描述的实施例中,通过例示切换多个表的配置,同时例示由2的p次根的幂形成的值表以外的表,更清楚地说明存储电路组530是可重写寄存器的优点。

[0354]

4.2值表的示例

[0355]

如上所述,基础技术提出了一种新的量化方法,其目的是减少深度神经网络(dnn)和卷积神经网络(cnn)的积和运算量。通常,信息论中的量化是指用离散值近似表示模拟量,但这里的量化定义为表示用较小位量表示原始值的精度。例如,将原来由32位浮点数表示的值截断为10位或8位浮点数或定点数,更极端地,将该值截断为2位或1位称为量化。

[0356]

在基础技术中,通过在dnn/cnn推理时量化系数或变量,缩短表示系数或变量的数值的字长。因此,可以实现用于存储参数的存储器容量的减小、积和运算时的运算量和运算能量的减小等。

[0357]

因此,在基础技术中,变量被定义为x,并且常数被定义为w,已经执行了如公式(32)(对应于上述公式(20)和(21))所示的量化。

[0358][0359]

这里,xi表示输入向量x的第i个元素,wi表示系数向量w的第i个元素,s表示元素的正/负号,m表示量化输入向量x的第i个元素时的索引(符号),n表示量化系数向量w的第i个元素时的索引(符号),p表示量化的粒度。

[0360]

在基础技术中,如图23所示,指示量化粒度的p被用作参数,并且使用由p确定条目数和值的表(存储电路组530)来执行针对dnn/cnn推断处理的积和运算。具体地,沿着2次幂(更准确地说,2的p次根的幂)的函数空间的p个值被保存为表值,并且在根据变量的正/负号和动态范围进行缩放的同时执行累积加法,并且执行系数,从而实现2的幂方法的积和运算。注意,在基础技术中,下面描述的公式(33)被例示为表值。

[0361][0362]

当将公式(33)的表值绘制在曲线图上时,索引与表值之间的关系如图24所示。

[0363]

这里,考虑另一个表值。例如,沿着线性函数空间的值被应用为表的值,而不是沿着2的幂的函数空间的值。在这种情况下,执行如下面描述的公式(34)所示的量化。

[0364][0365]

在公式(34)中,关于每个符号,类似于公式(32)所示的2的幂的表达式的情况,xi表示输入向量x的第i个元素,wi表示系数向量w的第i个元素,s表示元素的正/负号,m表示量化输入向量x的第i个元素时的索引(符号),n表示量化系数向量w的第i个元素时的索引(符号),p表示量化的粒度。

[0366]

在本实施例中,组合基础技术的2的幂表达式中的表、域和范围,并将沿线性函数空间的p值设置为表值。使用这些值,在根据变量和系数的正/负号和动态范围执行缩放的同时执行累积加法,从而可以实现线性方法的积和运算。这种情况下的电路配置可以类似于图23中所示的积和运算电路。然而,存储电路组530中的表值是下面描述的公式(35)所示的值。

[0367][0368]

注意,公式(35)可以简单地表示为下面描述的公式(36)。

[0369][0370]

当将公式(35)或公式(36)表示的表值绘制在曲线图上时,索引与表值之间的关系

如图25所示。

[0371]

虽然已经以线性表达式的形式描述了该表达式,但是通过采用稍后描述的第三实施例中示例的记数法,该表达式也可以应用于具有符号部分、指数部分和尾数部分的浮点数表达式。

[0372]

图26是将以2的幂表示的表值和以线性表示的表值绘制在同一曲线图上的图。如图26所示,2的幂的表达式的表值相对于线性表达式具有向下突起的形状。

[0373]

通过以这种方式改变表值,可以容易地实现具有另一特征的积和运算电路。

[0374]

作为又一表的示例,可以想象将2的幂的表达式转换为相对于线性表达式的值的向上突起。

[0375]

此外,通过改变作为基础的函数空间,可以创建适用于cnn/dnn任务的各种表。但是,由于积和运算电路的特征,要求在该域段单调递减。

[0376]

注意,如在基础技术中所描述的,存储电路组530中包括的每个存储电路可以是将加法乘数保存为常数的只读电路,或者可以是可重写寄存器。

[0377]

4.3积和运算电路的具体示例

[0378]

接下来,将参考一些示例描述根据第一实施例的积和运算电路的具体示例。

[0379]

4.3.1第一具体示例

[0380]

图27是示出根据第一具体示例的积和运算电路的示意性配置示例的电路图。如图27所示,与图23所示的积和运算电路类似,根据第一具体示例的积和运算电路包括整数加法器(也简单地称为加法器)510、选择器520、存储电路组530、移位运算器540、xor电路550、加法器-减法器560和累加器570。

[0381]

(整数加法器510)

[0382]

整数加法器510将输入mi和ni相加。此时,mi和ni的相加结果可以表示为如附图所示的位数组[b

k-1

,...,bq,b

q-1

,...,b0]。

[0383]

(选择器520)

[0384]

选择器520基于与低阶q位对应的值[b

q-1

,...,b0]在存储电路组530中包括的多个存储电路中选择与该电路连接的存储电路。

[0385]

(存储电路组530)

[0386]

存储电路组530包括多个存储电路,每个存储电路对应于(mi ni)mod p的余数的值。在每个存储电路中,对应于每个余数的加法乘数被存储为具有以2为基数的指数部分的浮点表达式的归一化数。这里,由于在存储电路组530中存储的上述加法/减法乘数在大于0.5并且小于或等于1.0的范围内,因此其可以通过具有1位或更多的字长作为指数部分来用归一化数表示。注意,存储电路组530中包括的每个存储电路可以是将加法乘数保存为常数的只读电路,或者可以是可重写寄存器。当加法乘数作为常数存储在只读电路中时,具有可以简化电路配置和降低功耗的优点。

[0387]

(移位运算器540)

[0388]

根据本实施例的移位运算器540对存储在连接的存储电路中的加法乘数执行与[b

k-1

,...,bq]相对应的高阶位的值的右移位运算。

[0389]

(xor电路550)

[0390]

xor电路550基于输入s

xi

和s

wi

输出1或0。

[0391]

(加法器-减法器560)

[0392]

加法器-减法器560基于来自移位运算器540的输入和来自xor电路550的输入,对在累加器570中保存的y重复执行加法或减法。当来自xor电路550的输入为0时,执行加法,并且当输入为1时,执行减法。

[0393]

(累加器570)

[0394]

累加器570保存积和运算的结果y。

[0395]

此外,除了上述配置之外,根据第一具体示例的积和运算电路进一步包括保存多个不同表的存储器1530和选择性地将存储器1530中的表值写入存储电路组530的每个存储电路(寄存器或存储器)的选择器1531。

[0396]

(存储器1530)

[0397]

存储器1530保存例如上述2的幂的表达式的表1530a和线性表达式的表1530b。

[0398]

(选择器1531)

[0399]

选择器1531根据从高阶控制单元等输入的写入表控制值从存储器1530读取表1530a或1530b,并将读取表1530a/1530b写入存储电路组530的每个存储电路。

[0400]

在包括上述配置的情况下,可以切换作为基础的函数空间,因此可以根据cnn/dnn任务使用适当的表执行积和运算。

[0401]

4.3.2第二具体示例

[0402]

图28是示出根据第二具体示例的积和运算电路的示意性配置示例的电路图。如图28所示,在根据第二具体示例的积和运算电路中,在与图23所示的积和运算电路相同的配置中,存储电路组530被替换为保存多个不同表的多个(在本示例中为两个)存储电路组530a和530b,并且积和运算电路进一步包括选择器1532,该选择器选择性地切换存储电路组530a或530b与选择器520之间的连接。

[0403]

例如,类似于图23,存储电路组530a包括多个存储电路,其存储上述2的幂的表达式的表的值。另一方面,例如,存储电路组530b包括存储上述线性表达式的表的值的多个存储电路。

[0404]

选择器1532根据从高阶控制单元等输入的表切换信号来切换存储电路组530a/530b与选择器520之间的连接。

[0405]

在包括上述配置的情况下,与第一具体示例类似,可以切换作为基础的函数空间,因此可以根据cnn/dnn任务使用适当的表执行积和运算。

[0406]

4.4运算和效果

[0407]

如上所述,根据本实施例,例如,通过为表(存储电路组530)选择适当的加法常数,可以在不改变积和运算电路2100中的运算电路部分的配置的情况下,选择不是2的幂的表达式的线性浮点数。

[0408]

这使得可以选择与dnn/cnn处理任务相对应的表值,而不限于2的幂的表达式、线性表达式等。

[0409]

通常,当实施用于dnn/cnn的运算电路系统时,为了应付各种处理任务,布置大量处理器元件,包括多个积和电路,例如float32、float16和短字长浮点,并且还包括以基础技术的2的幂表示的积和电路。另一方面,根据本实施例,仅通过切换表,就可以通过2的幂和短字长浮点的表达式对乘积和电路使用完全相同的电路,从而可以实现整体电路的显着

减少。

[0410]

其他配置、运算和效果可以类似于上述基础技术的配置、运算和效果,因此这里将省略其详细描述。

[0411]

5.第二实施例

[0412]

下面,将参考附图详细描述第二实施例。

[0413]

5.1基础技术的问题

[0414]

在基础技术中,需要找到满足公式(29)的最小r,但在搜索用于实施的最佳r中,需要准备通过进一步将2的p次根的幂乘以2的2p次根而获得的值用于值比较。因此,在将现有表(存储电路组530)用于值搜索的情况下,每次都需要乘以2的2p次根的运算,计算成本变得非常高。可替代地,在使用预先乘以2的2p次根的表的情况下,需要在实施基础技术的系统中实现两个表:用于积和运算的表和用于量化舍入的表,并且存在管理趋于复杂的问题。

[0415]

因此,在本实施例中,将结合示例描述能够在抑制管理复杂性的同时降低计算成本的量化电路和方法。

[0416]

5.2量化电路的具体示例

[0417]

在基础技术中,每一层(或特征图)中的输入向量和积和运算结果需要在运行时量化为2的幂的表达式,并发送到后续处理或存储在内存中。由于dnn和cnn的系数的值在中间不改变,所以可以预先执行转换为2的幂的表达式并使用它,但需要将在推理计算中出现的数值转换为2的幂的表达式。这种处理通常被称为运行时量化。在本实施例中,将描述量化器的舍入的更发达形式。

[0418]

由于量化器的舍入是为了减少信息量而进行的量化,所以输出中的信息量小于量化器输入中的信息量。具体地,具有输入的一定宽度的数值由一个值表示。即,一定范围内的数值舍入为一个代表值。图29是示出量化器的舍入的示例的图。如图29所示,当输入一定范围ra内包括的值到量化器时,该值被舍入为a,并分配符号m-1。另一方面,当输入范围rb内包括的值时,该值被舍入为b,并分配符号m。

[0419]

在基础技术中的输入向量x的运行时量化中,需要找到满足上述公式(29)的最小r,但在搜索用于实施的最佳r中,需要准备通过进一步将2的p次根的幂乘以2的2p次根而获得的值。这对应于公式(37)中由实线包围的部分(与公式(29)相同)。

[0420][0421]

这意味着沿着2的幂的表达式的表达式函数进行0.5舍入,并且计算图29中的中间点b的值。当不包括上述公式(37)中的实线所包围的项的值根据r的值排列时,它变得与第一实施例中例示的积和运算的值表(见公式(33))相同。

[0422]

这意味着,如图30所示,基础技术中描述的表(存储电路组530)可以用于在运行时量化时的值搜索。注意,图30是示出作为比较示例的神经网络电路的示意性配置示例的框图。

[0423]

如图30所示,作为比较示例的神经网络电路包括幂表达式转换单元2001、乘法单元2002、变量缓冲器2003、系数存储器2004、运算结果缓冲器2005、积和运算电路2100。积和运算电路2100包括积和运算单元2101、幂表达式转换单元2102、幂表达式表2103和乘法单

元2104。

[0424]

(乘法单元2002)

[0425]

乘法单元2002通过对从幂表达式表2103读取的表值执行下面描述的公式(38)所示的乘法,沿着2的幂表达式的表达式函数执行0.5舍入,并将获得的值输入到幂表达式转换单元2001。

[0426][0427]

(幂表达式转换单元2001)

[0428]

幂表达式转换单元2001使用从乘法单元2002输入的值将输入值转换为2的幂的表达式。转换获得的值存储在变量缓冲器2003中。因此,2的幂表达式的变量存储在变量缓冲器2003中。

[0429]

(积和运算单元2101)

[0430]

积和运算单元2101根据存储在变量缓冲器2003中的幂表达式的变量和存储在系数存储器2004中的幂表达式的系数执行积和运算。此时,积和运算单元2101使用存储在幂表达式表2103中的表值执行积和运算。幂表达式表2103中存储的表是上述公式(33)中所示的值表。

[0431]

(乘法单元2104)

[0432]

乘法单元2104通过对从幂表达式表2103读取的表值执行上面描述的公式(38)所示的乘法,沿着2的幂表达式的表达式函数执行0.5舍入,并将获得的值输入到幂表达式转换单元2001。

[0433]

(幂表达式转换单元2102)

[0434]

幂表达式转换单元2102使用从乘法单元2104输入的值将从积和运算单元2101输入的值转换为2的幂的表达式。转换获得的值存储在运算结果缓冲器2005中。因此,2的幂表达式的变量存储在运算结果缓冲器2005中。

[0435]

如上所述,作为运行时量化器的幂表达式转换单元2001和2102可以通过将积和运算电路2100中存在的2幂表达式表2103(参数p)乘以2的2p次根来实现。

[0436]

然而,在上述配置中,由于每次运行时量化都发生乘法,因此计算成本显著高。因此,如图31所示,还可以预先准备通过将幂表达式表2103中的表值乘以公式(38)所示的常数而获得的表(幂表达式转换表2202和2204)。

[0437]

此外,运行时量化通过量化来执行,包括用于dnn/cnn的外部输入数据的量化和乘积求和后的舍入。它们是相同的处理。因此,如图32所示,幂表达式转换表2204由幂表达式转换单元2001和2102以时分方式共享和使用,由此可以减少整个系统的表保存量。

[0438]

同时,通过将作为确定量化粒度的参数p的2的幂表达式表乘以2的2p次根来获得幂表达式转换表2202和2204。即,当修改用于从幂表达式表2103导出幂表达式转换表2202和2204的转换公式(38)时,获得下面描述的公式(39)。

[0439][0440]

这意味着2的幂表达式表的奇数部分子集,它是参数2p。因此,可以将由下面描述的公式(40)表示的偶数部分子集的表耦合,即,可以将幂表达式表2103和幂表达式转换表

2202/2204统称为一个表。

[0441][0442]

图33是示出偶数部分子集和奇数部分子集组合成一个表的情况的图。如图33所示,积和运算单元2101和幂表达式转换单元2001和2102共享包括偶数部分子集和奇数部分子集的幂表达式表2203。例如,可以根据符号索引的地址的偶数和奇数来分配输入到积和运算单元2101和幂表达式转换单元2001和2102的表值。

[0443]

以这种方式,通过将两个表组合成一个表,例如,在将表作为常数存储在只读电路中的情况下,可以随着逻辑压缩大大简化电路配置,并获得可以降低功耗的优点。

[0444]

5.3运算和效果

[0445]

如上所述,根据本实施例,当执行运行时量化时,可以使用积和运算的2的幂表达式表来生成用于比较运行时量化的值。

[0446]

此时,尽管在基础技术中经常发生乘法,但通过提供预先准备的表,通过消除每次的乘法,可以大大降低运行时量化时的运算成本。

[0447]

此外,通过集成2的幂表达式表和比较值表,可以将需要管理的表合并为一个表。因此,可以减小电路规模并降低功耗。

[0448]

其他配置、运算和效果可以类似于上述基础技术或实施例的配置、运算和效果,因此这里将省略其详细描述。

[0449]

6.第三实施例

[0450]

下面,将参考附图详细描述第三实施例。

[0451]

6.1基础技术的问题

[0452]

在上述基础技术中,提出了能够进一步降低与内积运算相关的处理负荷并保证加权系数的量化粒度的新的和改进的信息处理装置和信息处理方法。

[0453]

然而,在基础技术的方法中,需要使用定点表达式作为内部数值表达式,并且需要较长的字长,导致规模增大,功耗增加。

[0454]

例如,当使用定点表达式以外的数值表达式时,移位运算是2的幂乘运算,因此,y=x*2^n是一般的。因此,需要幂运算器和乘法器,导致规模的增加。这里,*是乘法运算器,^是幂运算器。

[0455]

此外,在基础技术中,对于输入向量的量化,仅指示来自定点表达式的量化,而没有指示用于从其他数值表达式以低成本执行量化的方法。

[0456]

例如,使用基础技术的方法,所需的定点表达式字长如下面的描述。注意,在下面的描述中,输入向量分量xi和权重向量分量wi由上面描述的公式(32)表示。此外,在公式(32)中,s

xi

,s

wi

∈{-1,1}并且ni,mi∈{0,1,2,...}。

[0457]

此外,与量化输入值的指数相关的分子是mi,分母的预定除数是p,与量化加权系数的指数相关的分子是ni,分母的预定除数是p。

[0458]

根据上述参考图23描述的基础技术的积和运算电路通过单个加法器-减法器560和单个累加器570在较小的电路规模上实现内积运算。这里,例如,假设p=16,并且mi和ni的字长为8位,移位运算器540的最大移位量为32位。然后,例如,当有效数为6位数时,存储电路组530中存储的加/减乘数的字长为20位,因此移位运算器540的输出字长为52位。由于累

加器570的字长取决于执行加法的次数,例如,当加法的次数被设置为最大255次时,字长是通过向移位运算器540的输出字长相加8位而获得的60位。

[0459]

另一方面,作为用浮点表示数字的方法,基于ieee 754标准的方法是已知的。根据这个标准,以2或10为基数的有限数用三个整数表示:符号、尾数和指数。作为该标准的特征,在以2为基数的二进制浮点形式中,归一化尾数的最高有效位总是1,因此省略并表示。此外,在0或非归一化数的情况下,指数为0,并且在归一化数的情况下,通过将预定的固定值加到指数上而获得的偏置表达式。这些表达式形式可以很容易地扩展到任意字长的指数部分和尾数部分。以下,类似于ieee 754标准,将尾数部分的归一化数的最高有效位省略,在0或非归一化数的情况下指数部分为0,并且在归一化数的情况下采用偏置表达式的浮点表示法称为符合ieee 754。

[0460]

因此,在本实施例中,将结合示例描述能够减小电路规模和减小功耗的积和运算电路及其方法。根据下面描述的实施例,也可以以更短的字长,换句话说,以更小的电路规模和功耗实现基础技术的相同效果。

[0461]

6.2积和运算电路的具体示例

[0462]

图34是示出根据第三实施例的积和运算电路的示意性配置示例的电路图。如图34所示,根据第三实施例的积和运算电路包括整数加法器510、选择器520、存储电路组530、2的幂乘法运算器3540、xor电路550、浮点加法器-减法器3560和累加器570。

[0463]

在图34所示的配置中,整数加法器510、选择器520、存储电路组530、xor电路550和累加器570可以类似于第一实施例中参考图27描述的配置。

[0464]

(2的幂乘法运算器3540)

[0465]

2的幂乘法运算器3540对应于图27中的移位运算器540。因此,由2的幂乘法运算器3540执行的运算对应于定点表达式中的移位运算。

[0466]

2的幂乘法运算器3540对由连接的存储电路存储的加法乘数对应于[b

k-1

,...,bq]的高阶位的值s执行以-s为指数的2的幂运算,即d*2^-s。这里,p=2^q,并且将输入d的浮点表达式的2的幂乘法运算器3540的指数部分的字长与存储电路中的指数部分的字长相加,以便扩展到可以表示最小值-s的指数的大小,也就是说,扩展到可以表示指数-(1 2^(bw(mi)-q) 2^(bw(ni)-q))的大小,该运算只能通过对浮点表达式的指数部分进行整数减法来实施,并且运算结果不会变成非归一化数字。这里,bw(mi)和bw(ni)分别是表示mi和ni的字长的值。

[0467]

(浮点加法器-减法器3560)

[0468]

与加法器-减法器560类似,浮点加法器-减法器3560基于来自2的幂乘法运算器3540的输入和来自xor电路550的输入,对在累加器570中保存的y重复执行加法或减法。当来自xor电路550的输入为0时,执行加法,并且当输入为1时,执行减法。

[0469]

作为示例,假设存储电路组530,2的幂乘法运算器3540,浮点加法器-减法器3560,累加器570的存储值使用符合ieee 754的浮点表达式,并且在p=16并且mi和ni的字长为8位的情况下,如果s的最大值为32位就足够了,并且2的幂乘法运算器3540的浮点指数部分是7位(因为偏置是63,2^63到2^-62的范围可以用归一化数表示),如果在存储电路组530中存储的加/减乘数的字长为,例如,假设有效数是6位数,尾数部分19位和指数部分1位,并且浮点加法器-减法器3560和累加器570的字长,例如,假设加法次数最多为255,不从根据最大

值s确定的指数部分的字长进一步扩展,而是尾数部分19位和指数部分7位。

[0470]

6.3量化方法的开发

[0471]

如上所述,根据本实施例,由于作为积和运算的结果输出浮点表达式的值,因此还希望能够以低成本执行重新量化。从基数为2的浮点表达式的量化可以以下面描述的方式执行。

[0472]

首先,对浮点表达式xi进行归一化,使绝对值小于等于1.0。这种归一化可能类似于基础技术中的归一化。

[0473]

接着,当与量化值的指数相关的分子为mi、分母的预定除数为p、mi的字长为bw(mi)、p=2^q时,将具有指数部分的字长的浮点表达式用作输入|xi|<=1的浮点,该指数部分的字长可以用至少2^(-2^(bw(mi)-q))表示为归一化数。因此,可以如下所述执行量化。

[0474]

当xi≠0并且指数满足-2^(bw(mi)-q)或更大的条件时,

[0475]

l=-指数(基数为2的指数)

[0476]

d=尾数(作为定点符号处理,其msb为0.5位)

[0477]

并且,与基础技术类似,获得r

min

,即满足d≥2^-((r 1/2)/p)的最小r,并以mi=p(l-1) r

min

执行量化。由于满足当前条件的输入仅限于归一化数的浮点数,所以当使用基数为2的浮点表达式时,可以省略基础技术中所需要的“从c的msb计数连续0的位数l的配置”。

[0478]

另一方面,在不满足上述条件的情况下,即在xi=0或指数小于-2^(bw(mi)-q)(包括非归一化数)的情况下,替换表示0的量化符号。指数小于-2^(bw(mi)-q)的值是小于量化值所能表示的最小值的值,因此可以视为0。

[0479]

例如,假设量化后mi的字长为8位,并且q=4,则输入的浮点的指数至多-2^(8-4)=-16可以表示为归一化数就足够了。因此,当使用符合ieee754的浮点表达式时,如果指数部分为6位就足够了。也就是说,如果偏置是31,并且2^31到2^-30的范围可以用归一化数表示就足够了。

[0480]

此外,例如,假设输入是符合ieee754的浮点表达式,换句话说,指数部分exp是偏置表达式,尾数部分frac是其中省略msb中的1的表达式,对于xi≠0和指数为-2^(bw(mi)-q)或更多的xi,可以如下所述执行计算。

[0481]

l-1=(ebias-1)-exp(其中,ebias是指数部分的偏置值)

[0482]

d={1,frac}(其中{,}是位级联运算器)

[0483]

6.4量化电路的具体示例

[0484]

接下来,将描述实现上述量化方法的量化电路。图35是示出根据第三实施例的量化电路的示意性配置示例的电路图。

[0485]

如图35所示,根据本实施例的量化电路包括整数减法器3210、移位运算器3220、存储电路组3230、比较器组3240、优先级编码器3250、整数加法器3260、比较器3270和选择器3280。

[0486]

(整数减法器3210)

[0487]

整数减法器3210通过使用符合ieee 754的浮点表达式的输入指数部分exp来计算(l-1)=(ebias-1)-exp。

[0488]

(移位运算器3220)

[0489]

移位运算器3220通过将整数减法器3210计算的(l-1)的值乘以p来计算p(l-1)。这

里,由于p=2^q,这个乘法可以通过q位左移运算来实现。

[0490]

(存储电路组3230)

[0491]

存储电路组3230包括对应于2^-((r 1/2)/p)和r∈{0,...,p-1}的p个存储电路。

[0492]

存储电路组3230中包括的每个存储电路可以是将该值保存为常数的只读电路,或者可以是可重写寄存器。当该常数存储在只读电路中时,具有以下优点:利用后面将要描述的比较器组3240和优先级编码器3250可以简化电路配置,并且可以降低功耗。

[0493]

(比较器组3240)

[0494]

比较器组3240将从存储电路组输出的p值与从输入的浮点表达式的尾数部分生成的d={1,frac}进行比较,并且当d等于或大于d时输出1,并且如果不是这种情况,则输出0。

[0495]

(优先级编码器3250)

[0496]

优先级编码器3250输出与0到p-1范围内的p个输入中输入1的位置相对应的值。在存在多个1的输入的情况下,优先化具有较小数量的位置。在两个输入都为0的情况下,输出p。表10在真值表中指示优先级编码器3250的致动。

[0497]

表10

[0498][0499]

假设优先级编码器的输出为r

min

,则由存储电路组3230、比较器组3240和优先级编码器3250获得r

min

,即满足d≥2^-((r 1/2)/p)的最小r。此外,在找不到最小r的情况下,r

min

=p。

[0500]

(整数加法器3260)

[0501]

整数加法器3260将从移位运算器3220输入的p(l-1)值和从优先级编码器3250输入的r

min

相加,以获得p(l-1) r

min

。

[0502]

(比较器3270)

[0503]

比较器3270比较符合ieee 754的输入浮点表达式的指数部分exp和ebias-2^(bw(mi)-q),当exp和ebias-2^(bw(mi)-q)相等或exp更大时输出1,如果不是这种情况,则输出0。由此,确定了xi≠0并且指数为-2^(bw(mi)-q)或更大。通过使用符合ieee754的浮点表达式作为输入,可以仅通过与指数部分exp的比较来确定输入是否为0。

[0504]

(选择器3280)

[0505]

选择器3280基于比较器3270的输出,将从整数加法器3260输出的p(l-1) r

min

或表示0的符号输出为mi。

[0506]

6.5运算和效果

[0507]

如上所述,根据本实施例,也可以以更短的字长,换句话说,以更小的电路规模和功耗实现与基础技术等效的效果。

[0508]

此外,在安装多个根据本实施例的运算器的情况下,可以使用相同的资源(电路规

模、功率)安装更多的运算器,并且可以提高每个相同资源的运算性能。

[0509]

其他配置、运算和效果可以类似于上述基础技术或实施例的配置、运算和效果,因此这里将省略其详细描述。

[0510]

6.6变型示例

[0511]

此外,可以如下所述修改根据上述第三实施例的配置。

[0512]

6.6.1第一变型示例

[0513]

由于积和运算电路的存储电路组3230中存储的值的范围被限制在0.5以上和1.0以下的范围内,所以d*2^-s的指数为0或负值。因此,当采用符合ieee 754的指数部分偏置时,指数部分的msb固定为0值,因此可以省略。例如,假设p=16(q=4),mi和ni的字长为8位,则d*2^-s的指数范围为2^0到2^-33,因此仅使用指数部分7位(偏置为63)中的低阶6位。也就是说,可以表示2^0到2^-62的范围。在这种情况下,如果省略的msb被扩展并传递到随后的浮点加法器-减法器3560就足够了。

[0514]

6.6.2第二变型示例

[0515]

此外,由于积和运算电路的存储电路组3230中存储的值的范围被限制在大于0.5并且小于或等于1.0的范围内,关于指数部分的范围,正的最大值由累加器570的加法次数确定,负的最大值由s的最大值确定。因为它们可能不对称,所以可以通过将整数加法器510和累加器570中的指数部分的偏置设置为从2^(指数部分的字长-1)-1移位的值来减小指数部分的位。例如,假设p=16(q=4),mi和ni的字长为8位,有效位数为6位,累加器的加法次数最大为255次,则指数的范围为2^-33至2^7。因此,例如,假设偏置是42,指数部分可以是6位。在本示例中,可以表示2^-41到2^20。

[0516]

6.6.3第三变型示例

[0517]

此外,积和运算电路的指数部分的负最大值可以小于s的最大值。在这种情况下,当指数部分超过可以表示为减法的结果的范围时,可以通过尾数部分的右移来对应非归一化数。采用这样的配置,需要增加比较器和移位电路,但可以减少指数部分的位长。

[0518]

6.6.4第四变型示例

[0519]

此外,在积和运算电路的指数部分的负最大值小于s的最大值的情况下,当指数部分超过可以表示为减法的结果的范围时,指数部分可以被设置为零。当由此引起的精度下降可以忽略不计时,可以减少指数部分的位长。

[0520]

6.6.5第五变型示例

[0521]

此外,积和运算电路的d*2^-s的计算可以用浮点算符(乘法算符和幂运算器)来实现。

[0522]

6.6.6第六变型示例

[0523]

此外,可以通过程序来实现根据上述第三实施例的电路配置(积和运算电路和/或量化电路)的部分或全部。

[0524]

7.第四实施例

[0525]

下面,将参考附图详细描述第四实施例。

[0526]

7.1基础技术的问题

[0527]

如上所述,在基础技术中,提出了一种新的量化方法,其目的是减少深度神经网络(dnn)和卷积神经网络(cnn)的积和运算量。

[0528]

图36是用于说明一般dnn和cnn的致动的示意图。注意,图36示出了三层卷积神经网络。

[0529]

如图36所示,在一般dnn和cnn的致动中,对每一层依次执行诸如积和运算的卷积运算(卷积)、池化(池化)和激活函数激励(激活)等处理。此时,存在每一层的运算中使用的系数或该层的输出中出现的变量的取值范围或分布对于每一层都不同的情况。此外,这样的特征不限于每一层,并且可以作为对于每个特征图的分布不同的特征出现。

[0530]

图37至图43示出了用于卷积的每一层的输入/输出变量和系数的示例。图37示出了输入到图36中第一层的卷积层的系数w1,图38示出了输入到图36中第二层的卷积层的系数w2,图39示出了输入到图36中第一层的卷积层的系数w3。此外,图40示出了图36中卷积神经网络的输入(变量)x0,图41示出了图36中第一层的输出(变量)x1,图42示出了图36中第二层的输出(变量)x2,图43示出了图36中第三层的输出(变量)x3。

[0531]

从图37到图43可以看出,关于系数和变量,对于每一层,值的范围是不同的。具体地,关于系数,w1具有分布在大约-5到4之间的值范围,w2具有分布在大约-0.15到0.15之间的值范围,并且w3具有分布在大约-0.4到0.5之间的值范围,如图37到39所示。另一方面,如图40至图43所示,关于变量,x0分布在大约-1到1之间,x1分布在大约0到90之间,x2分布在大约0到120之间,并且x3分布在大约0到20之间。

[0532]

可以说,应该对每一层(或每一特征图)执行必要并且充分的量化(=位量减少)设置,以达到不影响dnn/cnn推断任务结果的程度,而不是出于上述原因不必要地减少表达式位数。在这种情况下,认为基础技术存在下面描述的问题。

[0533]-不考虑数字格式和实际数据的管理。

[0534]-不考虑关于量化设置(精度设置、动态范围设置)的差异化表达式。因此,不能对每一层(或每一特征图)进行不同的量化设置。

[0535]-不区分带正/负号的数值表达式和不带正/负号的数值表达式。

[0536]-所有数值都用正/负符号表示,并且在指定特定层(或特征图)(例如图41至图43中的x1、x2和x3)变量时使用的符号存在浪费。

[0537]-不考虑值0(零)的表达式。因此,不能表示图41至图43中出现的数值0(零)。

[0538]

因此,为了解决上述问题,本实施例提出了数字格式信息和能够以2的幂表达式执行数值表达式的容器。此外,在本实施例中,还提出了能够保存和分离多个量化设置的字节流格式。

[0539]

7.2数字格式信息的具体示例

[0540]

首先,将结合具体示例来描述数字格式信息。

[0541]

7.2.1 s.e.m格式

[0542]

需要用2的幂的表达式对数值表达式(数值数据)进行编码,其可以灵活地选择字长为正/负浮点表达式。为了区分具有正/负符号的数字表达式和不具有正/负符号的数字表达式,需要能够指定存在或不存在正/负符号的设置。此外,为了区分量化设置,需要能够独立地指定关于精度的设置和关于动态范围的设置。

[0543]

因此,在本实施例中,以下描述的三个元素的集合被定义为s.e.m格式。

[0544]-符号信息

[0545]

s.e.m格式中的“s”表示相对于正/负符号的存在或不存在而分配的位数。

[0546]-指数位宽

[0547]

s.e.m格式中的“e”表示相对于动态范围分配的位数。

[0548]-尾数位宽

[0549]

s.e.m格式中的“m”表示相对于精度分配的位数。

[0550]

在图44的数值表中示出了其中(s.e.m)=(1.4.3)(即,符号1位、动态范围4位和精度3位)实际上被分配为2的幂的示例。注意,关于m,2m的值对应于基础技术的p值。

[0551]

此外,有必要考虑值为0(零)的表达式,以便可以将零视为数值表达式。因此,在本实施例中,当e和m的所有位都为1时,该值被定义为零。通过将该位置定义为值0,可以确保单调递减属性(当包含{e,m}组合在其中的位串的索引的值在相同的正/负号内增加时,表达数值减少)。

[0552]

注意,这个数值表达式的最大值(绝对值的最大值)是1.0,当时e和m的所有位都是0。

[0553]

在s.e.m格式中,相应分配位数的s e m之和指示数据字长度(数值数据位宽度)。

[0554]

7.2.2 s.b.q格式

[0555]

在上述s.e.m格式中,为了确认数值的字长并从区域中提取数值,需要将s.e.m的值相加,因此,每次将格式切换到运算装置时都需要进行计算。因此,在本实施例中,除了s.e.m格式之外,定义了通过开发s.e.m格式而获得的s.b.q格式,使得数字格式信息本身与字长信息交织,并且执行分离而无需额外计算。注意,s.b.q格式指示的数值的处理与s.e.m格式完全等价。s.b.q格式的元素如下所示。

[0556]-符号信息

[0557]

s.b.q格式中的“s”表示相对于正/负符号的存在或不存在而分配的位数。这与s.e.m格式的s(符号信息)同义。

[0558]-数值数据位宽

[0559]

s.b.q格式中的“b”表示数值数据的字长。s.e.m格式的e(指数位宽)可以由e=数值数据位宽-s-q导出。

[0560]-q

[0561]

s.b.q格式中的“q”表示相对于精度分配的位数。这与s.e.m格式的m(尾数位宽)同义。

[0562]

7.3实际数据的管理方法:容器与数字格式信息的关系

[0563]

在本实施例中,s.e.m格式和s.b.q格式被称为数字格式信息(数字格式信息)。存储实际数据的容器(数值数据容器)如图45所示表示。

[0564]

7.4字节流

[0565]

为了使用以s.e.m或s.b.q格式表示的多个数值,需要清楚对应于每个数值的数字格式信息。在单个类型的情况下,即使当数值是连续的时,也可以不改变地截取字长。然而,在多种类型的情况下,只有在掌握了变化点之后才能分离字长,并且在确认了每个数字格式信息之后才能确定字长。当数字格式信息被赋予所有数值时,可以每次确定字长,但通过量化压缩的数据被放大。

[0566]

因此,本实施例提出了以下所示的三种类型的字节流,它们可以以恒定成本将它们分离的状态来表示,而不会将连续数字格式信息和数值之间的关联赋予所有。注意,后面

例示的字节流的结构仅仅是示例,可以进行各种修改。

[0567]-按基本结构和连续结构分组的字节流

[0568]-按扩展结构分组的字节流

[0569]-按自定义扩展结构的分组报头的有效载荷可变长度流

[0570]

7.4.1按基本结构(基本结构)和连续结构(连续结构)分组的字节流

[0571]

字节流的头部总是以恒定字节大小为单位对齐的基本结构(基本结构)开始。这种恒定大小的数据称为分组。分组的报头部分(以下称为分组报头)包括以下描述的元素。

[0572]-连续确定标识符(连续)

[0573]

连续确定标识符(连续)是指示是否重复使用紧接之前指定的数字格式信息的标识符。

[0574]-数字格式信息(数字格式信息)

[0575]

数字格式信息(数字格式信息)是指示数字格式信息是s.e.m格式和s.b.q格式中的哪一种的信息。

[0576]-数值数据的数量(数量)

[0577]

数值数据的数量(数量)指示要存储在有效载荷中的数值数据的数量。

[0578]-有效载荷区域(有效载荷)

[0579]

有效载荷区域(有效载荷)指示存储数值数据的区域。允许此有效载荷区域(有效载荷)不存在于根据其他标识符对齐的字节大小内。

[0580]-数值数据(数值数据)

[0581]

数值数据(数值数据)是以s.e.m格式或s.b.q格式指定的数值的主体。这个数值数据(数值数据)存储在有效载荷中,并且未使用的区域通过填充来填充。注意,通过填充来填充的区域并不限于紧接在分组报头之后的区域。例如,可以紧接在分组报头之后继续数值数据(数值数据),并且剩余的区域可以通过填充来填充。这同样适用于后面例示的字节流。

[0582]-报头跳过标识符(跳过报头)

[0583]

报头跳过标识符(跳过报头)是用于确定是否将下一对齐数据处理为无报头的有效载荷的标识符。

[0584]-自定义标识符(自定义)

[0585]

自定义标识符(自定义)是指示是否将分组报头处理为自定义格式的标识符。当确认自定义标识符(自定义)为有效值时,根据该值切换分组解释方法。

[0586]

图46和图47是示出可以通过基本结构(基本结构)实现的两个基本结构示例的图。具体地,图46示出了其中连续确定标识符是“不连续的”的基本结构(基本结构),图47示出了其中连续确定标识符是“连续的”的连续结构(连续结构)。

[0587]

如图46所示,在基本结构(基本结构)中,在连续确定标识符为“不连续”并且报头跳过标识符指示“不跳过”的情况下,由数值数据的数量指示的数字格式信息指定的数值的数量被存储在剩余的有效载荷区域(有效载荷)中。尽管可以存储在分组本身中的数值数据段的数量很少,但当与随后的连续数值保存相同的格式时,具有连续结构的分组报头是有用的。

[0588]

如图47所示,在连续确定标识符为“连续”的连续结构(连续结构)的分组报头中,仅通过输入数值数据的个数,就可以连续地将数值数据存储在有效载荷中直到随后的对

齐。

[0589]

当切换格式时,通过将连续确定标识符指定为“不连续”并放置基本结构的分组,可以切换到另一格式。因此,可以通过以恒定字节大小为单位执行处理来分离数值数据。

[0590]

利用上述结构,可以执行关联,而不需要确保复杂的字节流解析处理或等于或大于对齐大小的临时保存区域,也不需要向所有数值传递数字格式信息。

[0591]

7.4.2按扩展结构(扩展结构)分组的字节流

[0592]

在按扩展结构(扩展结构)分组的字节流中,当连续确定标识符为“不连续”并且在基本结构的分组报头中报头跳过标识符被指定为“跳过”时,以下描述的两个元素被视为扩展信息,并且直到下一对齐单元的字节大小的整个分组被视为有效载荷区域(有效载荷)。

[0593]-有效载荷的重复次数(有效载荷递归次数)

[0594]

有效载荷的重复次数(有效载荷递归次数)表示当下一个对齐单元用作有效载荷时,对齐单元的有效载荷重复了多少次。由于在指定数量的对齐单元的字节大小之后再次描述包括分组报头的分组,因此在这一点上可以切换格式。

[0595]-保留区域(保留)

[0596]

保留区域(保留)是预备区域。

[0597]

图48和图49示出了这种扩展结构(扩展结构)的分组和仅作为有效载荷对齐的分组的结构。图48示出了扩展结构(扩展结构)的分组的结构,并且图49示出了仅作为有效载荷对齐的分组的结构。如图49所示,在整个有效载荷的字节大小可以除以数值数据的字长的情况下、在连续结构中留下大剩余区域的情况下等,只有有效载荷而没有报头的分组是有用的。

[0598]

通过使用上述结构,与基本结构(基本结构)类似,可以保存数值数据,而不需要确保复杂的字节流解析处理或等于或大于对齐大小的临时保存区域,也不需要向所有数值传递数字格式信息。

[0599]

7.4.3按自定义扩展结构(自定义结构)的分组报头的有效载荷可变长度流

[0600]

在按自定义扩展结构(自定义结构)的分组报头的有效载荷可变长度流中,类似于该扩展结构的分组报头,在连续性确定标识符为“不连续”的情况下,将头部跳过标识符指定为“跳过”,并且将自定义标识符指定为“有效”,允许替换在基本结构中定义的分组报头的一部分,并且仅将以下描述的三种类型的位置和含义与基本结构的分组报头同等对待。

[0601]-连续确定标识符(连续)

[0602]-报头跳过标识符(跳过报头)

[0603]-自定义标识符(自定义)

[0604]

此外,在自定义扩展结构(自定义结构)中,除了上面所述的信息之外,还添加了以下信息。

[0605]-版本号(版本)

[0606]

版本号(版本)由数值指示,并指示自定义扩展结构(自定义结构)的类型。数值0保存以下作为有效载荷大小扩展描述的四个元素的信息。

[0607]-有效载荷大小(有效载荷大小)

[0608]

有效载荷大小(有效载荷大小)指示分组报头之后的有效载荷的大小。在自定义扩展结构(自定义结构)中,允许大小与在前面的结构中指示的分组报头的字节大小不相同。

[0609]-数字格式信息(数字格式信息)

[0610]

数字格式信息(数字格式信息)可以等效于基本结构(基本结构)中的数字格式信息(数字格式信息)。

[0611]-数值数据的数量(数量)

[0612]

数值数据的数量(数量)可以等效于基本结构(基本结构)中的数值数据的数量(数量)。

[0613]-有效载荷的重复次数(有效载荷递归次数)

[0614]

有效载荷的重复次数(有效载荷递归次数)可以与扩展结构(扩展结构)中有效载荷的重复次数(有效载荷递归次数)相同。

[0615]

在图50和图51中示出了该自定义扩展结构(自定义结构)的报头和有效载荷的示例。图50示出了自定义扩展结构(自定义结构)的报头的示例,并且图51示出了自定义扩展结构(自定义结构)的有效载荷的示例。

[0616]

与上述基本结构(基本结构)和扩展结构(扩展结构)不同,在自定义扩展结构(自定义结构)中,对字节流的解析处理变得复杂,并且需要在将有效载荷分离到由有效载荷大小指示的大小之前增加必要的临时保存区域,但是可以用在有效载荷中填充的数值比在扩展结构中填充的数值更多地保存有效载荷。

[0617]

这种自定义扩展结构(自定义结构)通过改变版本号并将其用作开发示例,为在有效载荷部分中存储除数值以外的信息留出了空间,并且还可以在字节流中嵌入诸如数值运算方法的附加信息。

[0618]

7.5字节流的实施示例

[0619]

接下来,下面将参考附图详细描述上述三种类型的字节流的具体实施示例。注意,在下面描述的描述中,将描述以s.b.q格式实施的示例。

[0620]

7.5.1基本结构(基本结构)和连续结构(连续结构)的字节流实施示例

[0621]

图52和图53是示出基本结构(基本结构)的字节流实施示例的图。图52示出了基本结构(基本结构)的分组,并且图53示出了连续结构(连续结构)的分组。

[0622]

如图52所示,基本结构(基本结构)的分组包括,例如,从左端msb(最高有效位)开始,1位连续确定标识符(在附图中,表示为

′

连续’)、2位数值数据数(在附图中,表示为

′

数字

′

)、1位报头跳过标识符(在附图中,表示为

′

跳过报头

′

)、1位自定义标识符(在附图中,表示为

′

自定义

′

)、1位s(符号信息)(在附图中,表示为

′

符号

′

)、4位b(数值数据位宽)(在附图中,表示为

′b′

)、3位q(在附图中,表示为

′q′

)、19位有效载荷区域(有效载荷)(在附图中,表示为

′

有效载荷

′

)。

[0623]

例如,1位连续确定标识符(连续)指示当值为

′1′

时在分组中包括新的格式报头,并且指示当值为

′0′

时使用前一分组的格式报头。

[0624]

例如,当数值数据(数字)的2位数字的值为

′

01

′

时,指示在分组的有效载荷区域(有效载荷)中存储了一段数值数据,当值为

′

10

′

时,指示存储了两段数值数据,并且当值为

′

11

′

时,指示存储了三段数值数据。注意,在

′

00

′

的情况下,指示分组中没有存储数值数据。

[0625]

例如,在1位报头跳过标识符(跳过报头)的值为

′1′

的情况下,指示下一个对齐数据被视为没有报头的有效载荷区域(有效载荷),并且当值为

′0′

时,指示下一个对齐数据被

视为不连续的新分组。

[0626]

例如,当1位自定义标识符(自定义)的值为

′0′

时,指示分组被视为普通格式的分组,并且当值为

′1′

时,指示分组被视为自定义格式的分组。也就是说,当自定义标识符(自定义)为

′1′

时,切换用于解释分组的方法。

[0627]

另一方面,如图53所示,连续结构(连续结构)的分组从左端msb开始依次包括1位连续确定标识符(在附图中,表示为“连续”)、2位数值数据的数量(在附图中,表示为“数字”)和29位有效载荷区域(有效载荷)(在附图中,表示为“有效载荷”)。

[0628]

连续确定标识符(连续)、数值数据的数量(数字)和有效载荷区域(有效载荷)可以类似于参考图53描述的那些。

[0629]

7.5.2扩展结构(扩展结构)的字节流实施示例

[0630]

图54和图55是示出扩展结构(扩展结构)的字节流实施示例的图。图54示出了扩展结构(扩展结构)的分组,并且图55示出了仅连续有效载荷区域(有效载荷)的分组。

[0631]

如图54所示,在扩展结构(扩展结构)的分组中,例如,在与图52所示的基本结构(基本结构)的分组的结构相似的结构中,19位有效载荷区域(有效载荷)被11位保留区域(在附图中,表示为“保留”)和8位有效载荷重复次数(在附图中,表示为“有效载荷递归次数”)替换。例如,在不使用保留区域(保留)的情况下,可以通过零填充来填充该区域。

[0632]

另一方面,如图55所示,例如,仅有效载荷区域(有效载荷)的分组包括32位有效载荷区域(在附图中,表示为“有效载荷”)。

[0633]

7.5.3自定义结构(自定义结构)的字节流实施示例

[0634]

图56和图57是示出自定义结构(自定义结构)的字节流实施示例的图。图56示出了自定义结构(自定义结构)的分组,并且图57的(a)至(c)示出了仅连续有效载荷区域(有效载荷)的分组。

[0635]

如图56所示,例如,自定义结构(自定义结构)的分组在与图52所示的基本结构(基本结构)的分组相似的结构中具有这样的结构,其中,数值数据的数量(在附图中,表示为

′

数字

′

)被移动到s.b.q格式部分的下一个,相反,版本号(在附图中,表示为

′

版本

′

)被布置在连续确定标识符(连续)和报头跳过标识符(跳过报头)之间,并且有效载荷大小(在附图中,表示为

′

有效载荷大小

′

)被添加在自定义标识符(自定义)和s.b.q格式部分之间。此外,19位有效载荷区域(有效载荷)被上述6位数值数据的数量(

′

数字

′

)和8位有效载荷重复次数(在附图中,表示为

‘

有效载荷递归次数

′

)替换。

[0636]

另一方面,如图57所示,对于自定义结构(自定义结构)的分组,仅有效载荷区域(有效载荷)的分组继续到由有效载荷大小(有效载荷大小)指定的大小。因此,配置了按自定义扩展结构的分组报头的有效载荷可变长度流。

[0637]

其他配置、运算和效果可以类似于上述基础技术或实施例的配置、运算和效果,因此这里将省略其详细描述。

[0638]

7.6字节流处理系统的配置示例

[0639]

图58是示出根据本实施例的处理字节流的系统的示意性配置示例的框图。注意,在附图中,实线箭头指示基本结构(基本结构)、连续结构(连续结构)、扩展结构(扩展结构)和自定义结构(自定义结构)中的数据流和控制命令流,并且虚线箭头指示可以在自定义结构(自定义结构)中扩展和处理的扩展示例的数据流和控制命令流。此外,单点虚线箭头指

示来自系统外部的指令或命令,并且双点虚线箭头指示可以在自定义结构(自定义结构)中扩展和处理的扩展示例的来自系统外部的指令或命令。

[0640]

如图58所示,处理系统4000包括幂表达式转换单元4003、存储/转换单元4004、输入特征图存储器4005、系数存储器4006、分析单元4007、提取单元4008、幂表达式转换单元4009、运算控制单元4010、运算器阵列4011、幂表达式转换单元4013、存储/转换单元4014和输出特征图存储器4015。

[0641]

(幂表达式转换单元4003)

[0642]

例如,幂表达式转换单元4003是与上述实施例中的幂表达式转换单元2001和2102相对应的配置,并且使用从乘法单元2002/2104等输入的系数4002将经由传感器i/f4001输入的值转换为2的幂的表达式。注意,作为传感器i/f4001,除了图像传感器、飞行时间(tof)传感器等之外,还可以应用获取可转换为数值数据的测量值的各种传感器,例如麦克风,测量诸如大气压力、温度、湿度和风速等天气信息的各种传感器等。

[0643]

(存储/转换单元4004)

[0644]

存储/转换单元4004被配置为将值存储在容器中或将该值转换为字节流。存储/转换单元4004根据从高阶装置输入的运算控制命令和存储/转换方法的指令,构造存储从传感器i/f4001或幂表达式转换单元4003输入的数字表达式或运算控制命令的字节流。注意,构造的字节流包括上述基本结构(基本结构)、连续结构(连续结构)、扩展结构(扩展结构)和自定义结构(自定义结构)的字节流。此外,例如,运算控制命令可以包括,指定将由后面将描述的运算器阵列4011的积和运算电路4012使用的值表。

[0645]

(输入特征图存储器4005)输入特征图存储器4005是与上述实施例中的变量缓冲器2003相对应的配置,并且存储由存储/转换单元4004构造的字节流。因此,2的幂的表达式的变量存储在输入特征图存储器4005中。

[0646]

(系数存储器4006)

[0647]

系数存储器4006是与上述实施例中的系数存储器2004相对应的配置,并且存储从存储/转换单元4004输入的2的幂的表达式的系数。

[0648]

(分析单元4007)

[0649]

分析单元4007解析(分析)从输入特征图存储器4005读取的字节流,并从其他信息中分离有效载荷区域(有效载荷)。

[0650]

(提取单元4008)

[0651]

提取单元4008提取容器中的实际数据的组合。具体地,从容器中提取诸如s.e.m格式和s.b.q格式的数字格式信息和容器中的数值表达式(数值数据)。

[0652]

此外,在自定义结构(自定义结构)的字节流中指定了预定版本号(版本)的情况下,提取单元4008从字节流中提取除幂表达式或控制命令之外的数值。例如,提取单元4008提取数值运算方法(运算控制命令)、数值类型(浮点类型等)、数值的实际数据等。

[0653]

(幂表达式转换单元4009)

[0654]

幂表达式转换单元4009是与上述实施例中的幂表达式转换单元2001和2102相对应的配置,并且将从提取单元4008输入的其他数值表达式的数值转换为幂表达式的数值。

[0655]

(运算控制单元4010)

[0656]

运算控制单元4010基于嵌入在预定版本号(版本)的自定义结构(自定义结构)的

字节流中的运算控制命令,向运算器阵列4011输出控制命令。

[0657]

(运算器阵列4011)

[0658]

例如,运算器阵列4011是包括上述实施例中的积和运算电路4012的配置,并且对输入的幂表达式的数值、另一数值表达式的数值等执行预定的运算处理。

[0659]

(幂表达式转换单元4013)

[0660]

幂表达式转换单元4013是与上述实施例中的幂表达式转换单元2001和2102相对应的配置,并且转换从运算器阵列4011输入的幂表达式的数值。

[0661]

(存储/转换单元4014)

[0662]

与存储/转换单元4004类似,存储/转换单元4014是执行容器中的值的存储或字节流的转换的配置,并且根据从高阶装置输入的运算控制命令或存储/转换方法的指令,构造存储从幂表达式转换单元4013或运算器阵列4011输入的数字表达式或运算控制命令的字节流。注意,构造的字节流包括上述基本结构(基本结构)、连续结构(连续结构)、扩展结构(扩展结构)和自定义结构(自定义结构)的字节流。

[0663]

(输出特征图存储器4015)

[0664]

输出特征图存储器4015是与上述实施例中的运算结果缓冲器2005相对应的配置,并且存储由存储/转换单元4014构造的字节流。注意,在输出特征图存储器4015中存储的输出特征图可以作为输入特征图被重新输入到分析单元4007。

[0665]

注意,图58中所示的部分或全部单元可以通过硬件或软件来实现。此外,在图58所示的配置中,可以适当地缓冲每个单元的输出。

[0666]

7.7运算和效果

[0667]

如上所述,根据本实施例,可以通过容器和数字格式信息对应用于cnn/dnn的每个层和/或每个图采用不同的数字表达式设置。

[0668]

例如,可以采用这样的数值表达式,其中,对于指向dnn/cnn的2的幂的表达式,可以独立地设置正/负符号、精度、动态范围等。

[0669]

此外,可以采用容器和数字格式信息的组合,其单元为对每个特定单元(层、图等)不同的数字表达式设置。

[0670]

此外,通过将字长信息合并到数字表达式的格式中,可以省略字长获取的计算,从而可以降低运算成本。

[0671]

此外,字节流格式的使用使得有可能在比dnn的每一层和/或图更细的单位中采用不同的数值表达式设置。例如,可以实现以诸如行单位和像素单位等更细的单位高效地切换数值表达式设置的字节流格式。

[0672]

其他配置、运算和效果可以类似于上述基础技术或实施例的配置、运算和效果,因此这里将省略其详细描述。

[0673]

8.通信技术应用示例

[0674]

接下来,将描述根据本公开的量化方法在其他领域的应用。在上述描述中,已经描述了将根据本公开的量化方法应用于与神经网络的前向传播相关的内积运算的情况。另一方面,根据本公开的量化方法不限于以上示例,并且可以应用于用于执行内积运算的各种技术。

[0675]

例如,根据本公开的量化方法可以应用于通信技术领域中使用的带通滤波器中的

卷积运算。下面将描述当根据本公开的量化方法应用于带通滤波器时的仿真结果。

[0676]

图59是示出当根据本公开的量化方法应用于带通滤波器时关于频率特征(增益特征)的仿真结果的图。这里,在根升余弦(rrc)滤波器中的系数(63tap,滚降0.5)被量化。

[0677]

注意,对于量化,使用了32个值(0到31),其中p=2、3和4。在附图中,示出了dnn(p,32)。此外,作为比较,示出了在使用浮点(浮点)和整数(线性)的情况下的仿真结果。

[0678]

这里,参考图59,可以看出,即使当应用根据本公开的量化方法时,带通中的平坦度特征也不会劣化。另一方面,聚焦于边带,即使在dnn(2,32)的情况下,也可能有约-25db的衰减,可以看出衰减的影响随着p的增加而增加。注意,量化的影响期望通过例如与低通滤波器(lpf)的组合进一步减小。

[0679]

此外,图60是示出当根据本公开的量化方法应用于带通滤波器时关于相位特征的仿真结果的图。参考图60,可以看出,即使当应用根据本公开的量化方法时,也不能确认通带中的相位旋转,即相位特征的劣化。如上所述,由于根据本公开的量化方法不会显著劣化带通滤波器的频率特征,因此可以说根据本公开的量化方法也充分适用于通信技术领域。

[0680]

此外,为了进一步研究根据本公开的量化方法的影响,通过误码率(ber)执行评估。图61是根据本公开的用于ber评估的框图。

[0681]

如图61所示,在该评估中,通过在解调之前在模数转换器(adc)和rrc滤波器中应用浮点、整数和dnn(p,32)来测量ber。此外,bpsk、qpsk和16qam用于调制和解调方法。

[0682]

图62是示出当bpsk用于调制方法时的ber评估结果的图。此外,图63是图62中的snr7至9db的数据的放大图。参考图62和图63,可以看出,当使用bpsk作为调制方法时,在p=4的情况下完全没有观察到ber的劣化,即使在p=2或3的情况下,ber也没有很大的影响。

[0683]

图64是示出当qpsk用于调制方法时的ber评估结果的图。此外,图65是图64中的snr10至12db的数据的放大图。参考图64和图65,可以看出,同样在使用qpsk作为调制方法的情况下,类似于使用bpsk的情况,具有p=2或3的量化对ber影响不大。

[0684]

图66是示出当16qam用于调制方法时的ber评估结果的图。此外,图67是图66中的snr16至18db的数据的放大图。参考图66和图67,在使用16qam作为调制方法的情况下,可以看到,在p=2或3的量化中,ber增加,但在p=4的量化中,ber的劣化没有得到确认。

[0685]

如上所述,当使用bpsk或qpsk作为调制方法时,可以说,不管p的值如何,根据本公开的量化方法都是有效的。此外,当采用16qam作为调制方式时,认为当p≥4时不影响ber。

[0686]

如上所述,根据本公开的量化方法在通信技术领域中也是有效的,并且可以实现性能的维护和处理负载的降低。

[0687]

9.硬件配置示例

[0688]

接下来,将描述根据本公开的实施例的信息处理装置10的硬件配置示例。图68是示出根据本公开的实施例的信息处理装置10的硬件配置示例的框图。参考图68,例如,信息处理装置10包括cpu 871、rom 872、ram 873、主机总线874、桥接器875、外部总线876、接口877、输入装置878、输出装置879、存储器880、驱动器881、连接端口882和通信装置883。注意,这里所示的硬件配置是示例,并且可以省略一些部件。此外,可进一步包括这里所示的部件以外的部件。

[0689]

(cpu 871)

[0690]

例如,cpu 871用作运算处理装置或控制装置,并基于记录在rom872、ram873、存储

器880或可移动记录介质901中的各种程序来控制每个部件或其一部分的整体运算。

[0691]

(rom 872、ram 873)

[0692]

rom872是存储由cpu 871读取的程序、用于运算的数据等的装置。ram873暂时或永久地存储例如由cpu 871读取的程序、当执行该程序时适当地改变的各种参数等。

[0693]

(主机总线874、桥接器875、外部总线876、接口877)

[0694]

例如,cpu871、rom872和ram 873经由能够高速数据传输的主机总线874相互连接。另一方面,例如,主机总线874经由桥接器875连接到具有相对较低数据传输速度的外部总线876。此外,外部总线876经由接口877连接到各种部件。

[0695]

(输入装置878)

[0696]

例如,使用鼠标、键盘、触摸面板、按钮、开关、控制杆等作为输入装置878。此外,作为输入装置878,可以使用能够使用红外线或其他无线电波发送控制信号的遥控器(以下,遥控器)。此外,输入装置878包括诸如麦克风的语音输入装置。

[0697]

(输出装置879)

[0698]

输出装置879是能够通过视觉或听觉向用户通知获取的信息的装置,例如,诸如阴极射线管(crt)、lcd或有机el的显示装置、诸如扬声器或耳机的音频输出装置、打印机、移动电话、传真机等。此外,根据本公开的输出装置879包括能够输出触觉刺激的各种振动设备。

[0699]

(存储器880)

[0700]

存储器880是用于存储各种数据的装置。例如,使用诸如硬盘驱动器(hdd)、半导体存储设备、光存储设备、磁光存储设备等的磁存储设备作为存储器880。

[0701]

(驱动器881)

[0702]

例如,驱动器881是读取记录在诸如磁盘、光盘、磁光盘或半导体存储器等可移动记录介质901上的信息或将信息写入可移动记录介质901上的装置。

[0703]

(可移动记录介质901)

[0704]

例如,可移动记录介质901是dvd介质、蓝光(注册商标)介质、hd dvd介质、各种半导体存储介质等。当然,可移动记录介质901可以是例如其上安装有非接触ic芯片的ic卡、电子设备等。

[0705]

(连接端口882)

[0706]

连接端口882是用于连接外部连接设备902的端口,例如通用串行总线(usb)端口、ieee1394端口、小型计算机系统接口(scsi)、rs-232c端口或光音频终端。

[0707]

(外部连接设备902)

[0708]

例如,外部连接的设备902是打印机、便携式音乐播放器、数码相机、数码摄像机、ic记录器等。

[0709]

(通信装置883)

[0710]

通信装置883是用于连接到网络的通信设备,并且例如是用于有线或无线lan、蓝牙(注册商标)或无线usb(wusb)的通信卡、用于光通信的路由器、用于非对称数字用户线(adsl)的路由器、用于各种通信的调制解调器等。

[0711]

尽管上文已经描述了本公开的实施例,但本公开的技术范围不限于目前的上述实施例,并且可以在不脱离本公开的主旨的情况下进行各种修改。此外,可以适当地组合不同

实施例和变型示例的部件件。

[0712]

此外,本说明书中描述的实施例的效果仅是示例而非限制性的,并且可以存在其他效果。

[0713]

注意,本技术也可以具有以下配置。

[0714]

(1)

[0715]

一种信息处理装置,包括:

[0716]

积和运算电路,被配置为基于由幂表达式量化的多个输入值和与各个输入值相对应的由幂表达式量化的多个加权系数来执行积和运算,

[0717]

其中,每个输入值的指数由分母中具有预定除数的分数表示,

[0718]

每个加权系数的指数由分母中具有所述除数的分数表示,

[0719]

积和运算电路使用基于余数的多个加法乘数执行积和运算,余数是进行以通过将与每个输入值的所述指数相关的分子和与每个加权系数的指数相关的分子相加而获得的值为被除数的除法时的余数,并且

[0720]

每个加法乘数都是指数部分的基数为2的浮点数。

[0721]

(2)

[0722]

根据(1)所述的信息处理装置,还包括:存储单元,被配置为保存所述多个加法乘数。

[0723]

(3)

[0724]

根据(2)所述的信息处理装置,还包括:运算器,被配置为基于通过将所述除法的商转换为整数而获得的值,对存储在所述存储单元中的所述加法乘数执行2的幂运算。

[0725]

(4)

[0726]

根据(3)或(4)所述的信息处理装置,其中,基于与每个输入值的所述指数相关的所述分子的字长、与每个加权系数的所述指数相关的所述分子的字长和所述预定除数,确定所述运算器中浮点数的指数部分的字长。

[0727]

(5)

[0728]

根据(3)或(4)所述的信息处理装置,其中,所述运算器对基数为2的浮点数的所述指数部分执行加法或减法。

[0729]

(6)

[0730]

根据(2)所述的信息处理装置,其中

[0731]

所述存储单元包括:

[0732]

存储电路组,包括多个可重写存储电路;

[0733]

存储器,保存多个第一加法乘数和与所述多个第一加法乘数不同的多个第二加法乘数;以及

[0734]

选择器,选择性地将保存在所述存储器中的所述多个第一加法乘数和所述多个第二加法乘数中的一者写入所述存储电路组。

[0735]

(7)

[0736]

根据(2)所述的信息处理装置,其中

[0737]

所述存储单元包括:

[0738]

第一存储电路组,保存多个第一加法乘数;

[0739]

第二存储电路组,保存与所述多个第一加法乘数不同的多个第二加法乘数;以及

[0740]

选择器,将连接到所述积和运算电路的存储电路组切换到所述第一存储电路组和所述第二存储电路组中的任一者。

[0741]

(8)

[0742]

根据(6)或(7)所述的信息处理装置,其中

[0743]

所述多个第一加法乘数是用2的幂表示的值,以及

[0744]

所述多个第二加法乘数是线性表示的值。

[0745]

(9)

[0746]

根据(2)所述的信息处理装置,其中,所述存储单元保存所述多个加法乘数和通过沿着2的幂的表达式的表达式函数对所述多个加法乘数中的每个加法乘数进行0.5舍入而获得的值。

[0747]

(10)

[0748]

一种信息处理系统,包括:

[0749]

分析单元,被配置为分析字节流;

[0750]

运算器阵列,包括积和运算电路,所述积和运算电路基于由幂表达式量化的多个输入值和与所述各个输入值相对应的由幂表达式量化的多个加权系数来执行积和运算;以及

[0751]

运算控制单元,被配置为基于所述分析单元的分析结果来控制所述运算器阵列,

[0752]

其中,所述运算器阵列还包括存储单元,所述存储单元保存多个加法乘数,

[0753]

所述存储单元包括:

[0754]

第一存储电路组,保存多个第一加法乘数;

[0755]

第二存储电路组,保存与所述多个第一加法乘数不同的多个第二加法乘数;以及

[0756]

选择器,将连接到所述积和运算电路的存储电路组切换到所述第一存储电路组和所述第二存储电路组中的任一者,

[0757]

所述字节流包括在所述积和运算中使用的存储电路组的指定,

[0758]

所述运算控制单元基于所述指定控制所述选择器,

[0759]

每个输入值的指数由分母中具有预定除数的分数表示,

[0760]

每个加权系数的指数由分母中具有所述除数的分数表示,

[0761]

所述积和运算电路使用基于余数的多个加法乘数执行所述积和运算,所述余数是进行以通过将与每个输入值的所述指数相关的分子和与每个加权系数的指数相关的分子相加而获得的值为被除数的除法时的余数,并且

[0762]

每个加法乘数都是指数部分的基数为2的浮点数。

[0763]

(11)

[0764]

一种由信息处理系统执行的信息处理方法,包括:分析单元,被配置为分析字节流;运算器阵列,包括积和运算电路,所述积和运算电路基于由幂表达式量化的多个输入值和与所述各个输入值相对应的由幂表达式量化的多个加权系数来执行积和运算;以及运算控制单元,被配置为基于所述分析单元的分析结果来控制所述运算器阵列,其中,所述运算器阵列还包括存储单元,所述存储单元保存多个加法乘数,所述存储单元包括:第一存储电路组,保存多个第一加法乘数;第二存储电路组,保存与所述多个第一加法乘数不同的多个

第二加法乘数;以及选择器,将连接到所述积和运算电路的存储电路组切换到所述第一存储电路组和所述第二存储电路组中的任一者,所述积和运算电路使用基于余数的多个加法乘数执行所述积和运算,所述余数是进行以通过将与每个输入值的所述指数相关的分子和与每个加权系数的指数相关的分子相加而获得的值为被除数的除法时的余数,

[0765]

所述方法包括:

[0766]

由所述分析单元从所述字节流特定在所述积和运算中使用的存储电路组的指定;

[0767]

由所述运算控制单元基于所述指定控制所述选择器;以及

[0768]

由所述积和运算电路,使用经由所述选择器连接的存储电路组中保存的所述多个加法乘数执行所述积和运算,

[0769]

其中,每个输入值的所述指数由分母中具有预定除数的分数表示,

[0770]

每个加权系数的所述指数由分母中具有所述除数的分数表示,以及

[0771]

每个加法乘数都是指数部分的基数为2的浮点数。

[0772]

参考符号列表

[0773]

10 信息处理装置

[0774]

110 输入单元

[0775]

120 运算单元

[0776]

130 存储单元

[0777]

140 输出单元

[0778]

200、300、400、500 积和运算电路

[0779]

530、530a、530b 存储电路组

[0780]

1530 存储器

[0781]

1530a、1530b 表

[0782]

1531,1532 选择器

[0783]

2001,2102 幂表达式转换单元

[0784]

2002,2104 乘法单元

[0785]

2003 变量缓冲器

[0786]

2004 系数存储器

[0787]

2005 运算结果缓冲器

[0788]

2100 积和运算电路

[0789]

2101 积和运算单元

[0790]

2103 幂表达式表

[0791]

2202,2204 幂表达式转换表

[0792]

2203 幂表达式表

[0793]

3210 整数减法器

[0794]

3220 移位运算器

[0795]

3230 存储电路组

[0796]

3240 比较器组

[0797]

3250 优先级编码器

[0798]

3260 整数加法器

[0799]

3270 比较器

[0800]

3280 选择器

[0801]

3540 2的幂乘法运算器

[0802]

3560 浮点加法器-减法器

[0803]

4001 传感器i/f

[0804]

4002 系数

[0805]

4003,4009,4013 幂表达式转换单元

[0806]

4004,4014 存储/转换单元

[0807]

4005 输入特征图存储器

[0808]

4006 系数存储器

[0809]

4007 分析单元

[0810]

4008 提取单元

[0811]

4010 运算控制单元

[0812]

4011 运算器阵列

[0813]

4015 输出特征图存储器。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。