finfet半导体设备

1.优先权要求

2.本专利申请要求于2019年7月30日提交的题为“finfet半导体设备”的申请号16/526,756的优先权,该专利申请已转让给本技术的受让人并且在此通过引用明确并入本文。

技术领域

3.所公开的主题涉及半导体设备。在一些方面中,所公开的主题涉及金属氧化物半导体场效应晶体管(mosfet)半导体设备,包括具有长沟道晶体管和短沟道晶体管的鳍片型场效应晶体管(finfet)设备。

背景技术:

4.诸如mosfet设备之类的传统半导体设备的尺寸正在减小,以提高处理速度、降低功耗、减小设备尺寸和/或降低制造成本。对半导体设备提高性能和减小尺寸的需求导致了多栅极设备的使用。这些多栅极设备包括多栅极鳍片型场效应晶体管(finfet)。在finfet中,沟道被形成在从衬底延伸的“鳍片”上。finfet设备允许通过在包括沟道区域的鳍片的侧面和顶部提供栅极来减小设备的栅极宽度。

5.然而,尺寸减小会导致对包括本文中所讨论的mosfet设备和finfet在内的半导体设备的负面影响。使用具有finfet长沟道晶体管和短沟道晶体管的传统技术半导体设备可能无法针对每个晶体管类型(长沟道或短沟道)实现其期望的阈值电压(vt)。

6.因而,具有能够允许短沟道晶体管和长沟道晶体管两者实现其所需的vt的finfet设计可能是有利的。

技术实现要素:

7.本发明内容标识了一些示例方面的特征,并非对所公开的主题的排他性或详尽描述。特征或方面是否包括在本发明内容中或从该发明内容中省略并不旨在指示这些特征的相对重要性。在阅读以下具体实施方式并查看形成其一部分的附图时,描述了附加特征和方面,并且对于本领域技术人员而言,变得显而易见。

8.本公开的一个方面包括一种半导体设备,该半导体设备包括在衬底上的多个鳍片。长沟道栅极被设置在多个鳍片的第一部分上方。栅极接触具有栅极接触基底和从有源区域外部的栅极接触基底延伸到有源区域中的延伸部分。

9.本公开的另一方面包括一种制造半导体设备的方法。该方法包括:在衬底上形成多个鳍片。长沟道栅极被设置在多个鳍片的第一部分上方。栅极接触被形成为具有栅极接触基底和从有源区域外部的栅极接触基底延伸到有源区域中的延伸部分。

10.基于附图和详细描述,与本文中所公开的各方面相关联的其他目的和优点对于本领域技术人员而言是显而易见的。

附图说明

11.提供附图以帮助描述所公开的主题的一个或多个方面的示例,并且仅提供用于说明示例而不是对其进行限制。

12.图1是图示了传统短沟道与长沟道vt与目标值的差异的图表。

13.图2是图示了根据本公开的一个或多个方面的短沟道与长沟道vt与目标值的差异的图表。

14.图3是传统finfet的图示。

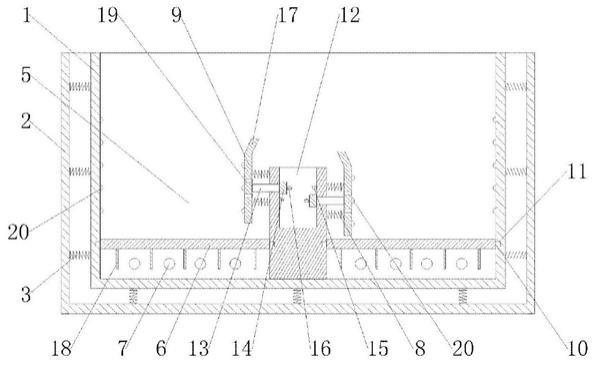

15.图4是根据本公开的一个或多个方面的finfet的图示。

16.图5是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。

17.图6是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。

18.图7是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。

19.图8是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。

20.图9是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。

21.图10是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。

22.图11是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。

23.图12是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。

24.图13是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。

25.图14是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。

26.图15是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。

27.图16图示了根据本公开的一个或多个方面的制造半导体设备的示例方法的流程图。

28.图17图示了其中集成了本公开的方面的示例设备。

29.图18图示了其中集成有本公开的各方面的设备的附加示例。

具体实施方式

30.在针对所公开的主题的具体示例的以下描述和相关附图中提供了主题的各方面。可以设计备选方案而不脱离所公开的主题的范围。附加地,不会对众所周知的元件进行详细描述或省略这些元件,以免混淆相关细节。

31.本文中使用单词“示例性”来意指“用作示例、实例或说明”。本文中被描述为“示例性”的任何方面不必被解释为优于或利于其他方面。同样,术语“方面”并不要求所有方面都包括所讨论的特征、优点或操作模式。

32.本文中所使用的术语仅描述特定方面并且不应被解释为限制本文中所公开的任何方面。如本文中所使用的,除非上下文另有明确指示,否则单数形式“一”、“一个”和“该”旨在也包括复数形式。本领域技术人员将进一步理解,如本文中所使用的术语“包括(comprises)”、“包括(comprising)”、“包含(includes)”和/或“包含(including)”指定了所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或多个其他特征、整数、步骤、操作、元件、部件和/或其组的存在或添加。

33.进一步地,可以根据要由例如计算设备的元件执行的动作序列来对各个方面进行描述。本领域技术人员将认识到,本文中所描述的各种动作可以由特定电路(例如,专用集

成电路(asic))、由一个或多个处理器执行的程序指令或由两者的组合来执行。附加地,本文中说描述的这些动作序列可以被认为完全体现在任何形式的非暂态计算机可读介质中,该非暂态计算机可读介质上存储有对应计算机指令集,这些计算机指令在执行时可能使得相关联的处理器执行本文中所描述的功能。因此,本文中所描述的各个方面可以以若干个不同形式体现,所有这些都被认为在所要求保护的主题的范围内。另外,对于本文中所描述的方面中的每个方面,任何此类方面的对应形式在本文中可以描述为例如“被配置为

……

的逻辑”和/或被配置为执行所描述的动作的其他结构部件。

34.进一步地,应当指出,术语“连接”、“耦合”或其任何变体表示元件之间的任何直接或间接的连接或耦合,并且可以涵盖在经由中间元件“连接”或“耦合”在一起的两个元件之间存在中间元件。还应当理解,除非另有说明,否则本文中所使用的“耦合”或“连接”意指电耦合或电连接。

35.如上文所指示的,传统电路设计的缺点包括不能针对短沟道晶体管和长沟道晶体管两者调整期望的vt。图1图示了传统短沟道与长沟道vt与目标值的差异。应当领会,传统finfet制造技术不能使用传统vt调谐技术(例如,调整well、halo和/或功函数(wf))满足短沟道晶体管(其可以用于逻辑电路)和长沟道晶体管(其可以用于模拟/射频(rf)电路)的目标vt。图1图示了具有短沟道和长沟道的7纳米节点技术的这一结果。x轴是具有不同vt类型和栅极长度的设备。例如,rvt_l8指示vt类型为规则电压阈值(rvt),栅极长度=8nm;lvt_l200指示vt类型为lvt低电压阈值(lvt),栅极长度=200nm;slvt_l8指示vt类型为超低电压阈值(svlt),栅极长度=8nm。如示例中所图示的,在7纳米技术(7nm)中,pmos设计的相对侧处的vt产生了vt低于目标约30mv至50mv的短沟道(sc)和vt高于目标约20mv至50mv的长沟道(lc)。传统vt调谐技术使vt沿相同方向移动,因此通过增加vt来实现sc设备可能会导致lc设备更远离目标vt。因而,传统vt调谐技术没有提供满足使用长沟道晶体管的模拟电路的vt的解决方案。

36.图2图示了根据本公开的一个或多个方面的短沟道与长沟道vt与目标值的差异。再次,示出了7nm技术中短沟道和长沟道的目标vt之间的差异。与图1所示的偏差相反,在图2中,pmos设计的vt产生了vt低于目标约10mv至20mv的短沟道(sc)设计和vt高于目标约10mv至20mv的长沟道(lc)设计,这对于传统设计是显著进步且在vt变化的期望范围(例如,-20mv至 20mv)内。在简要介绍传统设计之后,将在以下段落中对根据本公开的各个方面的finfet设计的细节进行描述。

37.图3是传统finfet半导体设备300的图示。传统fet设备通常是平面设备,其中设备的整个沟道区域平行形成并且略低于半导体衬底的上部平面表面。相比之下,finfet被认为是形成在半导体衬底上方的3d设备。如图3所示,根据平面视图,在短沟道(sc)设备310中,短沟道栅极314(sc栅极)与鳍片312重叠,该鳍片312可以由类似于衬底的材料(例如,硅,未图示)制成。鳍片312可以从衬底突出并且由鳍片312之间的多个鳍片形成沟槽隔开。sc设备310的栅极宽度正交于如短沟道栅极314所图示的栅极长度方向。由短沟道栅极314覆盖的鳍片312的各部分是sc设备310的沟道区域。鳍片312的位于短沟道栅极314外部的部分是源极/漏极区域并且通常被认为是sc设备310的有源区域318。栅极接触316被设置在位于有源区域318外部的短沟道栅极314的一端处。

38.同样,如图3所示,长沟道(lc)设备320包括与鳍片322重叠的长沟道栅极324(lc栅

极),该鳍片322可以由类似于衬底的材料(例如,硅,未图示)制成。鳍片322可以从衬底突出并且通过鳍片322之间的多个鳍片形成沟槽隔开。lc设备320的栅极宽度正交于如长沟道栅极324所图示的栅极长度方向。由长沟道栅极324覆盖的鳍片322的各部分是lc设备320的沟道区域。鳍片322的位于长沟道栅极324外部的部分为lc设备320的源极/漏极区域,并且通常被认为是lc设备320的有源区域328。栅极接触326被设置在位于有源区域328外部的长沟道栅极324的一端处。

39.如上文所指出的,finfet设备可以被形成具有不同的沟道长度(临界尺寸)和不同的阈值电压(vt),使得finfet设备展现出不同的特点,这些特点允许集成电路具有以不同特点表现的晶体管。例如,在一些应用中,集成电路设计有多个短沟道设备和多个长沟道设备,诸如如图3和图4所示。长沟道设备的临界尺寸或沟道长度通常大于短沟道设备的沟道长度或临界尺寸,并且短沟道设备的阈值电压(vt)通常小于长沟道设备的阈值电压。相反,短沟道设备的关态漏电流通常大于长沟道设备的关态漏电流。一般而言,相对于长沟道设备,短沟道设备展现出更快的开关速度和更高的关态漏电流。短沟道设备经常用于期望晶体管的快速开关速度的集成电路的逻辑部分中。相比之下,长沟道设备可以用于晶体管的开关速度不如其展现出低关态漏电流的能力重要的电路中。例如,长沟道设备可以用于模拟部分、rf部分和/或用于输入/输出电路。

40.图4是根据本公开的一个或多个方面的finfet的图示。如所图示的,根据平面图,半导体设备400可以包括一个或多个短沟道(sc)finfet设备410和/或一个或多个长沟道(lc)finfet设备420。在短沟道(sc)finfet设备410中,短沟道栅极414(sc栅极)与鳍片412重叠,该鳍片412可以由类似于衬底(未图示)的材料制成。在一些方面中,衬底可以是块状半导体衬底或绝缘体上硅(soi)衬底,并且可以由以下各项中的至少一项形成:硅、锗、硅-锗合金、碳掺杂硅、碳掺杂硅-锗合金、砷化镓、磷化铟或任何其他传统半导体衬底。鳍片412可以从衬底突出,并且由鳍片412之间的多个鳍片形成沟槽隔开。提供三个鳍片412仅用于说明,并且可以提供更多或更少个鳍片。同样,提供两个sc栅极414仅用于说明,并且栅极的数目可以更多或更少。sc finfet设备410的栅极宽度正交于由短沟道栅极414所图示的栅极长度方向“l”。鳍片412的由短沟道栅极414覆盖的部分为sc finfet设备410的沟道区域。鳍片412位于短沟道栅极414外部的部分为源极/漏极区域,并且通常被认为是sc finfet设备410的有源区域418。栅极接触416被设置在短沟道栅极414位于有源区域418外部的一端。应当领会,sc finfet设备410与sc设备310相似。

41.同样,如图4所图示的,半导体设备400可以包括长沟道(lc)finfet设备420,包括与鳍片422重叠的长沟道栅极424(lc栅极),该鳍片422可以由类似于衬底的材料(例如,硅,未图示)制成。鳍片422可以从衬底突出并且由鳍片422之间的多个鳍片形成沟槽隔开。提供三个鳍片422仅用于说明,并且可以提供更多或更少个鳍片。同样,提供两个lc栅极424仅用于说明,并且栅极的数目可以更多或更少。lc finfet设备420的栅极宽度正交于由长沟道栅极424所图示的栅极长度方向。鳍片422的由长沟道栅极424覆盖的部分为lc设备420的沟道区域。鳍片422的位于短沟道栅极424外部的部分为lc finfet设备420的源极/漏极区域,并且通常被认为是lc finfet设备420的有源区域428。栅极接触425包括栅极接触基底426,该栅极接触基底426被设置在长沟道栅极424位于有源区域428外部的一端处,并且还包括延伸部分427,该延伸部分427延伸到finfet设备420的有源区域428(例如,具有鳍片的区

域、源极/漏极)中。

42.在一些方面中,延伸部分427延伸超出鳍片422。应当领会,由于延伸部分427必须维持与有源区域428分离,以避免对有源区域428的潜在短路或过度泄漏,所以延伸部分427可以具有与栅极接触基底426不同的尺寸。在一些方面中,栅极接触基底426的长度(l)在30nm至300nm范围内且厚度/高度在10nm至50nm范围内。在一些方面中,延伸部分427的长度可能小于栅极接触基底426的长度(在“l”方向上)。例如,延伸部分427的长度(l)可以比栅极接触基底426窄约10nm。因而,在一些方面中,延伸部分的长度可以在20nm至290nm的范围内。在一些方面中,延伸部分被形成在与栅极接触基底的共同中心线上(在l方向上居中),例如,每一侧窄5nm以提供附加余量以防止短路、泄漏等。然而,在一些方面中,延伸部分427可以相对于栅极接触基底426具有相同的长度或更大的长度(在“l”方向上)。栅极接触基底426和延伸部分427可以由相同的材料(例如,氮化钛(tin)、钛铝(tial)、钛铝氮化物(tialn)、铝、钨、铜、或任何合适的导电材料)形成。延伸部分427允许设计人员调整长沟道设备的vt的附加调谐参数,这也允许对传统调谐参数(上文所讨论的)进行更大的调整,因此可以满足长沟道目标阈值电压和短沟道目标阈值电压,如图2所示。应当领会,前述尺寸和材料以及所图示的配置仅作为示例提供,不应解释为限制本文中所公开的各个方面。

43.因而,本公开的至少一个方面包括半导体设备(例如,400),具有衬底的多个鳍片(例如,422)。长沟道栅极(例如,424)被设置在多个鳍片(例如,422)的第一部分上方。半导体设备(例如,400)还具有栅极接触(例如,425),该栅极接触(例如,425)具有栅极接触(例如,426)和从有源区域外部的栅极接触基座(例如,426)延伸到有源区域(例如,418)中的延伸部分(例如,427)。

44.进一步地,应当领会,本文中所公开的方面可以在没有附加成本、对产量没有影响并且没有附加掩模或过程步骤的情况下制造,如以下段落中所更详细讨论的。在以下过程描述中,相同部件的编号相同。然而,并非所有部件都会在连续图中进行编号和/或讨论,以避免过多冗余并且关注与所图示的制造过程的每个部分相关的设备的各部分。

45.图5是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。如所图示的,硅(si)衬底使用传统浅沟槽隔离(sti)过程被有效地分成3个单独区域。例如,通过使用光刻技术,可选地,结合一个或多个光刻掩模,设计人员可以定义衬底部分(例如,si衬底510、520和530)的侧向尺寸、位置和形状。可选地,衬底部分可以以单独图案化顺序形成。单独的衬底部分可以用于不同应用。例如,si衬底510可以用于sc逻辑设备并且通过sti部分512与硅衬底的其他部分分开。si衬底520可以用于lc逻辑设备并且通过sti部分512和sti部分522与硅衬底的其他部分分开。si衬底520可以用于lc输入/输出(i/o)设备,并且通过sti部分522与硅衬底的其他部分分开。然而,应当领会,所图示的衬底和设计用途仅用于说明,并且可以形成或多或少的衬底部分,并且设计用途可以与所图示的示例不同。

46.图6是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。如所图示的,使用传统过程,伪栅极在各种si衬底部分上被图案化和形成。例如,sc伪栅极610被形成在si衬底510上方,lc伪栅极620被形成在si衬底520上方,并且lc伪栅极630被形成在si衬底530上方。

47.图7是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。如所图示的,可以使用传统过程将绝缘垫片施加到栅极。例如,绝缘垫片710被形成在sc伪栅极610

上,该sc伪栅极610被形成在si衬底510上,绝缘垫片720被形成在lc伪栅极620上,该lc伪栅极620被形成在si衬底520上方,绝缘垫片730被形成在lc伪栅极630上,该lc伪栅极630被形成在si衬底530上方。部分712、714是si衬底510中的源极/漏极区域,部分722、724是si衬底520中的源极/漏极区域,并且部分732、734是si衬底530中的源极/漏极区域,并且使用传统过程形成。

48.图8是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。传统外延生长材料可以用于形成finfet设备的源极/漏极区域。如所图示的,生长源极/漏极外延层,源极/漏极区域812和814与sc伪栅极610相邻形成并且被形成在si衬底510上方,源极/漏极区域822和824与lc伪栅极620相邻形成并且被形成在si衬底520上方,并且源极/漏极区域832和834与lc伪栅极630相邻形成并且被形成在si衬底530上方。

49.图9是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。第一电介质层900可以被形成在源极/漏极区域812、814、822、824、832和834、sc伪栅极610、绝缘垫片710、si衬底510、lc伪栅极620、绝缘垫片720、si衬底520、lc伪栅极630、绝缘垫片730和si衬底530上方。第一电介质层900可以被平坦化,直至sc伪栅极610、绝缘垫片710、lc伪栅极620、绝缘垫片720、lc伪栅极630和绝缘垫片730通过第一电介质层900而被暴露。可以进行化学机械抛光(cmp),直至第一电介质层900与如所图示的顶部部分基本共面或基本齐平。第一电介质层900可以保留在衬底部分和源极/漏极区域上方以在后续处理期间保护这些区域。

50.图10是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。如所图示的,sc伪栅极610、lc伪栅极620和lc伪栅极630使用传统技术(诸如垂直蚀刻过程,诸如反应离子蚀刻(rie))移除。从而在被第一电介质层900包围的绝缘垫片710、绝缘垫片720和绝缘垫片730内留下空隙。

51.图11是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。如所图示的,绝缘垫片710、720和730内留下的空隙使用高k(hk或hik)(例如,1112)/金属栅极(mg)(例如,1114)沉积物填充以形成sc栅极1110、lc栅极1120和lc栅极1130。术语高k是指相对于二氧化硅具有高电介质常数κ的材料。在沉积之后,栅极材料使用cmp进行平坦化。如所图示的,在cmp过程之后,第一电介质层900与sc栅极1110、绝缘垫片710、lc栅极1120、绝缘垫片720、lc栅极1130和绝缘垫片730的顶部部分基本共面或基本齐平。

52.图12是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。如所图示的,第二电介质层1200可以被形成在第一电介质层900以及sc栅极1110、绝缘垫片710、lc栅极1120、绝缘垫片720、lc栅极1130和绝缘垫片730的顶部部分上方。

53.图13是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。如所图示的,源极/漏极接触通过第一电介质层900和第二电介质层1200形成。具体地,源极/漏极接触1312、1314、1322、1324、1332和1334分别被耦合到源极/漏极区域812、814、822、824、832和834。

54.图14是根据本公开的一个或多个方面的形成finfet的过程的部分的图示。如所图示的,栅极接触1410、1420和1430通过第二电介质层1200形成。具体地,栅极接触1410使用传统过程耦合到sc栅极1110。然而,耦合到lc栅极1120的lc栅极接触1420具有在lc栅极1120的顶部上延伸的延伸部分。同样,耦合到lc栅极1130的lc栅极接触1430具有在lc栅极

1130的顶部上延伸的延伸部分。

55.图15是根据本公开的一个或多个方面的二维(2d)平面图finfet的图示。如所图示的,延伸部分1527从栅极接触1420的栅极接触基底1526延伸。应当领会,lc栅极接触1420的延伸部分1527和栅极接触基底1526都形成为一个结构,如图14所示。延伸部分1527在有源区域和鳍片1522中的至少一个鳍片上方延伸。在一些方面中,延伸部分1527在所有鳍片1522上方延伸。因而,无需附加过程步骤来形成延伸栅极配置。同样,延伸部分1537从栅极接触1430的栅极接触基底1536延伸。延伸部分1537在有源区域和鳍片1532中的至少一个鳍片上方延伸。在一些方面中,延伸部分1537在所有鳍片1532上方延伸。应当领会,lc栅极接触1430的延伸部分1537和栅极接触基底1536也形成为一个结构,如图14所示。与先前所讨论的栅极接触的延伸部分相比,sc栅极接触1410以传统方式形成并且没有延伸到鳍片1512上方的部分。因而,本公开的各方面允许改进长沟道finfet设备而不影响短沟道设备。附加地,所公开的各个方面无需附加过程步骤,因此不会对生产复杂性或成本产生负面影响。

56.应当领会,诸如分离源极/漏极接触1312、1314、1322、1324、1332和1334以及将栅极接触、源极接触和漏极接触耦合到附加晶体管和/或其他元件之类的附加金属处理可以使用本领域已知的传统技术执行。进一步地,应当领会,在前面的描述中,没有提供用于形成finfet的传统过程方法的详尽细节。进一步地,本文中所描述的各个方面不限于在前述制造过程描述中提供的细节,并且熟练的设计人员可以使用各种已知过程来形成根据所公开的各方面的半导体设备。

57.因而,应当领会,本文中所公开的各个方面包括用于制造半导体设备的方法。图16图示了根据本公开的一些示例的半导体设备的示例性制造方法的流程图。如图16所示,方法1600开始于框1602:在衬底上形成多个鳍片。方法1600在框1604继续:形成长沟道栅极,该长沟道栅极设置在多个鳍片的第一部分上方。方法1600在框1606中继续:形成栅极接触,该栅极接触具有栅极接触基底和从有源区域外部的栅极接触基底延伸到有源区域中的延伸部分。

58.图17图示了根据本公开的一些示例的示例性移动设备。现在,参考图17,描绘了根据示例性方面配置的移动设备的框图并且一般指定为1700。在一些方面中,移动设备1700可以配置为无线通信设备,该无线通信设备可以包括如本文中所公开的一个或多个finfet半导体设备(例如、逻辑、存储器、rf、i/o等),该一个或多个finfet半导体设备可以集成到下文所讨论的各种有源设备中。如所示出的,移动设备1700包括处理器1701。处理器1701被示为包括指令流水线1712、缓冲处理单元(bpu)1708、分支指令队列(biq)1711和节流器1710,如本领域公知的。为了清楚起见,处理器1701的这个视图中省略了这些块的其他众所周知的细节(例如,计数器、条目、置信域、加权和、比较器等)。

59.处理器1701可以通过链路通信耦合到存储器1732。移动设备1700还包括显示器1728和显示器控制器1726,其中显示器控制器1726耦合到处理器1701和显示器1728。

60.在一些方面中,图17可以包括耦合到处理器1701的编码器/解码器(codec)1734(例如,音频和/或话音codec);耦合到codec1734的扬声器1736和麦克风1738;以及耦合到无线天线1742和处理器1701的无线控制器1740(其可以包括调制解调器)。

61.在存在上文所提及的块中的一个或多个块的特定方面中,处理器1701、显示器控制器1726、存储器1732、codec 1734和无线控制器1740可以包括在系统级封装设备或片上

系统设备1722。输入设备1730(例如,物理或虚拟键盘)、电源1744(例如,电池)、显示器1728、输入设备1730、扬声器1736、麦克风1738、无线天线1742和电源1744可以位于片上系统设备1722外部,并且可以耦合到片上系统设备1722的部件,诸如接口或控制器。

62.应当指出,虽然图17描绘了移动设备,处理器1701和存储器1732以及可以包括一个或多个如本文中所公开的半导体设备在内的其他部件也可以集成到机顶盒、音乐播放器、视频播放器、娱乐单元、导航设备、个人数字助理(pda)、固定位置数据单元、计算机、膝上型电脑、平板电脑、通信设备、移动电话或其他类似设备中。

63.图18图示了根据本公开的一些示例的可以与上述集成设备、半导体设备、集成电路、管芯、中介层、封装或层叠封装(pop)中的任一项集成的各种电子设备。例如,移动电话设备1802、膝上型计算机设备1804和固定位置终端设备1806可以包括如本文中所描述的如本文所公开的一个或多个半导体设备1800。集成设备1800可以为例如本文中所描述的集成电路、管芯、集成设备、集成设备封装、集成电路设备、设备封装、集成电路(ic)封装、层叠封装设备。图18中图示的设备1802、1804、1806仅是示例性的。其他电子设备也可以以集成设备1800为特征,包括但不限于设备(例如,电子设备)组,该设备组包括移动设备,手持式个人通信系统(pcs)单元,便携式数据单元(诸如个人数字助手、支持全球定位系统(gps)的设备、导航设备、机顶盒、音乐播放器、视频播放器、娱乐设备),固定位置数据单元(诸如抄表设备、通信设备、智能手机、平板计算机、计算机、可穿戴式设备、服务器、路由器),在机动车辆、无人机、自动车辆中实现的电子设备,或存储或检索数据或计算机指令的任何其他设备,或其任何组合。

64.根据前述公开内容,应当领会,用于制造本文中所公开的各个方面的附加过程对于本领域技术人员而言是显而易见的,并且上文所讨论和所附附图中所图示的过程的所有变型的字面再现并非必要。

65.前述公开的设备和功能(例如,如参考图4至图18中的任一项或多项所描述的)可以被设计和配置为存储在计算机可读介质上的计算机文件(例如,rtl、gdsii、gerber等)。一些或所有此类文件可以提供给基于此类文件制造设备的制造处理人员。所得产品可能包括半导体晶片,这些半导体晶片然后切割成半导体管芯并且封装成半导体芯片。然后,可以在如上文所描述的设备中采用这些芯片。

66.结合本文中所公开的实施例所描述的方法、序列和/或算法可以直接体现在硬件中、由处理器执行的软件模块中、或两者的组合中。软件模块可以驻留在ram存储器、闪存、rom存储器、eprom存储器、eeprom存储器、寄存器、硬盘、可移除式磁盘、cd-rom或本领域已知的任何其他形式的存储介质中。示例性存储介质耦合到处理器,使得处理器可以从存储介质读取信息和将信息写入存储介质。在备选方案中,存储介质可以集成到处理器中。

67.因而,本文中所公开的实施例可以包括体现如本文中所公开的一个或多个半导体设备的制造方法的非暂态计算机可读介质。因而,由于用于执行本文中所描述的制造过程的任何手段都被本公开所设想,所以本公开不限于所图示的示例。

68.虽然前述公开示出了各种说明性实施例,但是应当指出,在没有背离如所附权利要求限定的本公开的教导范围的情况下,可以在本文中进行各种改变和修改。举例标识并说明的各种材料可以被已知等同或备选材料代替。上文所讨论的示例制造过程可以将各种过程操作组合或拆分成附加过程操作。附加地,除非具体描述为需要特定次序或如果有必

要如取决于前一过程,否则根据本文中所描述的本公开的实施例的方法权利要求中描述的过程、功能、步骤和/或动作无需按任何特定次序执行。更进一步地,尽管本公开的元件可以以单数形式描述或要求保护,但是除非明确陈述局限于单数,否则复数为所设想。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。